# 7L14 SPECTRUM ANALYZER

**OPTIONS INCLUDED**

Please Check for CHANGE INFORMATION at the Rear of This Manual Copyright © 1980 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and registered trademarks of Tektronix, Inc. TELEQUIP-MENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

# **TABLE OF CONTENTS**

|            |                                                                        | rage                                   |                                                                                                  | ı age                                        |

|------------|------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------|

| LIST OF IL | LUSTRATIONS                                                            | v                                      | Section 2 OPERATING INSTRUCTIONS (cont)                                                          |                                              |

|            | R SAFETY SUMMARY                                                       |                                        | Adjust Contrast and Check Baseline Clipper Operation                                             | 2-8<br>2-9                                   |

| Section 1  | GENERAL INFORMATION AND SPECIFICATION General Information              | 1-1                                    | Equipment Required                                                                               | 2-9<br>2-9<br>2-9                            |

|            | Change and History Information Accessories                             | 1-1                                    | Check Frequency Readout Accuracy Check Range of the VAR Control Check the Operation of the VIDEO | 2-11                                         |

|            | Frequency Related                                                      | 1-2<br>1-3                             | FILTERS                                                                                          | 2-11                                         |

|            | General Characteristics                                                | 1-4<br>1-5                             | Internal Sources                                                                                 | 2-13                                         |

|            | Physical Characteristics                                               |                                        | Check Sweep Circuit Operation with the TIME/DIV Selector in the Manual and Off Positions         | 2-15<br>2-15<br>2-16<br>2-16<br>2-17<br>2-18 |

| Section 2  | OPERATING INSTRUCTIONS  Unpacking and Initial Inspection  Installation | 2-1<br>2-1<br>2-2<br>2-7<br>2-7<br>2-7 | Selecting Sweep Rate                                                                             | 2-18<br>2-18<br>2-19<br>2-19<br>2-20         |

|            | Check and Adjust LOG AMPL                                              | 2 0                                    | T                                                                                                |                                              |

REV MAY 1984 i

# **TABLE OF CONTENTS (CONT)**

|           | l l                                                                 | Page      |                                       | Page |

|-----------|---------------------------------------------------------------------|-----------|---------------------------------------|------|

|           | WARNING                                                             | Section 4 | CALIBRATION (cont)                    |      |

|           |                                                                     |           | Equipment Required (Table 4-1)        | 4-1  |

|           | OLLOWING SERVICING INSTRUCTION                                      |           |                                       |      |

|           | PR USE BY QUALIFIED PERSONNEL ONL<br>OID PERSONAL INJURY, DO NOT PE |           | PERFORMANCE CHECK                     |      |

|           | ANY SERVICING OTHER THAN THAT CO                                    |           | Introduction                          |      |

|           | OIN OPERATING INSTRUCTIONS UNLES                                    |           | Incoming Inspection Test              |      |

| YOU AF    | RE QUALIFIED TO DO SO.                                              |           | Check Frequency Readout Accuracy .    | 4-2  |

| Section 3 | THEORY OF OPERATION                                                 |           | Check Frequency Span Accuracy and     |      |

| Section 5 | Block Diagram                                                       | 3-1       | Linearity                             | 4-2  |

|           | Detailed Circuit Description                                        |           | Check Display Mode Accuracy           | 4-4  |

|           | RF or Microwave Circuits                                            |           | Check the Calibrator Frequency        | 4-5  |

|           | Phase Lock and Frequency                                            | 0.2       | Check the Calibrator Power Level      | 4-6  |

|           | Stabilization                                                       | 3-3       | Check RF Attenuator Accuracy          | 4-6  |

|           | YIG Driver, Voltage Memory, Phase                                   |           | Check IF Gain Step Accuracy           | 4-7  |

|           | Lock Logic and Marker Generator .                                   | 3-5       | Check Noise Sidebands                 | 4-8  |

|           | Frequency Tuning Control and                                        |           | Check Sweep Accuracy                  | 4-8  |

|           | Readout                                                             | 3-5       | Check Triggering Sensitivity          | 4-8  |

|           | Tuning Control                                                      | 3-5       | Check Display Flatness                | 4-10 |

|           | YIG Driver                                                          | 3-6       | Check Resolution Bandwidth Accuracy   |      |

|           | Frequency Span                                                      | 3-6       | and Shape Factor                      | 4-11 |

|           | Marker Generator                                                    | 3-6       | Check Signal Level Change between any |      |

|           | 105 MHz IF Amplifier, 3rd Mixer and                                 |           | 2 bandwidths                          |      |

|           | Oscillator                                                          | 3-6       | Check Residual FM (in phaselocked) .  | 4-13 |

|           | 10 MHz IF Pre-resolution Amplifier                                  |           | Check Residual FM (phaselocked)       | 4-14 |

|           | and Resolution Filter Circuits                                      | 3-6       | Check Stability                       | 4-14 |

|           | 30 Hz Filter                                                        | 3-7       | Check Sensitivity                     | 4-14 |

|           | 50 MHz Calibrator                                                   | 3-7       | Check Residual Spurious Responses .   | 4-15 |

|           | Function IF Amplifier                                               | 3-7       | Check Second Order Intermodulation    |      |

|           | Video Filter, Baseline Clipper and                                  |           | Products                              | 4-15 |

|           | Vertical Output                                                     | 3-8       | Check Third Order Intermodulation     |      |

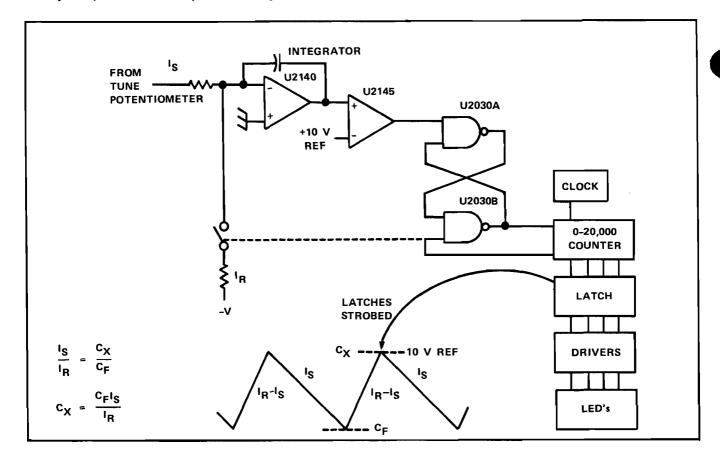

|           | Frequency Readout                                                   | 3-9       | Products                              | 4-16 |

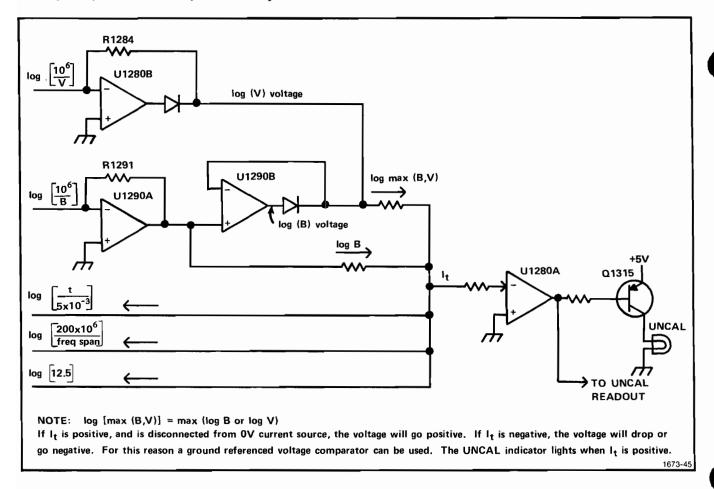

|           | Uncal Circuit                                                       | 3-11      |                                       |      |

|           | Sweep Triggering, Sweep Generator                                   |           | ADJUSTMENT PROCEDURE                  |      |

|           | and Horizontal Amplifiers                                           | 3-11      | Introduction                          | 4-18 |

|           | Digital Storage                                                     | 3-12      | Time Base Section                     | 4-18 |

|           | Vertical Section                                                    | 3-13      | Adjust Sweep Length, Offset and       |      |

|           | Horizontal Section                                                  | 3-15      | Triggering                            | 4-18 |

|           | Reference Level Readout                                             | 3-16      | Function IF Alignment                 | 4-20 |

|           |                                                                     |           | Adjust the LIN Mode Baseline Offset   | 4-21 |

|           |                                                                     |           | Adjust the Gain Compensation and      |      |

| Section 4 | CALIBRATION                                                         |           | Calibrate the Reference Level         | 4-21 |

|           | Introduction                                                        |           | 1st LO Phase Lock Loop                | 4-22 |

|           | History Information                                                 | 4-1       | Error Amplifier Offset Adjustment .   | 4-22 |

ii REV MAY 1984

# **TABLE OF CONTENTS (CONT)**

|           |                                       | Page |           |                                                        | Page       |

|-----------|---------------------------------------|------|-----------|--------------------------------------------------------|------------|

| Section 4 | CALIBRATION (cont)                    |      | Section 5 | MAINTENANCE INSTRUCTIONS (cont)                        |            |

|           | Frequency Span and 1st LO Calibration | 4-22 |           | Resistor Color Code                                    | 5-4        |

|           | Adjust the Frequency Span of the 1st  |      |           | Capacitor Marking                                      | 5-4        |

|           | LO and 16-19 MHz Oscillators          | 4-22 |           | Diode Color Code                                       | 5-4        |

|           | Calibrate the Center Frequency and    |      |           | Transistor and IC Electrode                            |            |

|           | Frequency Readout                     |      |           | Configuration                                          | 5-4        |

|           | Adjust Marker Gain and Marker Offset  |      |           | Diode Checks                                           | 5-5        |

|           | Calibration of Digital Storage        |      |           | IC Checks                                              | 5-5        |

|           | Setting B-SAVE A Reference Level .    |      |           | General Troubleshooting Technique                      | 5-6        |

|           | Adjust Digital Storage Compensation   | 4-27 |           | CORRECTIVE MAINTENANCE                                 | 5-6        |

|           | Phase Lock Calibration Adjustments .  | 4-28 |           | Obtaining Replacement Parts                            | 5-6        |

|           | Adjust the Memory Gain                | 4-28 |           | Parts Repair and Return Program .                      | 5-6        |

|           | Resolution                            | 4-29 |           | Soldering Technique                                    | 5-7        |

|           | Adjust the Bandpass of the 105 MHz    |      |           | Replacing the Square Pin for Multi-                    |            |

|           | IF Amplifier and 300 kHz Filter       | 4-29 |           | pin Connectors                                         | 5-7        |

|           | Adjust the Resolution Gain Leveling   |      |           | Selected Components                                    | 5-7        |

|           | Compensation                          |      |           | MAINTENANCE OF THE LEFT SIDE .                         | 5-8        |

|           | Adjust the Post Resolution Amplifier  |      |           | Replacing Assemblies                                   | 5-8        |

|           | Gain                                  |      |           | Maintenance Tools                                      | 5-8        |

|           | Minimize Intermodulation Products     | 4-34 |           | Replacing the Differential Attenuator                  |            |

|           | 50 MHz Calibrator                     | 4-34 |           | Assembly                                               | 5-8        |

|           |                                       |      |           | Replacing the 1st LO (YIG) Oscillator                  |            |

|           |                                       |      |           | ,                                                      | 5-8        |

| Section 5 | MAINTENANCE INSTRUCTIONS              |      |           | Replacing the 2.095 GHz Filter                         |            |

|           | Introduction                          |      |           | Assembly, or the Multiplier, Bandpass                  | <b>5</b> 0 |

|           | Access to the Interior of the 7L14    |      |           |                                                        | 5-8        |

|           | Static Sensitive Components           |      |           |                                                        | 5-9        |

|           | PREVENTIVE MAINTENANCE                | 5-2  |           | ,                                                      | 5-9        |

|           | Cleaning                              |      |           | Adjust the Response of the Filter and Mixer Assemblies | 5-11       |

|           | Exterior                              | 5-3  |           | Replacing Switches                                     |            |

|           | Interior                              | 5-3  |           | Replacing the Display Mode                             | J-11       |

|           | Lubrication                           | 5-3  |           |                                                        | 5-11       |

|           | Visual Inspection                     | 5-3  |           | MAINTENANCE OF THE RIGHT SIDE                          |            |

|           | Transistor and IC Checks              | 5-3  |           |                                                        | 5-12       |

|           | Performance Checks and                |      |           | Replacing the Frequency Tuning                         |            |

|           | Recalibration                         |      |           |                                                        | 5-12       |

|           | TROUBLESHOOTING                       |      |           | Replacing the Sweep Circuit Board                      | 5-12       |

|           | Troubleshooting Aids                  |      |           |                                                        | 5-12       |

|           | Diagrams                              |      |           | Replacing the Resolution Circuit                       |            |

|           | Circuit Board Illustrations           |      |           |                                                        | 5-12       |

|           | Wiring Color Code                     |      |           | Replacing Circuit Boards in the Phase                  |            |

|           | Harmonica Connector Holders .         | 5-4  |           | Lock Circuit Assembly                                  | 5-14       |

|           |                                       |      |           |                                                        |            |

# **TABLE OF CONTENTS (cont)**

|           |                                          | Page |

|-----------|------------------------------------------|------|

| Section 5 | MAINTENANCE INSTRUCTIONS (cont)          |      |

| Re        | placing the 5 V Regulator Board          | 5-14 |

| Re        | placing the Digital Storage Drawer       |      |

| As        | sembly                                   | 5-14 |

| Re        | emoving the DVM Logic and                |      |

| Re        | eadout Circuit Board                     | 5-14 |

| Re        | placement of the Left Interface          |      |

| As        | sembly                                   | 5-14 |

| Repla     | acing Knobs and Switches                 | 5-14 |

| Repla     | acing the FREQ SPAN/DIV and              |      |

| RESC      | DLUTION Knobs and Starts                 | 5-14 |

| Repla     | acing the Cam Switches                   | 5-15 |

| Repla     | acing the FREQ                           |      |

| SPAN      | N/RESOLUTION Selector                    | 5-15 |

| TIME      | /DIV Selector Replacement                | 5-16 |

| Repla     | acing the Cam Actuator and               |      |

| Poter     | ntiometer Switch Assemblies              | 5-16 |

| Remo      | oving the Front-Panel Pushbutton         |      |

| Switc     | ches                                     | 5-16 |

| Tr        | iggering Switches                        | 5-16 |

| Vi        | deo Filter and Digital Storage           |      |

| Sv        | vitches                                  | 5-16 |

|           |                                          |      |

| Section 6 | OPTIONS                                  |      |

| Section 7 | REPLACEABLE ELECTRICAL PARTS             |      |

| Section 8 | DIAGRAMS AND CIRCUIT BOARD ILLUSTRATIONS |      |

| Section 9 | REPLACEABLE MECHANICAL                   |      |

# LIST OF ILLUSTRATIONS

| Fig.<br>No.     | ı                                                                       | Page            | Fig.<br>No. |                                                                | Page |

|-----------------|-------------------------------------------------------------------------|-----------------|-------------|----------------------------------------------------------------|------|

|                 | 7L14 Spectrum Analyzer                                                  | x               | 4-7         | Measuring bandwidth and shape factor .                         | 4-12 |

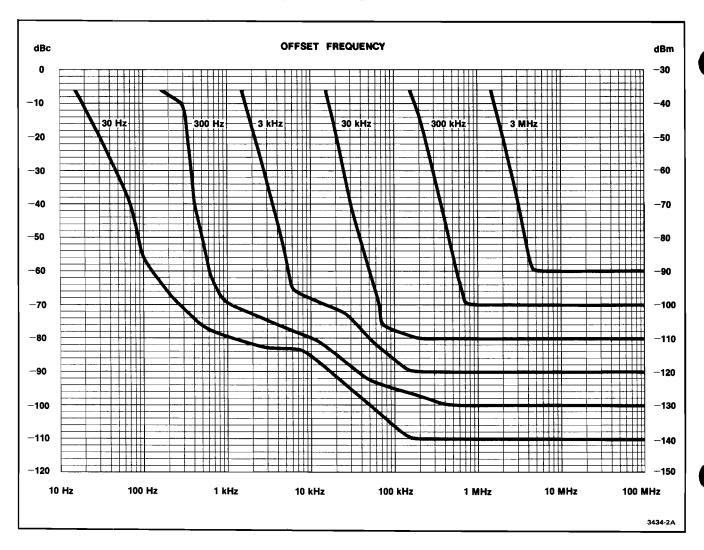

| 1-1             | Typical filter shape, phase noise sidebands                             |                 | 4-8         | Measuring residual FM                                          | 4-13 |

|                 | and sensitivity for the 7L14                                            |                 | 4-9         | Resistive bridge used for measuring 2nd                        |      |

| 2-1             | Front-panel controls                                                    | 2-2             |             | order IM products                                              | 4-16 |

| 2-2             | Front-panel selector positions for front-                               |                 | 4-10        | Measuring 3rd order IM products                                | 4-17 |

|                 | panel calibration                                                       | 2-6             | 4-11        | Calibrating the sweep ramp                                     | 4-19 |

| 2-3             | Calibrating the sweep span                                              | 2-8             | 4-12        | Location of adjustments on the sweep                           |      |

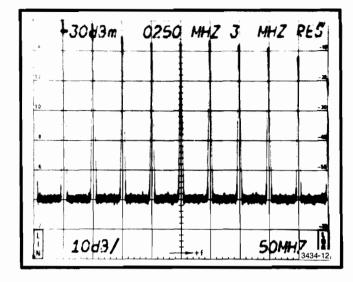

| 2-4             | Video filter operation                                                  | 2-12            |             | board                                                          | 4-20 |

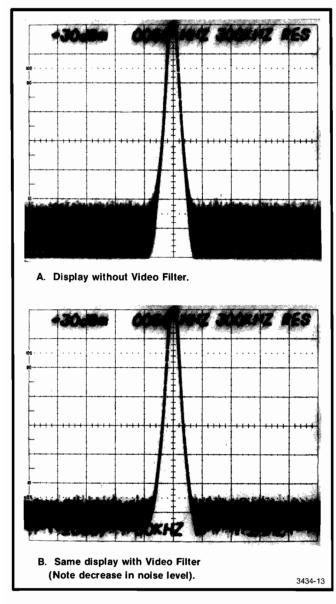

| 2-5             | Measuring bandwidth and shape factor .                                  | 2-13            | 4-13        | Calibration adjustments and test points on                     |      |

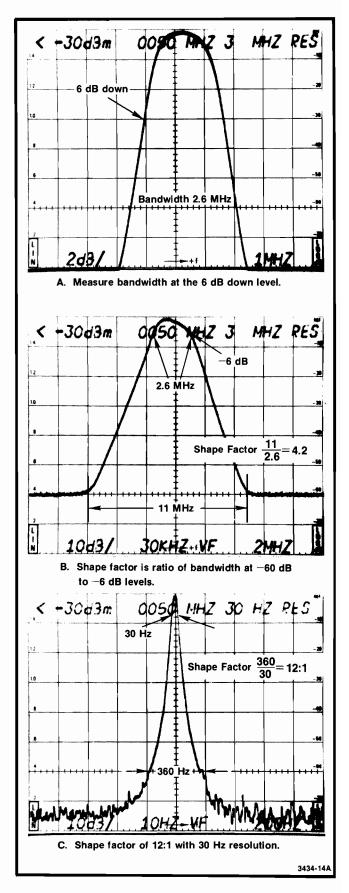

| 2-6             | Measuring residual FM                                                   | 2-14            |             | the Function IF board                                          | 4-21 |

| 2-7             | Using digital storage to measure the                                    |                 | 4-14        | Grounding strap connected to pin 1 of                          | 4 00 |

|                 | difference between two displays                                         | 2-15            | 4.45        | P1078                                                          | 4-23 |

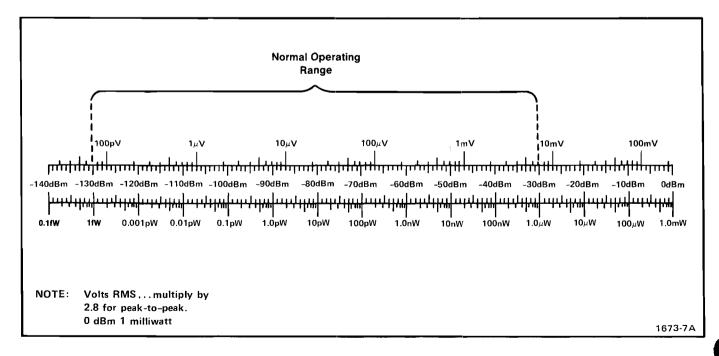

| 2-8             | Volts-dBm-Watts Conversion chart for 50 $\Omega$                        |                 | 4-15        | Location of P69 and R51 on Hybrid Assembly A24                 | 4-23 |

|                 | impedance                                                               | 2-16            | 4-16        | Location of the YIG Driver and Voltage                         | 4-20 |

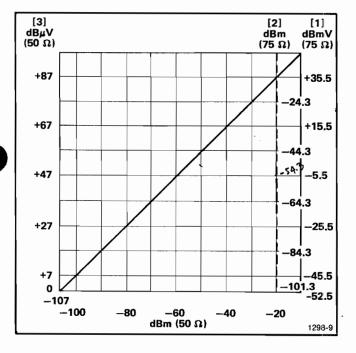

| 2-9             | Circuit of a 75 $\Omega$ -to-50 $\Omega$ matching pad (ac               |                 | 4-10        | Memory adjustments                                             | 4-24 |

|                 | coupled)                                                                | 2-17            | 4-17        | 100 MHz markers on a 100 MHz/Div                               |      |

| 2–10            | Graph to illustrate the relationship between                            |                 | 7 17        | frequency span                                                 | 4-25 |

| )               | dBm, dBmV and dB $\mu$ V (matching attenuator included where necessary) | 2 17            | 4-18        | Location of R1960, Sweep Driver                                |      |

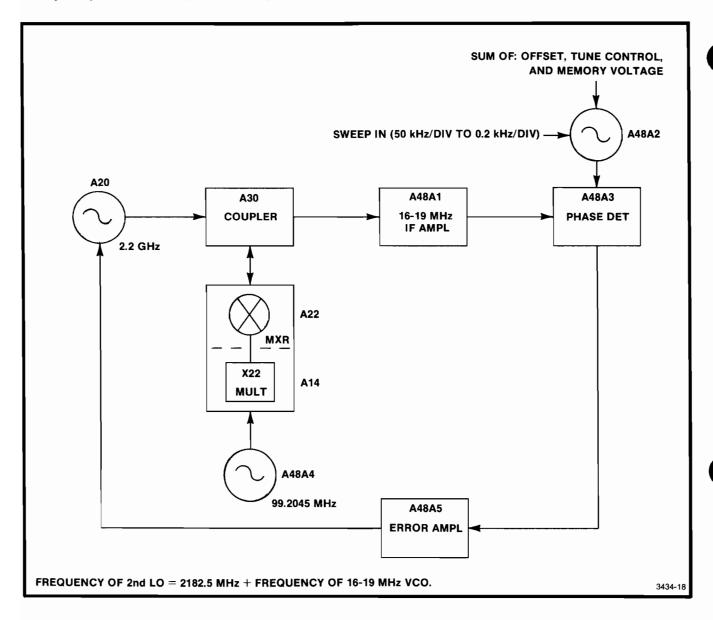

| 3-1             | Functional block diagram of 2nd LO phase                                | 2-17            |             | adjustment for the 16-19 MHz oscillator .                      | 4-25 |

| 3-1             | lock circuit or frequency servo system                                  | 3-4             | 4-19        | Frequency Readout circuit adjustments .                        | 4-25 |

| 3-2             | Log converter curve                                                     |                 | 4-20        | Marker Gain and Marker Offset                                  |      |

| 3-3             | Functional block diagram of the frequency                               |                 |             | adjustments                                                    | 4-26 |

|                 | readout circuit                                                         |                 | 4-21        | Location of Digital Storage adjustments.                       | 4-27 |

| 3-4             | Basic functional block diagram of the uncal                             |                 | 4-22        | Location of the Phase Lock calibration                         |      |

|                 | circuit                                                                 | 3-12            |             | adjustments                                                    | 4-28 |

| 4-1             | Test equipment set up for checking                                      |                 | 4-23        | Location of Memory Adjust R2605                                | 4-29 |

|                 | accuracy of center frequency readout and                                |                 | 4-24        | 105 MHz IF and 3 MHz bandwidth                                 |      |

|                 | frequency span                                                          |                 |             | adjustments                                                    |      |

| 4-2             | Test equipment setup for checking display                               |                 | 4-25        | Wide-band Filter Adjust C456                                   |      |

|                 | mode accuracy, calibrator power level and                               |                 | 4-26        | Typical flat-top response when narrow filter                   |      |

| 4.0             | RF attenuator                                                           | 4-5             |             | is adjusted correctly                                          | 4-30 |

| 4-3             | Test equipment set up for checking                                      | 4-6             | 4-27        | Typical response characteristics for the                       | 4 00 |

| 4.4             | calibrator frequency                                                    |                 |             | 105 MHz IF through the wide filter                             | 4-30 |

| 4-4             | Test equipment set up for checking sweep accuracy                       | 4-9             | 4-28        | Connections and adjustments for adjusting                      | 4 21 |

| 4-5             | Display showing time markers for checking                               | <del>-</del> -3 | 4.00        | the narrow post-amplifier filter                               | 4-31 |

| <del>4</del> -3 | sweep accuracy                                                          | 4-9             | 4-29        | 300 kHz filter adjustments and typical response charateristics | 4-31 |

| 4-6             | Test equipment set up for checking                                      | . •             | 4-30        | Resolution gain compensating adjustments                       |      |

| . 3             | triggering sensitivity                                                  | 4-10            | + 00        | 1.000 attoring and compensating adjustments                    | 4-00 |

**REV MAY 1984**

# **LIST OF ILLUSTRATIONS (cont)**

| Fig.<br>No. | F                                                                           | Page | Fig.<br>No. |                                                              |

|-------------|-----------------------------------------------------------------------------|------|-------------|--------------------------------------------------------------|

| 4-31        | Test equipment set up to measure IM distortion                              | 4-34 | 8-1         | A48A6—Sampling Generator and Driver circuit board.           |

| 4-32        | Location of C95 in the 3rd Mixer assembly                                   | 4-35 | 8-2         | A48A1-16-19 MHz Amplifier circuit board.                     |

| 4-33        | Location of R956, Calibrator Output Level adjustment                        |      | 8-3         | A48A3—Phase Detector circuit board (SN B132456 & up).        |

| 5-1<br>5-2  | Gaining access to the 7L14 interior Multipin (harmonica circuit board       |      | 8–4         | A48A2—16-19 MHz Voltage Controlled Oscillator circuit board. |

| 5-3         | connectors)                                                                 |      | 8-5         | A48A5—Summing Amplifier and Second LO Error Amplifier.       |

| 5-4         | Electrode configuration for semiconductor                                   |      | 8-6         | A48A4-99.2045 MHz Oscillator circuit board.                  |

|             | components                                                                  | 5-5  | 8-7         | A48A7—Mother Board.                                          |

| 5-5         | Location of screws and assemblies of the                                    |      | 8-8         | A1-Front Panel circuit board.                                |

|             | left side                                                                   | 5-9  | 8-9         | A72—Tune Control circuit board.                              |

| 5-6         | Test equipment and illustrations to show                                    |      | 8-10        | A78-YIG Driver circuit board.                                |

|             | the response when calibrating the Multiplier, 2.18 GHz BP Filter, and Mixer |      | 8-11        | P/O A38-Resolution circuit board                             |

|             | Assembly for the 2nd LO frequency Servo                                     |      | 8-12        | A26-105 MHz IF circuit board.                                |

|             | system                                                                      |      | 8-13        | A38—Resolution circuit board.                                |

| 5-7         | Location of the mixer assembly locking                                      |      | 8-14        | A40—Function IF circuit board.                               |

|             | screws                                                                      | 5-11 | 8-15        | P/O A40-Function IF circuit board.                           |

| 5-8         | Adjustments for filter response                                             | 5-11 | 8-16        | A74—Center Interface circuit board.                          |

| 5-9         | Illustrations to show the procedures for                                    |      | 8-17        | A1A1-Reference Level Readout circuit board.                  |

|             | removing the Sweep board                                                    |      | 8-18        | A32A1-Display Mode Connector circuit board.                  |

| 5-10        | Removing the Frequency Readout boards                                       |      | 8-19        | A32-Display Mode Resistor circuit board.                     |

| 6-1         | Max Span Extender                                                           | 6-2  | 8-20        | A42A1-Sweep circuit board.                                   |

|             |                                                                             |      | 8-21        | A42A1-Sweep circuit board.                                   |

|             |                                                                             |      | 8-22        | A42A1-Sweep circuit board.                                   |

|             |                                                                             |      | 8-23        | A42A1-Sweep circuit board.                                   |

|             |                                                                             |      | 8-24        | A88-Digital Storage circuit board.                           |

|             |                                                                             |      | 8-25        | A90-Digital Storage Horizontal circuit board.                |

|             |                                                                             |      | 8-25        | A88—Digital Storage circuit board.                           |

|             |                                                                             |      | 8-26        | A90-Digital Storage Horizontal circuit board.                |

|             |                                                                             |      | 8-27        | A42A1—Sweep circuit board.                                   |

|             |                                                                             |      | 8-28        | A84—Readout Control circuit board.                           |

|             |                                                                             |      | 8-29        | A82-CRT Readout circuit board.                               |

|             |                                                                             |      | 8-30        | A80-Reference Level Readout circuit board.                   |

|             |                                                                             |      | 8-31        | A68-DVM Analog circuit board.                                |

|             |                                                                             |      | 8-32        | A60—DVM Readout circuit board.                               |

|             |                                                                             |      | 8-33        | A46—Sweep and Video Filter Readout circuit board.            |

|             |                                                                             |      | 8-34        | A74—Center Interface circuit board.                          |

vi REV MAY 1984

# **OPERATORS SAFETY SUMMARY**

The general safety information in this part of the summary is for both operating and servicing personnel. Specific warnings and cautions will be found throughout the manual where they apply, but may not appear in this summary.

#### Terms In This Manual

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### Terms As Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

#### Symbols In This Manual

This symbol indicates where applicable cautionary or other information is to be found.

#### Symbols As Marked on Equipment

DANGER - High voltage.

Protective ground (earth) terminal.

ATTENTION -- refer to manual.

#### **Power Source**

This product is intended to operate from a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### **Danger Arising From Loss of Ground**

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulating) can render an electric shock.

#### Do Not Operate in Explosive Atmospheres

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

#### Do Not Remove Covers or Panels

To avoid personal injury, do not remove the product covers or panels. Do not operate the product without the covers and panels properly installed.

REV MAY 1984 vii

## **SERVICE SAFETY SUMMARY**

## FOR QUALIFIED SERVICE PERSONNEL ONLY

Refer also to the preceding Operators Safety Summary.

#### Do Not Service Alone

Do not perform internal service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

#### Use Care When Servicing With Power On

Dangerous voltages exist at several points in this product. To avoid personal injury, do not touch exposed connections and components while power is on.

Disconnect power before removing protective panels, soldering, or replacing components.

#### **Power Source**

This product is intended to operate from a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

3434-1

7L14 Spectrum Analyzer

# GENERAL INFORMATION AND SPECIFICATION

## **GENERAL INFORMATION**

#### **Product Description**

The 7L14 Spectrum Analyzer displays information of signals within the frequency span of 10 kHz to 1.8 GHz. It contains horizontal sweep and timing circuits for frequency and time domain displays, and provides means for using an external sweep source to slave the 7L14 to some external device, such as a recorder.

The 7L14's digital storage capability permits flickerfree displays at slow sweep speeds. In the storage mode, the vertical display can be divided with a positionable threshold level: above this level video peaks are detected, below it video peaks are averaged. This threshold level is indicated by a horizontal cursor on the display.

The 7L14 requires three plug-in widths in any of the TEKTRONIX 7000 series mainframe oscilloscopes.

#### Standards, Documents, and References Used

Terminology used in the manual is in accordance with industry practice. Abbreviations are in accordance with ANSI Y1.1-1972, with exceptions and additions explained in parentheses after the abbreviation. Graphic symbology is based on ANSI Y32.2-1975. Logic symbology is based on ANSI Y32.14-1973 and the manufacturer's data books or sheets. A copy of ANSI standards may be obtained from the Institute of Electrical and Electronic Engineers, 345 47th Street, New York, NY 10017.

#### **Change and History Information**

Change information that involves manual corrections and/or additional data is located at the back of the manual in the CHANGE INFORMATION section. History information with the updated data is integrated into the text or diagrams when a page or diagram is updated.

#### Accessories

For a complete listing of the Standard and Recommended Accessories for the 7L14, refer to the Mechanical Parts List in the back of this manual.

# **SPECIFICATION**

The following list of instrument characteristics and features apply to the 7L14 Spectrum Analyzer after a 20 minute warmup, except as noted.

The Performance Requirement column describes the limits of the characteristic, and the Supplemental column describes features and typical values or information that may be useful to the user. Procedures to verify perfor-

mance requirements are provided in the Calibration section of the Service Instructions. The Performance Check procedures require sophisticated equipment as well as technical expertise to perform.

The Operator's Section contains a procedure that checks all functions of the 7L14. This check is recommended for incoming inspections to verify that the instrument is performing properly.

Table 1-1

ELECTRICAL CHARACTERISTICS

| Characteristic                                                                                          | Performance Requirement                                                | Supplemental Information                                                                                                               |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Related                                                                                       |                                                                        |                                                                                                                                        |

| Center Frequency                                                                                        |                                                                        |                                                                                                                                        |

| Range                                                                                                   | 10 kHz to 1.8 GHZ                                                      |                                                                                                                                        |

| Readout Resolution                                                                                      | Within 1 MHz                                                           |                                                                                                                                        |

| Readout Accuracy                                                                                        | ±(5 MHz +20% of Frequency Span/Div)                                    |                                                                                                                                        |

| Frequency Span                                                                                          | 200 Hz/Div to 100 MHz/Div                                              | In calibrated steps in a<br>1-2-5 sequence                                                                                             |

| Accuracy                                                                                                | Within 5% of the span selected                                         |                                                                                                                                        |

| Linearity                                                                                               | Within 5% of the span selected                                         |                                                                                                                                        |

| Max Span                                                                                                |                                                                        | Provides 1.8 GHz of span                                                                                                               |

| 0 Span                                                                                                  |                                                                        | Provides fixed frequency operation for time domain display                                                                             |

| Resolution Bandwidth<br>Range                                                                           |                                                                        | 30 Hz to 3 MHz, in decade steps                                                                                                        |

| Accuracy (6 dB down)                                                                                    | Within $\pm 20\%$ of the resolution selected                           |                                                                                                                                        |

| Shape Factor (60/6 dB)                                                                                  | 4:1 or less for 3 MHz to 0.3 kHz;<br>12:1 or less for 30 Hz resolution |                                                                                                                                        |

| Signal level change<br>between any two band-<br>widths                                                  | ±0.5 dB at room temperature ±2.0 dB max over temperature               |                                                                                                                                        |

| Incidental Fm'ing                                                                                       | ≤13 Hz (P-P) when phaselocked                                          |                                                                                                                                        |

|                                                                                                         | ≤10 kHz (P-P) for 20 ms when not phaselocked                           |                                                                                                                                        |

| Stability, at a fixed frequency and temperature after a two hour warmup and stable ambient temperature. | Within 2 kHz/Hr phaselocked                                            |                                                                                                                                        |

| por ataro.                                                                                              | Within 75 kHz/Hr not phaselocked                                       | A restabilization time of 10 minutes<br>per GHz of 1st LO frequency<br>change must be allowed if the cen-<br>ter frequency is retuned. |

<sup>&</sup>lt;sup>a</sup> 0 RF attenuation, -30 dBm reference level

Table 1-1 (cont.)

| Characteristic                                         | Performance Requirement                                                                        | Supplemental Information                                      |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Amplitude Related                                      |                                                                                                |                                                               |

| Display Modes<br>LOG 10 dB/Div                         |                                                                                                | Provides 70 dB dynamic range                                  |

| Accuracy                                               | Within 0.15 dB/dB to 2 dB max over 70 dB dynamic range                                         |                                                               |

| LOG 2 dB/Div                                           |                                                                                                | Provides 14 dB dynamic range                                  |

| Accuracy                                               | Within ±0.4 dB/2 dB to 1.0 dB max over 14 dB dynamic range                                     |                                                               |

| LIN                                                    | Within 10% over 8 divisions                                                                    |                                                               |

| Deviation Between Display Modes <sup>b</sup>           | ≤2 dB from 2 dB/Div to 10 dB/Div ≤0.5 Divisions from 2 dB/Div to LIN                           |                                                               |

| Reference Level<br>Below 100 KHz                       |                                                                                                | +30 dBm to -50 dBm, as the center frequency approaches 10 KHz |

| Above 100 KHz                                          |                                                                                                | +30 dBm to -100 dBm in 10 dB calibrated steps                 |

| Display Flatness                                       | ±1.5 dB, with respect to 50 MHz, over any selected frequency span.                             |                                                               |

| Sensitivity                                            |                                                                                                |                                                               |

| At 50 MHz<br>Resolution Bandwidth                      | Equivalent (average) Input Noise<br>Level (worst case)                                         | Applicable from 100 KHz to 1.8 GHz                            |

| 30 Hz<br>300 Hz<br>3 kHz<br>30 kHz<br>0.3 MHz<br>3 MHz | -130 dBm -120 dBm -110 dBm -100 dBm 90 dBm 80 dBm                                              |                                                               |

| Spurious Responses                                     |                                                                                                |                                                               |

| Residual                                               | $\leq$ -100 dBm (referenced to the 1st mixer input)                                            |                                                               |

| Second order inter-<br>modulation products             | 100 kHz -1.8 GHz: down 70 dB or<br>more from two -40 dBm signals,<br>within any frequency span |                                                               |

| Third order inter-<br>modulation products              | 100 kHz -1.8 GHz: down 70 dB or more from two -30 dBm signals, within any frequency span       |                                                               |

| RF Attenuator                                          |                                                                                                | Calibrated in 10 dB steps                                     |

| Accuracy                                               | ±0.25 dB or 1.2% of dB reading; whichever is greater                                           |                                                               |

<sup>&</sup>lt;sup>b</sup>For full screen signal.

Table 1-1 (cont.)

| Characteristic                                        | Performance Requirement                                                                   | Supplemental Information                                        |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Amplitude Related                                     |                                                                                           |                                                                 |

| IF Gain                                               |                                                                                           |                                                                 |

| Range                                                 |                                                                                           | 70 dB (80 dB when operating in 30 Hz resolution bandwidth)      |

| Step Accuracy                                         | ±1 dB per 10 dB step to ±2 dB max over entire range°                                      |                                                                 |

| General Characteristics                               |                                                                                           |                                                                 |

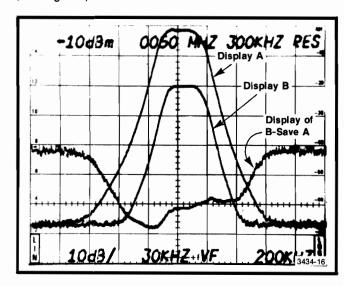

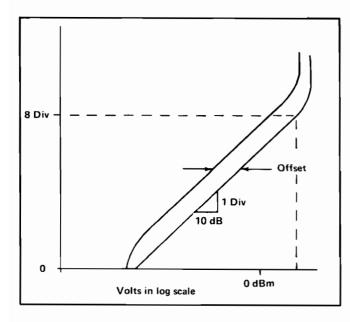

| Noise Sidebands                                       | 70 dB down; 25X resolution bandwidth                                                      | See Fig. 1-1                                                    |

| Sweep                                                 |                                                                                           | Triggered, manual, external                                     |

| Sweep Time                                            |                                                                                           | 10 s/Div to 1 μs/Div in a<br>1-2-5 sequence                     |

| Accuracy                                              | ±6% of selected Time/Div                                                                  |                                                                 |

| Triggering Modes                                      |                                                                                           | INTERNAL, EXTERNAL, EXT in HORIZ/TRIG and LINE                  |

| Sensitivity                                           | ≤0.5 division of internal<br>signal (P-P) and/or ≤0.5<br>volt (P-P) of external<br>signal |                                                                 |

| Power requirements from the mainframe                 |                                                                                           |                                                                 |

| To +50 V                                              |                                                                                           | Approx 35 mA                                                    |

| −50 V<br>+15 V                                        |                                                                                           | Approx 65 mA<br>Approx 875 mA                                   |

| −15 V<br>−15 V                                        |                                                                                           | Approx 900 mA                                                   |

| +5 V                                                  |                                                                                           | Approx 1080 mA                                                  |

| +5 V Lights<br>Total Lights                           |                                                                                           | Approx 130 mA<br>38 Watts typical                               |

| Input Signal Characteristics                          |                                                                                           |                                                                 |

| RF Input                                              |                                                                                           |                                                                 |

| Maximum input power level                             |                                                                                           | +30 dBm                                                         |

| Maximum input power level to the RF attenuator ≥10 dB |                                                                                           | 1 watt average (including DC),<br>100 watts peak simultaneously |

| Input Impedance                                       |                                                                                           | 50 ohm; vswr 1.35 max with 10 db                                |

<sup>&</sup>lt;sup>c</sup>Gain and attenuator not off-setting each other.

## Table 1-1 (cont.)

| Characteristic                              | Performance Requirement            | Supplemental Information                                                                                                                                                                                                                       |

|---------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Signal Characteristics (cont)         |                                    |                                                                                                                                                                                                                                                |

| External Horizontal/Trigger Input Connector |                                    |                                                                                                                                                                                                                                                |

| Input Voltage Range                         |                                    | Typically 0 V to 10 V for 10 division sweep                                                                                                                                                                                                    |

|                                             |                                    | Typically 0.5 V (P-P) to trigger the sweep circuits. 40 V peak max                                                                                                                                                                             |

| Output Signal Characteristics               |                                    |                                                                                                                                                                                                                                                |

| CAL OUT                                     | -30 dBm, ±0.3 dB at 50 MHz, ±0.01% | 50 MHz comb markers are provided for frequency and span calibration                                                                                                                                                                            |

| 1st LO OUT and<br>2nd LO OUT                |                                    | Provide access to the output of the respective local oscillators (1st LO +5 dBm min., 2nd LO -10 dBm min. +10 dBm max. These ports must be terminated in 50 ohms.                                                                              |

| SWP OUT                                     |                                    | 0 to -5 V                                                                                                                                                                                                                                      |

| Video Output                                |                                    | Typically 0.5 V of video signal per display division. Output impedance approx. 10 K ohm. Markers can be inserted upon the stored or non-stored trace by providing the VIDEO OUT port with a negative-going signal. Max. input level—10 V peak. |

REV MAY 1984 1-5

Fig. 1-1. Typical filter shape, phase noise sidebands and sensitivity for the 7L14.

Table 1-2

ENVIRONMENTAL CHARACTERISTICS

| Characteristic                     | Descri                                                                                                                                                                                                                                                                                                                  | ption           |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Temperature and Relative Humidity  |                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |

| Operating                          | +10°C to +40°C (75% humidity)                                                                                                                                                                                                                                                                                           |                 |  |  |  |

| Non-operating                      | -55°C to +75°C (75% humidity)                                                                                                                                                                                                                                                                                           |                 |  |  |  |

| Vibration                          |                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |

| Operating                          | Resonant searches along all three axes at 0.015 inch, frequency varied from 10-55 Hz, 15 minutes. All major resonances must be minimum per axis plus dwell at resonant frequency or 55 Hz for 10 minutes minimum per axis. Instrument secured to vibration platform during test. Total vibration time about 75 minutes. |                 |  |  |  |

| Shock                              |                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |

| Operating                          | Three shocks of 30g, one-half sine, 11 ms duration, each direction along each major axis. Guillotine-type shocks. Total of 18 shocks.                                                                                                                                                                                   |                 |  |  |  |

| Electromagnetic Interference (EMI) |                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |

|                                    | Test Method                                                                                                                                                                                                                                                                                                             | Remarks         |  |  |  |

| Conducted Emissions                | CE01                                                                                                                                                                                                                                                                                                                    | 60 Hz to 20 KHz |  |  |  |

|                                    | CE03<br>20 KHz to 50 MHz power leads                                                                                                                                                                                                                                                                                    | Full limits     |  |  |  |

| Conducted Susceptibility           | CS01<br>30 Hz to 50 KHz power leads                                                                                                                                                                                                                                                                                     | Full limits     |  |  |  |

|                                    | CS02<br>50 KHz to 400 KHz power leads                                                                                                                                                                                                                                                                                   | Full limits     |  |  |  |

|                                    | CS06 spike power leads                                                                                                                                                                                                                                                                                                  | Full limits     |  |  |  |

| Radiated Emissions                 | RE01<br>30 Hz to 30 KHz magnetic field                                                                                                                                                                                                                                                                                  | Full limit      |  |  |  |

|                                    | RE02<br>14 ± 3 KHz to 1 GHz                                                                                                                                                                                                                                                                                             | Full limits     |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |

| Radiated Susceptibility            | RS01<br>30 Hz to 30 KHz magnetic field                                                                                                                                                                                                                                                                                  | Full limit      |  |  |  |

Table 1-3

PHYSICAL CHARACTERISTICS

| Characteristic | Performance Requirement | Supplemental Information |

|----------------|-------------------------|--------------------------|

| Weight         |                         | 16 lbs. (7.2 kg)         |

| Length         |                         | 14.75 inches (375 mm)    |

| Height         |                         | 5.00 inches (120 mm)     |

| Width          |                         | 8.15 inches (200.5 mm)   |

# **OPERATING INSTRUCTIONS**

#### Unpacking and Initial Inspection

Before unpacking the 7L14 from its shipping container or carton, inspect for signs of external damage. If the carton is damaged, notify the carrier, as well as TEKTRONIX, Inc. The shipping carton contains the basic instrument and its standard accessories. Optional accessories are shipped in separate containers. Refer to the Accessories listing in the Mechanical Parts List for a complete listing.

If the contents of the shipping container are incomplete, if there is mechanical damage or defect, or if the instrument does not meet operational check requirements, contact your local Tektronix Field Office or representative.

The instrument has been inspected both mechanically and electrically before shipment. It should be free of mechanical damage and meet or exceed all electrical specifications. Procedures to check functional or operational performance are in the Operational Check Procedures. This check should satisfy the requirements for most receiving or incoming inspections. The electrical performance check procedure is part of the Service Instructions.

#### Installation

Installation of the 7L14 into the 7000 series mainframe consists of sliding the unit into the mainframe compartment.

Power to the mainframe should be OFF when installing the 7L14.

Ensure that the 7L14 is securely latched into place.

#### NOTE

A safety latch is used to reduce the possibility of the instrument slipping out of the mainframe.

For information on power source and power requirements, and environmental considerations, refer to the manual supplied with the 7000 series mainframe oscilloscope.

#### Repackaging for Shipment

When the 7L14 is to be shipped to a Tektronix Service Center for service or repair, attach a tag showing: owner and address, name of individual at your firm that can be contacted, complete serial number, and a description of the service required. If the original packaging is unfit for use or not available, repackage the equipment as follows:

- 1. Obtain a carton of corrugated cardboard having inside dimensions that are at least six inches more than the equipment dimensions, to allow for cushioning. Carton test strength should be 275 lbs (102.5 kg).

- 2. Surround the 7L14 with polyethylene sheeting to protect the finish.

- 3. Cushion the equipment on all sides with packing material or urethane foam between the carton and the sides of the equipment.

- 4. Seal with shipping tape or industrial stapler.

A safety latch must be released before the 7L14 can be pulled from the oscilloscope compartment. The unit will pull out part way when the front panel release (see Fig. 2-1) is pulled, then the spring safety latch must be pushed up to free the unit completely. This safety latch is located underneath the right rail, near the front corner.

Do not ship the 7L14 when it is installed in the mainframe, unless it is bolted into the mainframe. A spectrum analyzer securing kit is available from Tektronix, Inc. for the following instruments: 7313/R, 7603/R, 7613/R, 7623/R, 7623A/R, and 7633/R. Order by Tektronix part number 016-0637-00.

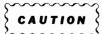

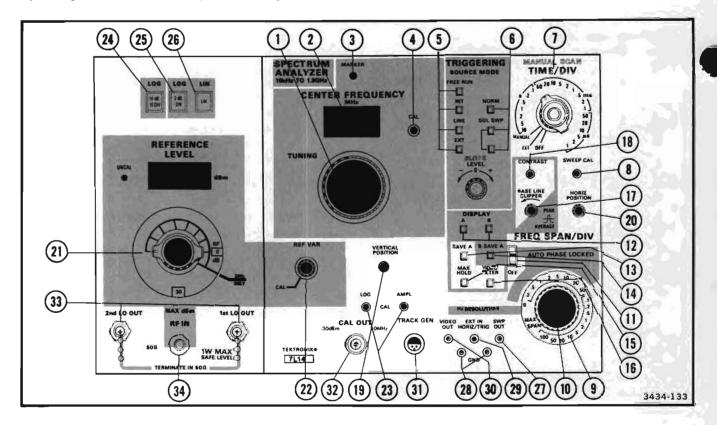

Fig. 2-1. Front-panel controls.

# CONTROLS, INDICATORS, AND CONNECTORS

The following describes the function of the controls, indicators, and connectors on the front panel of the 7L14. Figure 2-1 illustrates their location.

- 1) TUNING. The center frequency is tuned with this onespeed control. The tuning range is decreased to +50 kHz when the FREQ SPAN/DIV is 50 kHz or less and the AUTO PHASE LOCKED switch is on.

- 2 CENTER FREQUENCY. The center frequency or marker frequency is indicated by the LED readout.

- 3 MARKER. This indicator lights when the FREQ SPAN/DIV is at the MAX SPAN position. A notch on the baseline of the display indicates the center portion of the span that will be displayed when the FREQ SPAN/DIV is reduced.

- (4) CAL. The frequency readout can be calibrated to center frequency by adjusting the TUNING control for the correct reading.

(5) TRIGGERING SOURCE. One of four triggering sources can be selected.

FREE RUN. The sweep is free running without regard to trigger signals.

INT. Uses the displayed signal as a trigger source. The signal is ac coupled with an approximate frequency range from 15 Hz to 1 MHz.

LINE. The trigger signal source is a sample of the ac power line. Line signals are dc coupled to the triggering circuits.

**EXT.** Selects the signal that is applied to the EXT IN/HORIZ TRIG connector. External signals are dc coupled to the triggering circuits. Maximum signal input to the external input connector should not exceed 40 V (dc + ac peak) for triggering. Input impedance for the external input is about 30 k ohm.

2-2 REV MAY 1984

6 TRIGGERING MODE. One of two triggering modes can be selected.

NORM. The sweep will automatically recur at the end of holdoff time, if a trigger signal is absent. This feature provides a baseline on the display. In this mode triggering occurs at the slope and level selected by the SLOPE/LEVEL controls unless the triggering signal is below the required amplitude, or beyond the frequency limits of the circuit. Minimum signal amplitude for internal triggering is 0.5 division of signal for external triggering.

In the **SGL SWP** mode, the sweep is triggered by pushing the adjoining button. This button lights during sweep time and serves as an indicator to determine camera shutter time when photographing slow-scan time displays. Minimum signal amplitude for triggering is 0.5 division of signal and 0.5 V of external signal.

(7) TIME/DIV and MANUAL SCAN. Three sweep modes and an OFF state are provided.

TIME/DIV is calibrated in a 1, 2, 5 sequence from 10 S/Div to 1  $\mu$ s/Div. This control selects the sweep rates and the MANUAL, EXT and OFF modes.

In the OFF position, the crt beam is horizontally centered and the analyzer becomes a tuned receiver to the frequency indicated by the readout.

The EXT position connects any signal applied to the EXT IN/HORIZ TRIG connector to the horizontal deflection circuits of the 7L14. External sweep voltage (0 V to 10 V) signal can be used to slave the 7L14 to an external device, such as a recorder.

The MANUAL position connects the sweep circuits of the 7L14 to the MANUAL SCAN control, so the crt beam deflection can be manually controlled.

- **8 SWEEP CAL.** This adjustment compensates for differences in deflection sensitivities between oscilloscopes.

- 9 FREQ SPAN/DIV. This control sets the horizontal frequency calibration on the crt. The calibrated range of the selector is 100 MHz/Div to 200 Hz/Div in a 1, 2, 5 sequence. A MAX span position provides approximately 1.8 GHz of spectrum and a 0 Hz position converts the analyzer to a fixed tuned receiver for time-domain displays. Time analysis of the signal characteristics, within the bandwidth capabilities selected with the RESOLUTION control, can then be performed. In this case, Time/Div is read out on the crt instead of Span/Div.

- (10) RESOLUTION. This control allows the operator to analyze discrete frequency components within a frequency span. The calibrated range (within 20%) is 30 Hz to 3 MHz in decade steps. The RESOLUTION control can be coupled to the FREQ SPAN/DIV control when the knobs align with indicating marks. A concentric sleeve labeled PULL TO UNLOCK will uncouple the two selectors when it is pulled out and allow independent settings of each control.

- able the phase lock for some applications, such as tuning the analyzer more than 1 MHz when the instrument is used as a tuned receiver (0 span).

- (12) DISPLAY A, DISPLAY B. Without either of the pushbuttons activated, the 7L14 display is stored, but not displayed. When either or both these pushbuttons are selected, the contents of memory A and/or memory B are displayed. With SAVE A memory off, all memory locations are displayed and updated continuously. Data in A memory is interlaced with data from B memory.

- (13) SAVE A. When activated, this mode holds data in A memory and inhibits further updating. With SAVE A and VIEW A active, data in A memory is displayed but not updated, serving as a reference to compare contents of B memory.

- (14) B-SAVE A. When this button is activated, the contents of memory B minus the contents saved in memory A are displayed. This permits a comparison between two displays. The SAVE A function is also in effect.

- ory retains the maximum signal amplitude at each memory location. This permits visual monitoring of signal frequency and amplitude at each memory location over an indefinite period of time. This feature is used to measure drift, stability, and record peak amplitudes.

- (16) VIDEO FILTER. When the VIDEO FILTER button is pushed, one of three filters (10 Hz, 300 Hz or 30 kHz) is selected depending on the Resolution Bandwidth setting. The bandwidth of the filter selected is displayed on the crt. Video filters restrict the video bandwidth and reduce high frequency components for display noise averaging.

- (17) BASELINE CLIPPER-PEAK AVERAGE. When the digital storage is off, this control operates as a baseline clipper (i.e. as the control is rotated counterclockwise, more of the vertical display is progressively

REV MAY 1984 2-3

#### Operating Instructions—7L14 Spectrum Analyzer

clipped, or blanked). When the digital storage is on, the control sets the level at which the vertical display is either peak detected or averaged. Video signals above the level set by the control (shown by the horizontal cursor) are peak-detected and stored; video signals below the cursor are averaged and stored.

- (18) CONTRAST. When the digital storage is off, this control adjusts the brightness ratio between the blanked and unblanked portion of the display. Overall display intensity is set by the oscilloscope Intensity control. When digital storage is on, this control adjusts the intensity of the cursor. This feature is especially helpful for use with a digital processing oscilloscope or a 7854 oscilloscope.

- (19) **VERTICAL POSITION.** This control positions the display vertically.

- (20) HORIZONTAL POSITION. This control positions the display horizontally.

- 21) REFERENCE LEVEL. (Reference and IF Gain). These concentric controls select input attenuation to the input mixer, and the IF gain. The readout windows indicate REFERENCE LEVEL in dBm, of the full scale display, MAXimum signal input level (in dBm) for linear operation, and the input RF attenuation (from 0 to 60 dB).