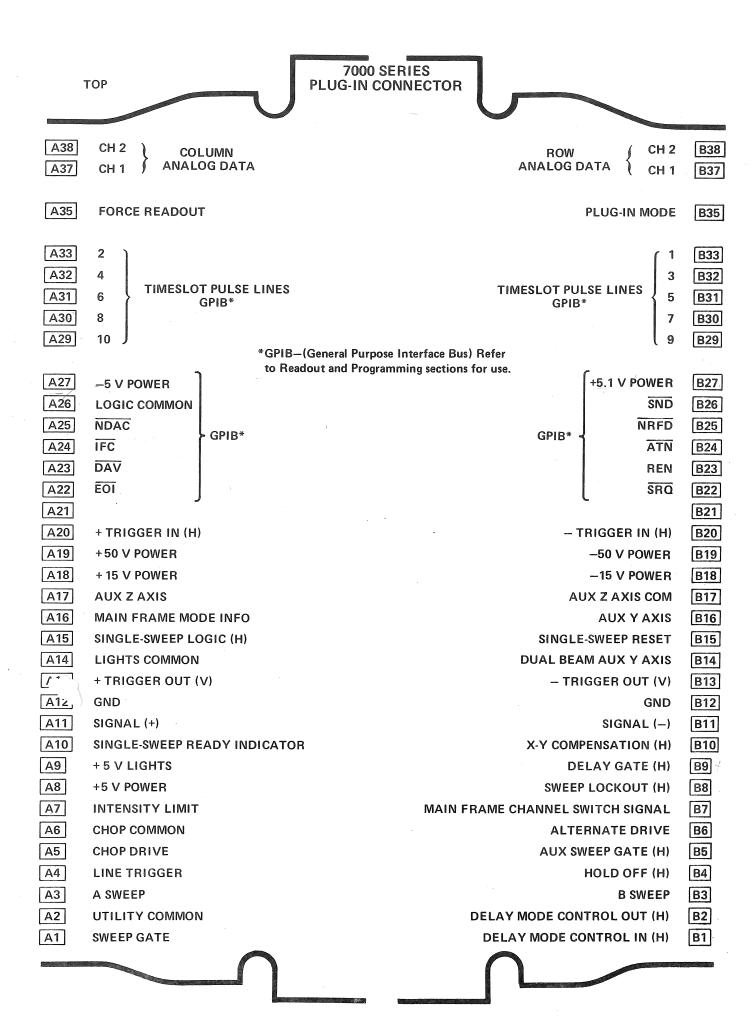

# 7000-SERIES PLUG-IN/MAINFRAME INTERFACE MANUAL

(An Engineering Guideline)

COMPANY

SPECIFICATION 704 March 1976

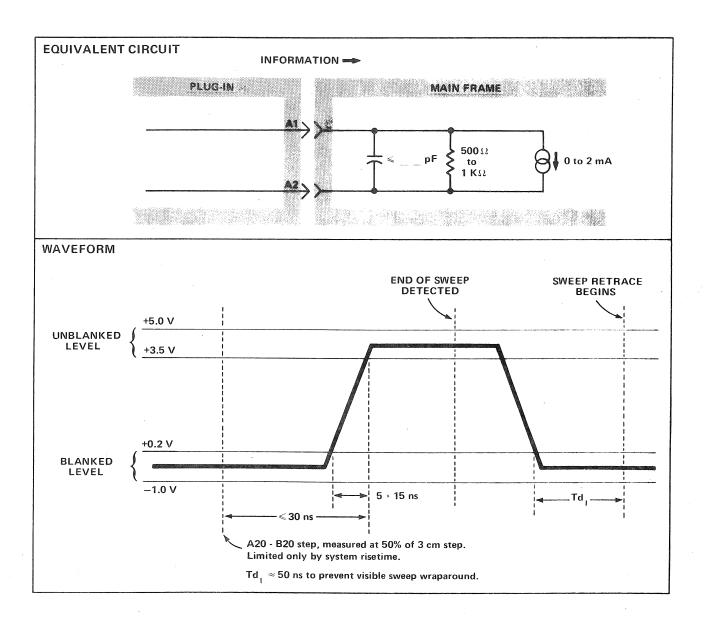

## **SWEEP GATE**

Sweep Gate, A1, is generated by the plug-in and used by the Main Frame to generate crt unblanking signals. The gate signal is required in all horizontal plug-in compartments.

## **Special Considerations:**

- 1. When the time-base plug-in Lockout (B8) is in the HI state, A1 should be in the LO state.

- 2. Plug-ins that do not generate a gate should connect A1 to A8 (+5 V) to unblank the crt when the plug in is used in the horizontal compartments.

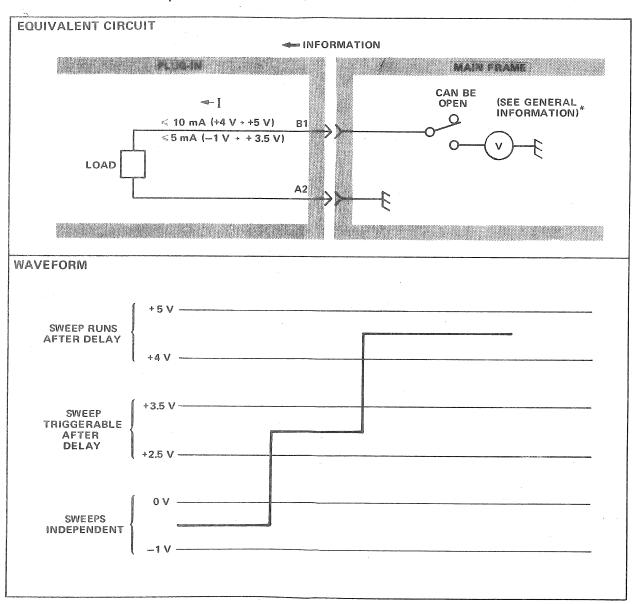

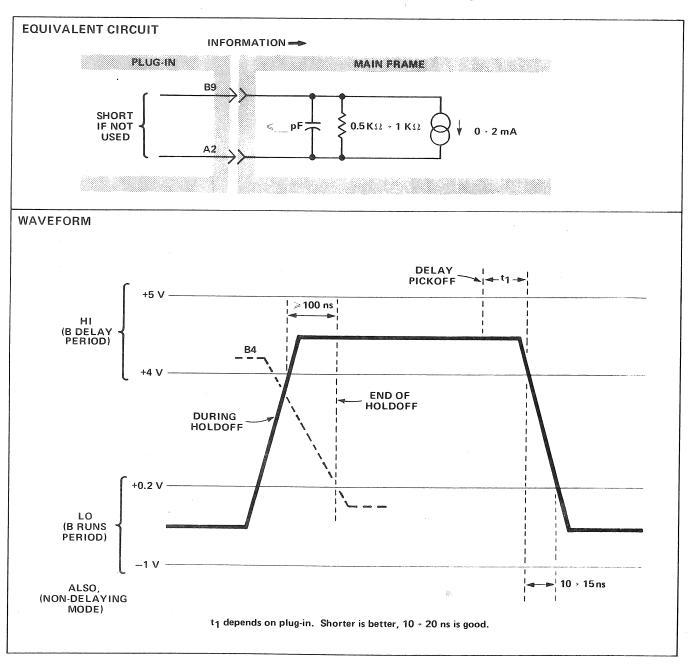

#### DELAY MODE CONTROL IN

Delay Mode Control In, B1, is used by the delayed sweep plug-in with the Delay Gate, B9, to produce delayed sweep operation. B1, Delay Mode Control In, is used only in four-hole Main Frames. In three-hole Main Frames, this line is open.

\* Typically, information goes into Main Frame A Horizontal, B2, through the Main Frame and out on B Horizontal, B1, to another plug-in.

For additional details on main frame switching, refer to section on Logic.

NOTE: A 7A22 unit short circuits B1 (B2) to ground. Instrument damage will occur under the following conditions: 7A22 installed in the B horizontal compartment; a 7B71, 7B51, or 7B85 installed in the A horizontal compartment and set for the "runs after delay time" mode.

\* mod M30219 cuts B1 on 7A22-067-0589-01

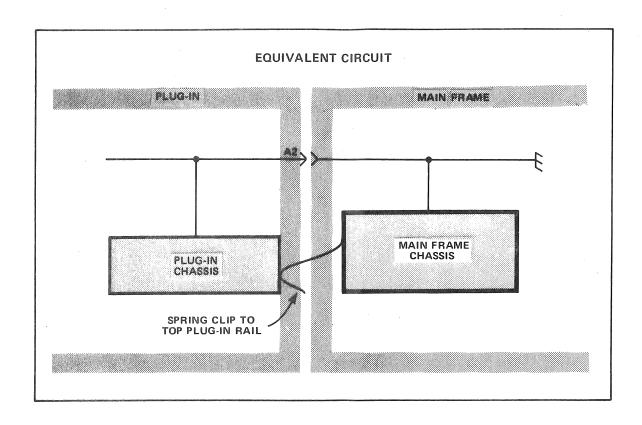

#### UTILITY COMMON

Utility Common, A2, was originally intended to be used exclusively as a ground return for the following pins: (A1) Sweep Gate; (B9) Delay Gate; (B8) Sweep Lockout; (B5) Auxiliary Sweep Gate; and (B4) Holdoff. It was not intended to be connected to the plug-in chassis. However, this was found to be unworkable and optimum performance was obtained when A2 was connected to the plug-in chassis ground.

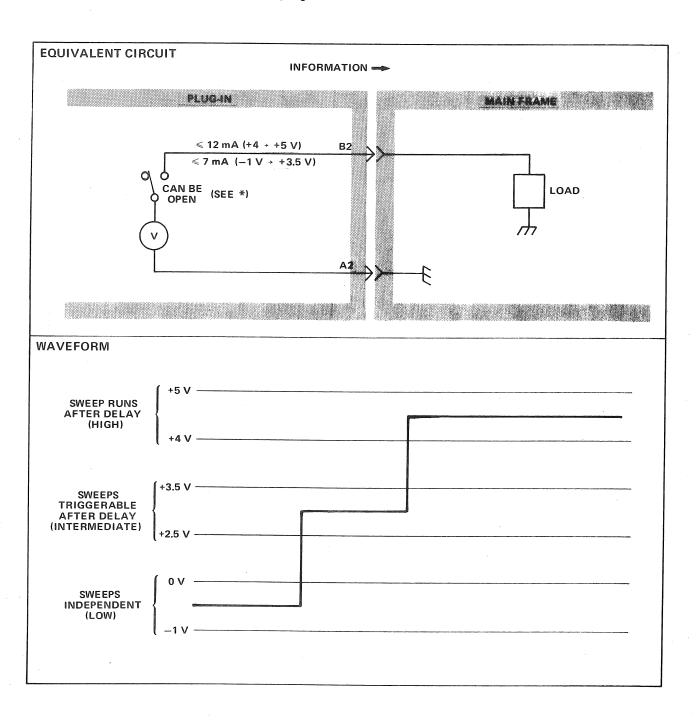

## **DELAY MODE CONTROL OUT**

Delay Mode Control Out, B2, is generated by the delaying sweep plug-in. This information is used by the Main Frame and the delayed sweep plug-in when the delaying sweep plug-in is in the A Horizontal compartment. This signal is connected to B1 in the B Horizontal compartment.

Delay Mode Control Out, B2, is used only in four-hole Main Frames. In three-hole Main Frames, this pin is open.

\*Typically, information goes into the Main Frame A Horizontal, B2, through the Main Frame and out on B Horizontal, B1, to another plug-in.

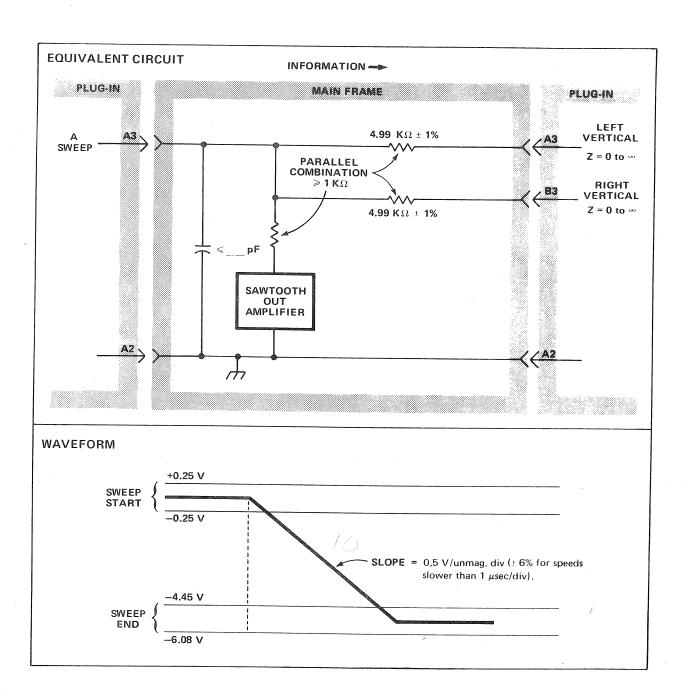

## A SWEEP

A Sweep, A3, from "A" time-base plug-in supplies a negative-going sawtooth to the right and left vertical plug-in compartments and the Sawtooth Out amplifier.

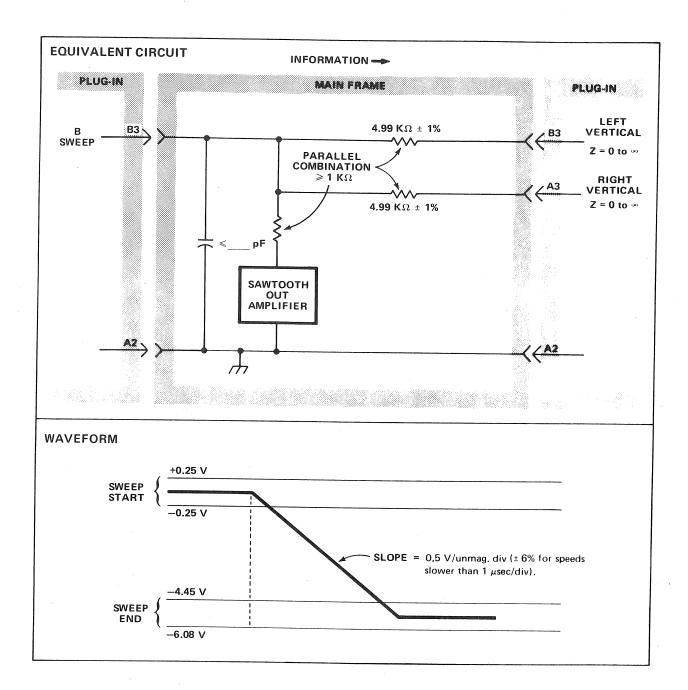

## **B SWEEP**

B Sweep, B3, is from time-base plug-ins. It supplies a negative-going sawtooth to the right and left vertical plug-in compartments and also to the sawtooth-out amplifier.

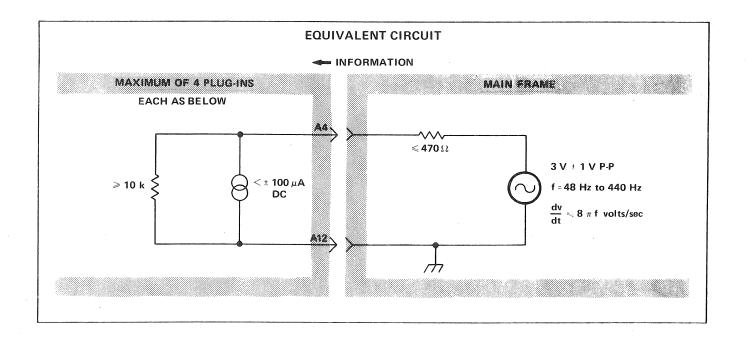

# LINE TRIGGER

Line Trigger A4 supplies a line trigger signal to the plug-ins.

# Main Frame Considerations:

Phasing

A4 will be positive going when "hot" line conductor

is positive going.

Maximum Noise

25 mV RMS (tangentially measured) 20 Hz to 1 KHz.

Power Line Isolation

2 kV RMS @ 60 Hz for 1 minute.

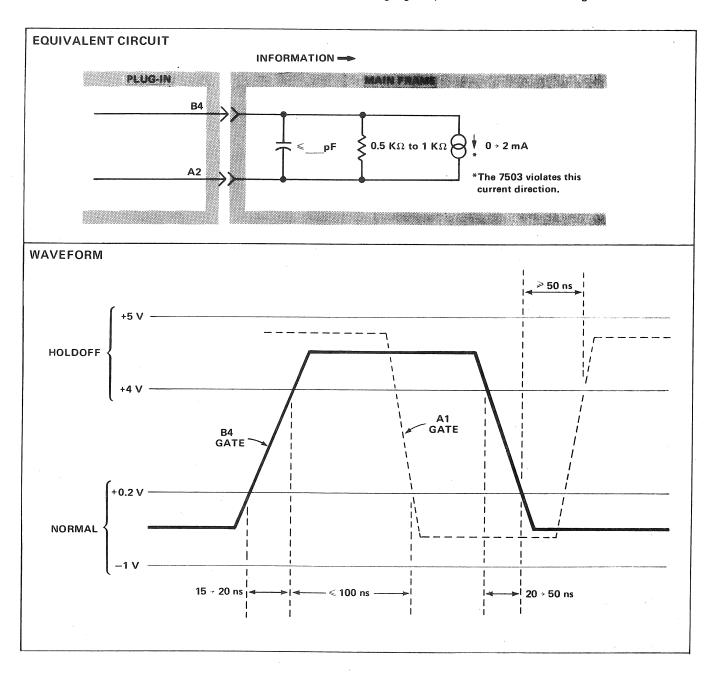

## **HOLDOFF**

Holdoff, B4, is generated by the time-base plug-in and used by the Main Frame to derive switching information. Holdoff time is a function of the plug-in Time/Div setting.

For additional details on Main Frame Channel Switching signals, refer to Section on Logic.

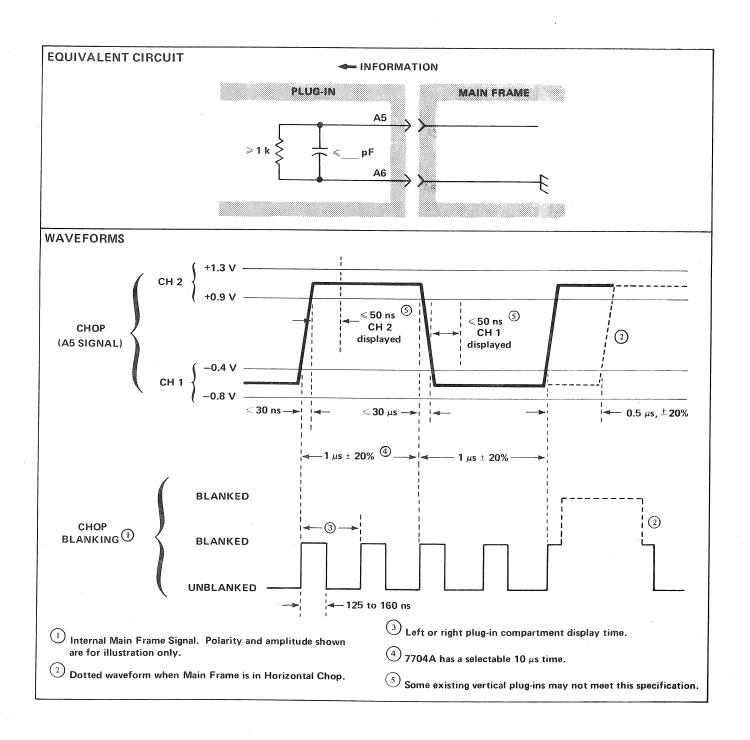

#### **CHOP DRIVE**

Chop Drive, A5, is generated by the Main Frame and used by dual-channel plug-ins to switch between Channel 1 and Channel 2 when the plug-in is in the Chop mode. The Chop Drive signal is always present.

# **General Information:**

For additional details on Main Frame Switching, refer to section on Logic.

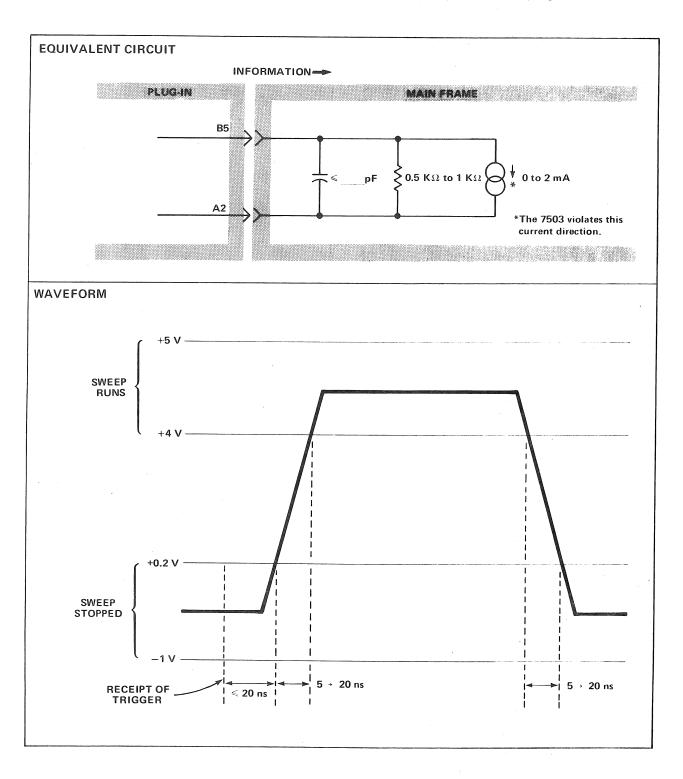

## **AUXILIARY SWEEP GATE**

Auxiliary Sweep Gate, B5, is generated only by dual-sweep plug-ins. Usages are Gate Signal Out and Main Frame processing. It is not intended to be used as an unblanking signal.

See Miscellaneous Section—7000 Series Gate Nomenclature, for explanation of plug-in differences.

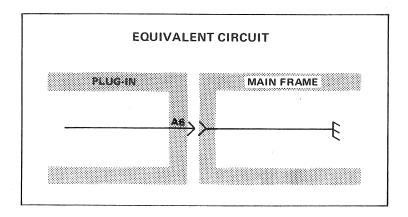

## **CHOP COMMON**

Chop Common, A6, is used to return to the Main Frame any current drawn from A5 (Chop Drive), B6 (Alternate Drive), and B7 (Main Frame Channel Switch signal). This line is grounded in the Main Frame and should not connect to ground in the plug-in unit.

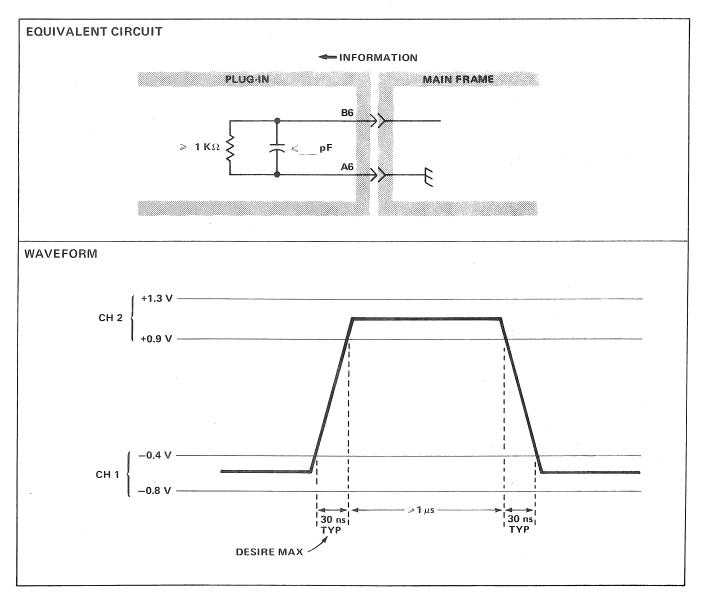

## **ALTERNATE DRIVE**

Alternate Drive, B6, is derived from horizontal plug-in or Main Frame information and used primarily by dual-channel plug-ins in the Alternate mode, to switch between channels.

## **General Information:**

In a 4-hole Main Frame, CH 1 of a dual-channel plug-in is slaved to B Sweep and CH 2 is slaved to A Sweep during the following conditions:

- (1) Main Frame horizontal is in ALT or CHOP.

- (2) Main Frame vertical is NOT in ALT. ( )ease Left, Right, Chop)

- (3) A Sweep is NOT in Delaying mode.

In a 3-hole Main Frame, vertical plug-ins are not slaved to the horizontal plug-in compartment.

For additional details of the Alternate Function, refer to the section on Logic.

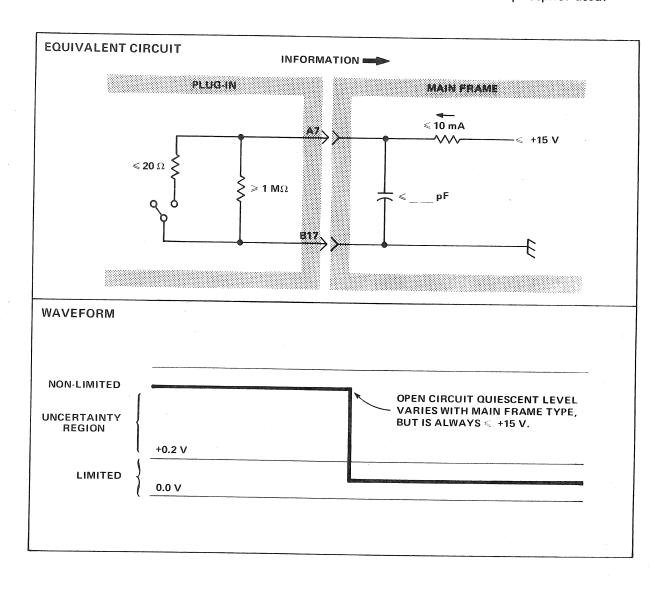

## INTENSITY LIMIT

Intensity Limit, A7, is used to reduce the possibility of burning the crt. Any time base sweep speed of 0.1 sec/div or slower will reduce the intensity to the limited value regardless of other time-base sweep speeds. The level of maximum intensity in the limited case is set by the Main Frame. For intensities below the limiting value, the intensity will not change when A7 is grounded.

## **General Information:**

To assure optimum protection, the limit value should be set for the crt phosphor used.

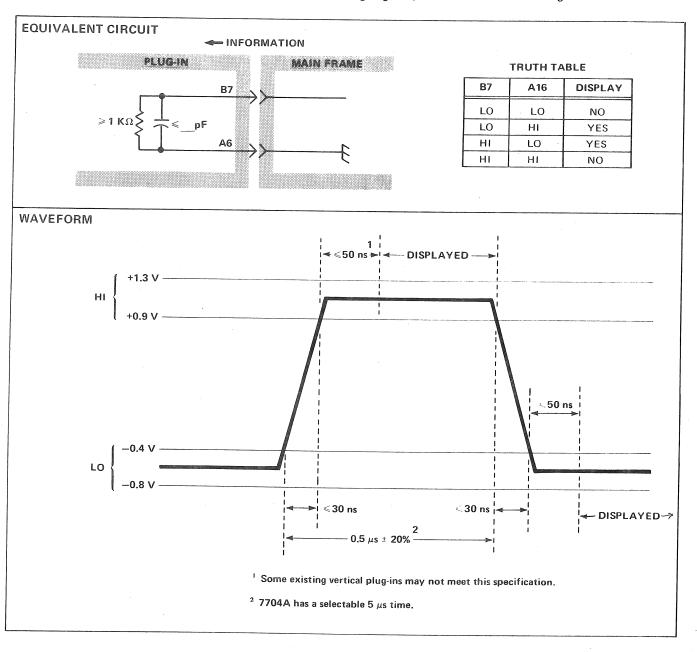

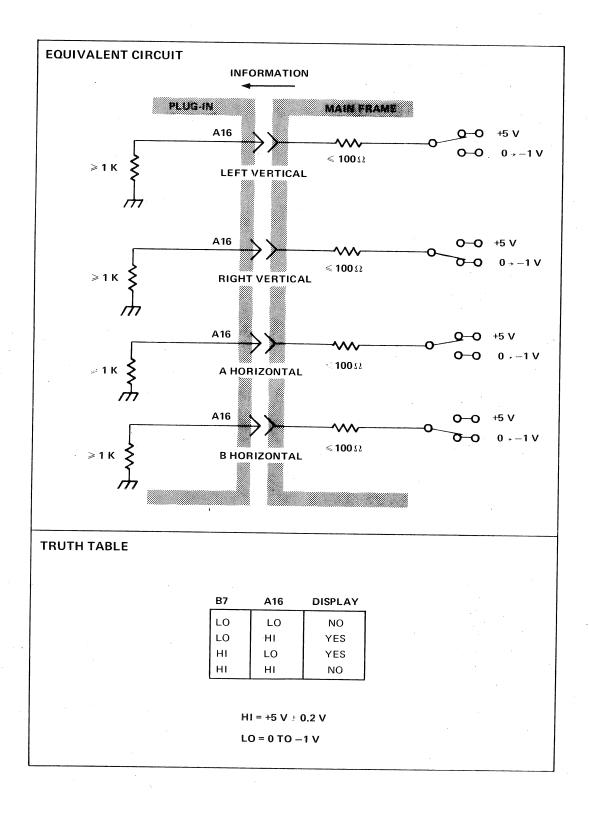

## MAIN FRAME CHANNEL SWITCH SIGNAL

Main Frame Channel Switch Signal, B7 (with A16), is used by the plug-ins to determine when they are being displayed. This information is necessary when the Aux Z and/or Aux Y Axis are/is being used. This insures that only the displayed plug-in is controlling the Z and/or Y Axis. The Main Frame Delay Line's Time Delay must be considered when using these signals.

For additional details of Main Frame Channel Switching Signals, refer to section on Logic.

## +5 V POWER

$\pm 5$  V Power, A8, will provide up to 500 mA to each plug-in compartment. Each plug-in is limited to 16.5 W total power consumption.

# **General Information:**

Refer to section on Power Supplies for information concerning power supply parameters.

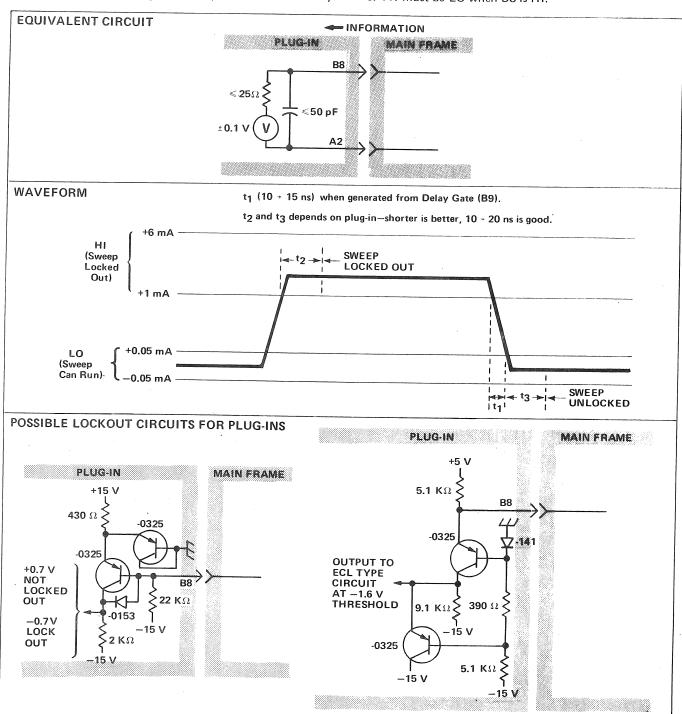

## **SWEEP LOCKOUT**

Sweep Lockout, B8, is derived from the time-base plug-in Delay Gate B9 or from main frame commands. This information is used to control when a sweep may operate.

B1 determines what the time base plug-in does when B8 goes to its LO state.

## **Special Considerations:**

- 1. If B8 goes to the HI state when the sweep is running, the sweep must reset and perform its holdoff cycle.

- 2. The fast fall rate is necessary to assure proper time base plug-in sequencing. However, some commands may

be much slower if sequencing is not of importance (i.e., storage commands).

3. A1 must be LO when B8 is H1.

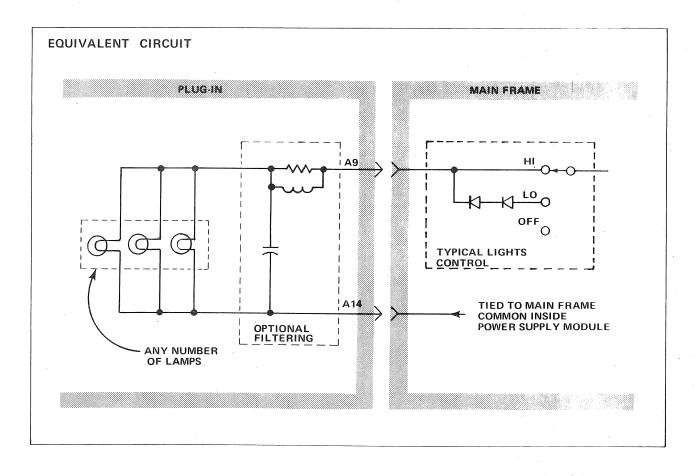

#### +5 V LIGHTS

+5 V Lights, A9, will provide up to 500 mA (previously 750 mA) to each plug-in compartment.

Each plug-in is limited to 16.5 W total power consumption.

## General Information:

Refer to section on Power Supplies for information concerning power supply parameters.

Main Frames generally provide +5 V lights and control switching: HI (+5 V), LO (  $\approx$  +3.5 V), and OFF. The 7300, 7400, and 7600 Series do not provide +5 V Lights except as a conversion kit (040-0686-00).

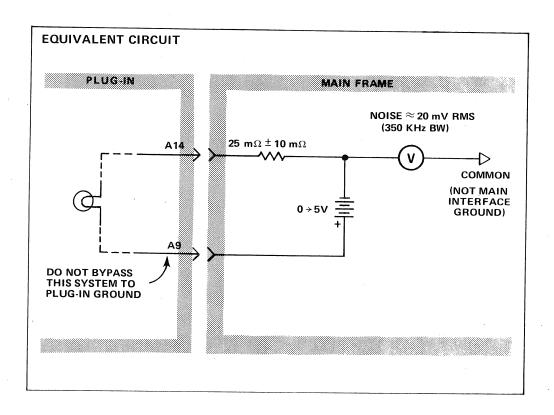

## Special Considerations:

- 1. When lights are used close to high sensitivity circuitry, i.e., vertical plug-in inputs, additional +5 V Lights filtering may be required.

- 2. A9, +5 V Lights, shall only be returned to A14.

#### **DELAY GATE**

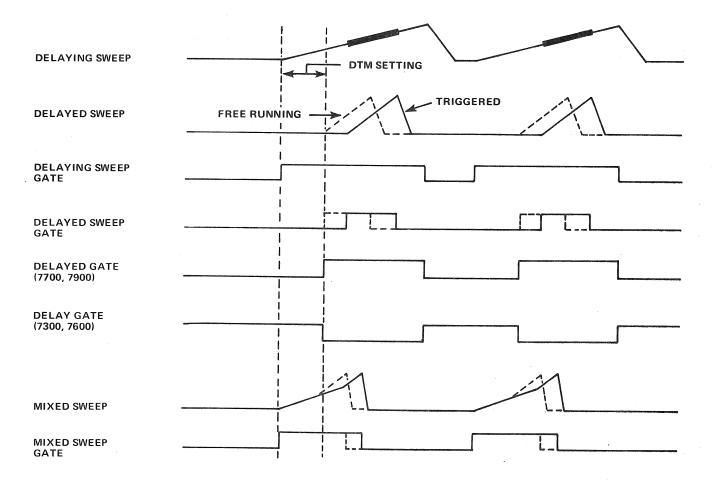

Delay Gate, B9, is generated by delaying sweep plug-ins (except dual-sweep plug-ins) when used in the Delaying mode. The Delaying mode is only usable when the Delayed Gate is generated by a sweep plug-in in the A compartment (B9 [A] drives B8 [B]). In some Main Frames, B9 information is used to generate Gate Out signals.

## **Special Considerations:**

- 1. Following B9 transition from high to low, the sweep plug-in should run or be triggerable. The sweep must run only **ONCE** per B9 high to low transition.

- 2. B9 must stay low, if B2 is low.

B2 determines what the B compartment time-base plug-in does when B9 goes to its LO state.

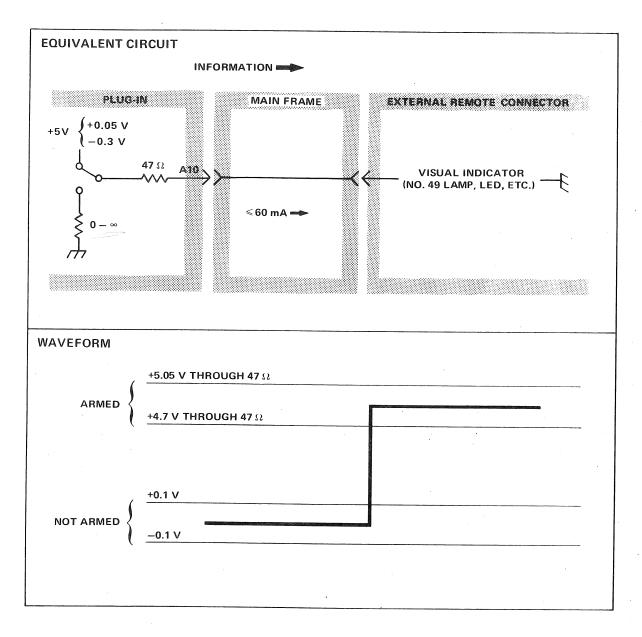

## SINGLE SWEEP READY INDICATOR

Single Sweep Ready Indicator, A10, is used to determine if a sweep is armed when in the Single Sweep mode.

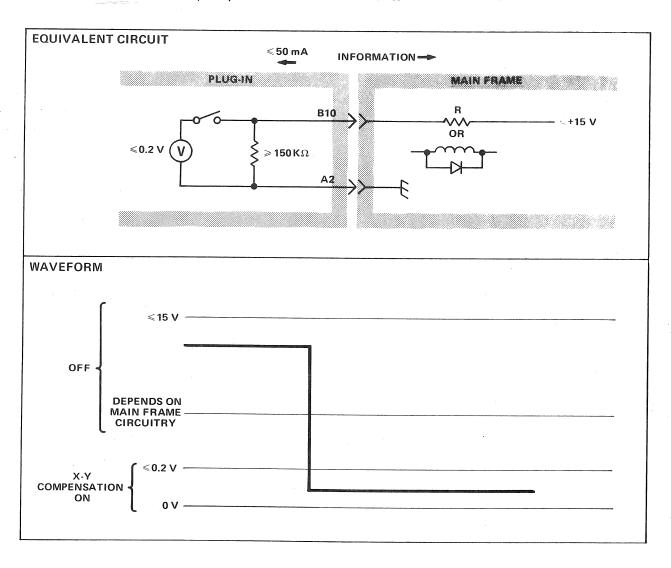

## X-Y COMPENSATION

X-Y Compensation, B10, supplies the Main Frame with information to identify the presence of an amplifier plug-in (or sweep plug-in in Amplifier mode) in a horizontal plug-in compartment. This information can be used to switch in Horizontal signal path X-Y Compensation, Horizontal Alternate mode LOGIC and any other necessary control functions.

\*Beware of 7B51 and 7T11, they connect B10 to +15 volts.

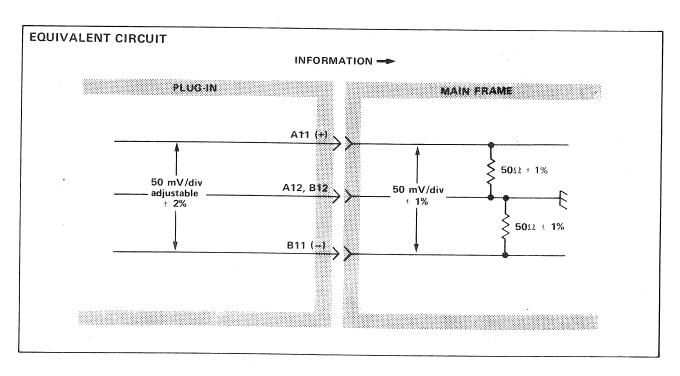

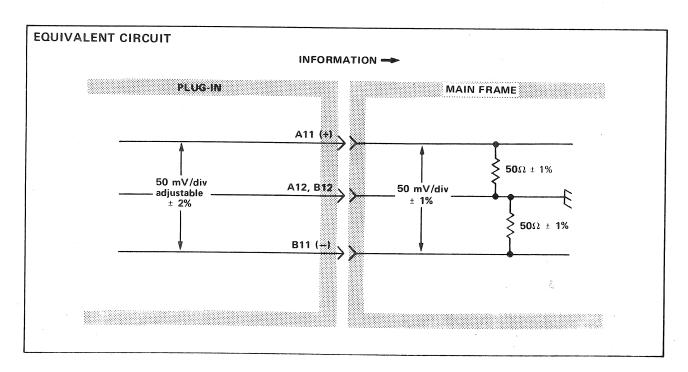

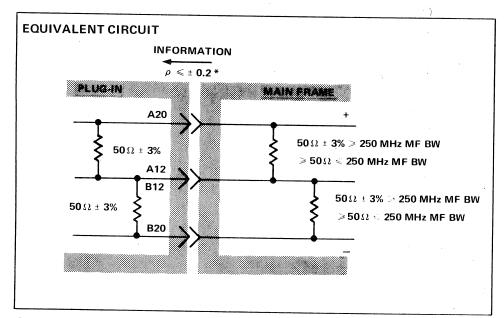

## SIGNAL +

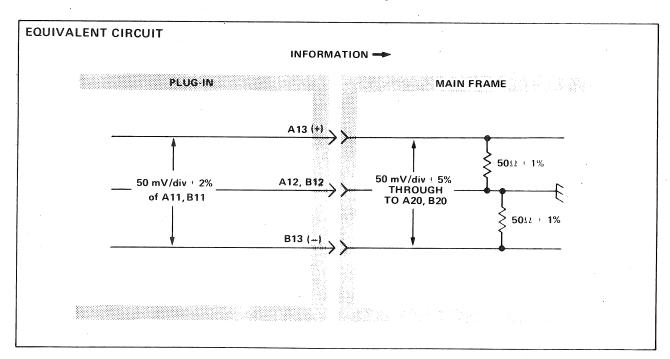

Signal +, A11, provides signal input to the Main Frame. Positive signal on A11 deflects the trace up in the vertical compartments and to the right in the horizontal compartment(s).

# **DC** Considerations:

| Deflection Factor                              | 50 mV/div ± 1% differential        |

|------------------------------------------------|------------------------------------|

| Input R                                        |                                    |

| A11 to A12, B12                                | 50 Ω ± 1%                          |

| B11 to A12, B12                                | 50 Ω ± 1%                          |

| A11 to B11                                     | 100 Ω ± 1%                         |

| A11 shorted to B11 to A12, B12                 | 25 Ω ± 10%                         |

| Usable Signal Limits (all AC & DC specs apply) | ± 9 divisions                      |

| Maximum Signal Limits                          | ± 15 divisions                     |

| DC Centering                                   | ± 0.5 division of graticule center |

| Maximum Input DC Common<br>Mode Component      | 150 mV or less                     |

# **AC Considerations:**

| O.35 ÷ 1.5 x Main Frame bandwidth]  | 2% ≤ 250 MHz<br>10% ≥ 250 MHz          |

|-------------------------------------|----------------------------------------|

| CMRR to BW (for full screen signal) | ≥ 100:1 ≤ 250 MHz<br>≥ 50:1 > 250 MHz* |

<sup>\*</sup> Plug-in should be back-terminated.

Signal —, B11, provides signal input to the Main Frame. Negative signal on B11 deflects the trace up in the vertical compartments and to the right in the horizontal compartment(s).

# **DC** Considerations:

| Deflection Factor                              | 50 mV/div ± 1% differential        |

|------------------------------------------------|------------------------------------|

| Input R                                        |                                    |

| A11 to A12, B12                                | 50 Ω ± 1%                          |

| B11 to A12, B12                                | 50 Ω ± 1%                          |

| A11 to B11                                     | 100 Ω ± 1%                         |

| A11 shorted to B11 to A12, B12                 | 25 Ω ± 10%                         |

| Usable Signal Limits (all AC & DC specs apply) | ± 9 divisions                      |

| Maximum Signal Limits                          | ± 15 divisions                     |

| DC Centering                                   | ± 0.5 division of graticule center |

| Maximum Input DC Common<br>Mode Component      | 150 mV or less                     |

## **AC Considerations:**

| TDR (push-pull) [ $t_r$ equivalent to .35 $\pm$ 1.5 $\times$ Main Frame bandwidth] | 2% ≤ 250 MHz<br>10% ≥ 250 MHz          |

|------------------------------------------------------------------------------------|----------------------------------------|

| CMRR to BW (for full screen signal)                                                | ≥ 100:1 ≤ 250 MHz<br>≥ 50:1 ≥ 250 MHz* |

<sup>\*</sup> Plug-in should be back-terminated.

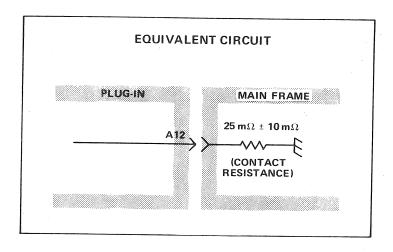

## **GROUND**

Ground, A12, provides ground reference for A11 and A13. In addition, it is used as the plug-in power supply reference and return.

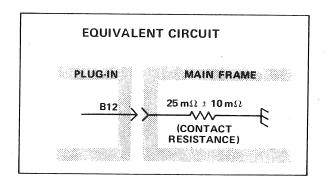

# **GROUND**

Ground, B12, provides ground reference for B11 and B13. In addition, it is used as the plug-in power supply reference and return.

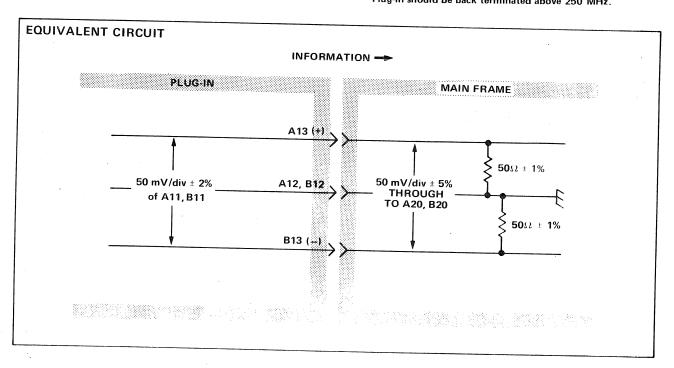

## + TRIGGER OUT (V)

+ Trigger Out (V), A13, (differentially with B13) trigger input to the Main Frame. This trigger information is processed by the main frame and presented to the Horizontal MFI on pins A20 and B20. Positive-going trigger signal on A13 corresponds to a positive-going A11.

## DC Considerations

| MAIN FRAME | (THROUGHPUT | TO A20, | B20) |

|------------|-------------|---------|------|

|            |             |         |      |

**Deflection Factor**

50 mV/displayed signal division ± 5%.

Input R

A13 to A12, B12

50  $\Omega$  ± 1%.

B13 to A12, B12

$50\Omega \pm 1\%$

A13 to B13 A13 shorted to B13

$100 \Omega \pm 1\%$ .

to A12, B12

25  $\Omega$  ± 10%.

Usable Signal Limits

± 9 divisions (all ac & dc

specifications apply)

Maximum Signal Limits

± 15 divisions.

Centering

± 0.20 division from

A11, B11.

Maximum Input DC Common Mode Component

150 mV or less.

#### PLUG-IN

Deflection Factor

Within 2% of A11, B11

(50 mV/div).

Output R

See ac considerations.

Usable Signal Limits

± 9 divisions referred to A11, B11 (all ac and dc

specifications apply)

#### PLUG-IN (cont.)

Maximum Signal Limits

± 15 divisions.

Centering

± 0.2 division from A11,

B11.

Maximum Input Common

Mode Component

150 mV or less.

Variable Volts/Div

Varies with signal channel.

Invert

Inverts with signal channel.

#### AC Considerations

# MAIN FRAME (THROUGHPUT TO A20, B20)

TDR (push-pull) (tr equal

2% ≤ 250 MH<sub>2</sub>

to  $0.35 \div 1.5 \times BW$ )

10% ≥ 250 MHz.

CMRR to BW (for full

$\geq 100:1 \leq 250 \text{ MHz}.$

screen signal.

≥ 50:1 ≥ 250 MHz, '

Risetime ≤ displayed signal risetime

(on screen).

Bandwidth

≥ displayed signal band-

width (on screen).

Aberrations

+5%, -5% or less. Total

5% peak-to-peak or less,

#### PLUG-IN

Aberrations

+5%, -5% or less. Total 5% peak-to-peak or less.

\* Plug-in should be back terminated above 250 MHz.

## - TRIGGER OUT (V)

- Trigger Out (V), B13, trigger input to the Main Frame. This trigger information is processed by the main frame and presented to the Horizontal MFI on pins A20 and B20. Positive-going trigger signal on B13 corresponds to a negative-going B11.

## **DC** Considerations

## MAIN FRAME (THROUGHPUT TO A20, B20)

Deflection Factor

50 mV/displayed signal

± 9 divisions (all ac & dc specifications apply)

division ± 5%.

$50 \Omega \pm 1\%$ .

$50\Omega \pm 1\%$ .

100  $\Omega$  ± 1%. 25  $\Omega$  ± 10%.

± 15 divisions.

± 0.20 division from

Input R

A13 to A12, B12

B13 to A12, B12

A13 to B13

A13 shorted to B13

to A12, B12

Usable Signal Limits

Maximum Signal Limits

Centering

Maximum Input DC Com-

mon Mode Component

## **PLUG-IN**

**Deflection Factor**

Output R

Usable Signal Limits

Within 2% of A11, B11

A11, B11. 150 mV or less.

(50 mV/div).

See ac considerations.

±9 divisions referred to A11, B11 (all ac and dc specifications apply)

#### PLUG-IN (cont.)

Maximum Signal Limits

± 15 divisions.

Centering

± 0.2 division from A11,

B11.

Maximum Input Common

Mode Component

Variable Volts/Div

Invert

150 mV or less.

Varies with signal channel.

Inverts with signal channel.

#### **AC Considerations**

## MAIN FRAME (THROUGHPUT TO A20, B20)

TDR (push-pull) (tr equal to to  $0.35 \div 1.5 \times BW$ )

CMRR to BW (for full

screen signal.

Risetime

$2\% \le 250 \text{ MHz}.$

10% ≥ 250 MHz.\*

$\geq 100:1 \leq 250 \text{ MHz}.$

≥ 50:1 ≥ 250 MHz.\*

≤ displayed signal risetime

(on screen).

Bandwidth

≥ displayed signal band-

width (on screen).

Aberrations

+5%, -5% or less. Total 5% peak-to-peak or less.

PLUG-IN

**Aberrations**

+5%, --5% or less. Total

5% peak-to-peak or less.

<sup>\*</sup> Plug-in should be back terminated above 250 MHz.

# **LIGHTS COMMON**

Lights Common, A14, provides a return path for A9. Typically, A9 ties to MF ground inside the power supply.

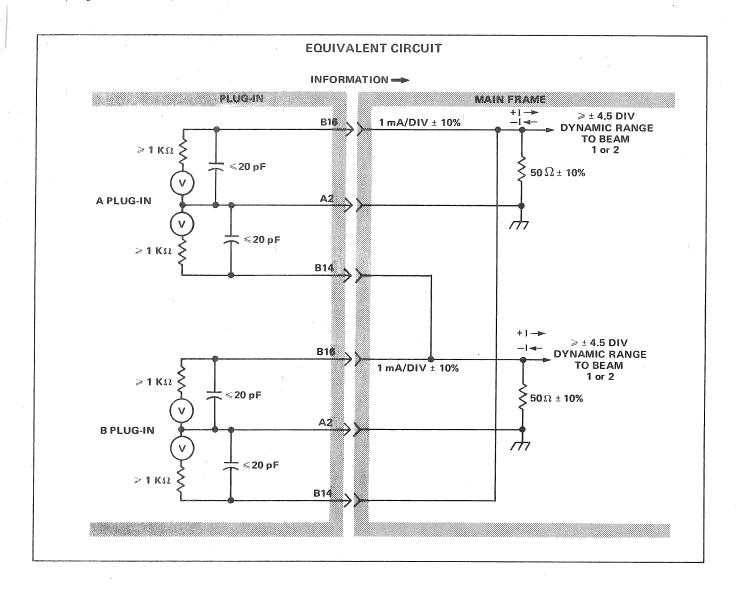

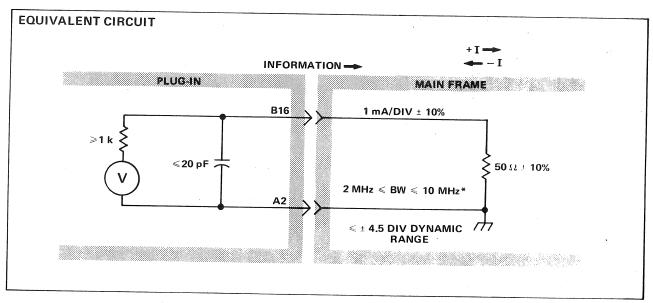

## **DUAL BEAM AUX Y AXIS**

Dual Beam Aux Y Axis, B14, is used for vertical trace separation in Dual Beam Main Frame Sweep Switching applications. The analog signal originates in the time-base plug-in and is added to the Vertical Amplifier signal in the Main Frame. The displayed signal is deflected up with +I and is deflected down with -I.

## **Special Considerations:**

The plug-in must obey A16 and B7.

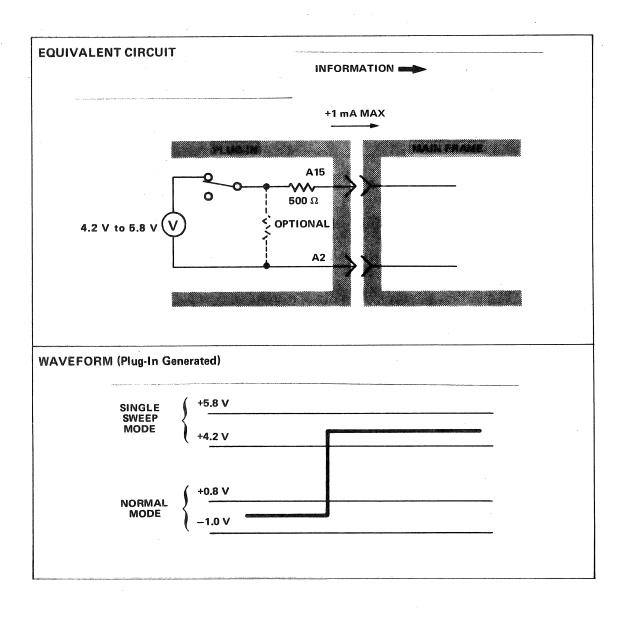

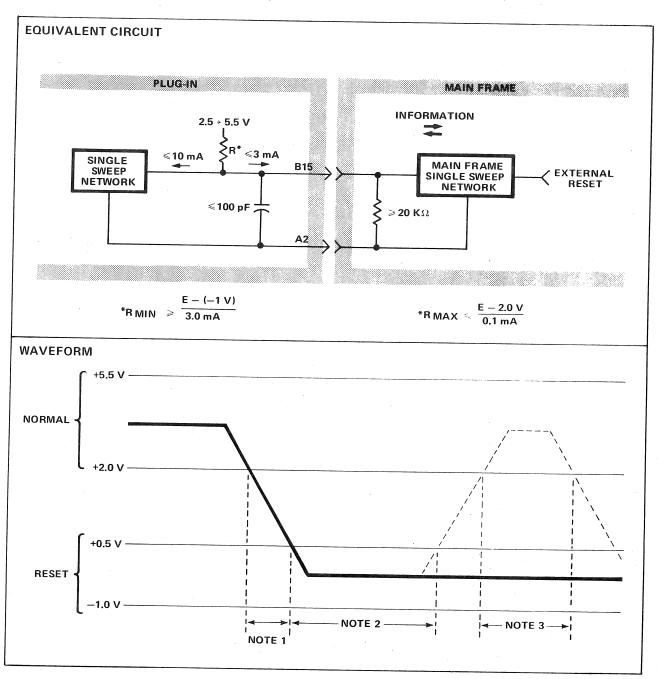

## SINGLE SWEEP LOGIC

Single Sweep Logic, A15, provides the Main Frame with logic information from the sweep plug-in(s), indicating when the plug-in(s) is/is not in single sweep mode.

**NOTE:** The 7B50, 7B51, 7B70, and 7B71 units do not meet this specification. They present a 4.7  $k\Omega$  series resistor when in the HI state.

## SINGLE SWEEP RESET

Single Sweep Reset, B15, is used to reset sweep plug-ins in the single-sweep mode. Some digital plugins use this pin as a strobe interrogation pulse.

#### NOTES

- 1. Falltime not critical (i.e., circuitry is DC coupled) except that digital plug-ins require fall times less than or equal to 100 ns.

- 2. The time for Reset is dependent on sweep plug-in state/ type.

- a. Sweep not running when reset received. Reset time  $\leqslant 400$  ns. (Typical sweep plug-in values 100-300 ns).

- b. Sweep running or lockout present when reset received. Some old sweep plug-ins will not recognize this condition, but new designs must. For those that will reset time; Total Sweep Time + Holdoff Time + Note 3 Time.

- c. When the 7D12/M2 is in  $\Delta$  sampling operation, the width of the Reset Pulse determines the time difference between strobing pulses.

- 3. Normal time following reset prior to next reset < 1 second. (Typical sweep plug-ins 1 ms to 800 ms.)

## MAIN FRAME MODE INFO

Main Frame Mode Info, A16 (with B7), is used by the plug-ins to determine when they are being displayed. This information is necessary when Aux Z (A17) and/or Aux Y (B16) is being used to insure that only the displayed plug-in is modifying the Z and/or Y axis signal.

### **AUX Y AXIS**

Aux Y Axis, B16, is used for vertical trace separation in Sweep Switching applications. The analog signal originates in the time-base plug-in and is added to the vertical amplifier signal in the Main Frame. The displayed signal is deflected up with  $\pm 1$  and is deflected down with  $\pm 1$ .

This pin was introduced after the 7704 and 7504. Hence, this pin is nto used in these instruments.

The plug-in must obey A16 and B7.

<sup>\* 7704</sup>A has greater than 10 MHz bandwidth, and causes problems with logic signals coupling into B16.

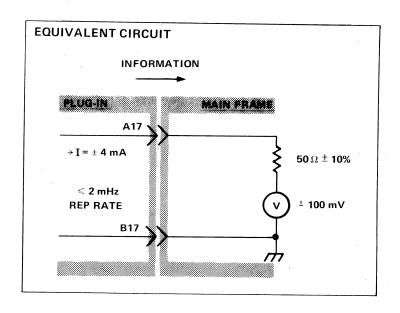

### **AUX Z AXIS**

Aux Z Axis, A17, is used by the plug-in to intensity modulate the crt. The Aux Z Axis will dim (+ I) or brighten (-I) the trace from the level set by the Main Frame INTENSITY control (i.e.,  $\approx$  +4 mA will extinguish a maximum intensity trace). A17 is used in conjunction with A16, A7, and B7.

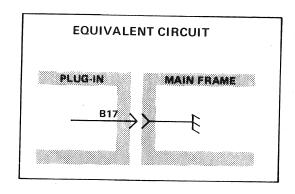

## **AUX Z AXIS COM**

Aux Z-Axis Com, B17, is used to return to the Main Frame any current drawn from Aux Z-Axis (A17). This line is grounded in the Main Frame and should not connect to ground in the plug-in.

### +15 V POWER

+15 V Power, A18, will provide up to 500 mA to each plug-in compartment.

Each plug-in is limited to 16.5 W total power consumption.

### **General Information:**

### -15 V POWER

$-15~\mathrm{V}$  Power, B18, will provide up to 500 mA to each plug-in compartment.

Each plug-in is limited to 16.5 W total power consumption.

## **General Information:**

### +50 V POWER

+50 V Power, A19, will provide up to 100 mA to each plug-in compartment.

Each plug-in is limited to 16.5 W total power consumption.

### **General Information:**

### -50 V POWER

$-50\ V$  Power, B19, will provide up to 100 mA to each plug-in compartment.

Each plug-in is limited to 16.5 W total power consumption.

## **General Information:**

## + TRIGGER IN (B20 = -A20)

+ Trigger In,A20,(with -Trigger In B20) provides a push-pull trigger signal to the horizontal plug-in. The trigger signal is positive going when the signal channel is positive going.

## Main Frame Considerations (Analog **Differential Signals)**

**Deflection Factor** Risetime

50 mV/displayed div  $\pm$  5%. ≤ to display channel.

**Aberrations**

$\leq \pm$  5%. Total  $\leq$  5% P-P for ≤ ± 5 div signals. Or 0.5 div P-P for signals  $> \pm 5$  div.

Bandwidth ≥ display channel.

Position with Respect to Display Channel

Within  $\pm$  0.5 div over  $\pm$  5 div of display channel positioning. Maximum Output Voltage

$\pm$  0.75 V for a total of 1.5 V differentially.

DC Common Mode Output Current to Plug-In

≤ 4 mA.

Common Mode Output

≤ 0.1 differential signal.

Signal

Maximum Common Mode

Current

≤ 4 mA.

Common Mode Output Resistance

$\geq 25\Omega$ .

$<sup>^*</sup>$  T<sub>r</sub> equivalent to 0.35  $\div$  1.5 x MF BW.

## - TRIGGER IN

See A20 information.

## + AUX TRIGGER IN

A21 was used as + Aux Trigger In. The 7B52 uses this pin, but no other plug-ins do. This pin will be left unused.

## - AUX TRIGGER IN

B21 was used as — Aux Trigger In. The 7B52 uses this pin—no other plug-ins do. This pin is now a spare.

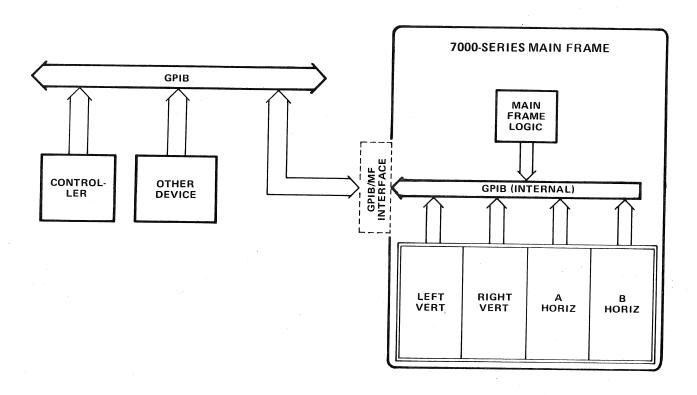

## EOI (End or Identify)

Bus management signal for programmable plug-ins. This is a TTL signal specified in IEEE standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                                                                        |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| A22        | EOI         | EOI (end or identify) is used to indicate the end of a multiple byte transfer sequence, or, in conjunction with ATN, to execute a polling sequence |

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in must be able to sink 24 mA at 0.4  $\rm V.$

## SRQ (Service Request)

Bus management signal for programmable plug-ins. This is a TTL signal specified in IEEE standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                                                                    |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| B22        | SRQ         | SRQ (service request) is used by a device to indicate the need for attention and to request an interruption of the current sequence of events. |

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in must be able to sink 24 mA at 0.4  $\rm V.$

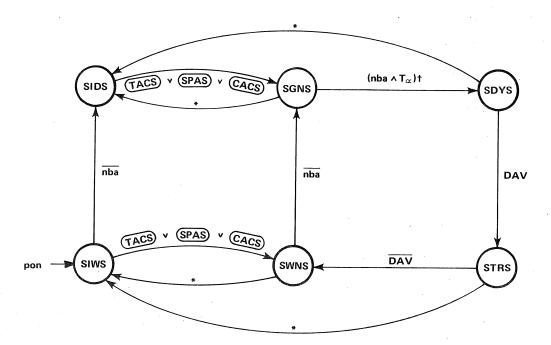

## DAV (Data Valid)

Handshake signal for programmable plug-ins. The function of this signal has been modified from Standard 488-1975. Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                                            |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| A23        | DAV         | DAV (data valid) is used to indicate the condition (availability and validity) of information on the DIO signal lines. |

A plug-in may place one standard TTL and one LSTTL input on the line.

Plug-ins may not drive this line.

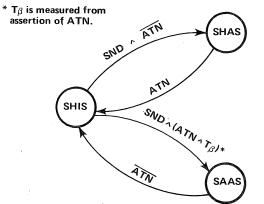

### **REN** (Remote Enable)

REN is a positive-true open collector TTL line.

REN (remote enable) used by the programmable main frame to enable or disable the local operation of the plug-ins.

The plug-ins respond to the RL (Remote Local) Interface function in the subset RL2. That is, the states LWLS (Local with Lockout State) and RWLS (Remote With Lockout State) are omitted. The main frame responds to the RL1 Interface Function requirements of the GPIB. Reference Table 23, IEEE Standard 488-1975.

The plug-ins must respond to a 1 microsecond pulse of REN =  $\emptyset$ , which occurs when the main frame rtl (return to local) button is pressed. The plug-ins respond to the RL2 subset, but in conjunction with the main frame, have full RL1 capability.

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in system controller must be able to sink 24 mA at  $0.4\ V_{\odot}$

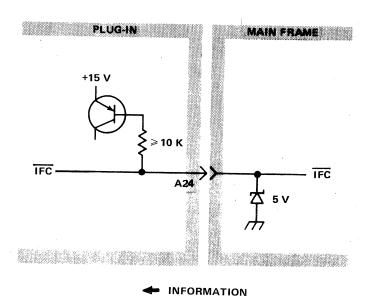

### **IFC** (Interface Clear)

Bus management signal for programmable plug-ins. This is a TTL signal specified in IEEE Standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                    |

|------------|-------------|--------------------------------------------------------------------------------|

| A24        | ĪFC         | IFC (interface clear) is used to place the interface system, portions of which |

|            |             | are contained in all interconnected devices, in a known quiescent state.       |

This line is also used by the Main Frame to indicate to the plug-ins that it is programmable. A non-programmable Main Frame makes no connection to A24.

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in system controller must be able to sink 24 mA at  $0.4\ V.$

## ATN (Attention)

Bus management signal for programmable plug-ins. This is a TTL signal specified in IEEE Standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                                                     |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| B24        | ATN         | ATN (attention) is used to specify how data on the DIO signal line is to be interpreted and which devices must respond to data. |

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in controller must be able to sink 24 mA at 0.4  $\rm V.$

## NDAC (Not Data Accepted)

Handshake signal for programmable plug-ins. This is a TTL signal specified in IEEE Standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                    |

|------------|-------------|------------------------------------------------------------------------------------------------|

| A25        | NDAC        | NDAC (not data accepted) is used to indicate the condition of acceptance of data by device(s). |

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in must be able to sink 24 mA at 0.4  $\rm V.$

## NRFD (Not Ready for Data)

Handshake signal for programmable plug-ins. This is a TTL signal specified in IEEE Standard 488-1975 and is part of the General Purpose Interface Bus (GPIB). Refer to the section on Programming for specifications.

| Pin Number | Signal Name | Description                                                                                           |

|------------|-------------|-------------------------------------------------------------------------------------------------------|

| B25        | NRFD        | NRFD (not ready for data) is used to indicate the condition of readiness of device(s) to accept data. |

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in must be able to sink 24 mA at 0.4  $\rm V_{\odot}$

## **LOGIC COMMON**

Provides a common ground return for logic signals.

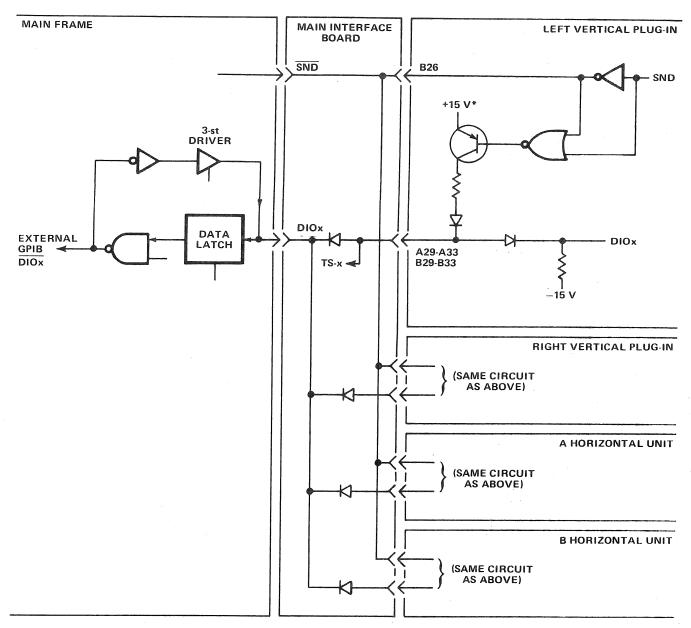

### SND (Send)

A TTL signal used by the plug-ins or main frame to indicate to the GPIB Source Handshake function in the main frame, that the device has a valid byte on the internal main frame data bus which should be transmitted by the main frame Source Handshake function.

When SND is asserted, the other plug-ins must disable their diode-logic-data-bus receivers, since the diode logic used restricts a plug-in to driving the main frame load only.

A plug-in may place one standard TTL and one LSTTL input on the line.

To drive the line low, a plug-in must be able to sink 24 mA at 0.4  $\rm V.$

### -5 V POWER

Power for programmable plug-ins.

Maximum current available to plug-ins is 0.5 amp per plug-in.

Each plug-in is limited to 25 watts total power consumption.

Initial Accuracy: ±1%.

Drift Per Year: 0.5%.

Total Ripple: 1 mV p-p.

Current fold-back protection.

## +5.1 VOLTS POWER

Power for the plug-in logic circuits.

Maximum available current is 2 amp per plug-in.

Each plug-in is limited to 25 watts total power consumption.

Adjustable to  $\pm 1\%$  initially.

Drift Per Year: ±1%.

Total Ripple: 10 mV p-p.

Inverter shut-down protection.

### **INTERPLUG-IN COMMUNICATIONS**

Interplug-in Communications, A27 and A28, were provided in the original 7000-series instruments. Because of lack of usage, they were modified out of later instruments.

A28 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of A28 allowed several contacts to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused readout IC failures.

## INTERPLUG-IN COMMUNICATIONS

Interplug-in Communications Lines, B26, B27, and B28, were provided in the original 7000-series instruments. Because of a lack of usage, they were modified out of later instruments.

B28 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of B28 allowed several pins to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused Readout IC failures.

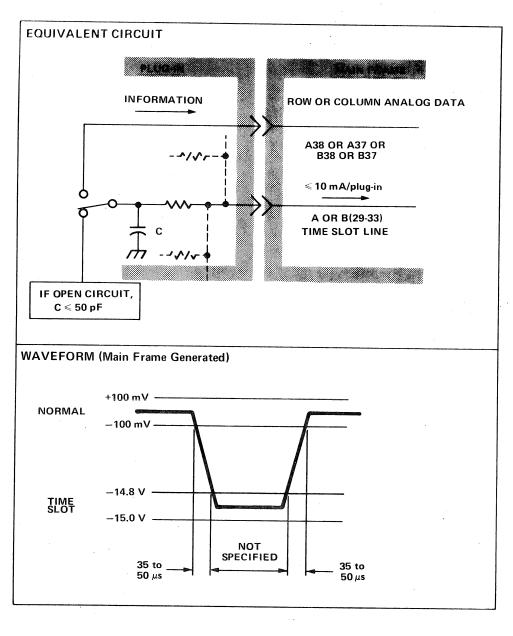

# A29 A30 A31 A32 A33

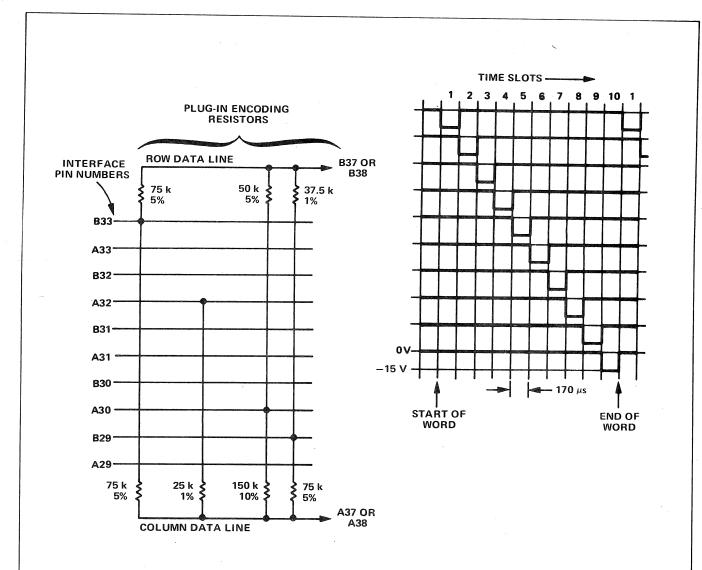

## TIME SLOT PULSE LINES NOS. 1 - 10

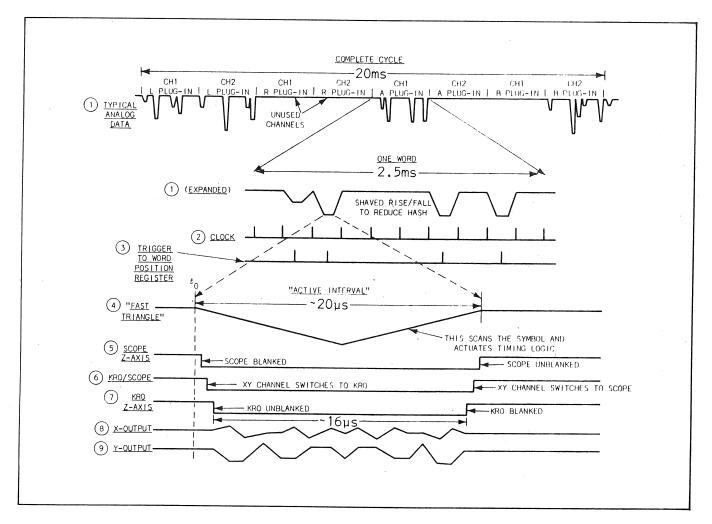

Time Slot Pulse Lines, A29-A33 and B29-B32 supply time slot #1-10 pulses to the plug-ins. Each time slot pulse encodes one character per word, and the ten pulses sequence at a fixed rate of approximately 4 kHz even when the readout is disabled at the main frame front panel, or when the readout is in its single sweep mode (except in the 7704A). The repetition rate of time slot #1-10 is 400 Hz. Frame rate is approximately 50 hertz.

For additional details of Word Scan Line Time Slots, refer to section on Readout.

For details on programmable instrument use of the time slot lines, refer to the section on Programming.

# B29 B30 B31 B32 B33

## TIME SLOT PULSE LINES

See A29 information.

### **DVM LINE**

A34 was originally used as the DVM line for the proposed two dot measuring system. This system has been deleted.

A34 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of A34 allowed several pins to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused Readout IC failures.

### **DVM COMMON LINE**

B34 was originally used as the DVM Common Line for the proposed 2-dot measuring system. This system has since been deleted.

B34 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of B34 allowed several pins to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused Readout IC failure.

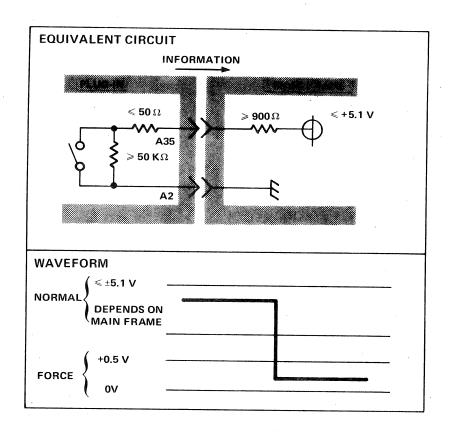

## **FORCE READOUT**

Force Readout, A35, allows plug-in readout information to be displayed regardless of the Main Frame Mode switch setting.

### **PLUG-IN MODE**

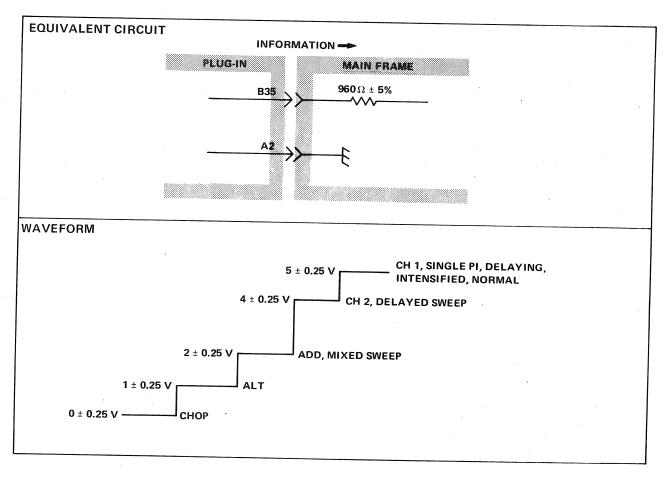

Plug-In Mode, B35, supplies the Main Frame with analog voltages to identify the operating mode of the dual-trace or dual-sweep plug-in.

The voltage levels below can be derived three different ways:

- (1) Voltage drive.

- (2) Current drive (0-5.2 mA).

- (3) Resistance to ground.

| PLUG-IN MODE                        | RESISTANCE              |

|-------------------------------------|-------------------------|

| Chop                                | 0 to $47\Omega \pm 5\%$ |

| Alt                                 | $240\Omega \pm 5\%$     |

| Add, Mixed                          | $620\Omega \pm 5\%$     |

| CH 2, Delayed                       | 3.9 K $\Omega$ ± 5%     |

| CH 1, Intensified, Normal, Delaying | ≥30 KΩ                  |

|                                     |                         |

## TRUE TIME INDICATOR

A36 was originally used as the True Time Indicator line for the proposed two dot measuring system. This system has been deleted.

A36 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of A36 allowed several pins to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused Readout IC failures.

B36 was physically removed (left blank) from the plug-in and the Main Frame connector. It was found that the presence of B36 allowed several pins to be shorted together when the plug-in was mis-aligned during insertion. This contact shorting sometimes caused Readout IC failures.

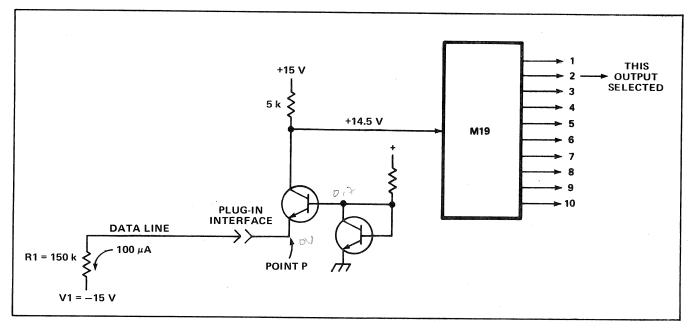

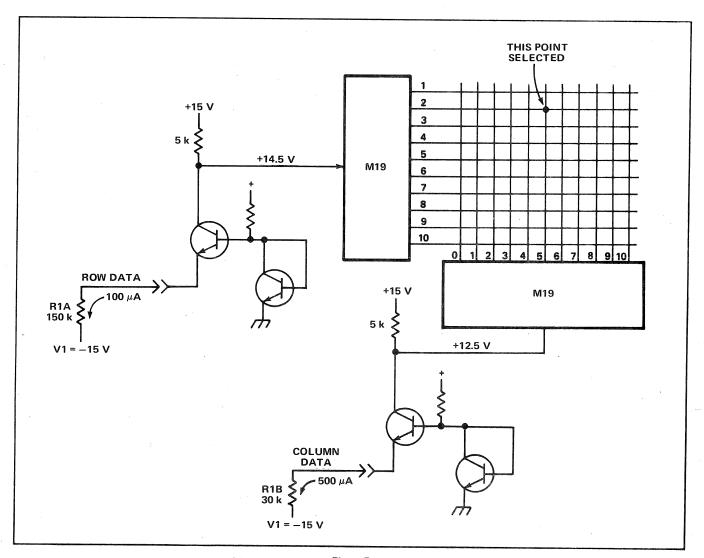

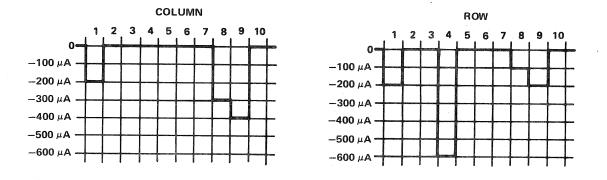

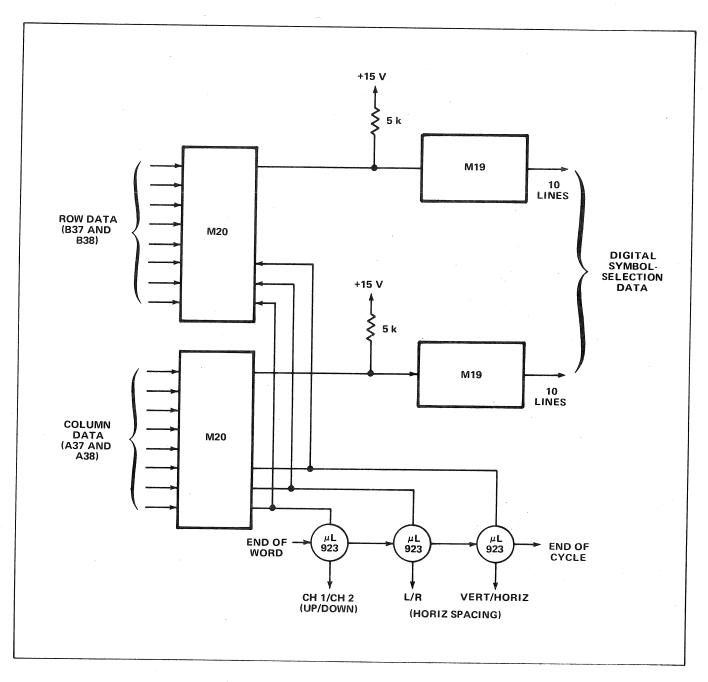

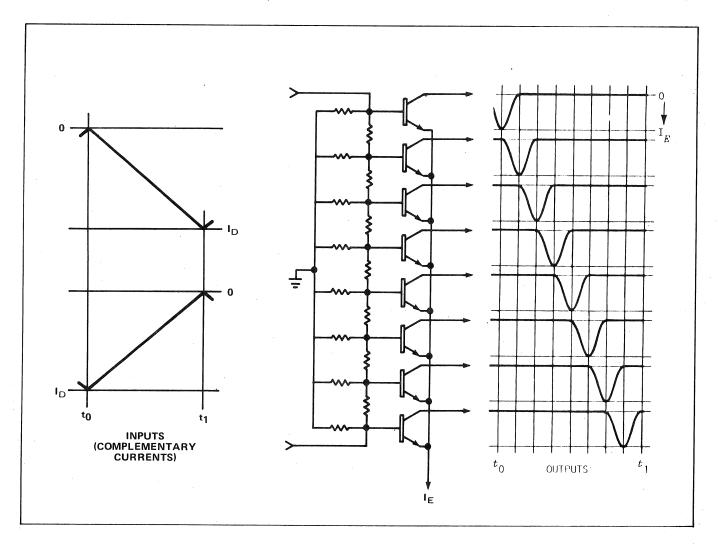

### CH 1 COLUMN ANALOG DATA

CH 1 Column Analog Data provides ten or more discrete current levels from the plug-ins to the Main Frame Readout circuitry. This information with the Time-Slot Logic (A29-33 and B29-33) provides the Main Frame with plug-in scale factor readout information.

### **CH 1 ROW ANALOG DATA**

CH 1 Row Analog Data provides ten or more discrete current levels from the plug-ins to the Main Frame Readout circuitry. This information with the Time-Slot Logic (A29-33 and B29-33) provides the Main Frame with plug-in scale factor readout information.

### **CH 2 COLUMN ANALOG DATA**

CH 2 Column Analog Data provides ten or more discrete current levels from the plug-ins to the Main Frame Readout circuitry. This information with the Time-Slot Logic (A29-33 and B29-33) provides the Main Frame with plug-in scale factor readout information.

# CH 2 ROW ANALOG DATA

CH 2 Row Analog Data provides ten or more discrete current levels from the plug-ins to the Main Frame Readout circuitry. This information with the Time-Slot Logic (A29-33 and B29-33) provides the Main Frame with plug-in scale factor readout information.

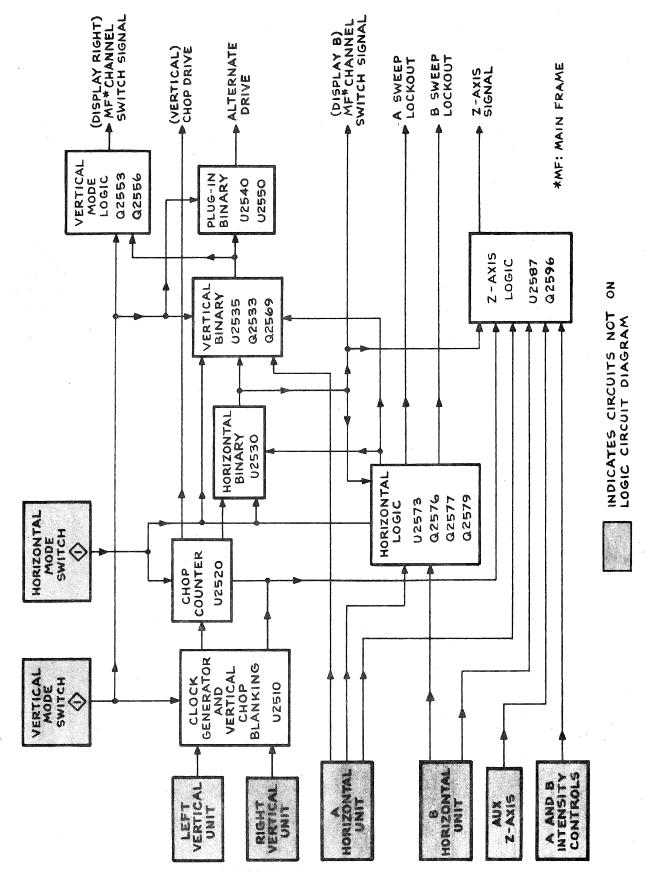

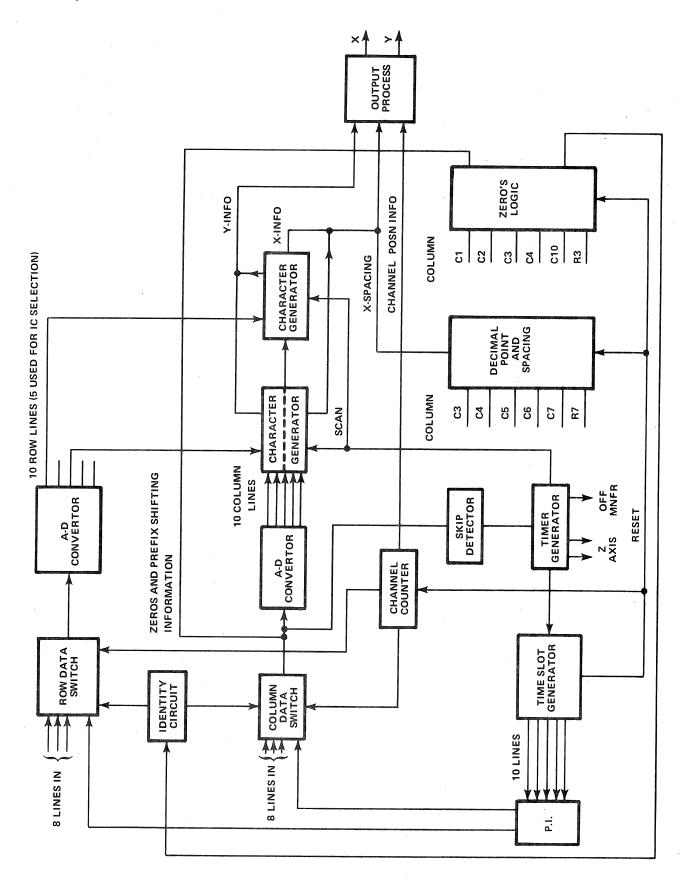

# LOGIC CIRCUIT

The Logic Circuit develops control signals for use in other circuits within this instrument. These output signals automatically determine the correct instrument operation in relation to the plug-ins installed or selected, plug-in control settings, and 7704A control settings. A block diagram of the Logic Circuit is shown in Figure 2. This diagram shows the source of the input control signals, the output signals produced by this stage, and the basic interconnections between blocks. The interconnections shown are intended only to indicate inter-relation between blocks and neither indicate a direct connection, nor that only a single connection is made between the given blocks. Details of the inter-relation between stages in this circuit are given in the circuit description which follows.

This circuit description for the Logic Circuit is written with the approach that each of the integrated circuits and its associated discrete components composes an individual stage as shown by the block diagram (Figure 2). The operation of each of these stages is discussed, relating the input signals or levels to the output, with consideration given to the various modes of operation that may affect the stage. A logic diagram is also provided for each stage. These diagrams are not discussed in detail, but are provided to aid in relating the function performed by a given stage to standard logic techniques. It should be noted that these logic diagrams are not an exact representation of the internal structure of the integrated circuit, but are only a logic diagram of the function performed by the stage. An input/output table is given, where applicable, for use along with the circuit description and logic diagram. These input/output tables document the combination of input conditions that are of importance to perform the prescribed function of an individual stage.

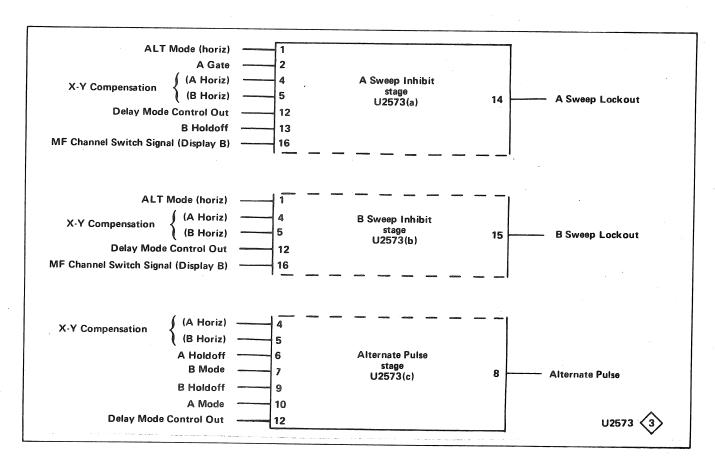

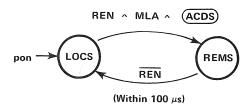

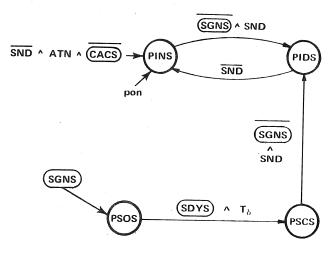

# Horizontal Logic

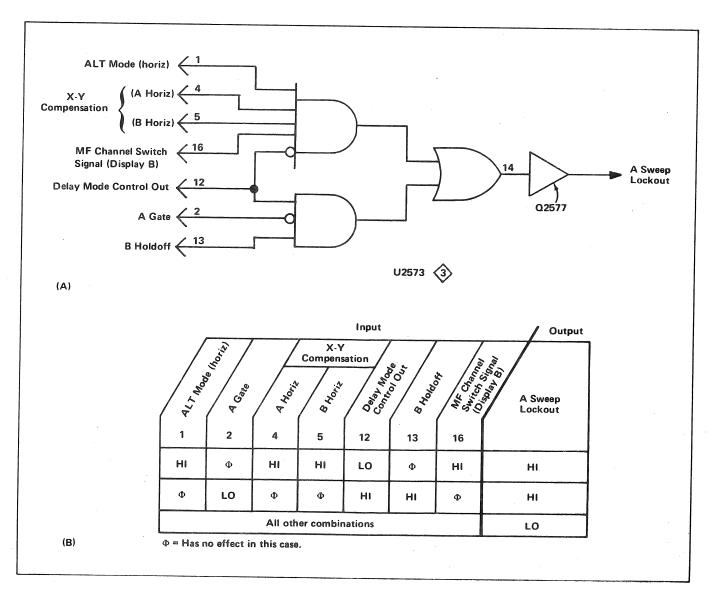

The Horizontal Logic stage performs these seperate logic functions: A Sweep Lockout, B Sweep Lockout, and Alternate Pulse Generator. Figure 1 identifies the three

three individual stages and the input and output terminals associated with each. Notice that some of the input signals are connected internally to more than one of the individual stages.

Figure 1. Breakdown of separate stages within Horizontal Logic IC (U2573) showing inputs and outputs for each stage.

Figure 2. Block diagram of Logic Circuit.

A Sweep Lockout. The A Sweep Lockout stage produces an output level at the collector of Q2577 that determines if the A HORIZ time-base unit can produce a sweep. If this output is HI, the A HORIZ unit is locked out (disabled) so it cannot produce a sweep. If the level is LO, the A HORIZ unit is enabled and can produce a sweep when triggered.

The first combination disables the A sweep while the B sweep is being displayed in the ALT horizontal mode (both units must be in time-base mode) if non-delayed operation is being used. The second combination disables the A sweep during delayed-sweep operation so that the B sweep can complete its holdoff before the next A sweep begins.

As shown by the logic diagram and input/output table of Figure 3, only two combinations of input conditions produce an A Sweep Lockout level (HI); if any one of the prescribed conditions is not met, the A Sweep Lockout level is LO and the A HORIZ time-base unit is enabled.

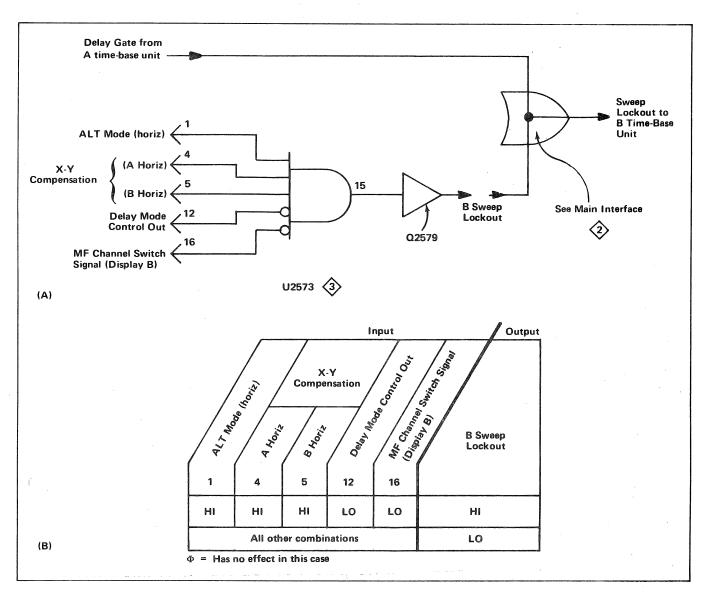

B Sweep Lockout. The B Sweep Lockout stage produces an output level at the collector of Q2579 that determines if the B HORIZ time-base unit can produce a sweep. A HI output level locks out (inhibits) the B HORIZ unit and a LO level enables the B HORIZ unit to produce a sweep.

Figure 3. (A) Logic diagram for A Sweep Lockout stage; (B) Table of input/output combinations.

As shown by Figure 4B, the output of this stage is HI only under one set of input conditions. This set of conditions disables the B sweep while the A sweep is being displayed in the ALT horizontal mode if both units are in a time-base mode and non-delayed sweep is used. For any other combination of input conditions, the B Sweep Lockout level is LO. However, the lockout level to the B time-base unit is determined by both the Delay Gate from the A time-base unit and the B Sweep Lockout level produced by this stage. The B sweep is enabled only when both of these levels are LO.

Figure 4A shows the logic diagram of the B Sweep Lockout stage. The gate connected to the output of this stage is a phantom-OR gate located on the Main Interface diagram (a phantom-OR gate performs the OR-logic function merely by interconnection of the two signal lines).

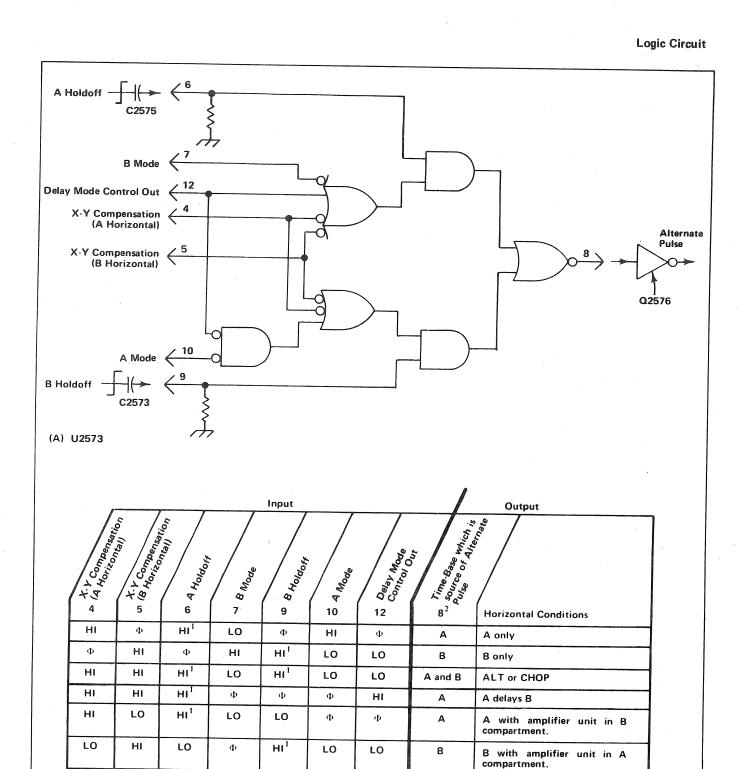

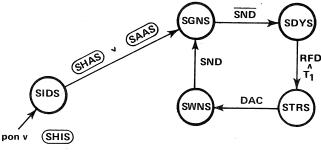

Alternate Pulse Generator. The third function performed by the Horizontal Logic stage is to produce an Alternate Pulse signal for use by the Horizontal and Vertical Binary stages. The Alternate Pulse is produced at the end of either sweep, depending upon the operating conditions as shown in Figure 5B. The holdoff gate produced at the end of the sweep by the respective time-base unit is differentiated by either C2575 or C2573 to provide a positive-going pulse to pin 6 or 9.

In Figure 5A, note the resistors shown connected to pins 6 and 9. These resistors, which are internal to the IC, hold the levels at pins 6 and 9 LO unless a HI level is applied to the corresponding input. Since the holdoff gate is capacitively-coupled to pins 6 and 9, these inputs are at the LO level except when a differentiated A or B Holdoff gate is received.

Figure 4. (A) Logic diagram for B Sweep Lockout stage; (B) Table of input/output combinations.

$<sup>\</sup>Phi$  = Has no effect in this case

All other combinations

No output pulse (LO at output)

(B)

Figure 5. (A) Logic diagram for Alternate Pulse Generator stage; (B) Table of input/output combinations.

Positive-going pulse. Where both A and B Holdoff are required to be HI, a HI at either input produces an Alternate Pulse.

<sup>&</sup>lt;sup>2</sup>Negative-going pulse.

The following discussions describe the operation of the Alternate Pulse Generator stage in relation to the various combinations of input conditions shown in Figure 5B.

#### 1. A (ONLY) MODE

An Alternate Pulse is produced at the end of each A sweep when the HORIZONTAL MODE switch is set to the A position.

#### 2. B (ONLY) MODE

In the B position of the HORIZONTAL MODE switch, an Alternate Pulse is produced at the end of each B sweep (A time-base must be in independent, non-delayed mode).

#### 3. ALT OR CHOP MODE

When the HORIZONTAL MODE switch is set to ALT or CHOP (A time-base unit must be in independent, non-delayed mode), an Alternate Pulse is produced at the end of each sweep. For example, an Alternate Pulse is produced at the end of the A sweep, then at the end of the B sweep, again at the end of the A sweep, etc. Although Alternate Pulses are produced in the CHOP horizontal mode, they are not used in this instrument.

# 4. DELAYED SWEEP (A DELAYS B)

When the A time-base unit is set for delayed operation, the operation of the Alternate Pulse Generator is changed so an Alternate Pulse is produced only at the end of the A sweep, even when the HORIZONTAL MODE switch is set to B. This is necessary since the A time-base establishes the amount of delay time for the B time-base unit whenever it is displayed.

# AMPLIFIER UNIT IN HORIZONTAL COMPARTMENT

When an amplifier unit is installed in either of the horizontal plug-in compartments, the Alternate Pulse can be produced only from the remaining time-base unit. If amplifier units are installed in both horizontal compartments, an Alternate Pulse is not produced since there are no time-base units to produce a holdoff pulse.

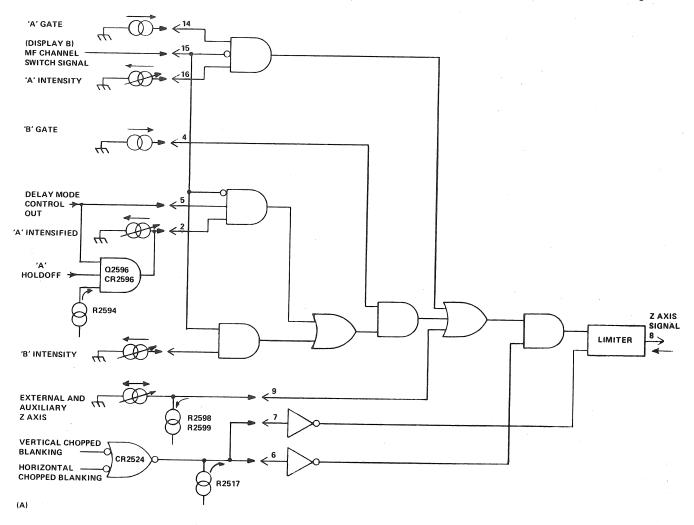

# **Z-Axis Logic**

The Z-Axis Logic stage produces an output current which sets the intensity of the display on the CRT. The level of this output current is determined by the setting of the A or B INTENSITY controls, by a current added to provide an intensified zone on the A sweep for delayed-sweep operation, or by an external signal. The input current from the A and B INTENSITY controls is switched so that the output current matches the horizontal

display. The Chopped Blanking signals are applied to this stage to block the output current and blank the CRT display for vertical and horizontal chopping.

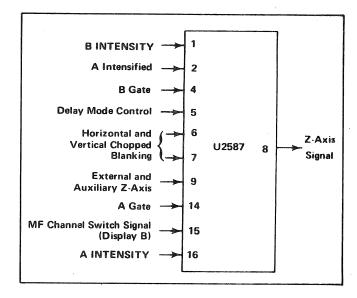

Figure 6 identifies the inputs to the Z-Axis Logic IC, U2587. This IC (integrated circuit) is current-driven at all inputs except pins 5 and 15. The current at pins 1, 2, 9, and 16 is variable from zero to four milliamperes and is determined by the applicable current source to control the output current at pin 8.

Figure 6. Input and output pins for Z-Axis Logic IC.

The Chopped Blanking signal connected to pins 6 and 7 enables or disables this stage to control all output current. Quiescently, the level at pins 6 and 7 is HI so that the intensity current from pins 1, 2, 9, and 16 can pass to the output. However, pins 6 and 7 go LO during Vertical Chopped Blanking or Horizontal Chopped Blanking. This blocks the output current and the CRT is blanked. The Vertical Chopped Blanking signal is connected directly to U2587 from pin 4 of U2510. The Horizontal Chopped Blanking is connected to U2587 from pin 4 of U2520 through LR2523 and CR2524. CR2524 is normally reverse biased. When the Horizontal Chopped Blanking level goes LO, CR2524 is forward biased to produce a corresponding LO level at pins 6 and 7 of U2573.

The A INTENSITY control sets the output current level when the A Gate at pin 14 is HI and the MF (Main Frame) Channel Switch Signal at pin 15 is LO. The A INTENSITY current is blocked whenever the A Gate level goes LO (indicating that the A sweep is complete), or the MF Channel Switch Signal goes HI (indicating that the B sweep is being displayed). The current from the A INTENSITY control (see diagram 1) is connected to pin 16 through R2587.

LO = Minimum voltage or current.

HI = Maximum voltage or current.

<sup>1</sup>Current level. LO = 0 mA HI = Veriable from 0 to 4 mA

= Has no effect in this case

<sup>2</sup>Current can be added or subtracted for intensity modulation.

Figure 7. (A) Logic diagram for Z-Axis Logic stage; (B) Table of input/output combinations.

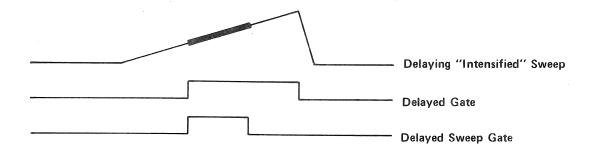

In the delayed mode, current is added to the A INTENSITY current during the A sweep time to intensify a portion of the trace. This intensified portion is coincident with the B-sweep time to provide an indication of the portion of the A sweep that is displayed in the delayed mode. The A Intensified current is supplied to pin 2 of U2587 from the A INTENSITY control through R2586. With this configuration, the intensified current increases as the A INTENSITY control setting is advanced to provide a proportional intensity increase in the intensified zone as the overall A-sweep intensity increases. Therefore, the intensified zone is more readily visible at high intensity levels. The intensified current is added to the A INTENSITY current to produce an intensified zone on the A sweep under the following conditions: HI A Gate level at pin 14, LO MF Channel Switch Signal at pin 15, HI B Gate level at pin 4, HI Delay Mode Control Out level at pin 5 and the base of Q2596, and LO A Holdoff level at the emitter of Q2596.

The B INTENSITY control determines the output current when the B Gate level at pin 4 and the MF Channel Switch Signal at pin 15 are both HI. The current from the B INTENSITY control (see diagram 1) is connected to the Z-Axis Logic stage through R2588.

The current level established by the intensity controls can be altered by the External and Auxiliary Z-Axis current level at pin 9. The current at this pin can come from the Z AXIS INPUT connector on the rear panel through R2092 or from any of the plug-in compartments through R2090, R2080, R2012, or R2010 (see diagram 2). This current either increases or decreases (depending on polarity) the output current to modulate the intensity of the display. Input from the Z AXIS INPUT connector allows the trace to be modulated by external signals. The auxiliary Z-Axis inputs from the plug-in compartments allow special purpose plug-in units to modulate the display intensity. Diodes CR2585 and CR2594 limit the maximum voltage change at pin 9 to about + and -0.6 volt to protect the Z-Axis Logic stage if an excessive voltage is applied to the Z AXIS INPUT connector.

Figure 7A shows a logic diagram of the Z-Axis Logic stage. Notice the current-driven inputs as indicated by the current-generator symbols at the associated inputs. An input/output table for the Z-Axis Logic stage is given in Figure 7B.

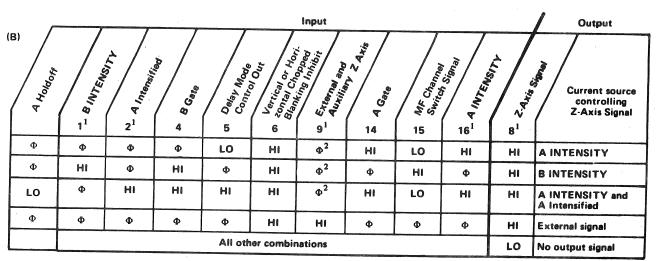

# **Horizontal Binary**

The MF (Main Frame) Channel Switch Signal (Display B) produced by the Horizontal Binary stage determines which horizontal unit provides the sweep display on the CRT. When this level is HI, the B HORIZ unit is displayed; when it is LO, the A HORIZ unit is displayed.

The MF Channel Switch Signal (Display B) is used in the following stages within the Logic Circuit: Horizontal Logic (for A and B Sweep Lockout), Z-Axis Logic (for blanking), and Vertical Binary (to synchronize vertical alternate switching with horizontal alternate switching). In addition, this signal is connected to the following circuits elsewhere in the instrument: Main Interface (to indicate which horizontal unit is to be displayed), Vertical Interface (for trace separation), and Horizontal Interface (for horizontal channel selection).

Notice that the levels at pins 3, 4, 7, and 10 are determined by the HORIZONTAL MODE switch (see diagram 1). This switch determines which horizontal mode has been selected by providing a HI level to only one of four output lines (the remaining lines are LO). Therefore, at any one time, either pin 3, pins 4 and 7 (notice that pins 4 and 7 are tied together), or pin 10 can be HI and the two unselected lines from the HORIZONTAL MODE switch remain LO.

The Horizontal Binary stage operates as follows for each position of the HORIZONTAL MODE switch (refer to Figure 8B for input/output conditions):

#### 1. A MODE

When the HORIZONTAL MODE switch is set to A, the MF Channel Switch Signal (Display B) is LO to indicate to all circuits that the A HORIZ unit is to be displayed.

#### 2. B MODE

Selecting the B horizontal mode provides a HI MF Channel Switch Signal (Display B) to all circuits.

# 3. CHOP MODE

In the CHOP position of the HORIZONTAL MODE switch, the MF Channel Switch Signal (Display B) switches between the HI and LO levels to produce a display that switches between the A HORIZ and B HORIZ units at a 200-kHz or 20-kHz rate, as selected by S2510. The repetition rate of the MF Channel Switch Signal (Display B) in this mode is determined by the Horizontal Chopped Blanking pulse (see Chop Counter description). Each time the Horizontal Chopped Blanking pulse at pin 1 drops LO, the output at pin 6 switches to the opposite state.

# 4. ALT MODE

For ALT horizontal operation, the MF Channel Switch Signal (Display B) switches to the opposite state each time the negative portion of the Alternate Pulse is received from the Horizontal Logic stage. Repetition rate of the MF Channel Switch Signal (Display B) in this mode is one-half the repetition rate of the Alternate Pulse applied to pin 8.

Figure 8A shows a logic diagram of the Horizontal Binary stage. An input/output table showing the conditions for each position of the HORIZONTAL MODE switch is shown in Figure 8B.

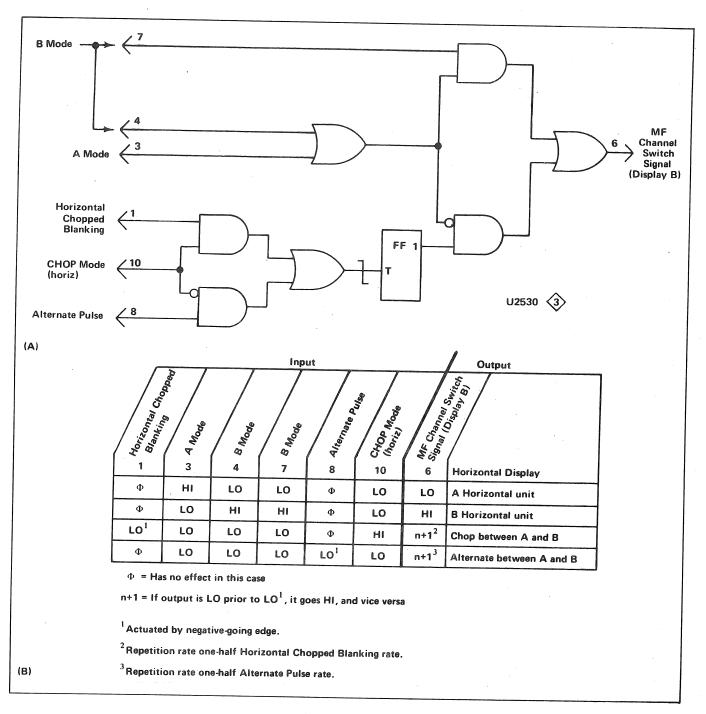

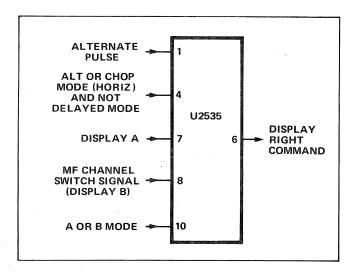

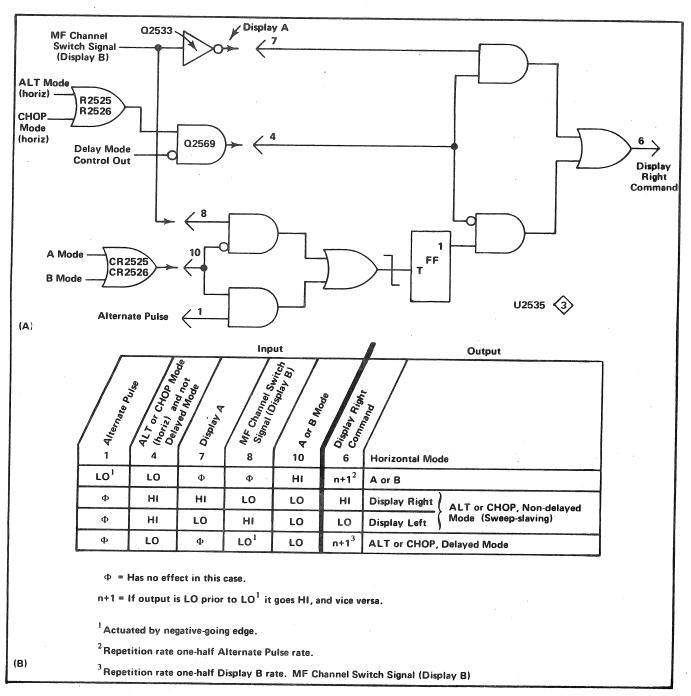

#### Vertical Binary

The Vertical Binary stage produces the Display Right Command to determine which vertical unit is to be displayed on the CRT. When this output level is HI, the

RIGHT VERT unit is displayed and when it is LO, the LEFT VERT unit is displayed. In the ALT or CHOP positions of the HORIZONTAL MODE switch (non-delayed operation only), the output of this stage is slaved to the output of the Horizontal Binary stage so that the Display Right Command is always HI when the MF (Main Frame) Channel Switch Signal (Display B) is LO, and vice versa. This action allows sweep-slaving operation in the ALT position of the VERTICAL MODE switch and the ALT or CHOP positions of the HORIZONTAL MODE

Figure 8. (A) Logic diagram for Horizontal Binary stage; (B) Table of input/output combinations.

switch, whereby the LEFT VERT unit is always displayed at the sweep rate of the B time-base unit. When the A time-base unit is set to the delayed mode, the repetition rate of the Display Right Command is one-half the repetition rate of the MF Channel Switch Signal (Display B). This results in each vertical unit being displayed first against the A time-base unit (delaying), then the B time-base unit (delayed), before the display is switched to the other vertical unit.

The Display B Command is used in the following stages within the Logic Circuit: Plug-In Binary, Vertical Chopped Blanking, and Vertical Mode Logic. It is also connected to the following circuits elsewhere in the instrument to indicate which vertical unit is to be displayed (through Vertical Mode Logic stage; ALT vertical mode only): Main Interface, Trigger Selector, and Vertical Interface circuits.

The Vertical Binary stage uses the same type of IC as the Horizontal Binary stage. Figure 9 identifies the function of the input pins for U2535. Notice the Display A level at pin 7. This input is the inverse of the MF Channel Switch Signal (Display B) at pin 8. Therefore, the Display A level is always HI when the MF Channel Switch Signal (Display B) is LO, and vice versa. The following discussions describe the operation of the Vertical Binary stage in relation to the modes of operation that can occur.

Figure 9. Input and output pins for Vertical Binary IC.

#### NOTE

Although the output at pin 6 of U2535 is always controlled by the HORIZONTAL MODE switch as described here, this level determines the MF Channel Switch Signal (Display Right) level at the collector of U2556 only in the ALT position of the VERTICAL MODE switch due to AND gate CR2552-CR2553. See the discussion of the Vertical Mode Logic stage in this section for further information.

#### 1. A OR B MODE

When the HORIZONTAL MODE switch is set to either A or B, the Display Right Command switches to the opposite state each time an Alternate Pulse is received from the Horizontal Logic stage. Repetition rate of the Display Right Command in this mode is one-half the repetition rate of the Alternate Pulse. The input conditions for these modes are:

Pin 1 LO—Alternate Pulse generated by Horizontal Logic stage goes negative.

Pin 4 LO-HORIZONTAL MODE switch in any position except ALT or CHOP, or the A time-base unit is set for delayed sweep.

Pin 10 HI-HORIZONTAL MODE switch set to A or B.

#### 2. ALT OR CHOP MODE (HORIZ)-NON-DELAYED

In the ALT or CHOP positions of the HORIZONTAL MODE switch, the output level at pin 6 is the same as the Display A level at pin 7. The Display A level is produced by inverting the MF Channel Switch Signal (Display B) from the Horizontal Binary stage. Therefore, the repetition rate of the output signal is the same as the MF Channel Switch Signal (Display B). The result, with the VERTICAL MODE switch set to ALT and the A time-base unit set for non-delayed operation, is that the RIGHT VERT unit is always displayed at the sweep rate of the A time-base unit, and the LEFT VERT unit at the sweep rate of the B time-base unit (sweep slaving). The input conditions to provide a HI output level so that the RIGHT VERT unit can be displayed at the A-sweep rate are:

Pin 4 HI—HORIZONTAL MODE switch set to ALT or CHOP with non-delayed sweep.

Pin 7 HI—A sweep is to be displayed; MF Channel Switch Signal (Display B) LO.

Pin 10 LO—HORIZONTAL MODE switch set to any position except A or B.

The input conditions to provide a LO output level so that the LEFT VERT unit can be displayed at the B-sweep rate are:

Pin 4 HI—HORIZONTAL MODE switch set to ALT or CHOP with non-delayed sweep.

Pin 7 LO-B sweep is to be displayed; MF Channel Switch Signal (Display B) HI.

Pin 10 LO-HORIZONTAL MODE switch set to any position except A or B.

The Display Right Command switches from HI to LO along with the Display A level at pin 7 (inverse of MF Channel Switch Signal, Display B). However, notice that the Display Right Command changes from HI to LO as the MF Channel Switch Signal (Display B) changes from LO to HI, and vice versa.

# 3. ALT OR CHOP MODE (HORIZ)-DELAYED

If the A time-base unit is set to the delayed mode when the HORIZONTAL MODE switch is set to either ALT or

CHOP, the operation of the stage is changed from that discussed above. Now, the Display Right Command switches between the HI and LO states at a rate that is one-half the repetition rate of the MF Channel Switch Signal (Display B). The resultant CRT display allows the RIGHT VERT unit to be displayed first against the A sweep (delaying) and then against the B sweep (delayed). Then the display switches to the LEFT VERT unit and is displayed consecutively against the A and B sweeps in the same manner. The input conditions for this mode of operation are:

Figure 10. (A) Logic diagram for Vertical Binary stage; (B) Table of input/output combinations.

Pin 4 LO-A time-base unit set for delayed operation.

Pin 8 LO-MF Channel Switch Signal (Display B) generated by Horizontal Binary stage goes negative.

Pin 10 LO-HORIZONTAL MODE switch set to any position except A or B.

A logic diagram of the Vertical Binary stage is shown in Figure 10A. Several logic functions in this stage are performed by logic devices made up of discrete components. The components that make up these logic devices are identified on the Logic diagram. An input/output table for the Vertical Binary stage is given in Figure 10B.

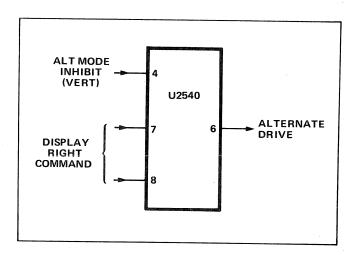

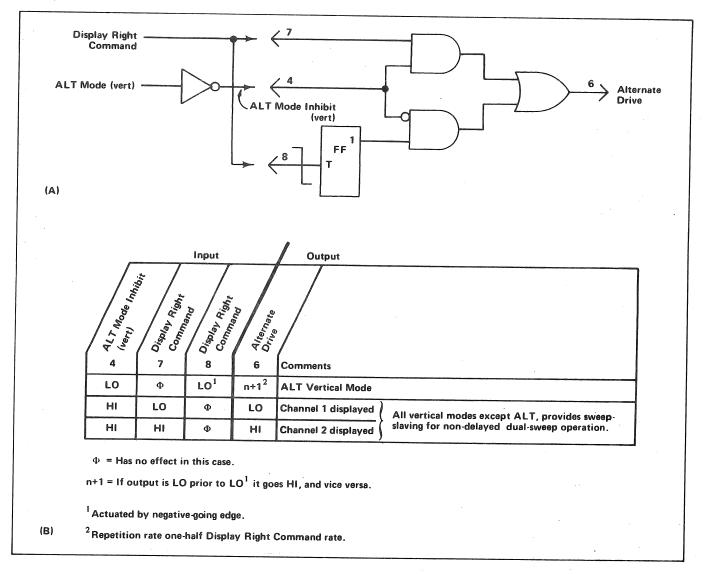

# Plug-In Binary

The Plug-In Binary stage produces the Alternate Drive signal to provide a plug-in alternate command to dual-trace plug-in units. This stage uses the same type of IC as the Horizontal Binary and Vertical Binary stages. Figure 11 identifies the function of the input pins for the Plug-In Binary IC, U2540.

Figure 11. Input and output pins for Plug-In Binary IC.

When the Alternate Drive level is HI and the plug-in unit is set for alternate operation, Channel 2 of the dual-trace unit is displayed. When it is LO, Channel 1 is displayed. The repetition rate of the Alternate Drive output is determined by the setting of the VERTICAL MODE switch. For all positions except ALT, the Alternate Drive level is the same as the Display Right Command from the Vertical Binary stage. Since the Display Right Command was derived directly from the MF (Main Frame) Channel Switch Signal (Display B), this allows the two channels of a dual-trace

vertical unit to be slaved to the time-base units (non-delayed, dual-sweep horizontal modes only) in the same manner as previously described for slaving between the vertical and time-base units. The resultant CRT presentation, when the dual-trace unit is set for alternate operation, displays the Channel 1 trace at the sweep rate of the B time-base unit and the Channel 2 trace at the sweep rate of the A time-base unit. Input conditions for a LO output so that Channel 1 of the vertical plug-in can be displayed at the B-sweep rate are:

Pin 4 HI-VERTICAL MODE switch set to any position except ALT.

Pin 7 HI-A sweep to be displayed.

The Alternate Drive switches from HI to LO as the MF Channel Switch Signal (Display B) from the Horizontal Binary stage switches from LO to HI, and vice versa.

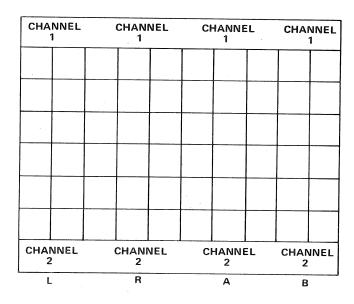

When the VERTICAL MODE switch is set to ALT, the Display Right Command from the Vertical Binary stage switches the vertical display between the two vertical units. However, if either of the vertical plug-in units are dual-trace units, they can be operated in the alternate mode also. To provide a switching command to these units, the Plug-In Binary stage produces an output signal with a repetition rate that is one-half the repetition rate of the Display Right Command. The sequence of operation, when two dual-trace vertical units are installed in the vertical plug-in compartments and they are both set for alternate operation, is as follows (VERTICAL MODE and HORIZONTAL MODE switches set to ALT): 1. Channel 1 of LEFT VERT unit at sweep rate of B time-base unit, 2. Channel 1 of RIGHT VERT unit at sweep rate of A time-base unit, 3. Channel 2 of LEFT VERT unit at sweep rate of B time-base unit, 4. Channel 2 of RIGHT VERT unit at sweep rate of A time-base unit. Notice that under these conditions, both channels of the LEFT VERT unit are displayed at the B-sweep rate and that both channels of the RIGHT VERT unit are displayed at the A-sweep rate. The repetition rate at the output of this stage is one-half the Display Right Command rate. Input conditions, when the VERTICAL MODE switch is set to ALT, are:

Pin 4 LO-VERTICAL MODE switch set to ALT.

Pin 8 LO—Display Right Command generated by Vertical Binary stage goes negative.

Figure 12A shows a logic diagram of the Plug-In Binary stage. An input/output table for this stage is shown in Figure 12B.

Figure 12. (A) Logic diagram for Plug-In Binary stage; (B) Table of input/output combinations.

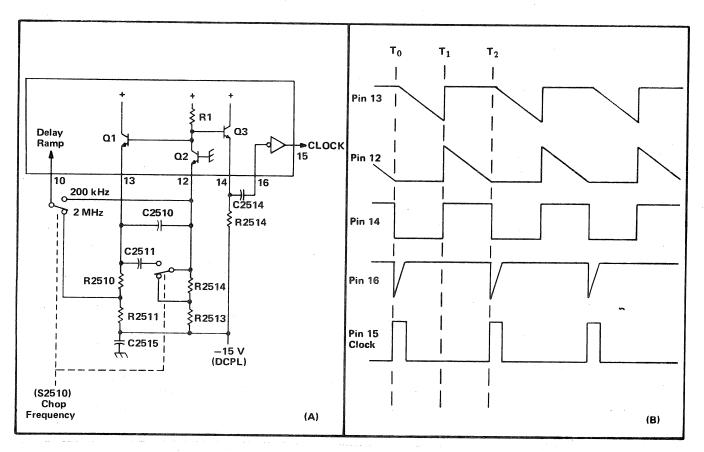

#### **Clock Generator**

Part of integrated circuit U2510, along with the external components shown in Figure 13A, make up the Clock Generator stage. R1, Q1, Q2, and Q3 represent an equivalent circuit within U2510. The output at pin 15 is a free-running timing (Clock) signal used to synchronize the vertical, horizontal, and plug-in chopping modes.

The frequency of the Clock signal is either 200 kilohertz or two megahertz, depending on the position of the internal Chop Frequency switch S2510. The 200-kilohertz output is provided for other systems using the A7704 Acquisition Unit (the bottom half of the 7704A). For normal operation of the 7704A, the Chop Frequency switch should be left in the 2-MHz position.

When the internal Chop Frequency switch is in the 200-kHz position, the stage operates as follows: At time  $T_{\rm O}$  (see Figure 13B), the collector current through Q2 is producing a voltage drop across R1 to cut off Q1. Since there is no current through Q1, C2510 and C2511 begin to charge towards -15 volts through R2510-R2511. This causes the emitter of Q1 to gradually go negative until it is about 0.6 volt more negative than the base. At this point ( $T_{\rm 1}$  on Figure 13B), Q1 is forward biased into conduction and its emitter rapidly goes positive. Since the charge on C2510-C2511 cannot change instantaneously, the sudden change in voltage at the emitter of Q1 pulls the emitter of Q2 positive also, to reverse-bias it into cutoff. When the current through Q2 stops, its collector rises to produce a positive output level at pin 14 (time  $T_{\rm 1}$ ).

During time  $T_1$ - $T_2$ , conditions are reversed. Since Q2 is biased off, there is no current through it and C2510-C2511 begins to discharge through R2512-R2513. The emitter level of Q2 follows the discharge of C2510-C2511 until it is about 0.6 volt more negative than the base. This forward biases Q2 and its collector drops negative to reverse-bias Q1. The level at pin 14 drops negative also, to complete the cycle. Once again, C2510-C2511 begin to charge through R2510-R2511 to start the second cycle. When S2510 is set to the 2-MHz position, R2512 is bypassed and one end of C2511 is disconnected from the RC timing circuit. The decreased RC time allows C2510 to charge and discharge at a two-megahertz rate.

Two outputs are provided by this oscillator: The Delay Ramp signal from Q1 or Q2 is connected to the Vertical Chopped Blanking stage, and a square-wave output from pin 14. The square wave at pin 14 is connected to pin 16 through an external capacitor, C2510. C2510 differentiates the square wave from pin 14 to produce a negative-going pulse coincident with the falling edge of the square wave (see pin-16 waveform on Figure 13B). This negative-going pulse is connected to pin 15 through an inverter-shaper which is part of U2510. The resulting output at pin 15 is a

positive-going Clock pulse at a repetition rate of either 200 kilohertz or two megahertz, depending on the position of S2510.

# Vertical Chopped Blanking

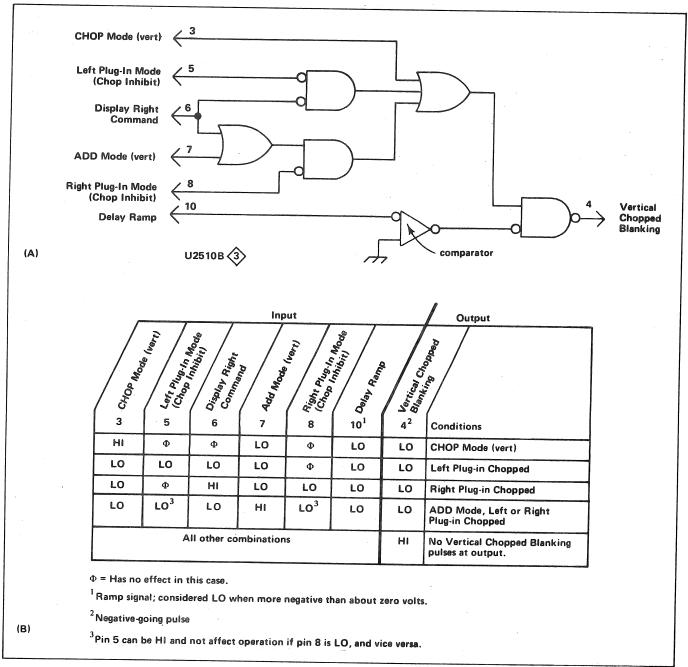

The Vertical Chopped Blanking stage is made up of the remainder of U2510. This stage determines if Vertical Chopped Blanking pulses are required, based upon the operating mode of the vertical system or the plug-in units (dual-trace units only). Vertical Chopped Blanking pulses are produced if: 1. VERTICAL MODE switch is set to CHOP; 2. Dual-trace vertical unit is operating in the chopped mode and that unit is being displayed; 3. Dual-trace vertical unit is operating in the chopped mode with the VERTICAL MODE switch set to ADD. The repetition rate of the negative-going Vertical Chopped Blanking pulse output at pin 4 is 0.2 or two megahertz for all of the above conditions (determined by the Clock Generator stage).

Figure 14 shows a logic diagram and an input/output table for the Vertical Chopped Blanking stage. Notice the comparator block on the diagram. The output of this comparator is determined by the relationship between the levels of its inputs. If pin 10 is more positive (HI) than the grounded input, the output is HI also; if it is more negative, the output is LO.

Figure 13. (A) Diagram of Clock Generator stage; (B) Idealized waveforms for Clock Generator stage.

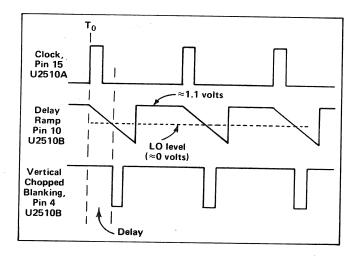

The Delay Ramp signal from the Clock Generator stage determines the repetition rate and pulse width of the Vertical Chopped Blanking pulses. The Delay Ramp applied to pin 10 starts to go negative from a level of about +1.1 volts coincident with the leading edge of the Clock pulse (see waveforms in Figure 15). This results in a HI quiescent condition for the Vertical Chopped Blanking pulse. The slope of the negative-going Delay Ramp is determined by the Clock Generator stage. As it reaches a level slightly negative from ground, the Vertical Chopped Blanking pulse output level changes to the LO state and remains LO until the Delay Ramp goes HI again.

Notice the delay between the leading edge of the Clock pulse generated by U2510A, and the leading edge of the Vertical Chopped Blanking pulses. The amount of delay between the leading edges of these pulses is determined by the Delay Ramp applied to pin 10. This delay is necessary due to the delay line in the vertical deflection system. Otherwise, the trace blanking resulting from the Vertical Chopped Blanking pulse would not coincide with the switching between the displayed traces. The duty cycle of the square wave produced in the Clock Generator stage determines the pulse width of the Vertical Chopped Blanking pulses (see Clock Generator description for more information).

Figure 14. (A) Logic diagram for Vertical Chopped Blanking stage; (B) Table of input/output combinations.

Figure 15. Idealized waveforms for Vertical Chopped Blanking stage.

## **Chop Counter**

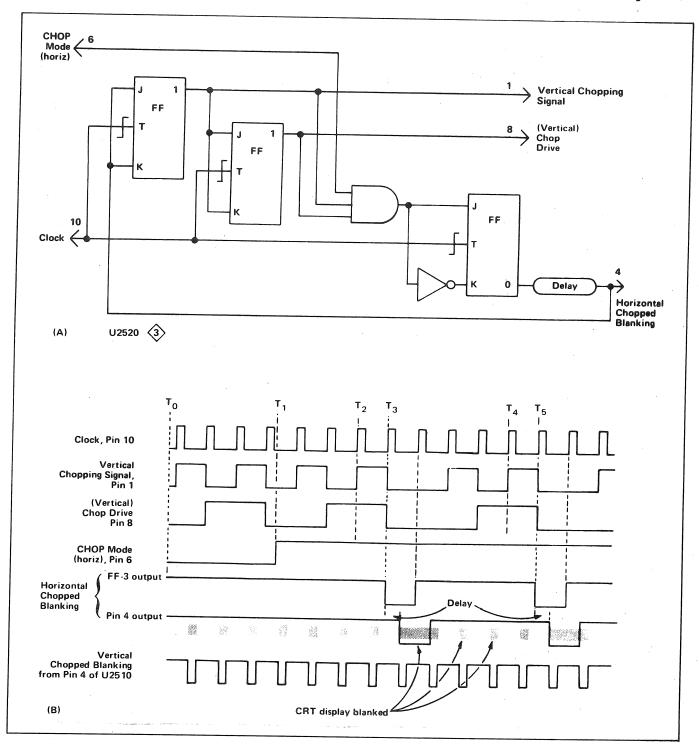

The Chop Counter stage of U2520 produces the Vertical Chopping Signal (pin 1), the (Vertical) Chop Drive (pin 8), and the Horizontal Chopped Blanking signal (pin 4). A logic diagram for U2520 is shown in Figure 16, along with waveforms showing the timing relationship between the input and output signals for this stage.

When the HORIZONTAL MODE switch is set to any position except CHOP, pin 6 remains LO and the repetition rate of the Vertical Chopping Signal at pin 1 is one-half the Clock rate (see time  $T_0$  to  $T_1$ ). This determines the switching rate between the left and right vertical compartments when the VERTICAL MODE switch is set to CHOP.

At the same time, the repetition rate of the (Vertical) Chop Drive at pin 8 is one-fourth the Clock rate. This provides a chopping signal to dual-trace vertical units to provide switching between the two channels. During this time, the level at pin 4 will remain HI.

When the HORIZONTAL MODE switch is set to CHOP, the basic repetition rate of the Vertical Chopping Signal and the (Vertical) Chop Drive is altered. For example, if the HORIZONTAL MODE switch is changed at time  $T_1$  (see Figure 16), a HI level is applied to pin 6. Outputs at pins 1 and 8 will be produced in the normal manner until both outputs are HI. (See time  $T_2$ ; this condition only occurs once every fifth Clock pulse and only when the HORIZONTAL MODE switch is set to CHOP.) When both of these outputs are at their HI level, the next Clock pulse (at time  $T_3$ ) switches both outputs LO, and at the same time, switches the Horizontal Chopped Blanking output to the LO level, where it remains until the start of the next Clock pulse.

This change at time T<sub>3</sub> does not appear at pin 4 immediately, due to a delay network in the circuit. (The delay is necessary to make the Horizontal Chopped Blanking coincide with the Vertical Chopped Blanking produced by U2510A; compare bottom two waveforms of Figure 16. Also, see Vertical Chopped Blanking description.) After the delay time, the output level at pin 4 goes LO to blank the display.

The Horizontal Chopped Blanking time must be longer than the Vertical Chopped Blanking time, since it takes more time for the display to switch between horizontal units than between vertical units. During the time that the level at pin 4 is LO, the CRT is blanked and the Vertical Chopping Signal and the (Vertical) Chop Drive cannot change levels. The Clock pulse at  $T_3$  changes only the Horizontal Chopped Blanking output. The level on pin 4 goes HI after the delay time to unblank the CRT.

For the next three Clock pulses, the Vertical Chopping Signal output and (Vertical) Chop Drive operate in the normal manner. However, at the fourth Clock pulse (Time  $\mathsf{T_4}$ ) both outputs are again at their HI level. The fifth Clock pulse at  $\mathsf{T}_6$  switches the output at pin 1, pin 8, and pin 4 (after delay) to the LO level to start the next cycle. Notice that a Horizontal Chopped Blanking pulse is produced at pin 4 with every fifth Clock pulse. Also notice that with the HORIZONTAL MODE switch set to CHOP, two complete cycles of the Vertical Chopping Signal are produced with each five Clock pulses (repetition rate, two-fifths Clock rate) and one complete cycle of the (Vertical) Chop Drive for every five Clock pulses (one-fifth Clock rate). Notice that the large shaded area produced by the Horizontal Chopped Blanking pulse (see Figure 16) is not part of the display time (CRT display blanked). However, about the same time segment is displayed from the vertical signal source with or without Horizontal Chopped Blanking, due to the change in repetition rate when in the CHOP horizontal mode.

The Vertical Chopping Signal at pin 1 of U2520 is connected to the Vertical Mode Logic stage (see following description) through L2519-R2519. This signal is HI when the right vertical unit is to be displayed and LO when the left vertical unit is to be displayed. The (Vertical) Chop Drive at pin 8 is connected to the plug-in units in the vertical compartments through L2528-R2528 via the Main Interface board. When this signal is HI, Channel 2 of the plug-in units can be displayed; when this level is LO, Channel 1 is displayed. The Horizontal Chopped Blanking signal at pin 4 is connected through LR2523 to the Horizontal Binary stage U2530 and to the Z-Axis Logic stage U2573 by way of CR2524. When this signal is HI, the CRT is unblanked to display the selected signal. When it is LO, the CRT is blanked to allow switching between the horizontal units.

Figure 16. (A) Logic diagram for Chop Counter stage; (B) Table of input/output combinations.

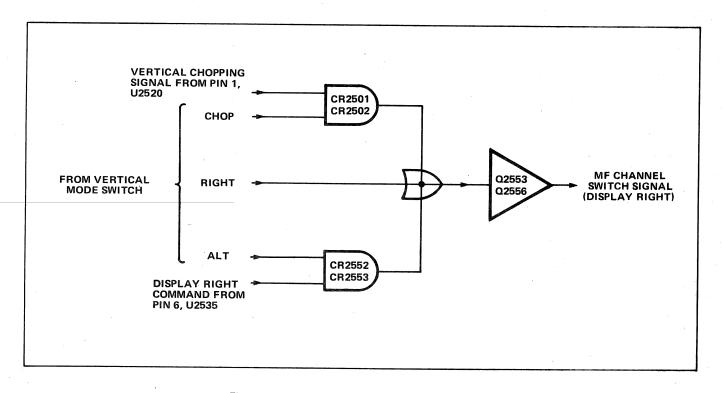

## Vertical Mode Logic

The Vertical Mode Logic stage is made up of discrete components CR2501-CR2502, CR2552-CR2553, and Q2553-Q2556. These components develop the MF (Main Frame) Channel Switch Signal (Display Right). This signal is connected to the Main Interface circuit (vertical plug-in compartments and trigger-selection circuitry) and to the

Vertical Interface circuit to indicate which vertical unit is to be displayed. When this output level is HI, the right vertical unit is displayed; when it is LO, the left vertical unit is displayed.

The VERTICAL MODE switch shown on diagram 1 provides control levels to this stage. This switch provides a

HI level on one of five output lines to indicate the selected vertical mode; the remaining lines are LO (notice that only four of the lines from the VERTICAL MODE switch are used on this schematic). Operation of this stage is as follows:

When the VERTICAL MODE switch is set to RIGHT, a HI level is connected to the base of Q2553 through R2501. This forward-biases Q2553, and the positive-going level at its emitter is connected to the emitter of Q2556. The collector of Q2556 goes HI to indicate that the right vertical unit is to be displayed. For the CHOP position of the VERTICAL MODE switch, a HI level is applied to the anodes of CR2501-CR2502 through R2502. Both diodes are forward biased so that the Vertical Chopping Signal from pin 1 of U2520 can pass to the base of Q2553. This signal switches between the HI and LO levels at the Clock Generator rate and produces a corresponding MF Channel Switch Signal (Display Right) output at the collector of Q2556. When this output is HI, the right vertical unit is displayed and when it switches to LO, the left vertical unit is displayed.

In the ALT position of the VERTICAL MODE switch, a HI level is applied to the anodes of CR2552-CR2553 through R2551. These diodes are forward biased so the Display Right Command from pin 6 of the Vertical Binary stage can pass to the base of Q2553 to determine the MF Channel Switch Signal (Display Right) level. The Display Right Command switches between its HI and LO levels at a rate determined by the Vertical Binary stage.

The control levels in the LEFT and ADD positions of the VERTICAL MODE switch are not connected to this stage. However, since only the selected line from the VERTICAL MODE switch can be HI, the RIGHT, CHOP, and ALT lines must remain at their LO level when either LEFT or ADD are selected. Therefore, the base of Q2553 remains LO to produce a LO MF Channel Switch Signal (Display Right) output level at the collector of Q2556.

A logic diagram of the Vertical Mode Logic stage is shown in Figure 17.

Figure 17. Logic diagram of Vertical Mode Logic stage.

# **POWER SUPPLIES**

The 7000-Series Main Frames were the first Tektronix Laboratory oscilloscopes to have power supplies treated as a separate module. This gave the design engineer more flexibility in the choice of a power system as evidenced by the initial 7000-Series Main Frames: One with a lossy supply (7504) and the other (7704) with a high-efficiency supply.

Second generation 7000-Series Main Frames again used the separate power supply module concept. As before, two types of supplies were used: A low-efficiency low-cost unit for the 7400- and 7600-Main Frames, and an improved, more compact, reduced-cost high-efficiency supply (7800 and 7900 Main Frames). Both concepts provided for 5.25 inch-high rackmount main frame applications.

The 7400 and 7600 supplies have separate low and high voltage modules. The 7800 and 7900 supplies combine the low and high voltage supplies in the same package deriving both from the common inverter source.

The reason for continuing with two power supply concepts is primarily economical. The high efficiency supply would have been used exclusively, had its costs been lower. A comparison follows:

|                      | Low Efficiency | High Efficiency |

|----------------------|----------------|-----------------|

| Cost                 | + (1.0)        | - (1.5 to 2.0)  |

| Efficiency           | <b>– 50%</b>   | + 75%           |

| Weight               | – 15 - 25 lbs. | + 7 - 10 lbs.   |

| Size                 | <b>–</b> (1.0) | + (0.75)        |

| Servicing Difficulty | +              | _               |

| EMI Generation       | +              | <del>_</del>    |

| Reliability*         | <b>+</b>       | _               |

+ = In favor.

– = Against.

Historically this has not been true due to the high thermal stress on some low-efficiency supply components. However, a moderately stressed low-efficiency supply should be more reliable, due primarily to its lesser number of components.

# POWER SUPPLY FEATURES AND SPECIFICATIONS

Except as noted, the following are common to both the high- and low-efficiency supplies.

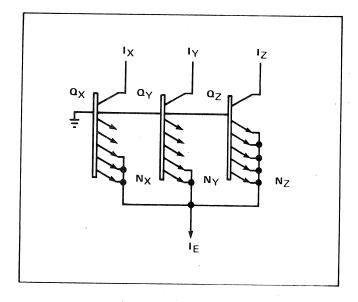

# **Voltage Sensing**

Voltage sensing is used to assure accurate supply voltages at the Main Frame/Plug-In Interface. The  $\pm 5$  V,  $\pm 15$  V, and  $\pm 50$  V supplies are used by the plug-ins which require accurate voltages so that calibration can be assured regardless of the main frame used.

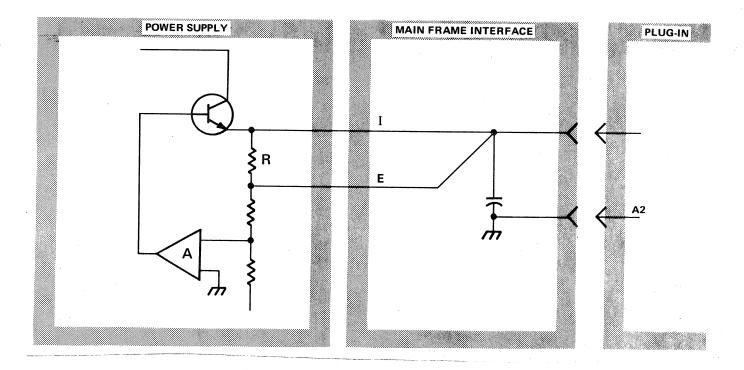

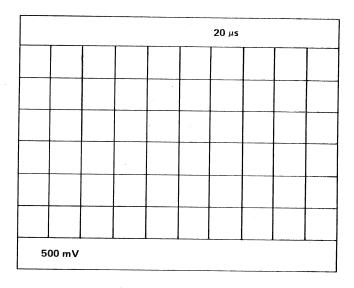

This sensing is done on the Main Interface board close to the plug-in connectors. Heavy conductor lines are provided for the current path and light conductor lines for the voltage sensing. A typical circuit is as follows:

There is essentially zero change in current in the Sense Line (E) with changing load, therefore, it is not load dependent. This is not true of the Current Line (I) as the voltage on the Series Pass Emitter will move with changing load. Resistor R prevents supply runaway if the Sense Line opens. The Resistor R is large enough to minimize loading on the Sense Line (E).

#### **Overload Protection**

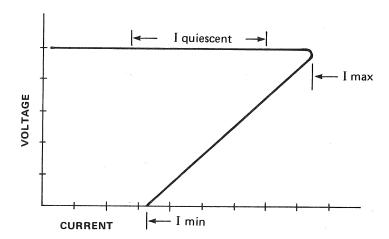

The +5 V, ±15 V, and ±50 V supplies utilize foldback of the output current for protection, i.e., output current is limited to a maximum value, then as the supply output voltage is pulled toward ground, the current reduces.

Where:

I max: >I quiescent. Typically 20 - 30% over I quiescent.

I min: