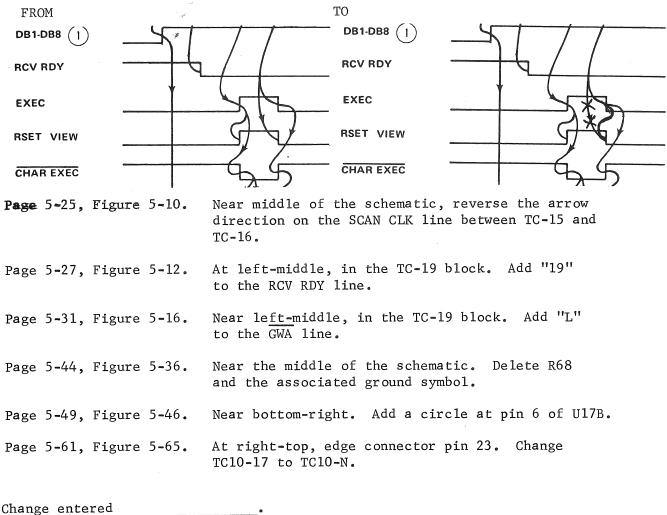

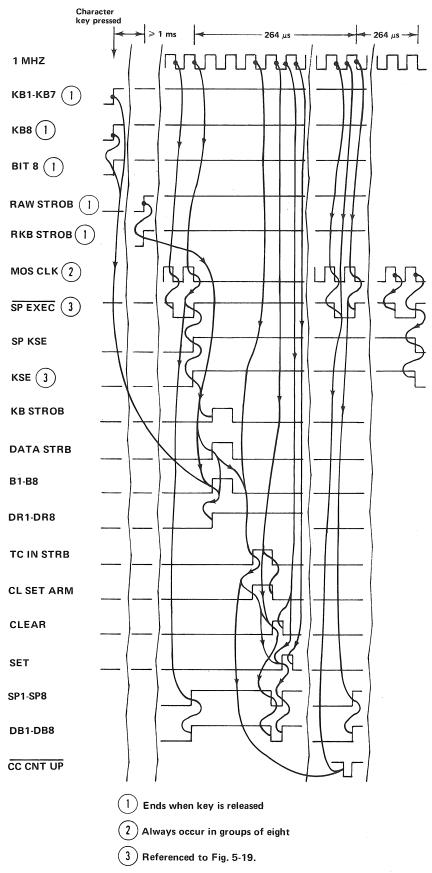

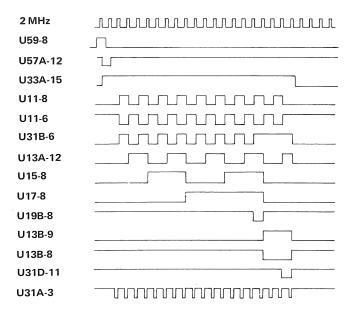

Page 5-24, Figure 5-7. Change part of the timing as shown below:

Date

File this change notice in the back of the manual.

Premanent File Copy

с ... Б

4002A DRAWER UNIT AND KEYBOARD MAINTENANCE MANUAL EFF SN B070630 This modification modernizes TC-2 circuitry.

SECTION 2: Replace pages 2-3/2-4 with the enclosed pages 2-3 through 2-4A.

SECTION 4: Replace pages 4-5/4-6 with the enclosed pages 4-5, 4-5A, 4-5B & 4-6.

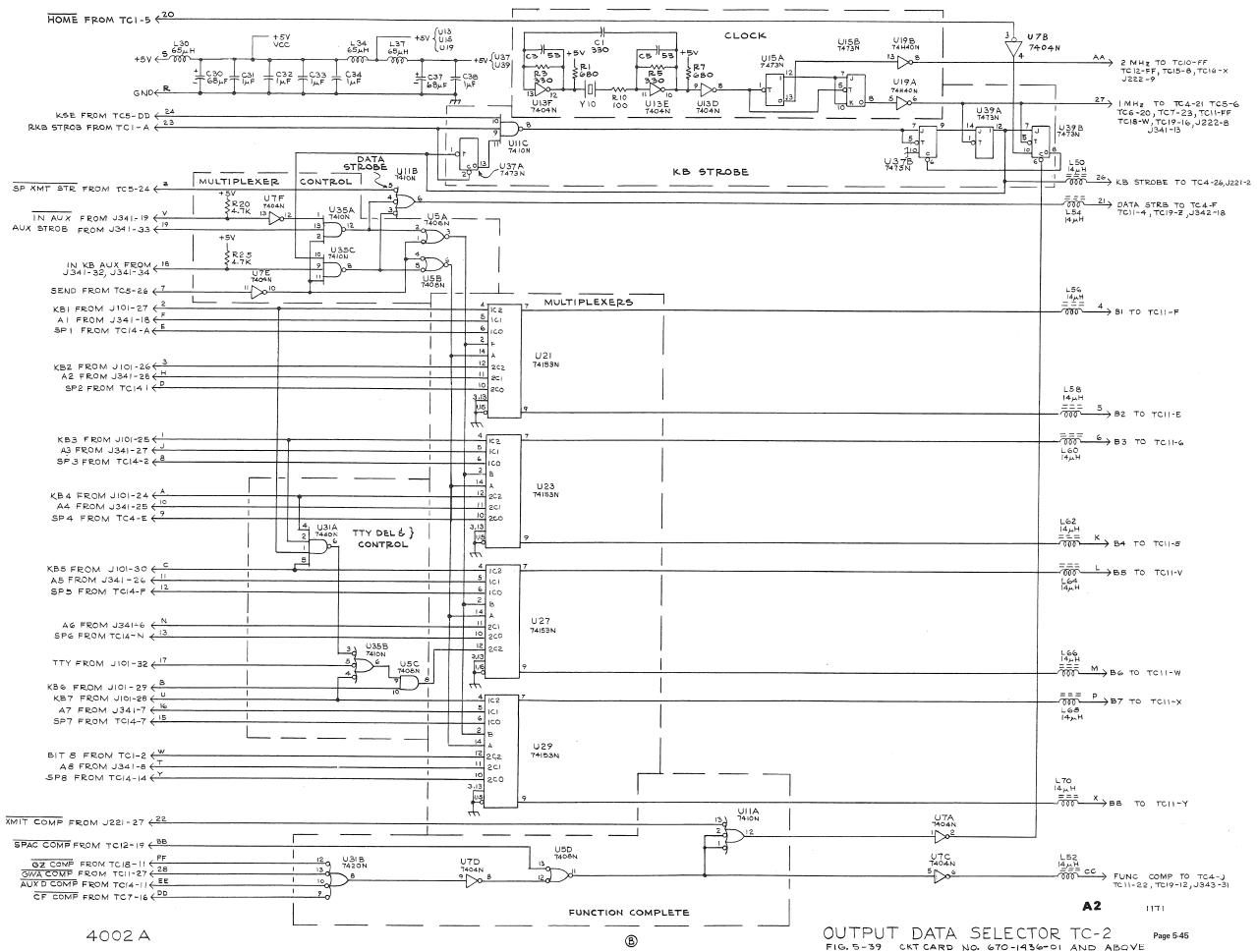

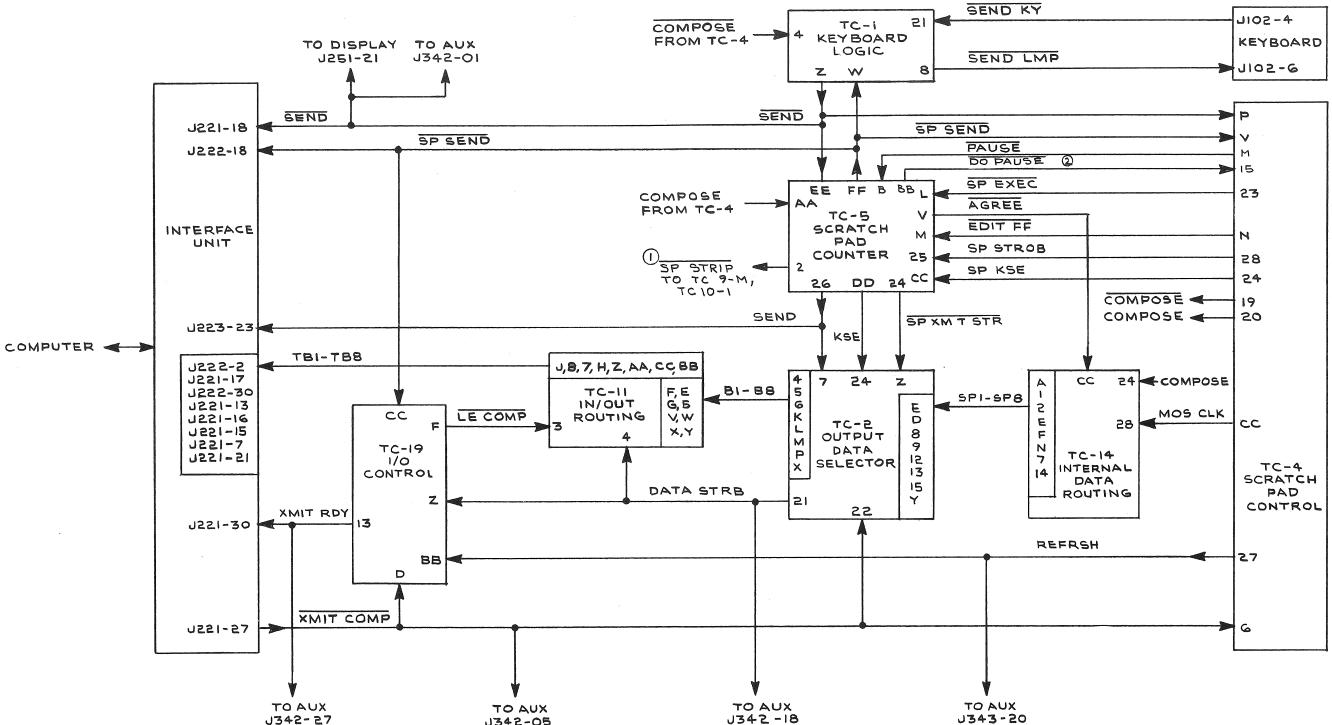

SECTION 5: Page 5-45 - Change Tab label to read TC-2 670-1436-00

Change Fig. 5-37 title to "Fig. 5-37A. KB STROBE

timing (TC-2 circuit card 670-1436-00)."

Change Fig. 5-38 title to "Fig. 5-38A. Clock timing

(TC-2 circuit card 670-1436-00)."

Change Fig. 5-39 title to "Fig. 5-39A. OUTPUT DATA

SELECTOR. TC-2 CIRCUIT CARD 670-1436-00."

Change page number to 5-45A.

Insert the enclosed page 5-45 between page 5-44 and 5-45A.

Modification entered in manual \_\_\_\_\_.

Date

Insert this instruction page in the back of the manual.

viewing level, thus prolonging tube life. Whenever data is processed by the Terminal or whenever appropriate keys are pressed, the  $\overline{HOLD}$  signal is removed and a  $\overline{VIEW}$  signal is generated to permit another 60 to 120 second viewing period. Just before the  $\overline{HOLD}$  signal is generated, the View Lamp pulsates to warn of the impending Hold Mode. This permits the operator to reset the circuit for another 60 to 120 seconds before it drops into the Hold Mode.

Operation is as follows: Assume that either a VIEW KY or a RSET VIEW signal has just been received. It is applied to U95, where it generates a positive 60 to 120 second output pulse. This pulse is applied to U87 to reset that counter circuit, and is also applied to Q93 to hold it in conduction. With Q93 in conduction, its collector holds the gate of Q91 low to keep that device turned off. When the delay period has elapsed, the output of U95 returns low, releasing U87 and turning Q93 off. With Q93 turned off, C20 charges until it places Q91 in conduction momentarily. C20 then discharges through R24 and the gate junction of Q91. Q91 then again turns off, permitting C20 to go into another charge cycle.

Each time Q91 turns on, it applies a positive pulse to U87. The trailing edge of this pulse advances the U87 count by one. The VIEW LMP signal is caused by the  $\div$  2 output of U87, and causes the lamp to blink 7 times until all four outputs from U87 go high. The output of U85B then goes low, and applies a high through R12 to Q93. Q93 conducts and shorts out C20, holding Q91 cut off. The low out of U85B becomes the HOLD signal. It is inverted by Q71 to place a high on the VIEW line. The VIEW LMP output is held low until another viewing cycle is commanded.

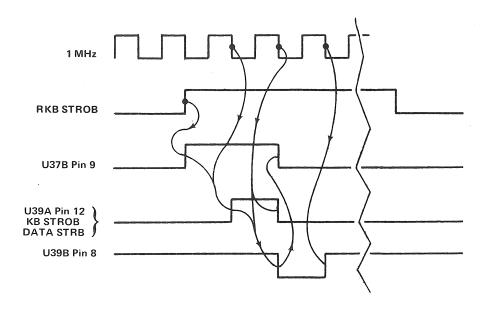

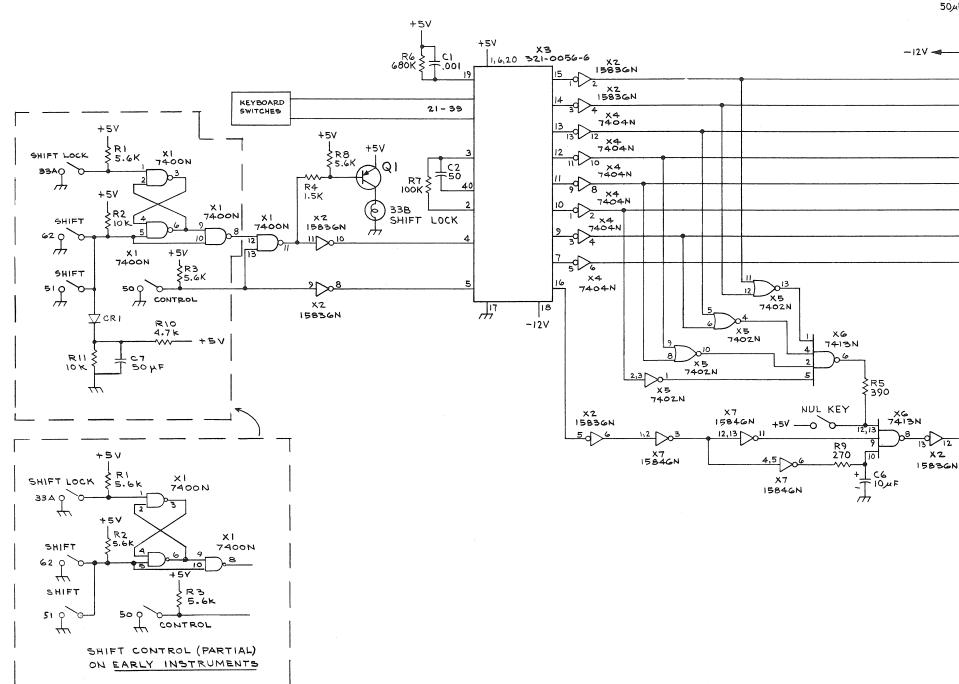

The Strobe and Repeat circuit operates to provide an RKB STROB signal each time a keyboard character is actuated. If the Repeat key is held down while a key is held down, the circuit causes repetitive RKB STROB signals to be generated at a 20 Hz rate.

When a RAW STROB is received, it is applied to U85A, whose other outputs are normally held high. The low from U85A passes through U1B and becomes RKB STROB. Under this circumstance, the RKB STROB duplicates the RAW STROB. If a Keyboard key is held down continuously, the RAW STROB remains high and holds the RKB STROB high. However, if the Repeat key is held down, the RPT KY input turns Q1 off, placing a high at the Q3 gate. C33 charges through R33 until Q3 goes into conduction. This permits C33 to discharge through L37 and the Q3 gate junction. When C33 discharges sufficiently, Q3 again turns off and C33 starts another charge cycle. The positive pulse that occurs when Q3 goes into conduction is applied to U23A, where its trailing edge causes U23A to change states. The U23A configuration is such that its pin 5 output changes state for each input pulse from Q3. This results in the pin 1 input of U85A going alternately low and high at a 10 Hz rate. This causes the RKB STROB output to be interrupted ten times a second, even though the RAW STROB input signal remains high.

KB Click Circuit. The outputs from U85A are also applied to the input of U5. Each negative input into U5 causes it to deliver a 200  $\mu$ s (approximate) positive pulse through R5 and R42 to the Bell circuit. This causes the output speaker to emit a short pulse, or "click".

Bell Circuit. The Bell circuit can be separated into three sub-circuits . . . . the Multivibrator, the Gating section and the Amplifier. The Multivibrator is a unijunction diode controlling a D latch to generate push-pull output signals. The pulses from Q45 causes the U23B outputs to continuously change state. The push-pull outputs of U23B are applied to opposite sides of output transistors Q47 and Q49. Except when a Bell signal has been commanded, Q47 and Q49 are without current, and the push-pull outputs from U23B can go no further. However, when a BEL X or a RING signal is received, it causes the U83A output to go low, turning Q53 on. This provides drive to Q51, supplying current to Q47 and Q49. Q47 and Q49 alternately turn on and off, supplying the Bell signal to the operational amplifier circuit. The operational amplifier drives the BELL SPKR line, producing an audible output.

When the  $\overline{\text{BEL X}}$  or  $\overline{\text{RING}}$  signal is made available to U83B, it not only turns Q53 and Q51 on, it also provides drive to Q63. When Q63 turns on, its low output provides a low to U83A. This causes U83A to produce a high output, which turns Q53 off. During the time that Q53 was turned on, C96 accumulated a charge. With Q53 turned off, the long time constant of C96-R96 holds Q51 in conduction for about one-half second. Then Q51 turns off, ending the audible output.

Initial and Home Circuit. The object of this circuit is to provide an INITIAL signal at turn-on, and to generate a HOME signal whenever a HOME KY signal is received. At turn-on, the +5 V supply builds up, applying a positive voltage to the base of Q41. Until C101 charges, it holds Q41 cut off. This holds Q43 cut off, applying a high to U1C and a low to U81A and U81B. While this condition exists, a HOME and an INITIAL signal occur. Approximately 100 ms later, C101 is charged sufficiently to place Q41 in conduction, causing Q43 to conduct. This removes the high from U1C, ending the output pulses.

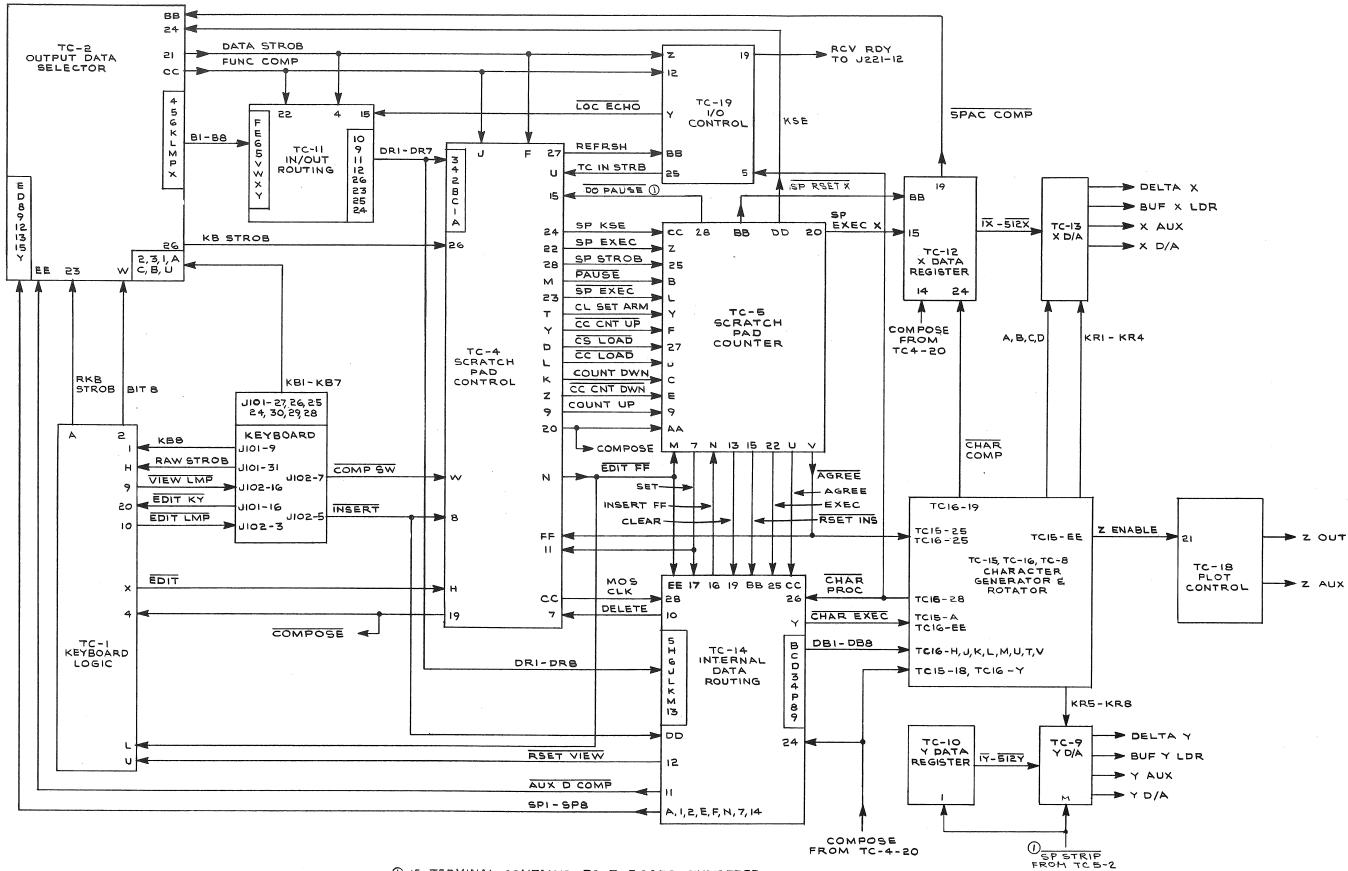

# Output Data Selector TC-2 (Circuit Card 670-1436-01)

The Output Data Selector circuit card performs several functions. It provides clock signals, develops a KB STROB, a FUNC COMP signal, a DATA STRB signal, and makes data bits available to the rest of the Terminal. The circuits that perform these functions are the Clock circuit, the KB Strobe circuit, the Function Complete circuit, Multiplexer Control circuit, Data Multiplexers, the Data Strobe circuit, and the TTY DEL and Closing Bracket Control circuit.

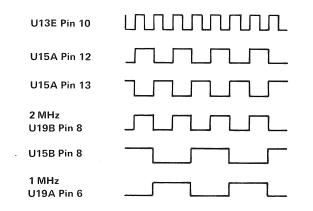

**Clock Circuit.** The 4 MHz signal developed by the crystal-controlled multivibrator is applied to U13E, which provides a square wave through U13D to clock the U15A and U15B flip-flops. U15A divides the 4 MHz by 2 to provide a symmetrical 2 MHz clock for the rest of the Terminal. The output of U15A is also sent to U15B, where it is again divided by 2 to provide a 1 MHz clock.

Keyboard Strobe Circuit. When a keyboard character is struck, the RKB STROB line goes high. The low from U11C one-sets U37B. The next negative transition of the 1 MHz clock one-sets U39A, generating KB STROBE. The next 1 MHz negative transition one-sets U39B, causing it to zero-set U37B. The next 1 MHz negative transition zero-sets U39A, placing a low on the J input of U39B. U39B then has lows on the J and K inputs and remains in the one-set condition until zero-set (via U7A) by the Function Complete circuit.

**Function Complete Circuit.** The Function Complete circuit consists of several negative input OR gates which respond to any one of a number of low input signals. Two outputs are derived from this circuit; one is the FUNC COMP signal, and the other is a signal for resetting the KB Strobe circuit. Any one of the six input signals can cause a reset signal to be sent to the KB Strobe circuit. All except the XMIT COMP signal cause a FUNC COMP signal to be generated.

**Multiplexers.** These devices are provided with A and B control signals to determine which input data (C0, C1, C2) will control the output of its respective section. BA combinations of 00, 01, 10 will engage C0, C1, C2 respectively.

**Multiplexer Control Circuit.** This circuit provides two signals to each of the multiplexers, determining which input will control the outputs. When a keyboard signal is entered, the KB STROBE causes a low from U35C, which causes a low from U5B. The U5A output remains high. This combination permits keyboard input data (KB1, etc) to appear at the output of the multiplexers.

During Scratch Pad Send operation, SEND goes high and applies lows to the A and B inputs of the multiplexers, causing Scratch Pad data (SP1, etc) to leave the multiplexers.

In auxiliary operation, IN AUX is low. AUX STROB generates a low from U35A, which places a low on the B inputs while the A inputs remains high. Auxiliary data (A1, etc) then passes through the multiplexers.

Data Strobe Circuit. The Data Strobe Circuit provides a DATA STRB whenever Keyboard or Auxiliary data is being passed through the multiplexers. During Scratch Pad transmission, SP XMT STR must go low to cause DATA STRB.

**TTY DEL and Closing Bracket Control Circuit.** The purpose of this circuit is to limit the output during TTY operation so that output bit B6 remains low at all times except when the character DEL or Closing Bracket is being transmitted. In essence, the circuit has no effect when TTY is low. Notice that TTY is applied to U35B. If it is low, it causes U35B to have a high output, causing the U5C output to follow the KB6 input. Since the U5C output is applied to the 2C2 input of U27, it has the effect of applying KB6 directly to the multiplexer.

When Teletype Mode is selected, TTY is high. Now U35B is controlled either by the KB7 input or by the U31A output. The B6 output follows the KB6 input as long as KB7 is low. When KB7 is high, the U35B output can only go high when the KB1, KB3, KB4, KB5, and KB6 combination indicates that a DEL or Closing Bracket is being generated. During those times, the U31A output goes low, causing U35B to place a high on U5C, permitting KB6 to again control the B6 output via U5C and U27.

# Output Data Selector TC-2 (Circuit Card 670-1436-00)

The Output Data Selector circuit card performs several functions. It provides clock signals, develops a KB STROB, a FUNC COMP signal, a DATA STRB signal, and makes data bits available to the rest of the Terminal. The circuits that perform these functions are the Clock circuit, the KB Strobe circuit, the Function Complete circuit, Gate Enabling circuit, Keyboard Input Gates, AUX Input Gates, Scratch Pad Send Gates, the Data Strobe circuit and the TTY DEL and Closing Bracket Control circuit.

**Clock Circuit.** The 4 MHz signal developed by the crystal-controlled multivibrator is applied to Q7, which provides a square wave through U7A to clock the U35A and U35B flip-flops. U35A divides the 4 MHz by 2 to provide a symmetrical 2 MHz clock for the rest of the Terminal. The output of U35A is also sent to U35B, where it is again divided by 2 to provide a 1 MHz clock.

**KB Strobe Circuit.** When a keyboard character is struck, the RKB STROB line goes high and combines with the other three highs on U55 to provide a low output. This causes U13A to become one-set. The next negative-going excursion of the 1 MHz clock pulse causes U15 to become one-set, causing the KB STROB line to go high. The next negative transition of the 1 MHz clock pulse zero-sets U15 and one-sets U13B. The zero output from U13B goes to U15, where it disables U15 in the zero-set condition. U13B now has two low inputs and remains in its one-set condition. The next positive excursion of the 1 MHz clock causes U33D to provide a low output, which zero-sets U13A to prepare it for the next input signal. U13B remains in its one-set condition until such time as the Function Complete circuit provides it with a zero-setting signal.

**Function Complete Circuit.** The Function Complete circuit consists of several negative input OR gates which respond to any one of a number of low input signals. Two outputs are derived from this circuit; one is the FUNC COMP signal, and the other is a signal for resetting the KB Strobe circuit. Any one of the six input signals can cause a reset signal to be sent to the KB Strobe circuit. All except the XMIT COMP signal cause a FUNC COMP signal to be generated.

Gate Enabling Circuit. The Gate Enabling circuit permits one of the three sets of gates to be enabled at a given time. The SEND input signal takes precedence. Whenever it exists, it enables the Scratch Pad Send Gates and disables the KB Input Gates and the Aux Input Gates.

When the SEND signal is low and IN KB AUX signal exists, U9A has two high inputs. Just before a KB STROB is developed in response to an RKB STROB, U13A applies another high signal to U9A. This sends a high to the KB Input Gates, permitting KB Data bits to pass through the input gates.

Two highs exist on U9C if SEND and IN AUX are low. When an AUX STROB arrives at the circuit, U9C provides a low output, causing U11C to place a high on the Aux Input Gates. The auxiliary data bits are then permitted to pass through. Data Strobe Circuit. The Data Strobe Circuit provides a DATA STRB whenever data is being passed through any one of the three input gate circuits. When keyboard data is being input, highs are applied to U33A during KB STROB time, sending a low to U51A to generate the DATA STRB signal. When auxiliary inputs are being provided, the AUX STROB causes U33B to generate the DATA STRB. During Scratch Pad transmission, the low SP XMT STR signal causes the DATA STRB.

TTY DEL and Closing Bracket Control Circuit. The purpose of this circuit is to limit the output during TTY operation so that output bit B6 remains low at all times except when the character DEL or Closing Bracket is being transmitted. In essence, the circuit has no effect when TTY is low. Notice that TTY is applied to U9B. If it is low, it causes U9B to have a high output, causing the U7C output to follow the KB6 input. Since the U7C output is applied to U27D, it has the effect of applying KB6 directly to U27D.

When Teletype Mode is selected, TTY is high. Now U9B is controlled either by the KB7 input or by the U1 output. The B6 output follows the KB6 input as long as KB7 is low. When KB7 is high, the U9B output can only go high when the KB1, KB3, KB4, KB5, and KB6 combination indicates that a DEL or Closing Bracket is being generated. During those times, the U1 output goes low, causing U9B to place a high on U7D, permitting KB6 to again control the B6 output via U7D, U7C, and U27D.

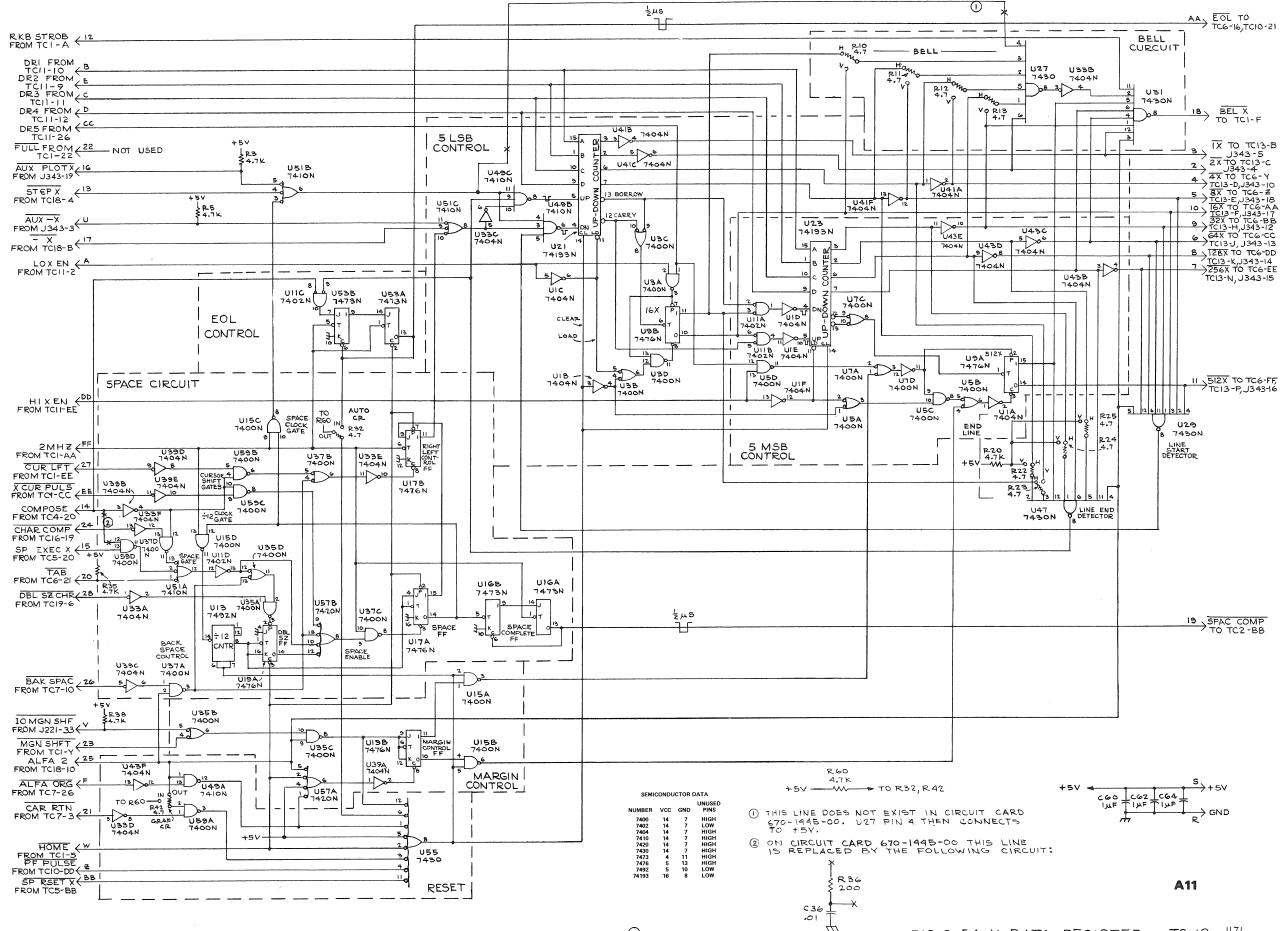

#### Scratch Pad Control TC-4

This circuit card contains most of the circuitry for controlling the Scratch Pad features of the Terminal. When the Scratch Pad has not been selected at the keyboard or by program control, it is essentially a bypass card, and can be represented by the Scratch Pad Bypass drawing which appears on the schematic.

When in Compose Mode, most of the circuitry on the card is interactive, and therefore will be explained as part of an operating sequence rather than an individual circuits.

**a**.

| Ckt. No.     |        | Tektronix<br>Part No.      | Serial/Model<br>Eff | No.<br>Disc | Description                                                           |

|--------------|--------|----------------------------|---------------------|-------------|-----------------------------------------------------------------------|

|              | (      |                            |                     | 8130        |                                                                       |

| RESISTORS    | (cont) |                            |                     |             |                                                                       |

| R154         |        | 317-0272-00                |                     |             | 2.7 k $\Omega$ , 1/8 W, 5%                                            |

| R156         |        | 317-0272-00                |                     |             | 2.7 k $\Omega$ , 1/8 W, 5%                                            |

| R158<br>R159 |        | 317-0473-00                |                     |             | 47 kΩ, 1/8 W, 5%<br>47 kΩ, 1/8 W, 5%                                  |

| R161         |        | 317-0473-00<br>317-0123-00 |                     |             | 47  km, 178  w, 5%<br>12 k $\Omega$ , 1/8 W, 5\%                      |

| R163         |        | 317-0123-00                |                     |             | $47 \ k\Omega, \ 1/8 \ W, \ 5\%$                                      |

| R165         |        | 317-0102-00                |                     |             | $1 k\Omega, 1/8 W, 5\%$                                               |

| R166         |        | 317-0123-00                |                     |             | $12 k\Omega, 1/8 W, 5\%$                                              |

| KT00         |        | 517-0125-00                |                     |             | 12 Rate 1/0 Wy 5%                                                     |

| R168         |        | 317-0223-00                |                     |             | 22 kΩ, 1/8 W, 5%                                                      |

| R171         |        | 317-0123-00                |                     |             | 12 kΩ, 1/8 W, 5%                                                      |

| R173         |        | 317-0104-00                |                     |             | 100 kΩ, 1/8 W, 5%                                                     |

| R175         |        | 317-0474-00                |                     |             | 470 kΩ, 1/8 W, 5%                                                     |

| R177         |        | 317-0471-00                |                     |             | 470 Ω, 1/8 W, 5%                                                      |

| R178         |        | 317-0101-00                |                     |             | 100 A, 1/8 W, 5%                                                      |

| R179         |        | 317-0123-00                |                     |             | 12 kΩ, 1/8 W, 5%                                                      |

| INTEGRATED   | CIPCUT | тs                         |                     |             |                                                                       |

| Ul           | CINCUI | 156-0058-00                |                     |             | Hex. invert, replaceable by T.I. SN7404N                              |

| U5           |        | 156-0072-00                |                     |             | Monostable multi, replaceable by T.I. SN7404N                         |

| U7           |        | 156-0049-00                |                     |             | Op ampl, replaceable by Fairchild µA741C                              |

| U9           |        | 156-0094-00                |                     |             | Dual peripheral driver, replaceable by T.I. SN75451P                  |

|              |        |                            |                     |             |                                                                       |

| U19          |        | 155-0031- <b>0</b> 0       |                     |             | Quad timing logic                                                     |

| U23          |        | 156-0041-00                |                     |             | Dual D flip-flop, replaceable by T.I. SN7474N,                        |

| U29          |        | 156-0094-00                |                     |             | Dual peripheral driver, replaceable by T.I. SN75451P                  |

| U39          |        | 156-0030-00                |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N                        |

| U51          |        | 156-0043-00                |                     |             | Quad 2-input NOR gate, replaceable by T.I. SN7402N                    |

| U57          |        | 155-0031-00                |                     |             | Quad timing logic                                                     |

| U59          |        | 156-0030-00                |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N                        |

| U81          |        | 156-0094- <b>0</b> 0       |                     |             | Dual peripheral driver, replaceable by T.I. SN75451P                  |

| U8 3         |        | 156-0034-00                |                     |             | Dual 4-input gate, replaceable by T.I. SN7420N                        |

| U85          |        | 156-0034-00                |                     |             | Dual 4-input gate, replaceable by T.I. SN7420N                        |

| U87          |        | 156-0032-00                |                     |             | 4-bit binary counter, replaceable by T.I. SN7493N                     |

| <b>U95</b>   |        | 156-0081-00                | ·                   |             | Retriggerable monostable multivibrator, replaceable by Fairchild 9601 |

B

0

.

a

| Ckt. No.         | Tektronix<br>Part No.         | Serial/Model<br>Eff | No.<br>Disc | Description                                                             |

|------------------|-------------------------------|---------------------|-------------|-------------------------------------------------------------------------|

| ASSEMBLY,        |                               |                     |             |                                                                         |

| A2               | 670-1436-01                   |                     |             | OUTPUT DATA SELECTOR TC#2 Circuit Card                                  |

| CAPACITORS       |                               |                     |             |                                                                         |

| C1               | 281-0546-00                   |                     |             | 330 pF, 500 V, $\pm 10\%$                                               |

| C3               | 283-0602-00                   |                     |             | 53 pF, 300 V, $\pm 3\%$                                                 |

| C5               | 283-0602-00                   |                     |             | 53 pF, 300 V, $\pm 3\%$<br>53 pF, 300 V, $\pm 3\%$                      |

| C30              | 290-0530-00                   |                     |             | 68 $\mu$ F, 6 V, $\pm 20\%$                                             |

| C31              | 283-0177-00                   |                     |             | 1 $\mu$ F, 25 V, +80%-20%                                               |

| C32              | 283-0177-00                   |                     |             | 1 $\mu$ F, 25 V, +80%-20%                                               |

| C33              | 283-0177-00                   |                     |             | 1 $\mu$ F, 25 V, +80%-20%                                               |

| C34              | 283-0177-00                   |                     |             | 1 $\mu$ F, 25 V, +80%-20%                                               |

| C37              | 290-0530-00                   |                     |             |                                                                         |

| C38              | 283-0177-00                   |                     |             | 68 μF, 6 V, ±20%<br>1 μF, 25 V, +80%-20%                                |

| 050              | 203-0177-00                   |                     |             | 1 μr, 25 V, 100%-20%                                                    |

| INDUCTORS        | 100 0005 00                   |                     |             |                                                                         |

| L30              | 108-0395-00                   |                     |             | 64 μH                                                                   |

| L34              | 108-0395-00                   |                     |             | 64 µH                                                                   |

| L37              | 108-0395-00                   |                     |             | 64 μH                                                                   |

| L50              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L51              | 108-0551-00                   |                     |             | 14 μH                                                                   |

| L54              | 108-0551-00                   |                     |             | 14 µH                                                                   |

| L56              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L58              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L60              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L62              | 108-0551-00                   |                     |             | 14 µH                                                                   |

| L64              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L66              | 108-0551-00                   |                     |             | $14 \mu H$                                                              |

| L68              | 108-0551-00                   |                     |             | 14 μH                                                                   |

| L70              | 108-0551-00                   |                     |             | 14 μH                                                                   |

| RESISTORS        |                               |                     |             |                                                                         |

| R1               | 315-0681-00                   |                     |             | 680 Ω, 1/4 W, 5%                                                        |

| R3               | 321-0147-00                   |                     |             | 332 A, 1/8 W, 1%                                                        |

| R5               | 321-0147-00                   |                     |             | 332 Ω, 1/8 W, 1%                                                        |

| R7               | 315-0681-00                   |                     |             | 680 Ω, 1/4 W, 5%                                                        |

| R10              | 321-0097-00                   |                     |             | 100 Ω, 1/8 W, 1%                                                        |

| R20              | 315-0472-00                   |                     |             | 4.7 kΩ, 1/4 W, 5%                                                       |

| R25              | 315-0472-00                   |                     |             | 4.7 kΩ, 1/4 W, 5%                                                       |

| INTEGRATED CIRCU | ITS                           |                     |             |                                                                         |

| U5               | 156 <b>-</b> 0129 <b>-</b> 00 |                     |             | Quad 2-input positive & gate, replaceable by T.I. SN7408N               |

| U <b>7</b>       | 156-0058-00                   |                     |             | Hex. invert, replaceable by T.I. SN7404N                                |

| U11              | 156-0047-00                   |                     |             | Triple 3-input gate, replaceable by T.I. SN7410N                        |

| U13              | 156-0058-00                   |                     |             | Hex. invert, replaceable by T.I. SN7404N                                |

| U15              | 156-0039-00                   |                     |             | Dual J-K flip-flop, replaceable by T.I. SN7473N                         |

| U19              | 156 <b>-</b> 0156 <b>-</b> 00 |                     |             | Dual 4-input positive or/nor clock driver,                              |

| U21              | 156-0098-00                   |                     |             | replaceable by MC1023L<br>Dual 4-line to 1-line, data select multiplex, |

| 021              | 190-0090-00                   |                     |             | replaceable by T.I. SN74153N                                            |

| U23              | 156-0098-00                   |                     |             | Dual 4-line to 1-line, data select multiplex,                           |

| 025              | 100-000-00                    |                     |             | replaceable by T.I. SN74153N                                            |

| U27              | 156-0098-00                   |                     |             | Dual 4-line to 1-line, data select multiplex,                           |

| 021              | 100-00-00                     |                     |             | replaceable by T.I. SN74153N                                            |

| U29              | 156-0098-00                   |                     |             | Dual 4-line to 1-line, data select multiplex,                           |

| 047              | 100-00-00                     |                     |             | replaceable by T.I. SN74153N                                            |

| U31              | 156-0034-00                   |                     |             | Dual 4-input gate, replaceable by T.I. SN7420N                          |

| U35              | 156-0047-00                   |                     |             | Triple 3-input gate, replaceable by T.I. SN7420N                        |

|                  |                               |                     |             | TTPLE 5 TAPAC BACC, TEPTACCADIE by 1.1. DN/410M                         |

s.

| Ckt. No.       | Tektronix<br>Part No. | Serial/Model<br>Eff | No.<br>Disc | Description                                     |

|----------------|-----------------------|---------------------|-------------|-------------------------------------------------|

| INTEGRATED CIF | RCUITS (cont)         | -                   |             |                                                 |

| U37            | 156-0039-00           |                     |             | Dual J-K flip-flop, replaceable by T.I. SN7473N |

| U39            | 156-0039-00           |                     |             | Dual J-K flip-flop, replaceable by T.I. SN7473N |

| CRYSTAL        |                       |                     |             |                                                 |

| ¥10            | 158-0056-00           |                     |             | 4 MHz                                           |

| ASSEMBL        | 1                     |                     |             |                                                 |

| A2             | 670-1436-00           |                     |             | OUTPUT DATA SELECTOR TC#2 Circuit Car           |

| CAPACITORS     |                       |                     |             |                                                 |

| C12            | 283-0177-00           |                     |             | 1 μF, Cer, 25 V, +80%-20%                       |

| C13            | 281-0510-00           |                     |             | 22 pF, Cer, 500 V, 20%                          |

| C18            | 283-0177-00           |                     |             | 1 $\mu$ F, Cer, 25 V, +80%-20%                  |

| C20            | 283-0187-00           |                     |             | 0.047 $\mu$ F, Cer, 400 V, 10%                  |

| C36            | 281-0510-00           |                     |             | 22 pF, Cer, 500 V, 20%                          |

| C52            | 283-0177-00           |                     |             | 1 μF, Cer, 25 V, +80%-20%                       |

| C53            | 283-0177-00           |                     |             | 1 $\mu$ F, Cer, 25 V, +80%-20%                  |

| C54            | 283 <b>-</b> 0177-00  |                     |             | 1 $\mu$ F, Cer, 25 V, +80%-20%                  |

| C55            | 283-0177-00           |                     |             | 1 $\mu$ F, Cer, 25 V, +80%-20%                  |

| C56            | 283-0177-00           |                     |             | 1 $\mu$ F, Cer, 25 V, +80%-20%                  |

| C57            | 283-0177-00           |                     |             | 1 $\mu F$ , Cer, 25 V, +80%-20%                 |

| <u>Ckt</u> . | No.         | Tektronix<br>Part No. | Serial/Model<br>Eff | No.<br>Disc | Description                                      |

|--------------|-------------|-----------------------|---------------------|-------------|--------------------------------------------------|

| SCD.         | DIODE       |                       |                     |             |                                                  |

| ָּכ <b>ּ</b> | CR20        | 152-0185-00           |                     |             | Silicon, replaceable by 1N4152                   |

| INDU         | JCTORS      |                       |                     |             |                                                  |

| L            | .13         | 108-0395-00           |                     |             | 64 μH                                            |

| I            | 150         | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 152         | 108-0551-00           |                     |             | 14 μH                                            |

| I            | -54         | 108-0551-00           |                     |             | 14 µH                                            |

| I            | 156         | 108-0551-00           |                     |             | 14 µH                                            |

| L            | -58         | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 260         | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 62          | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 64          | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 266         | 108-0551-00           |                     |             | 14 μH                                            |

| I            | 68          | 108-0551-00           |                     |             | 14 μH                                            |

| I            | <b>17</b> 0 | 108-0551-00           |                     |             | 14 µH                                            |

| TRAN         | SISTOR      |                       |                     |             |                                                  |

| C            | 27          | 151-022 <b>3</b> -00  |                     |             | Silicon, NPN, 2N4275                             |

| RESI         | ISTORS      |                       |                     |             |                                                  |

| F            | R10         | 317-0102-00           |                     |             | 1 kΩ, 1/8 W, 5%                                  |

| F            | R11         | 317-0202-00           |                     |             | 2 kΩ, 1/8 W, 5%                                  |

| F            | R13         | 317-0431-00           |                     |             | 430 Ω, 1/8 W, 5%                                 |

| F            | R15         | 317-0621-00           |                     |             | 620 Ω, 1/8 W, 5%                                 |

| F            | R16         | 317-0182-00           |                     |             | 1.8 kΩ, 1/8 W, 5%                                |

| F            | R17         | 317-0102-00           |                     |             | 1 kΩ, 1/8 W, 5%                                  |

| F            | R18         | 317-0682-00           |                     |             | 6.8 kΩ, 1/8 W, 5%                                |

| F            | R20         | 317-0222-00           |                     |             | 2.2 kΩ, 1/8 W, 5%                                |

| F            | R22         | 317-0222-00           |                     |             | 2.2 kn, 1/8 W, 5%                                |

| F            | R30         | 317-0472-00           |                     |             | 4.7 kΩ, 1/8 W, 5%                                |

| F            | R34         | 317-0472-00           |                     |             | 4.7 kΩ, 1/8 W, 5%                                |

| F            | R40         | 317-0472-00           |                     |             | 4.7 kΩ, 1/8 Ŵ, 5%                                |

| F            | R52         | 317-0102-00           |                     |             | 1 kΩ, 1/8 W, 5%                                  |

| F            | R53         | 317-0102-00           |                     |             | 1 kΩ, 1/8 W, 5%                                  |

| F            | R54         | 317-0102-00           |                     |             | 1 kΩ, 1/8 W, 5%                                  |

| INTE         | EGRATED CIR | CUITS                 |                     |             |                                                  |

| τ            | J1          | 156-0035-00           |                     |             | 8-input gate, replaceable by T.I. SN7430N        |

| τ            | J5          | 156-0033-00           |                     |             | Linear, RF/IF amp1, replaceable by RCA CA3028A   |

| τ            | J <b>7</b>  | 156-0030-00           |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N   |

| τ            | J <b>9</b>  | 156-0047-00           |                     |             | Triple 3-input gate, replaceable by T.I. SN7410N |

| τ            | <b>J11</b>  | 156-0058-00           |                     |             | Hex. invert, replaceable by T.I. SN7404N         |

| τ            | J <b>13</b> | 156-0039-00           |                     |             | Dual J-K flip-flop, replaceable by T.I. SN7473N  |

| τ            | J15         | 156-0038-00           |                     |             | J-K flip-flop, replaceable by T.I. SN7472N       |

| τ            | J2 <b>3</b> | 156-0030-00           |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N   |

| τ            | J25         | 156-0030-00           |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N   |

|              | J27         | 156-0030-00           |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N   |

| τ            | J29         | 156-0030-00           |                     |             | Quad 2-input gate, replaceable by T.I. SN7400N   |

,

Fig. 5-37. KB STROBE timing. (TC-2 Circuit card 670-1436-01).

Fig. 5-38. Clock timing (TC-2). Circuit card (670-1436-01).

TC-2 670-1436-01

4002A DRAWER UNIT AND KEYBOARD MAINTENANCE MANUAL MOD INSERT FOR M18,158 EFFECTIVE AT SN B070630 This modification provides initialization for the Edit circuit.

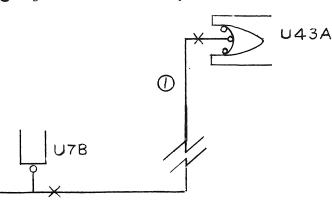

Page 5-46, Fig. 5-41 Near the center of the schematic, remove

+5 V from pin 1 of U43A and add a line from pin 1 of U43A to pin 6 of U7B (bottom, near center). Place an X near each extreme of this line and put a ① adjacent to the line, as shown below.

Add a note to the schematic as follows:

This wire added in later board versions. Pin

1 of U43A was previously connected to +5 V.

MOD INSERT FOR M18,161 Effective at SN B080000-up INCORPORATES NEW CIRCUIT BOARD AND CARDS AS FOLLOWS:

TC-0 670-1522-01

TC-5 670-1438-02

TC-10 670-1443-02

TC-12 670-1445-01

This modification improves Local Edit Send, Page Full operation, and bell operation. It also permits use with scan converters and enables refreshed Scratch Pad operation with synchronous interface units.

MAKE THE FOLLOWING CHANGES:

| SECTION 2: | Replace pages 2-7 through 2-14 with the enclosed pages |

|------------|--------------------------------------------------------|

|            | 2-7 through 2-14A.                                     |

SECTION 4: Change Electrical Parts List as follows: Page 4-9

ASSEMBLY

A4 670-1438-00 B010100 - B079999 SCRATCH PAD COUNTER TC#5 Circuit Card 670-1438-01 B080000

ADD:

| R12 | 315-0472-00 XB080000 | 4.7 kΩ, 1/4 W, 5%                             |

|-----|----------------------|-----------------------------------------------|

| U19 | 156-0131-00 XB080000 | Single 25 MHz, 8-bit, replaceable by SN74164N |

Page 4-16

ASSEMBLY

A9 670-1443-00 B010100 - B079999 Y DATA REGISTER TC#10 Circuit Card 670-1443-01 B080000 - B089999 670-1443-02 B090000 Page 4-18

0

ASSEMBLY

| A11 | 670-1445-00 | B <b>010100 -</b> B <b>079999</b> | X DATA REGISTER TC#12 Circuit Card |

|-----|-------------|-----------------------------------|------------------------------------|

|     | 670-1445-01 | XB <b>080000</b>                  |                                    |

#### REMOVE :

| C36 | 283-0220-00 | B010100 - B079999X | 0.01 $\mu F,$ Cer, 50 V, 20% |

|-----|-------------|--------------------|------------------------------|

| R36 | 315-0201-00 | B010100 - B079999X | 200 A, 1/4 W, 5%             |

Page 1

M18,161/1171

MOD INSERT FOR M18,161 Effective at SN B080000-up

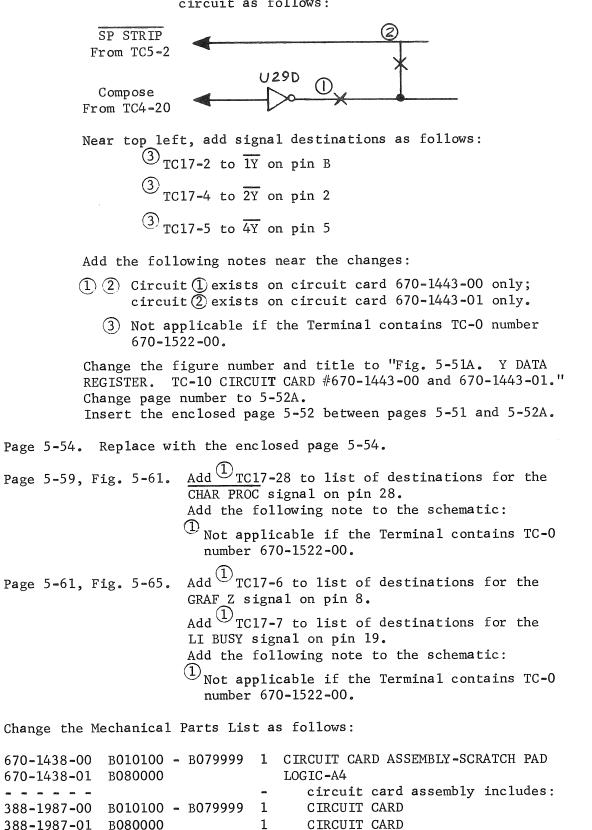

SECTION 5: Page 5-5 - Add DO PAUSE \*P TC5-28 Initiating command for PAUSE

Page 5-8 - Add SP STRIP \*L TC5-2 Sets Y register to Scratch Pad position

Page 5-14 Change J121 pin 19 as follows:

19 REFRSH L TCO4  $27^{(1)}$

Add the following note below the J121 listing:

"<sup>(1)</sup>Not connected on TC-0 number 670-1522-00."

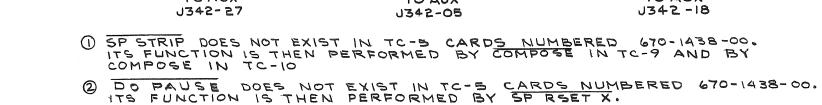

Page 5-21/5-22 Remove and replace with the enclosed page 5-21/5-22

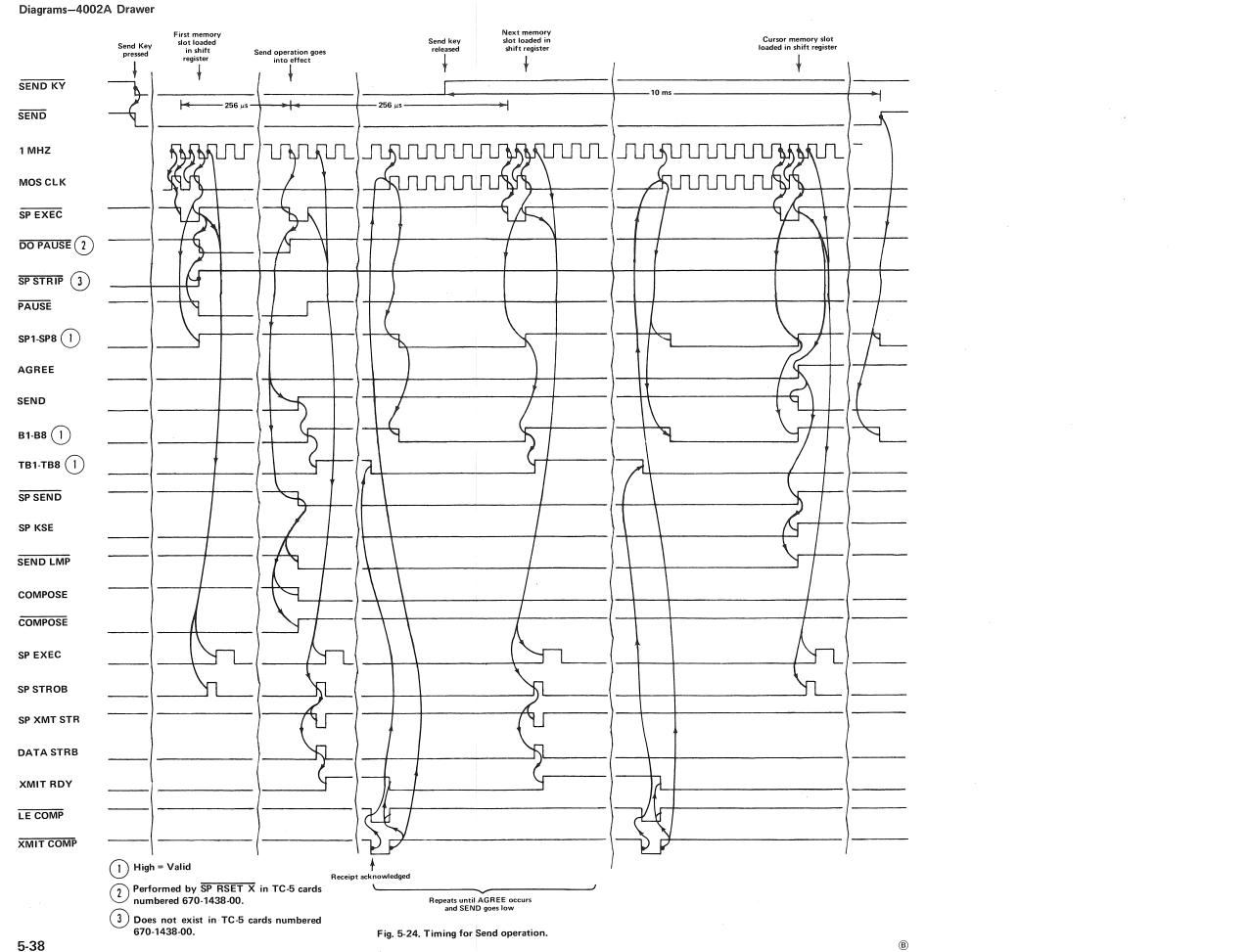

Pages 5-33 through 5-39. Remove and replace with the enclosed pages 5-33 through 5-39.

Page 5-44, Fig. 5-36  $\frac{\text{Add}^{(1)}}{\text{HOME}}$  TC17-1 to list of destinations for the

Add note to the schematic:

(1) Not applicable if the Terminal contains TC-0 number 670-1522-00

Page 5-46, Fig. 5-41 Add <sup>(1)</sup> TC17-8, <sup>(1)</sup> J121-19 to list of destinations for the REFRSH signal on pin 27

Add note to the schematic:

(1) Not applicable if the Terminal contains TC-0 number 670-1522-00

Page 5-47, Fig. 5-42 Fig. 5-43 Change figure number to 5-42A. Near right middle of schematic, change U51A name from SEND INITIATE FF to SEND ENABLE FF. Change figure number and title of schematic to "Fig. 5-43A. SCRATCH PAD COUNTER. TC-5 CIRCUIT CARD #670-1438-00". Change the page number to 5-47

Insert the enclosed page 5-47 between 5-46 and 5-47A.

Page 5-49. Fig. 5-46. Add <sup>(1)</sup> TC17-3 to list of destinations for the DC4 signal on pin U. Add note to the schematic: Not applicable if the Terminal contains TC-0 number 670-1522-00.

Page 5-52, Fig. 5-50. Change figure number to 5-50A.

M18,161/1171

MOD INSERT FOR M18,161 Effective at SN B080000-up

SECTION 6: Page 6-9

Fig. 3-24

Page 5-52, Fig. 5-51 At the top-left of the schematic, change the circuit as follows:

M18,161/1171

MOD INSERT FOR M18,161

SECTION 6:

| Fig32 | 670-1443-00<br>670-1443-01<br>670-1443-02                | B010100 - B079999<br>B080000 - B089999<br>B090000           | 1                | CIRCUIT CARD ASSEMBLY-Y DATA<br>REGISTER A9                                                                     |

|-------|----------------------------------------------------------|-------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|

|       | 388-1992-00<br>388-1992-01                               | B010100 - B089999<br>B090000                                | -<br>1<br>1      | circuit card assembly includes:<br>CIRCUIT CARD<br>CIRCUIT CARD                                                 |

| Fig34 | 670-1445-00<br>670-1445-01<br>388-1994-00<br>388-1994-01 | B010100 - B079999<br>B080000 - B079999<br>B080000 - B079999 | 1<br>-<br>1<br>1 | CIRCUIT CARD ASSEMBLY-X DATA<br>REGISTER A11<br>circuit card assembly includes:<br>CIRCUIT CARD<br>CIRCUIT CARD |

Modification entered in manual\_\_\_\_\_

Date

Insert these instructions pages in the back of the manual.

Page 4

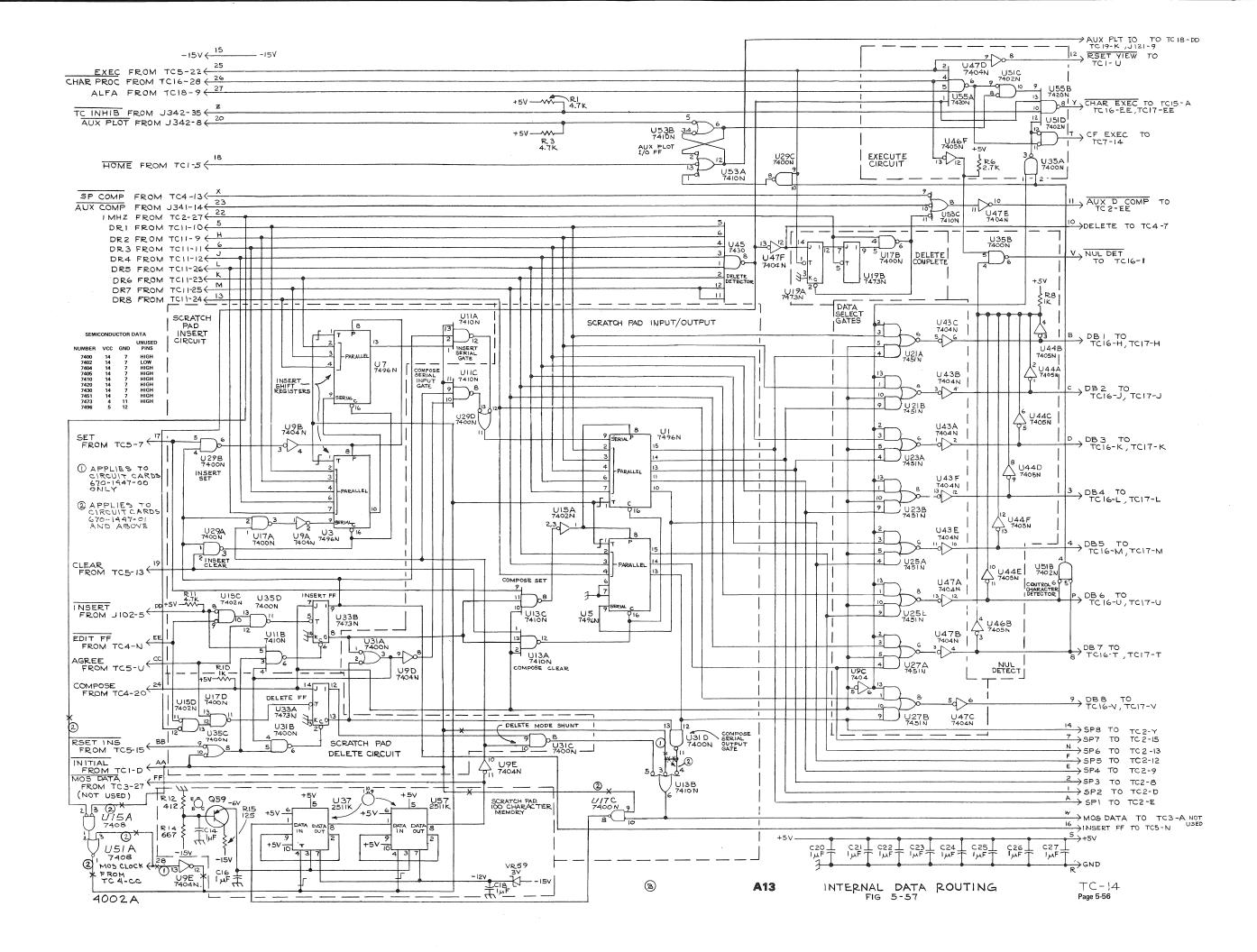

If it is desired to shift from Unrefreshed Scratch Pad operation to Edit Mode under program control, the characters ESC ? must be sent to Terminal. The ESC character arms the U47B FF as previously explained and the ? character causes a signal to be routed through U2, U53D, and U51F to set the U33A output high. The high is blocked from U29A by CR22. After the ? is loaded into the memory, eight MOS CLK pulses occur and U7A develops a low output which goes to U43A to set the U33A output low. This low is felt at U29A, sending a signal through U45C, U51E and U53A to one-set Refresh FF U27A. The U33A output is also routed through U53D and U51F to the Edit Control circuit to one-set EDIT FF U7B. Edit operation is then as previously explained.

Program command sequence ESC C clears the Scratch Pad memory if in Unrefreshed Mode. ESC arms the U47B FF and the C causes a signal to pass through U23, Clear Select gate U53C, U14A and into U31 where it generates a 1 ms pulse. This 1 ms pulse affects the circuit in the same manner as previously explained.

Certain Interface Units are capable of causing the Unrefreshed Scratch Pad contents to be sent directly to the Terminal screen. This is accomplished by sending a SEND SCRN signal to TC-4 and TC-5. The SEND SCRN signal into TC-4 causes Send Screen FF U27B to one-set, enabling U15B and turning Q5 on. U15B sends out an INHIBIT X signal. Q5 disables U5A and enables U5C. SEND SCRN is also routed through U29A, U45C, U51E, and U53A to one-set Refresh FF U27A. As soon as the first character in memory is contained in the Shift Register, an SP SEND signal is received from TC-5. The SP SEND signal goes through U45A and U25F to zero-set U27A. SP SEND also goes through U59F to place an enabling voltage on U9D.

TC-2 sends a FUNC COMP signal to TC-4 to acknowledge receipt of the data transmitted by the Scratch Pad. This is applied to U5C. The output from U5C is routed through U9A and U9D to place a low pulse on MOS CLK Enable gate U11A. This results in eight MOS CLK pulses, which advance the next character into the Shift Register. An SP STROB and an SP EXEC signal follow the MOS CLK pulses. Another character is transmitted to the SCREEN and the operation is repeated until all characters are transmitted. The SP SEND signal then goes high, causing SEND SCREEN FF U27B to return to its zero-set condition. Q5 cuts off and U5C becomes disabled.

The Terminal can also be switched from the Unrefreshed Scratch Pad Mode to the Direct Mode by pressing the Home button. The HOME signal is applied to U14C. As soon as the Position Counter agrees with the Cursor Counter (on TC-5), AGREE is received by TC-4, causing a signal from U14C and U59E. This is routed to both the Refresh SP FF and the Unrefreshed SP FF, resetting them for Direct Mode operation.

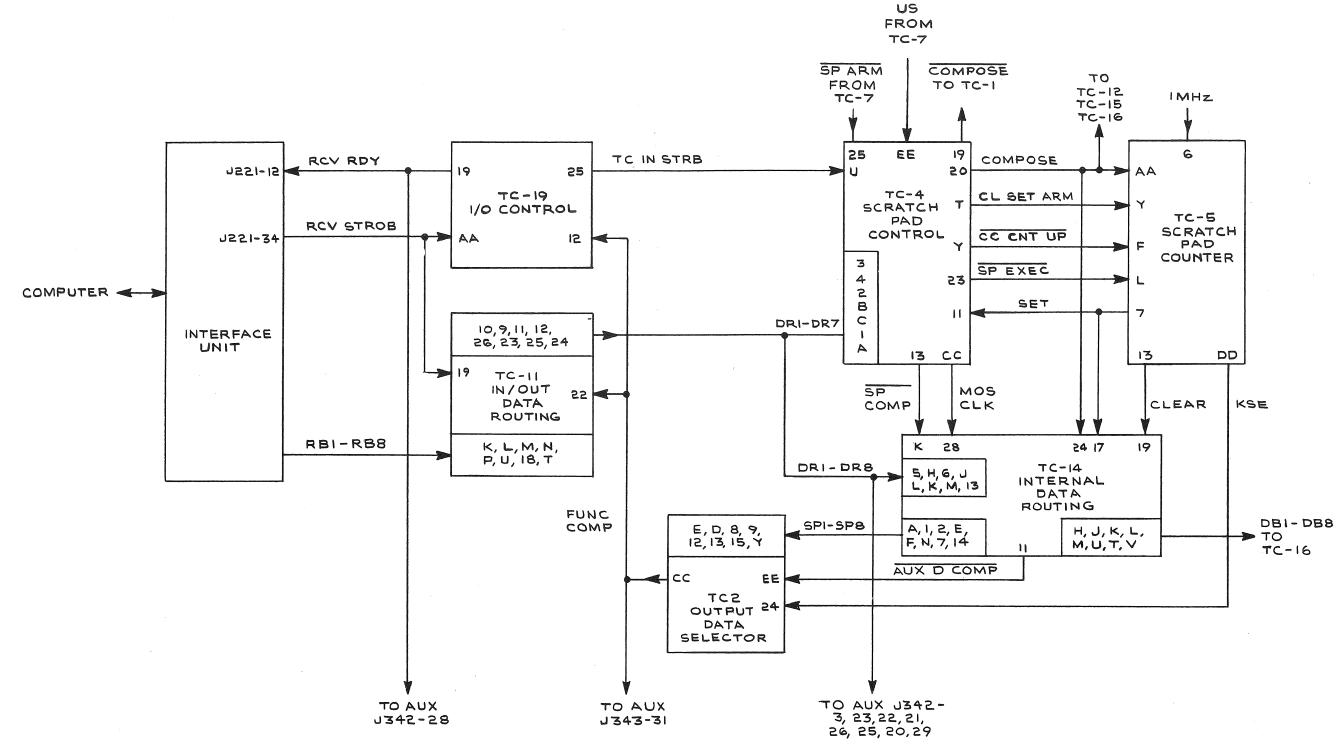

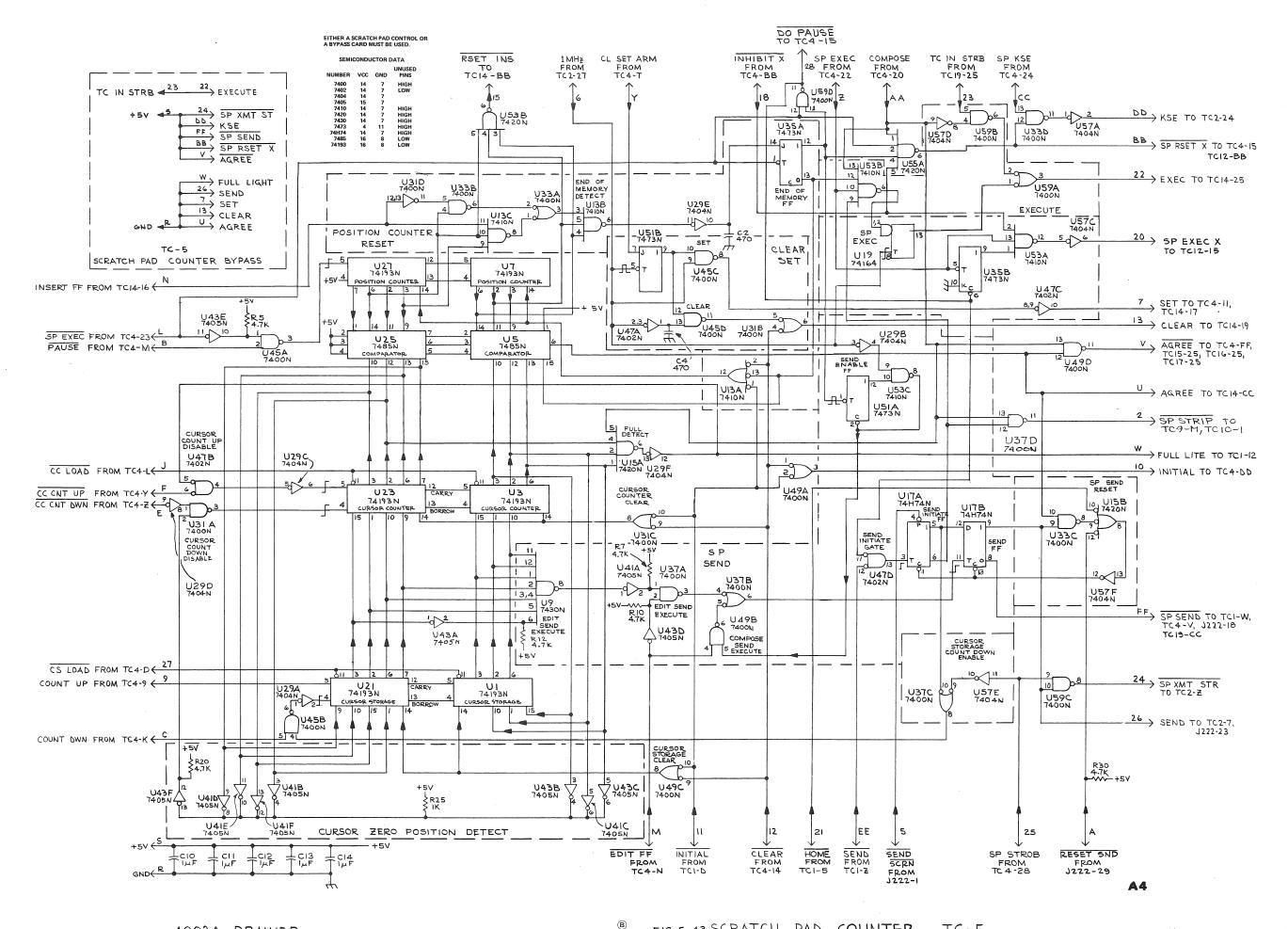

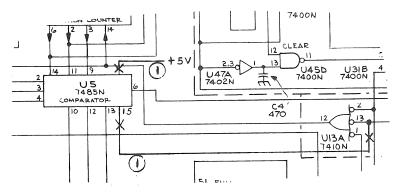

#### Scratch Pad Counter TC-5

The Scratch Pad Counter circuit contains the Position Counter Registers, the Cursor Counter Registers, and the Cursor Storage Registers which are used in conjunction with the Scratch Pad Memory circuit. Other circuitry dependent upon these counters is also included on this diagram. When the Scratch Pad circuit is not in use, the card can be represented as the Scratch Pad Counter Bypass card, which is also shown on the schematic diagram.

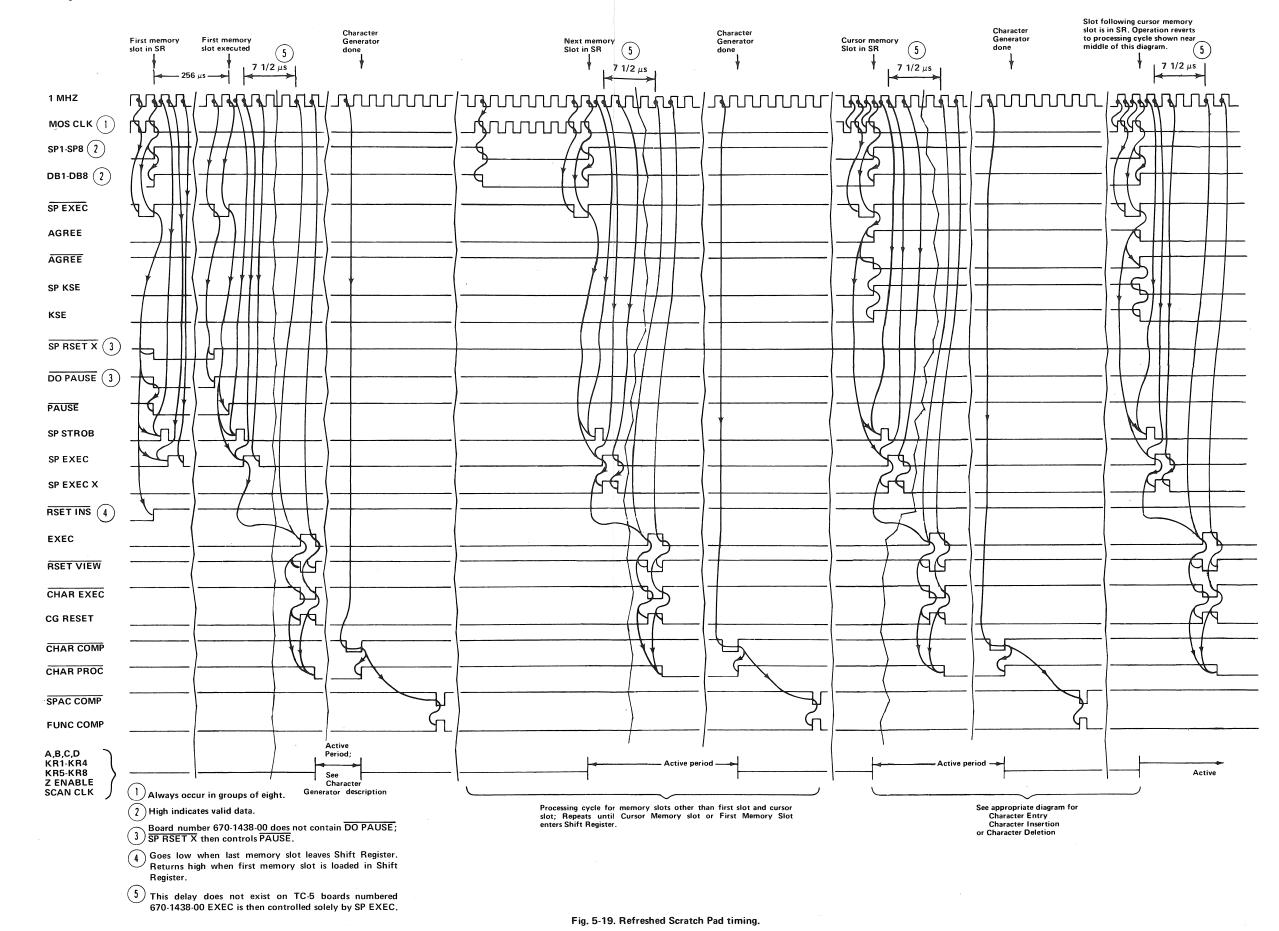

As soon as the Terminal has been initialized, the INITIAL signal received on TC-5 resets the circuitry. When the Terminal is placed in Refreshed Compose Mode, SP EXEC signals are received continuously every 256 microseconds. Each one of these is routed through U43E and U45A to the Position Counter circuit.

The purpose of the Position Counters is to count the Scratch Pad Memory character position which is contained in the Shift Register on TC-14, and it is incremented every time that an SP EXEC signal is received. The Cursor Counter is incremented each time a character is inserted into the Scratch Pad Memory circuit. The CC CNT UP signal is passed through Cursor Count Up Disable gate U47B and through U29C to increment the counter. Assume that thirty characters have been stored in the Scratch Pad Memory. The Cursor Counter would contain the digital equivalent of thirty. Each time the Position Counter reaches that value, the A=B output of comparator U5 would cause U49D to generate the  $\overrightarrow{AGREE}$  signal.

This paragraph pertains only to TC-5 circuit cards numbered 670-1438-01 and above. If an insert condition does not exist, low pulses are generated by U55B and U13B each time the Position Counters reach one hundred. (If insert conditions exists, U13B generates a low output when the Position Counter reaches 101. This accounts for the added Insert shift register on TC-14.) The U53B output forms the RSET INS signal, while the U13B output is processed through the TC-5 circuit as an "end of memory" signal. This signal causes a high to be applied to the J input of U35A. The trailing edge of the next SP EXEC signal causes U35A to one-set. This causes several things to happen. The one output provides enabling voltage to U55A and U59D. The low from the zero output goes to U55B to disable it, and goes to U13A to reset the position counters to zero. The low from U35A also goes to U5 during this time to inhibit AGREE signals. (With pin 1 high and pin 15 low, the comparator cannot generate an AGREE output.) When SP EXEC returns high, it generates an SP RSET X from U55A and a DC PAUSE from U59D. SP RSET X goes to TC-12 to reset the X registers. DO PAUSE goes to TC-4 to inhibit MOS CLK pulses. It is also used in TC-5 circuitry

#### Detailed Circuit Description-4002A Drawer

to zero-set U35B (to inhibit SP EXEC X pulses) and to one-set U17A if the SEND signal is low. (Send operation is discussed later.) U17A is normally zero-set, supplying enabling voltages to U37D and U55B. The U37D output is thus held low, supplying an SP STRIP signal to hold the display in the scratch pad area of the display. The next  $\overline{SP}$ EXEC pulse ends the DO PAUSE signal from U59D, ends the SP RSET X pulse from U55A, and zero-sets U35A. When DO PAUSE ends, it releases U35B. When U35A zero-sets, its zero output puts a high on U55B. The one output from U35A one sets U51A to permit Send operation, if it had been ordered by a SEND signal. Each subsequent SP EXEC pulse causes a low out of U55B. This low appears at the output of U19 eight 1 MHZ pulses later. generating an EXEC signal to permit writing the character in the Scratch Pad strip.

This paragraph pertains only to TC-5 circuit cards numbered 670-1438-00. If an insert condition does not exist, low pulses are generated by U55B and U13B each time the Position Counters reach one hundred. (If insert conditions exists, U13B generates a low output when the Position Counter reaches 101. This accounts for the added Insert shift register on TC-14.) The U55B output forms the RSET INS signal, while the U13B output is processed through the TC-5 circuit as an "end of memory" signal. This signal causes a high to be applied to the J input of U35A. The trailing edge of the next SP EXEC signal causes U35A to one-set. This causes several things to happen. The first of these is that the zero output is applied to U13A to zero-set the Position Counters. This removes the highs from the output gates of the counters and removes the enabling high from pin J or U35A. With U35A one-set, U55A receives enabling voltage and generates an SP RSET X signal which goes to the X-Register to return it to zero position. The trailing edge of the next SP EXEC signal returns U35A to its zero-set condition. This places an enabling voltage on U53B, permitting SP EXEC signals to control the output of that device. It also causes the Send Enable FF U51A to become one-set, thus initiating Send operation with the first character in Scratch Pad memory.

When Edit Mode is selected, a CS LOAD signal causes the Cursor Counter output to be loaded into the Cursor Storage circuit. This records the cursor count at the point where Edit Mode was selected, so that if Edit Send is to be accomplished, it can start from that position. It also occurs when the Terminal is shifted out of Scratch Pad Mode, so that the Cursor Counter can return to this value when the Terminal is switched back to Scratch Pad Mode.

If a character is inserted while the Terminal is in Edit Mode, a COUNT UP signal is applied to the Cursor Storage Register and CC CNT UP is applied to the Cursor Counter, permitting both counters to increment by one. If a character is deleted from memory while in Edit Mode, a COUNT DWN signal is received to decrement the Cursor Storage Register at the same time a CC CNT DWN signal is decrementing the Cursor Counter. Thus the Cursor Storage Registers are compensated for additions or deletions of characters. When the Terminal is switched from Edit to Compose Mode, a CC LOAD signal is applied to the Cursor Counters, causing them to change their values to that contained in the Cursor Storage circuit.

Notice that the Cursor Counter is provided with a Cursor Count Up Disable gate and a Cursor Count Dwn Disable gate. Count up is disabled when the registers contain a digital equivalent of 98, causing a FULL LITE signal to exist as well as the disabling feedback signal. Count down disabling occurs when the Cursor Zero-Position Detect Diodes all have low inputs, indicating that the Cursor Counter has reached a value of zero.

One other circuit associated with insertion of characters into memory is the Clear Set circuit. When a character is to be inserted, the CL SET ARM line goes high, enabling U51B. The next negative transition of the 1 MHz line causes U51B to become one-set, placing enabling voltages on Set and Clear gates U45C and U45D. With the 1 MHz line low, U45D generates a low output, causing the CLEAR signal to be sent to the Shift Registers. (The CLEAR signal insures that the Shift Register contains all zeros before the SET signal loads the new character data.) The next half microsecond finds the 1 MHz line high; U45C generates a low output, causing the SET line to go high.

This paragraph pertains only to TC-5 circuit cards 670-1438-01 and above. When the Position Counter passes through one hundred and reaches the first character position, Send Enable FF U51A becomes one-set. The next low input on the 1 MHz line causes a low pulse out of U53C. This is applied through U49B and U37B to Send FF U17B. If a SEND had previously caused U17A to one-set, U17B would become one-set, causing SP SEND and SEND signals to be sent out. In addition, the pin 9 output of U17B puts an enabling voltage on U33C and U59C. U59C permits SP XMT STR signals to be generated. When an AGREE signal occurs (indicating that the last character has been transmitted), U33C generates a low output and causes U15B to send a reset signal through U57F to the Send Initiate and the Send flip-flops, restoring them to their zero-set condition.

This paragraph pertains only to TC-5 circuit cards numbered 670-1438-00. When the Position Counter passes through one hundred and reaches the first character position, Send Enable FF U51A becomes one-set. The next low input on the 1 MHz line causes a low pulse out of U53C. This is applied to Send Initiate gate U47D. If a SEND signal is present, U47D generates a high output pulse, the leading edge of which one-sets Send Initiate FF U17A, applying a high to the D input of U17B. The low pulse from U53C is also applied to U49B. When it ends, the U49B output goes low, causing a high to appear at the U37B output. This one-sets SEND FF U17B, causing SP SEND and SEND signals to be sent out. In addition, the pin 9 output of U17B puts an enabling voltage on U33C and U59C. U59C permits SP XMT STR signals to be generated. When an AGREE signal occurs (indicating that the last character has been transmitted), U33C generates a low output and causes U15B to send a reset signal through U57F to the Send Initiate and the Send flip-flops, restoring them to their zero-set condition.

If the Terminal is in the Edit Mode when the SEND command is executed, the EDIT FF signal disables U49B and enables Edit Send Execute device U37A. At the time that Edit was selected, the Cursor Counter loaded its contents into the Cursor Storage Register. When the Position Counter reached the first character position, it indirectly caused Send Initiate FF U17A to become one-set. This removed the low from the U37C pin 10 input, permitting that device to come under control of the SP STROB signal. Now each time the Position Counter increments one count, an SP STROB signal and a COUNT DWN signal are received by TC-5, causing the output of U45B to go low. This sends a high COUNT DWN signal into U21. When the Position Counter reaches the value that had been in Cursor Storage, the Cursor Storage contains the complement of 1. (Complement of 0 for TC-5 circuit cards numbered 670-1438-00.) All inputs to U9 are high. This causes the Edit Send Execute gate U9 to send a low to U41A, causing U37A and U37B to deliver a high pulse to U17B, one-setting that device and initiating transmission. Transmission continues until the Cursor Counter and the Position Counter values agree, at which time transmission is terminated and the Scratch Pad Send circuits become reset.

## Horizontal Tab TC-6

The purpose of this circuit card is to permit insertion of tab positions, removal of tab positions, and the shifting of beam writing position to pre-determined tab positions. Circuitry consists of the following sections: Control Signal Decoder, Disarming Circuit, Tab Arm flip-flop, Set flipflop, Clear flip-flop, Master Clear Control Circuit, Read/ Write flip-flop, Reset flip-flop, Tab Pulse Control, Random Access Memory, and Master Clear Counters.

Assume that no tab positions have been established, and that it is desired to insert a tab at the position occupied by

the beam. The eight most significant bits are routed through Master Clear Counters U55 and U57 and applied to the Random Access Memory U35. There they call up a specific memory location which is coincident with the content of these lines. Upon receipt of a coded character (normally ESC), the Terminal provides an SP ARM signal into the circuit. The trailing edge of this pulse one-sets flip-flop U9B, applying enabling voltages to Set flip-flop U9A. Clear flip-flop U29A and Master Clear Control flip-flop U29B. In order to set a tab, the next input data must provide a low output from U1 in the Control Signal Decoder. As configured on the schematic, the number 1 provides all highs into U1. When the TC IN STRB pulse arrives, it causes a low pulse out of U1 which passes through U27A, is inverted and causes Set flip-flop U9A to become one-set. This applies a low to U31A, causing that device to remove the clear signal from Read/Write flip-flop U11A, at the same time sending a TAB BSY signal out through U53B. The TAB BSY signal is routed back to U51D to reset U9B to its zero-set condition. With the clear voltage removed from Read/Write flip-flop U11A, the next 1 MHz clock pulse one-sets U11A; U11A then applies a high to U51C and a low to U53A. The high at pin 9 of U51C has no effect, since the second input to U51C remains low. U51C therefore maintains a high into pin 12 of U35, holding that input in its tab setting condition. Read/Write gate U53A has coincidence between the low signal from the 1 MHz line and the low from the 0 output of U11A, and therefore provides a high into the R/W input of U35. This high at the R/W input of U35 causes the high at pin 12 to set a tab. Simultaneously, the U35 Data Out signal goes low, indicating that a tab position is contained at the existing address. A tab position has been written and the Tab Arm flip-flop has been reset. The next 1 MHz clock pulse one-sets U11B, resetting Set and Clear flip-flops U9A and U29A.

Let's now consider how the beam can be ordered to the tab position which was just inserted. This is accomplished by receiving an HT signal, which comes in and is applied to U51B to generate a TAB signal which goes to TC-12, the X Data Register. In TC-12, this tab signal causes the register to increment by 12 points, which is the spacing between character positions. As the X Register increments, the bit information coming into U55 and U57 changes, continuously calling up new addresses in the U35 Random Access Memory. The HT signal is also applied through U49B, where its trailing edge causes flip-flop U13A to become one-set. When this one-sets, it provides a TAB BSY signal to inform the Terminal that the circuitry is busy providing tab functions. At the same time, U13A releases the clear signal from U33B, U33A, and U13B. This permits that circuit to start counting from 0 to 8 in response to the 1 MHz input signals.

The X Register is incremented through its 12 points at a 2 MHz rate. Therefore, after 6 microseconds, the X Register completes incrementing to its new position. By this time,

### Detailed Circuit Description-4002A Drawer

the divide by 8 counter is providing a low to U53C. If the Random Access Memory has not arrived at a tab position, the Data Out connection remains high and U53C continues to provide a low output to U53D. This permits U53D to continue applying a high to the Clear input of U13A. U13A remains one-set and permits the divide by 8 counter to continue counting.

When the divide by 8 counter reaches 8, it applies three highs to U31B. The next time the 1 MHz clock goes high, U31B applies a low to U51B which causes another TAB signal to be sent to the X Register. The X Register increments through another 12 points and again the Random Access Memory indicates whether or not a tab position exists. If none exists, the divide by 8 counter causes another TAB signal to be sent out. This continues until either a tab position is arrived at, or the end of the line is reached and an EOL signal arrives. EOL is processed through U7A and U53D to apply a low to U13A, zero-setting that device. This places a clear signal onto the three flip-flops in the divide by 8 circuit, causing them to become zero-set. They are thus prevented from generating any more TAB signals.

Assume that the circuit is generating TAB signals and the X Register comes to rest in the position that addresses a tab in U35. The U35 Data Out line goes low. This low is joined in U53C by a low from U13B. The high from U53C causes U53D to zero-set U13A. When U13A becomes zero-set, the divide by 8 counter is again locked in a cleared condition, preventing additional TAB signals. It should be noted that at the same time U13A becomes zero-set, the TAB BSY is ended.

Assume now that the X Register is resting in a position that calls up a tab indication from U35, and that it is desired to clear this tab position. It can be done as follows: First, the SP ARM signal must be received to one-set Tab Arm flip-flop U9B. This provides enabling voltages to the Set flip-flop, Clear flip-flop, and the Master Clear flip-flop. The next character input must cause gate U3 to provide a low output. In the configuration shown on the schematic, the number 0 will perform this function. Assuming that a 0 has been received, the low output from U3 causes a high pulse to appear on the Clear flip-flop. The trailing edge of this causes the Clear flip-flop to become one-set, with the zero output causing a TAB BSY signal to be generated. At the same time, U51A applies a high to the Clear Set gate U51C.

Note that in addition to causing TAB BSY signal to be generated, U31A releases U11A from its cleared condition. The next 1 MHz pulse causes U11A to become one-set, applying a high to U51C, and a low to U53A. U51C now has two high inputs, and applies a low to the Data In connection of U35. The next time the 1 MHz clock goes

Assume now that a number of tabs exist in the Random/Access Memory, and that all these tabs are to be cleared. Again, we must first receive an SP ARM signal which causes Tab Arm flip-flop U9B to become one-set, applying an enabling voltage to Master Clear Control flip-flop U29B. If the next character is an M, it causes the U5 output to pulse low, causing U29B to become one-set. The low transition into U37 causes it to generate a pulse of approximately 1.5 milliseconds duration. The zero output from U37 goes to U51A to place a high on U51C. The zero output from U37 also is processed by U31A to release the clear signal from R/W flip-flop U11A and to generate the TAB BSY signal. As before, the TAB BSY signal goes back to reset the TAB ARM flip-flop to its cleared condition.

The next 1 MHz CLOCK signal to arrive causes R/W flip-flop U11A to become one-set. This cause a high into U51C and a low into U53A. U51C now has two high inputs, causing a low output to be applied to the Data In terminal of U35. While the zero output from U37 is controlling U51A and U31A, the one output from U37 is applying a positive pulse to the Cnt/Load inputs of U55 and U57. This high signal permits U55 and U57 to be disconnected from the X Registered input lines and allows U55 and U57 to advance through one count for each input of the 1 MHz clock signal. The positive excursion of the 1 MHz clock advances the U55 and U57 count by one position. The negative level of the 1 MHz clock is then applied to R/W Gate U53A. The high pulse from U53A writes the low Data In signal into the Random Access Memory. A low is written into each address as the 1 MHz clock carries the U55 and U57 circuits through their entire range.

The U37 output pulse ends at the end of 1.5 ms. Notice that during pulse time, the 0 output from U37 was being fed back to U29B, locking U29B in a cleared condition. When the pulse ends, U29B remains in that condition until it again becomes enabled by the Tab Arm flip-flop and receives another input signal from U5. It should be noted that throughout the clearing of the tabs, the X Register was permitted to remain stationary. The U55, U57 outputs were clocked serially through their entire range by the combination of the high into pin 9 and the repetitive application of 1 MHz pulses.

One more point should be considered-receipt of a character other than those recognizable by U1, U3, or U5

while the SP ARM flip-flop is armed. In such a case, U1, U3, and U5 apply highs to U7B, causing U7B's output to remain low. This causes U49A to apply a high to U7C. When the SP ARM signal elapses, it applies a high to a second input of U7C. When the TC IN STRB signal arrives, this third high causes a low output of U7C, which results in U9B disarming.

#### **Control Function Decoder TC-7**

TC-7 is the control character and special function decoder for the Terminal. It consists principally of two Character Decoders, a Control Function Completes Delay circuit, and the special function output circuitry.

The inputs to the decoders consist of data lines DR1 through DR5. DR5 selects the decoder, and DR1 through DR4 determine its outputs. The CF EXEC signal is applied through an inverter to the decoders as an enabling voltage. Inputs 18 and 19 must both be low in order for the device to decode the DR1 through DR4 information. Therefore, when DR5 is low, U7 is enabled by the CF EXEC signal. When DR5 is high, U11 is enabled by the CF EXEC signal. Thus, if DR1 through DR5 were all high, U11 would be selected; when CF EXEC occurred, a low would appear on output pin 17, resulting in a high US control character signal out of the card.

The special function signals are generated whenever appropriate control characters are decoded by U7 or U11. These are then processed by the applicable circuitry and made available as outputs. It should be noted that although standard factory-wired connections are shown to indicate which signals control the special functions, these resistive straps can be moved to connect any of the control characters to any one of the special function control lines.

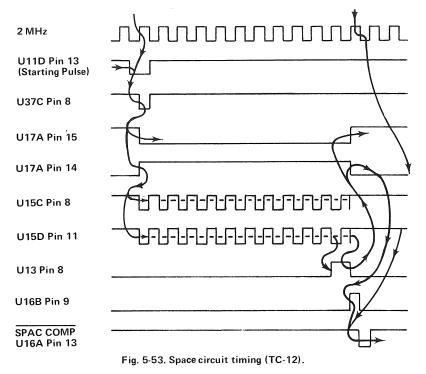

**CF Comp Delay Circuit.** The purpose of this circuit is to provide a 64  $\mu$ s time delay between receipt of the CF EXEC signal and the CF COMP output signal. This 64  $\mu$ s permits adequate time for any special function or control character to be executed by the Terminal. The details regarding this special function complete delay circuit can be determined from the timing diagram associated with the TC-7 schematic.

#### **Character Rotator TC-8**

TC-8 is the character rotator card, and is optional in the Terminal. When the card is not in use, a bypass card must be in its place. With the bypass card in use, the A, B, C, and D signals appear at the output as KR5, KR6, KR7, and KR8, respectively, and the  $\overline{E}$ ,  $\overline{F}$ , and  $\overline{G}$  signals appear at the output as KR2, KR3, and KR4, respectively. The KR1 output is held low and the  $\overline{KR}$  SHIFT output is held high.

Assume that the Character Rotator card is in use and that U15A and U15B are in their zero-set condition. (This condition could occur as a result of a HOME signal, an INITIAL signal, or a US signal; it could also occur by having a successive number of NAK signals sufficient to leave the two flip-flops in their zero-set condition.) With the flip-flops zero-set, U13B receives two high signals and U13A, U13D, and U13C receive at least one low signal. Under this condition U35C has all high signals applied, causing a high output on the KR SHIFT line. U11D has a low input, causing it to place highs on 2 section input gates U3A, U5, U25, U7, U27, U9, and U31. Notice that the second input to these sections is provided by the A, B, C, D, E, F, G, inputs as follows: U3A is driven by A, U5 is driven by E, U25 is driven by B, U7 is driven by F, U27 is driven by C, U9 is driven by  $\overline{G}$ , and U31 is driven by D. When row 1 is selected by the Character Generator matrix in TC-16, A, B, C, and D are low. By following these signals to the respective  $0^\circ$  gates, it can be seen that they control the KR5, KR6, KR7, and KR8 outputs-which would also be low at this time. When column 1 is selected, E, F, and G are high. Following them through their  $0^{\circ}$  gates will result in KR2, KR3, and KR4 being high.

Now assume that an NAK has been received. U15A becomes one-set, causing U13C to receive two highs while the other three NAND gates each receive at least one low. The output of U13C goes low, causing a low KR SHIFT signal to be developed. At the same time, highs are received by one input of the 90° AND gates. The second input to these  $90^{\circ}$  gates is controlled by their respective A, B, C, D,  $\overline{E}$ ,  $\overline{F}$ , and  $\overline{G}$  inputs. Now an interchange of functions has been accomplished. Note that KR1 is now put into use to control the X-axis, because the interchange has caused the 10 rows to be applied to the X Registers instead of the usual 8 columns. It should also be noticed that during  $90^{\circ}$ operation, the KR5 output is disabled, and is held in a low condition. This occurs because the KR6, KR7, and KR8 lines now are handling the column selection and three lines are sufficient. With 90° character rotation selected, the A, B, C, and D input lines control the KR1, KR2, KR3, and KR4 output lines respectively, while the E, F, and G lines control the KR6, KR7, and KR8 lines, respectively.

Receipt of another NAK signal causes  $180^{\circ}$  character rotation to be selected. At this time, U15A becomes zero-set and U15B becomes one-set. This condition results in U13D providing a low output to cause the KR SHIFT signal. U13D and U11A provide highs to appropriate AND gates. KR1 is now disabled and is held low, while KR5 is put back into use. Operation is similar to 0° condition except that the A, B, C, and D lines control KR8, KR7, KR6, and KR5, respectively. This causes the inverse of that which existed at 0° character rotation. Under these same circumstances, the E, F, and G lines control the KR4, KR3, and KR2 lines, respectively.

One more NAK signal causes U13A to receive two highs, with its low output causing a low KR SHIFT signal and

causing highs to be applied to appropriate AND gates. The operation now is similar to that described for  $90^{\circ}$  operation except that A, B, C, and D now control KR4, KR3, KR2, and KR1, respectively, while  $\overline{E}$ ,  $\overline{F}$ , and  $\overline{G}$  control KR8, KR7, and KR6, respectively.

## Y D/A TC-9

The TC-9 circuit description is essentially the same as that for TC-13. Only the differences will be discussed here.

TC-9 does not contain an Italics circuit. Another difference is that TC-9 does contain a Compose circuit. When the Terminal is not in Compose Mode, the input to pin 6 of U87C is high; Q57 and Q77 are turned on. If S99 is set at BTM, CR84 is back-biased and prevents Q77 from affecting U55.

When Compose is selected, the input to pin 6 of U87C goes low, turning Q77 off and placing a high on the anode of CR84. This high passes through S99 to the negative input of U55, causing the output of U55 to hold the CRT beam in the Scratch Pad strip at the bottom of the display area. The D/A circuits now have no effect upon the vertical position of the beam. However, the beam can still be influenced by the character generator matrix signal coming in through the KR5 through KR8 lines at the bottom of the schematic.

If the tube had been rotated so that the Scratch Pad strip were at the top of the CRT, S99 would be in the Top position. Compose Mode would cause Q57 to turn off, placing a low signal through CR88 to the U55 circuit. This low into the negative input of U55 would result in a positive output, holding the display at the top of the CRT in the Scratch Pad area.

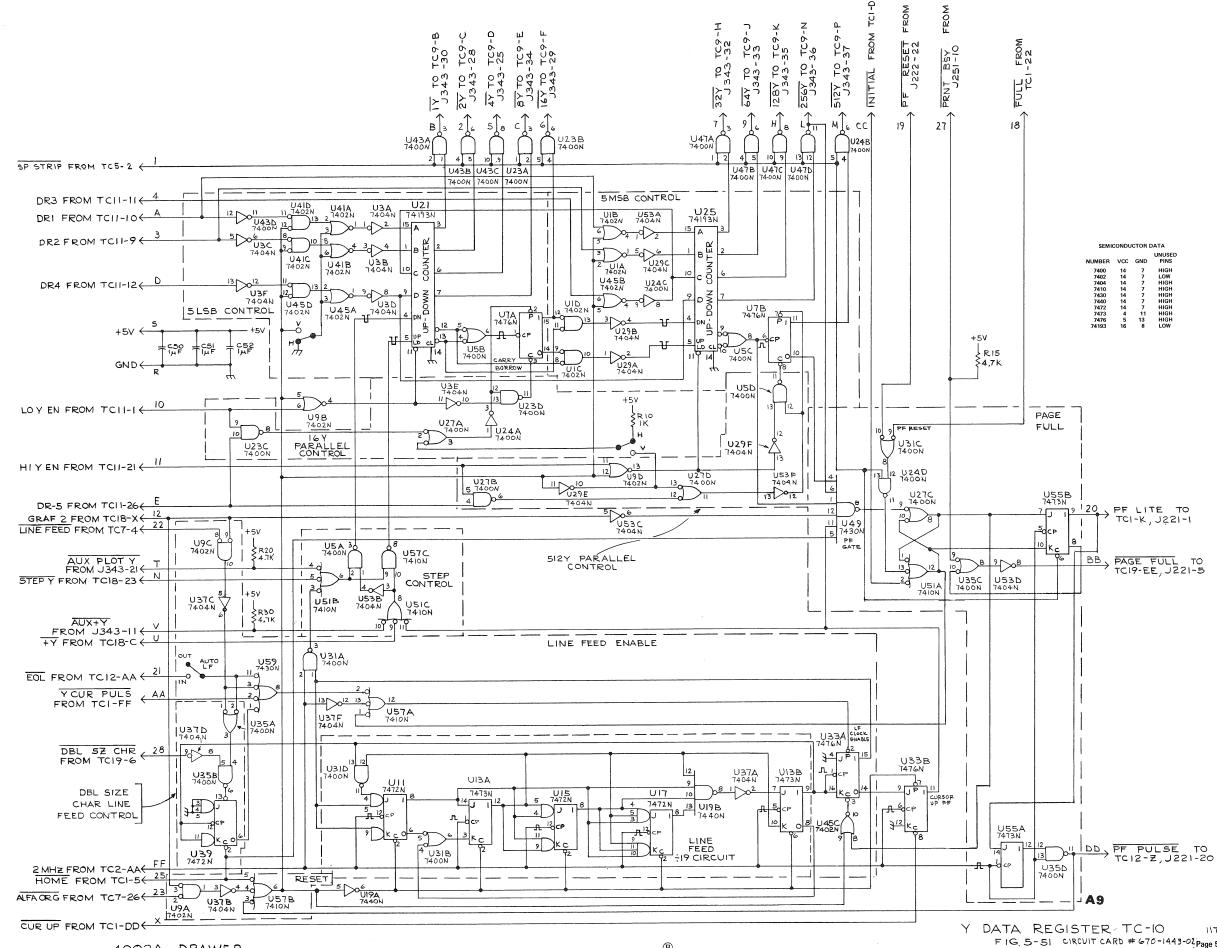

#### Y Data Register TC-10

The Y register contains the following circuits: 5 Least Significant Bit (LSB) control 5 Most Significant Bit (MSB) control 16 Y Parallel control 512 Y Parallel control Step control Line Feed Enable Line Feed ÷19 Double Size Character Line Feed control Reset Circuit Cursor Up Page Full

These circuits will be discussed in that order.

**5 LSB Control**. The 5 LSB control circuit can be driven either parallel or serial. Under initial or reset conditions it is driven in parallel manner. Parallel input gates U41D, U41C,

and U45D are inhibited by the high signal from U57B. The resulting lows from these gates are applied to U41A, U41B, and U45A. When a horizontally oriented display tube is installed, a low is applied to the second inputs of each of these three OR gates, causing their outputs to be high, applying lows to U21 inputs A, B, and D. U21 pin C is receiving a high from U24C because of the effect of U57B on U45B. The high pulse from U57B also passes through U9B to apply a low to the load input of U21, causing the low-low-high-low at A, B, C, and D respectively, to be felt at outputs 3, 2, 6, and 7. These are inverted to cause  $\overline{1Y}$ ,  $\overline{2Y}$ , and  $\overline{8Y}$  to be high, and  $\overline{4Y}$  to be low.

The  $\overline{16Y}$  line is controlled by U7A. During resetting, the high signal from U57B is coupled through U9B to U3E, where it causes a high output to be applied to U23D. At this time, U24A is also applying a high to U23D, causing a low from U23D to zero-set U7A. This causes the 1 output to be low, causing the 16Y line to be high.

The condition of the just-described five lines is determined by whether a vertical or horizontal format is in use. The description given was for a horizontally oriented CRT. When a vertically oriented CRT is in use, the inputs to U41A, U41B, and U45A are high during the time that the pulse from U57B is high; this results in highs into U21 A, B, and D, causing the  $\overline{1Y}$ ,  $\overline{2Y}$ , and  $\overline{8Y}$  lines to be low. In addition, the high from U57B is inverted by U29E, applying a low through the strap link to U27A, putting a low on U23D, disabling it. Simultaneously, the low is applied to the preset connection of U7A, causing U7A to one-set. With U7A one-set, the one output is high, putting a low on the  $\overline{16Y}$  line. It may be noted that U5B serves no function during this resetting action.