# TYPE 453 LECTURE NOTES

### WRITTEN AND PRODUCED IN MARKETING TECHNICAL TRAINING

BY:

Chuck Miller

**GRAPHIC ARTS:**

ARTWORK - Jackie Gossett

Dorothea Lloyd Marlys Weber

TYPING - Joan Bailey

## CONFIDENTIAL

© 1965, Tektronix, Inc. All Rights Reserved

### INDEX

| 1. | INT | RODU | JCTION |

|----|-----|------|--------|

|    |     |      |        |

- II. CHANNEL 1 INPUT AMPLIFIER

- III. CHANNEL 2 INPUT AMPLIFIER

- IV. VERTICAL SWITCHING

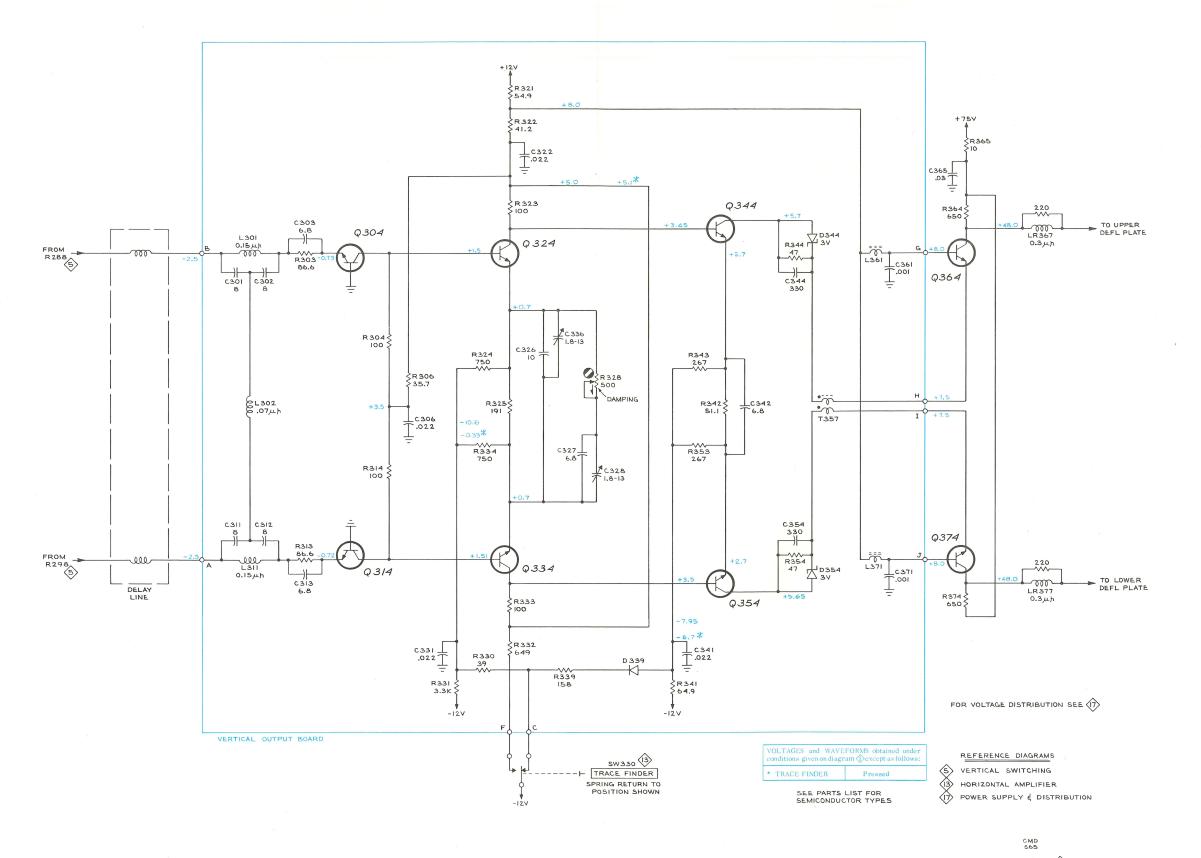

- V. VERTICAL OUTPUT AMPLIFIER

- VI. TRIGGER PREAMP

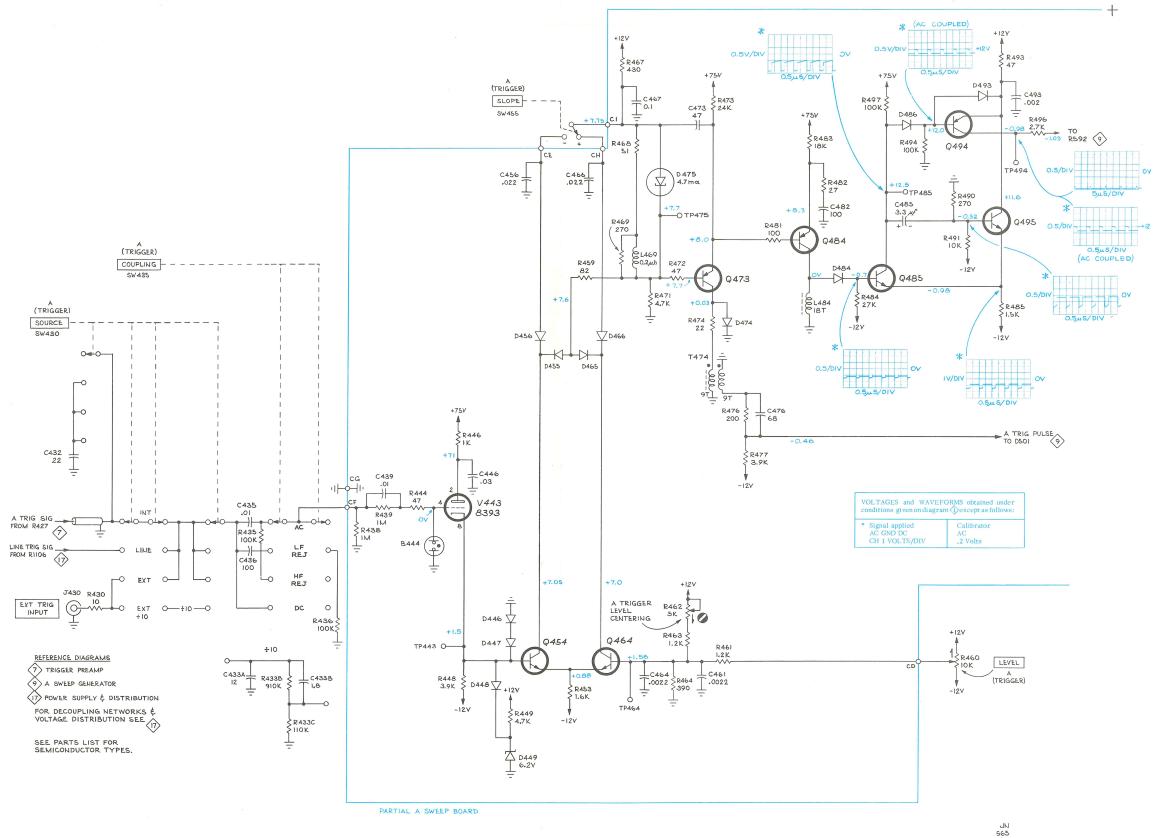

- VII. A TRIGGER GENERATOR

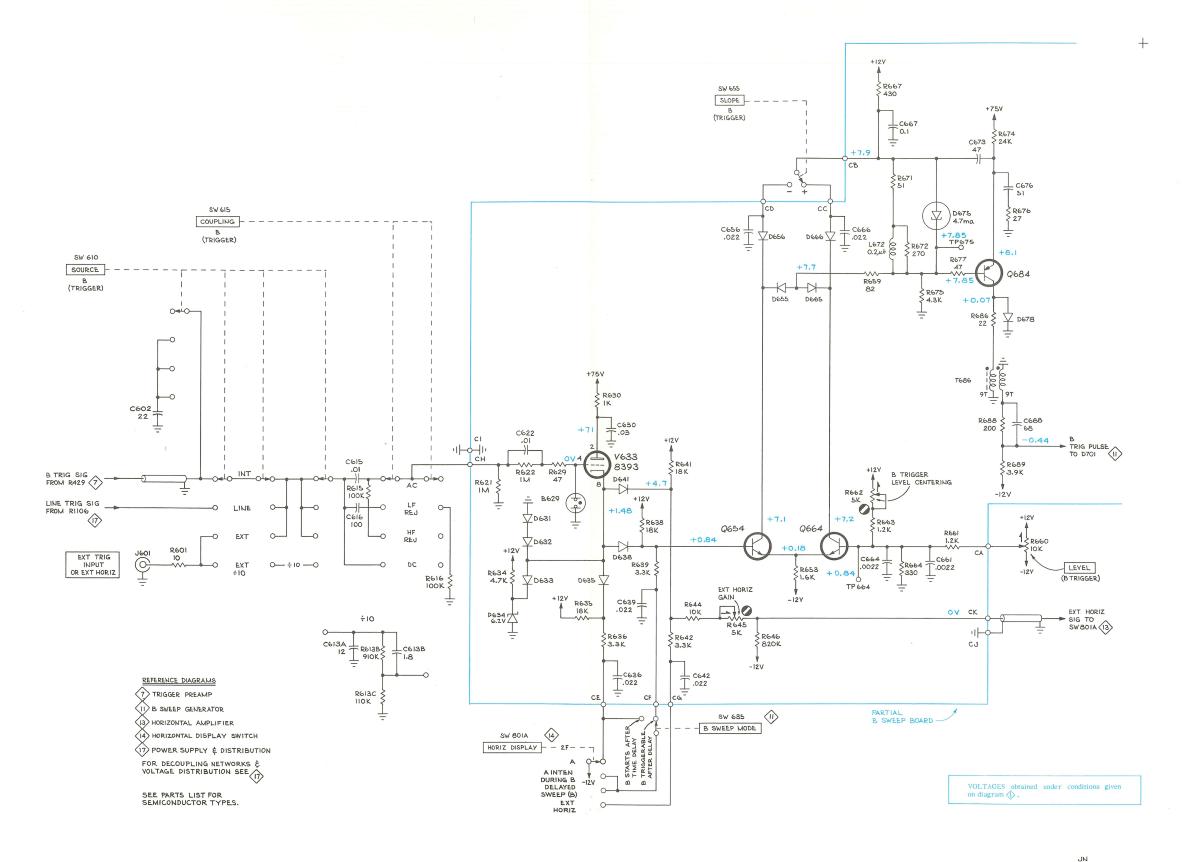

- VIII. B TRIGGER GENERATOR

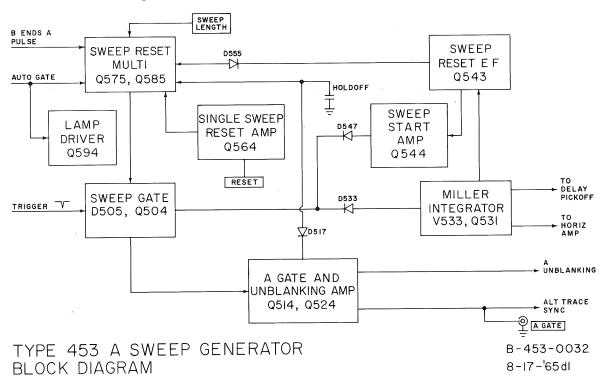

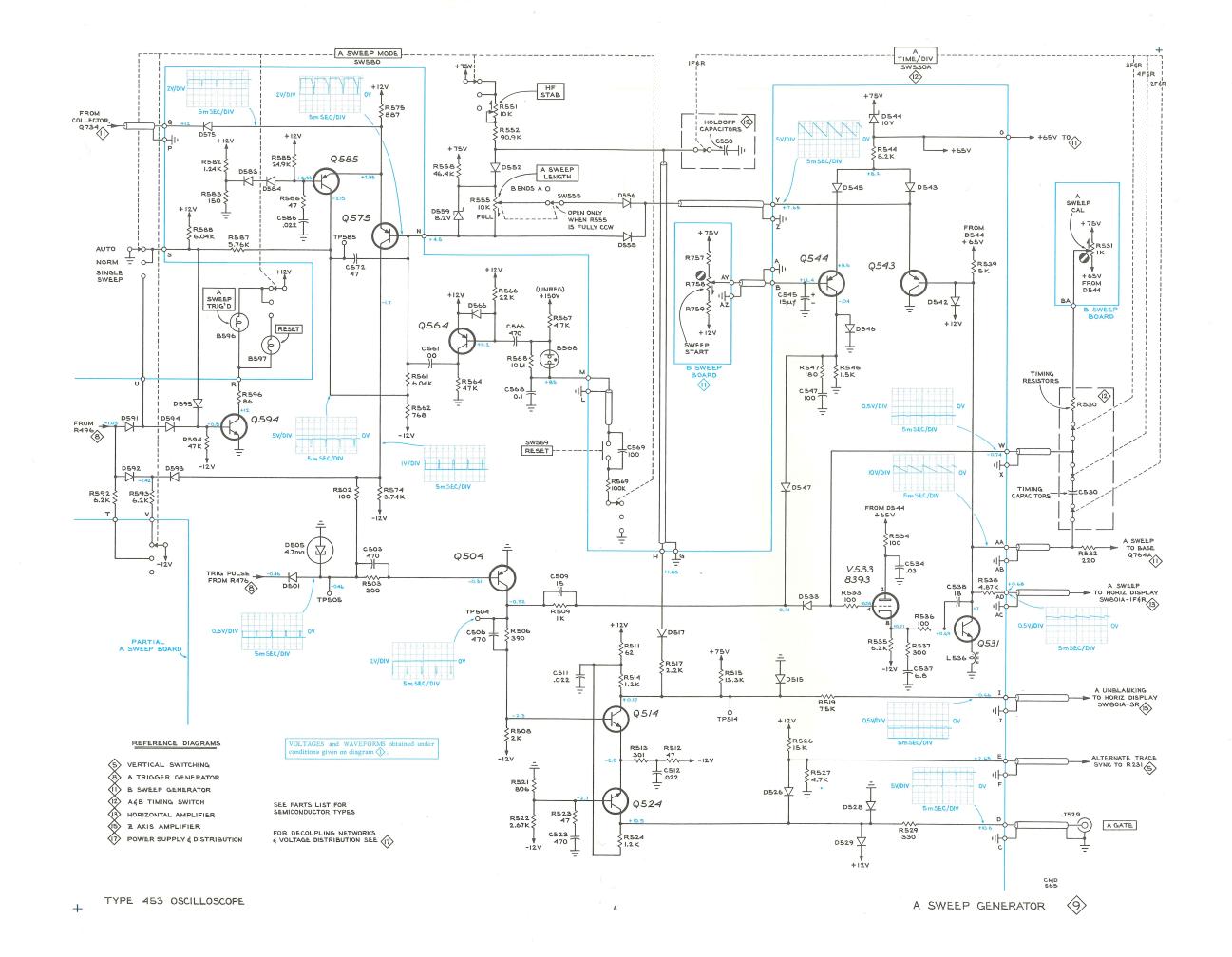

- IX. A SWEEP GENERATOR

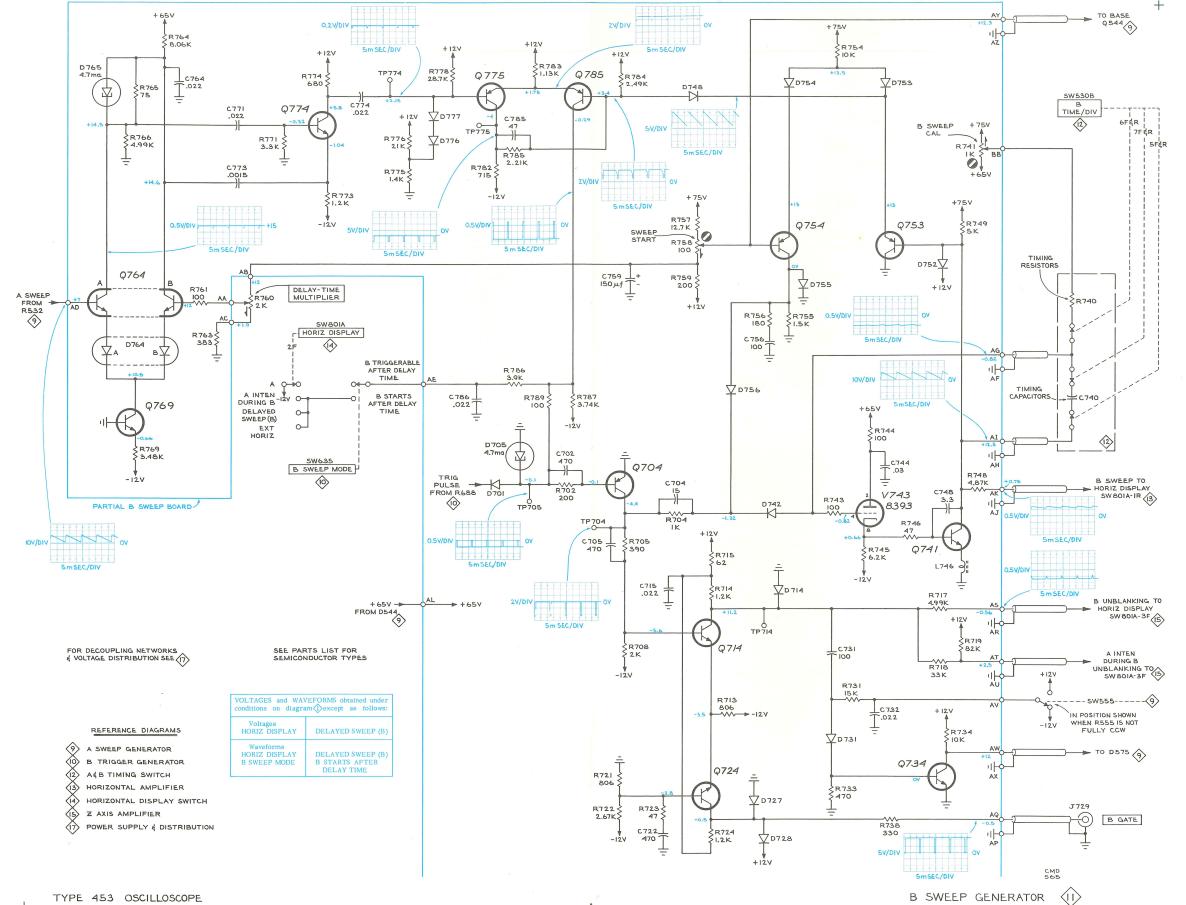

- X. B SWEEP GENERATOR

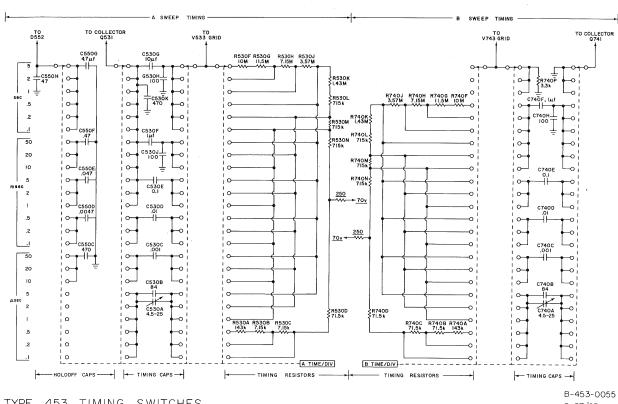

- XI. TIMING SWITCHES

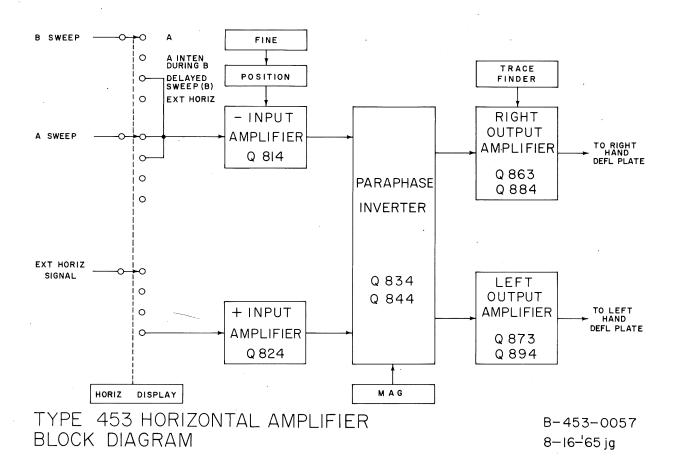

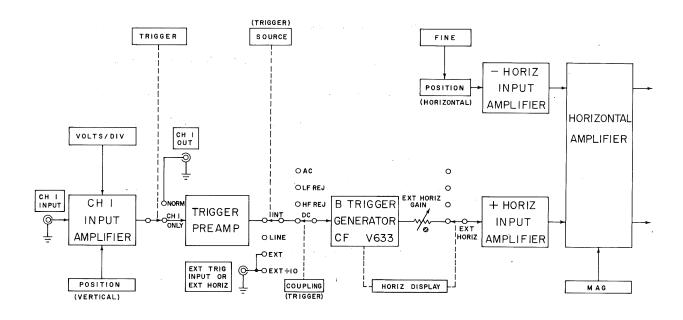

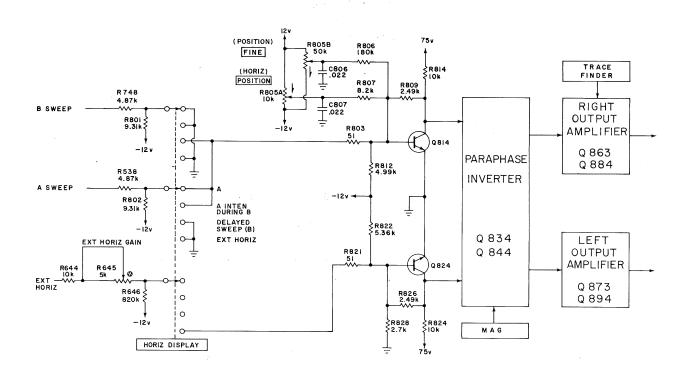

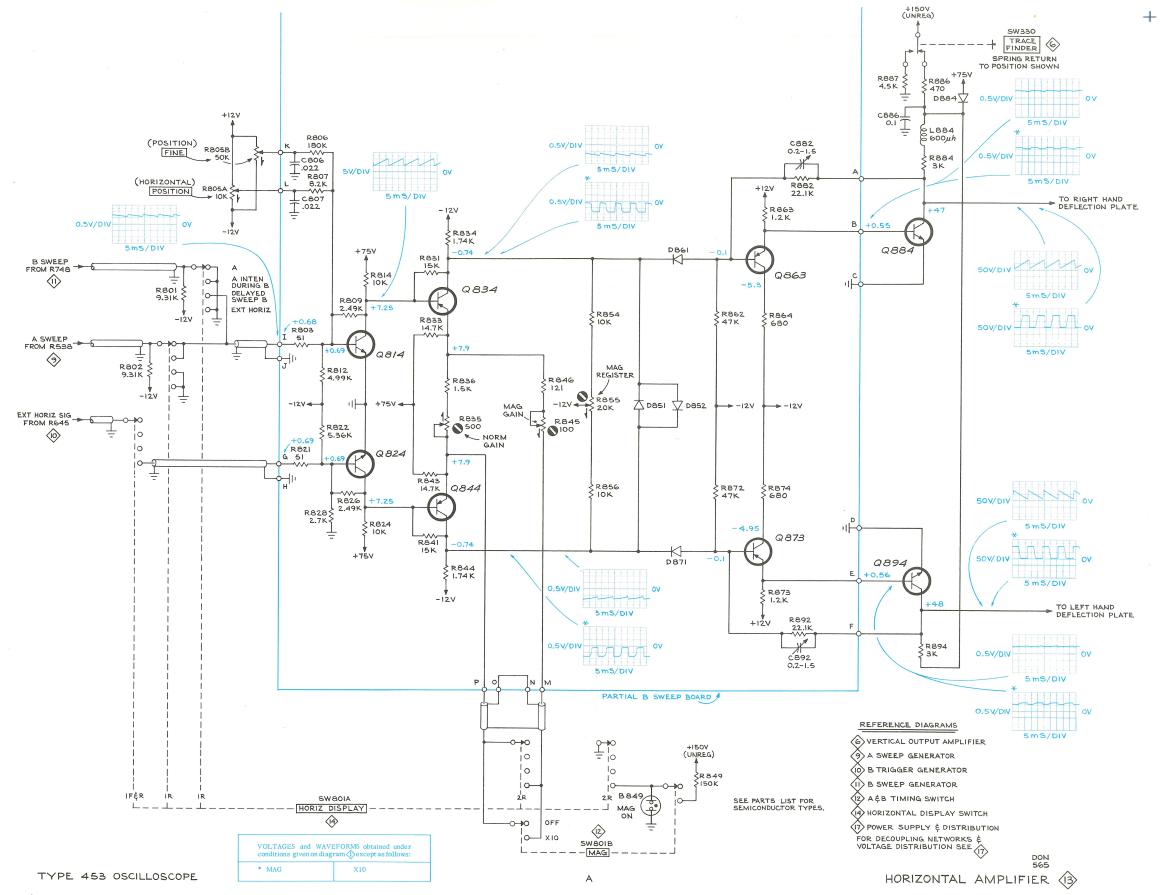

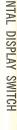

- XII. HORIZONTAL AMPLIFIER

- XIII. CRT AND HIGH VOLTAGE

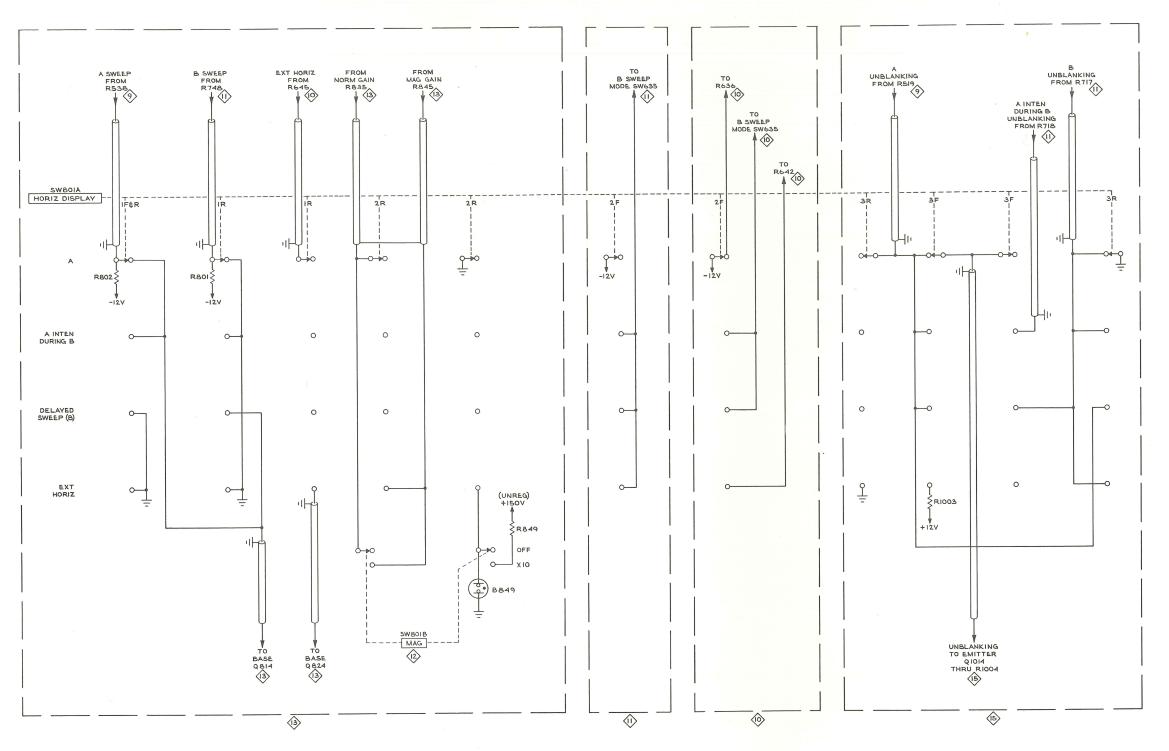

- XIV. Z AXIS AMPLIFIER

- XV. POWER SUPPLY

- XVI. CALIBRATOR

• \* ~ :

#### I. INTRODUCTION

A. The Type 453 is a transistorized portable oscilloscope designed to operate in a wide range of environmental conditions.

#### B. General Information

- 1. The Vertical system features dual-channel DC 50 mc operation.

- a. Calibrated vertical deflection factors from 5 mv to 10 volts/div are provided.

- b. The two Input Preamps may be cascaded to provide a 1 mv/div deflection factor.

- 2. The trigger circuits provide stable triggering over the full range of vertical frequency response.

- a. A "bright line automatic" circuit is featured that, in the absence of triggers, causes the sweep to free run at a rate determined by the TIME/DIV control.

- 3. The Time Base circuits provide a maximum sweep rate of .1  $\mu$ sec/div (10 nsec/div using the X10 magnifier).

- a. Minimum sweep speed is 5 sec/div.

- b. A delayed sweep is provided, with a range of .1 µsec/div to .5 sec/div.

- 4. Accurate X-Y measurements may be made with Channel 1, providing horizontal deflection, and Channel 2, providing the vertical deflection.

- a. Both vertical and horizontal deflection sensitivities may be calibrated.

- b. TRIGGER switch is set to CH 1 ONLY and the HORIZ DISPLAY switch is set to EXT HORIZ.

### C. Characteristics

- 1. The following characteristics apply over an ambient temperature range of -15°C to +55°C except as otherwise indicated.

- a. Allow 20 minutes warm-up time for the indicated accuracies.

#### **VERTICAL DEFLECTION SYSTEM**

| Characteristic                              | Perform                                                                                                                                                                                  | ance Requirement                | Supplemental Information                                          |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------|

| Deflection Factor                           | 5 millivolts/division to 10 volts/division in 11 calibrated steps for each channel                                                                                                       |                                 | Steps in 1-2-5 sequence                                           |

| Deflection Accuracy                         | Within ±3% of ind control fully clockwise                                                                                                                                                | icated deflection with VARIABLE | With gain correct at 20 mV                                        |

| Variable Deflection Factor                  | Uncalibrated deflection factor at least 2.5 times the VOLTS/DIV switch indication. This provides a maximum uncalibrated deflection factor of 25 volts/division in the 10 volts position. |                                 |                                                                   |

| Frequency Response (not more than 30% down) | Type 453 Only                                                                                                                                                                            | With P6010 Probe                |                                                                   |

| 20 mV to 10 VOLTS/DIV                       | Dc to 52.5 Mc                                                                                                                                                                            | Dc to 50 Mc                     |                                                                   |

| 10 mV/DIV                                   | Dc to 46.5 Mc                                                                                                                                                                            | Dc to 45 Mc                     | ·                                                                 |

| 5 mV/DIV                                    | Dc to 41 Mc                                                                                                                                                                              | Dc to 40 Mc                     |                                                                   |

| Channel 1 and 2 cascaded                    | Dc to 25 Mc                                                                                                                                                                              | Dc to 25 Mc                     | Measured at 1 millivolt/division                                  |

| Added                                       | Dc to 52.5 Mc                                                                                                                                                                            | Dc to 50 Mc                     | Measured at 20 mV                                                 |

| Risetime (calculated)                       |                                                                                                                                                                                          |                                 |                                                                   |

| 20 mV to 10 VOLTS/DIV                       | Less than 6.7 nanoseconds 7                                                                                                                                                              |                                 |                                                                   |

| 10 mV/DIV                                   | Less than 7.5 nanoseconds 7.8                                                                                                                                                            |                                 |                                                                   |

| 5 mV/DIV                                    | Less than 8.75 nanoseconds 8.75                                                                                                                                                          |                                 |                                                                   |

| Channel 1 and 2 cascaded                    | Less than 14 nanoseconds 14                                                                                                                                                              |                                 | Measured at 1 millivolt/division                                  |

| Added                                       | Less than 6.7 nanoseco                                                                                                                                                                   | onds 7                          | Measured at 20 mV                                                 |

| Input Rc Characteristics                    |                                                                                                                                                                                          |                                 | Typically 1 megohm ( $\pm 2\%$ ), parallel by 20 pf ( $\pm 3\%$ ) |

| Maximum Input Voltage                       |                                                                                                                                                                                          |                                 | 600 volts combined dc and peak<br>ac                              |

| Input Coupling Modes                        | Ac or dc, selected by fr                                                                                                                                                                 | ont-panel switch                |                                                                   |

| AC Low-frequency response                   |                                                                                                                                                                                          |                                 | Typically 30% down at 1.6 cps,<br>AC GND DC switch set to AC      |

| Trace Shift Due to Input Grid<br>Current    | Less than 0.4 division at 5 mv                                                                                                                                                           |                                 |                                                                   |

| Vertical Display Modes                      | Channel 1 only<br>Channel 2 only<br>Dual-trace, alternate b<br>Dual-trace, chopped b<br>Added algebraically                                                                              |                                 |                                                                   |

### VERTICAL (cont'd)

| Characteristic                                                          | Performance Requirement                                                                                                    | Supplementa                                                               | l Information                                            |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------|

| Chopped Repetition Rate                                                 | Approximately 1-microsecond segments from each channel displayed at repetition rate of 500 kc, ±20%                        |                                                                           | ų.                                                       |

| Attenuator Isolation                                                    | Greater than 10,000:1, dc to 20 Mc                                                                                         |                                                                           |                                                          |

| Common Mode Rejection Ratio                                             | Greater than 20:1 at 20 Mc; input signal less than eight times VOLTS/DIV switch setting                                    | With optimum C                                                            |                                                          |

| Linear Dynamic Range useful for<br>Common-Mode Rejection in<br>ADD Mode |                                                                                                                            | Less than 10%<br>nal distortion for<br>input voltage of<br>times VOLTS/DI | or instantaneous<br>f —10 or +10,                        |

| Polarity Inversion                                                      | Signal on Channel 2 can be inverted                                                                                        |                                                                           | -                                                        |

| Signal Delay                                                            |                                                                                                                            | Approximately 1                                                           | 40 nanoseconds                                           |

| Vertical Linearity                                                      | Less than 0.15 division compression or expansion of 2 division signal when positioned to vertical extremes of display area | Includes crt line                                                         | arity                                                    |

| Trace Drift (after 15 minute warm up)                                   |                                                                                                                            | Time                                                                      | Temperature                                              |

| 20 mV to 10 VOLTS/DIV                                                   |                                                                                                                            | Typically less<br>than 0.25 divi-<br>sion/hour                            | Typically less<br>than 0.025 di-<br>vision / degree<br>C |

| 10 mV/DIV                                                               |                                                                                                                            | Typically less<br>than 0.5 divi-<br>sion/hour                             | Typically less<br>than 0.05 divi-<br>sion/degree C       |

| 5 mV/DIV                                                                |                                                                                                                            | Typically less<br>than 1 division/<br>hour                                | Typically less<br>than 0.1 divi-<br>sion/degree C        |

| Channel 1 Output Signal<br>Output Voltage                               | Greater than 25 millivolts/division of crt display into<br>1 megohm load                                                   | At CH 1 OUT (<br>Channel 1 VAR<br>DIV control set                         | RIABLE VOLTS/                                            |

| Frequency Response (not more than 30% down)                             | Dc to 25 Mc when cascaded with Channel 2 or into 50-ohm load                                                               |                                                                           |                                                          |

| Risetime (calculated)                                                   | 14 nanoseconds                                                                                                             |                                                                           |                                                          |

| Output Coupling                                                         | Dc                                                                                                                         |                                                                           |                                                          |

| Output Resistance                                                       |                                                                                                                            | Approximately 5                                                           | 0 ohms                                                   |

### TRIGGERING (A AND B SWEEP)

| Characteristic               | Performance Requirement                                                                                              | Supplemental Information                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Source                       | Internal from displayed channel or from Channel 1 only<br>Internal from ac line<br>External<br>External divide by 10 |                                         |

| Coupling                     | Ac low-frequency reject Ac high-frequency reject Dc                                                                  |                                         |

| Polarity                     | Sweep can be triggered from positive-going or negative-going portion of trigger signal                               |                                         |

| Internal Trigger Sensitivity |                                                                                                                      |                                         |

| AC ,                         | 0.2 division of deflection, minimum, 30 cps to 10 Mc; increasing to 1 division at 50 Mc                              | Typically 30% down at 16 cps            |

| LF REJ                       | 0.2 division of deflection, minimum, 30 kc to 10 Mc; increasing to 1 division at 50 Mc                               | Typically 30% down at 16kc              |

| HF REJ                       | 0.2 division of deflection, minimum, 30 cps to 50 kc                                                                 | Typically 30% down at 16 cps and 100 kc |

| DC                           | 0.2 division of deflection, minimum, dc to 10 Mc; increasing to 1 division at 50 Mc.                                 |                                         |

TRIGGERING (cont'd)

| Characteristic                                          | Performance Requirement                                                                                                              | Supplemental Information                       |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| External Trigger Sensitivity<br>AC                      | 50 millivolts, minimum, 30 cps to 10 Mc; increasing to                                                                               | Typically 30% down at 16 cps                   |

| LF REJ                                                  | 200 millivolts at 50 Mc 50 millivolts, minimum, 30 kc to 10 Mc; increasing to 200 millivolts at 50 Mc                                | Typically 30% down at 16 kc                    |

| HF REJ                                                  | 50 millvolts, minimum, 30 cps to 50 kc                                                                                               | Typically 30% down at 16 cps and 100 kc        |

| DC                                                      | 50 millivolts, minimum, dc to 10 Mc; increasing to 200 millivolts at 50 Mc                                                           |                                                |

| Auto Triggering (A Sweep only)                          | Provides normal triggering capability for trigger signals above 20 cps and produces free-running sweep in absence of trigger signal. |                                                |

| Single Sweep (A Sweep only)                             | Triggering capability same as normal trigger Performance Requirement.                                                                |                                                |

| Display Jitter                                          | Less than 1 nanosecond at 10 nanoseconds/division sweep rate (MAG switch set to ×10)                                                 |                                                |

| Maximum Input Voltage                                   |                                                                                                                                      | 600 volts combined dc and peak ac              |

| External Trigger Input Rc Characteristics (approximate) |                                                                                                                                      | 1 Megohm paralleled by 20 pf, except in LF REJ |

| LEVEL Control Range                                     | At least $\pm 2$ volts, SOURCE switch in EXT position At least $\pm 20$ volts, SOURCE switch in EXT $\div 10$ position               |                                                |

HORIZONTAL DEFLECTION SYSTEM

A and B Sweep Generator

| Characteristic                                  | Performance                                                                                                          | Requirement                                            | Supplemental Information                                                                                    |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Sweep Rates                                     |                                                                                                                      |                                                        |                                                                                                             |

| A Śweep                                         | 0.1 microsecond/division to calibrated steps                                                                         | 5 seconds/division in 24                               | A Sweep is main and delaying sweep                                                                          |

| B Sweep                                         | 0.1 microsecond/division to calibrated steps                                                                         | 0.5 second/division in 21                              | B Sweep is delayed sweep                                                                                    |

| Sweep Accuracy — A and B<br>Sweep               | 0°C to +40°C                                                                                                         | —15°C to +55°C                                         |                                                                                                             |

| 5 SEC to 0.1 SEC/DIV                            | Within ±3% of indicated sweep rate                                                                                   | Within ±5% of indicated sweep rate                     | A VARIABLE and B TIME/DIV<br>VARIABLE controls set to CAL                                                   |

| 50 mSEC to 0.1 $\mu$ SEC/DIV                    | Within $\pm 3\%$ of indicated sweep rate                                                                             | Within ±4% of indicated sweep rate                     |                                                                                                             |

| Variable Sweep Rate                             | Uncalibrated sweep rate to a DIV indication, or a maximu division in the 5 SEC position 1.25 seconds/division in the | m of at least 12.5 seconds/<br>on (B Sweep, maximum of |                                                                                                             |

| Sweep Length                                    |                                                                                                                      |                                                        |                                                                                                             |

| A Sweep                                         | Variable from less than 4 divisions to 11.0, $\pm 0.5$ division                                                      |                                                        | A TIME/DIV switch set to 1 mSEC                                                                             |

| B Sweep                                         | 11.0 divisions, $\pm$ 0.5 division                                                                                   |                                                        | B TIME/DIV switch set to 1 mSEC                                                                             |

| Sweep Hold-off—A Sweep 5 SEC to $10\mu SEC/DIV$ | Less than one times the A T                                                                                          | IME/DIV switch setting                                 |                                                                                                             |

| $5~\mu SEC$ to $0.1~\mu SEC/DIV$                | Less than 2.5 microsecond                                                                                            |                                                        |                                                                                                             |

| Gate Output Signal<br>Waveshape                 | Rectangluar pulse                                                                                                    |                                                        |                                                                                                             |

| Polarity                                        | Positive-going .                                                                                                     |                                                        | Baseline at about -0.7 volts                                                                                |

| Amplitude                                       | 12 volts, $\pm 10\%$                                                                                                 |                                                        |                                                                                                             |

| Duration                                        | About 11 times TIME/DIV s                                                                                            | witch setting                                          | A GATE duration variable between about 4 and 11 times A TIME/DIV switch setting with A SWEEP LENGTH control |

| Output resistance                               |                                                                                                                      |                                                        | Approximately 1.5 kilohms                                                                                   |

### Sweep Magnifier

| Characteristic                | Performance Requirement                                                                                                                     | Supplemental Information                              |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Sweep Magnification           | Each sweep rate can be increased 10 times the indicated sweep rate by horizontally expanding the center division of display                 | Extends fastest sweep rate to 10 nanoseconds/division |

| Magnified Sweep Accuracy      | 1% tolerance added to specified sweep accuracy                                                                                              |                                                       |

| Magnified Sweep Linearity     | $\pm 1.5\%$ for any eight division portion of the total magnified sweep length (excluding first and last 60 nanoseconds of magnified sweep) |                                                       |

| Normal/Magnified Registration | Less than $\pm 0.2$ division trace shift at graticule center when switching MAG switch from $\times 10$ to OFF                              |                                                       |

Sweep Delay

| Characteristic                   | Performance                                | Requirement                                | Supplemental Information                          |

|----------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------------|

| Calibrated Delay Time Range      | Continuous from 50 seconds                 | to 1 microsecond                           | A VARIABLE control set to CAL for indicated delay |

| Delay Time Accuracy              | 0°C to +40°C                               | −15°C to +55°C                             |                                                   |

| 5 SEC to 0.1 SEC/DIV             | Within $\pm 2.5\%$ of indicated sweep rate | Within $\pm 3.5\%$ of indicated sweep rate | Includes incremental multiplier                   |

| 50 mSEC to 1 $\mu$ SEC/DIV       | Within ±1.5% of indicated sweep rate       | Within ±2% of indicated sweep rate         | linearity                                         |

| Incremental Multiplier Linearity | ±0.2%                                      | ±0.3%                                      |                                                   |

| Delay Time Jitter                | Less than 1 part in 20,000 switch setting  | of 10 times A TIME/DIV                     |                                                   |

**External Horizontal Amplifier**

| Characteristic                                                           | Performance Requirement                                                                          |                                    | Supplemental Information                                                                          |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------|

| Input to Channel 1 (TRIGGER<br>switch in CH 1 ONLY)<br>Deflection factor | 5 millivolts/division to 10 volts/division in 11 calibrated steps                                |                                    | Steps in 1-2-5 sequence. Chan-<br>nel 1 VARIABLE control does<br>not affect horizontal deflection |

| Accuracy                                                                 | 0°C to +40°C                                                                                     | _15°C to +55°C                     |                                                                                                   |

|                                                                          | Within ±5% of indicated deflection                                                               | Within ±8% of indicated deflection | With External Horizontal gain correct at 20 mV                                                    |

| Frequency response                                                       | Dc to 5 Mc, not more than 30% down                                                               |                                    |                                                                                                   |

| Input rc characteristics                                                 |                                                                                                  |                                    | Typically 1 megohm ( $\pm 2\%$ ), paralleled by 20 pf ( $\pm 3\%$ )                               |

| Phase difference between X and Y amplifiers at 50 KC                     |                                                                                                  |                                    | Less than 3°                                                                                      |

| Input to EXT HORIZ Connector                                             |                                                                                                  |                                    |                                                                                                   |

| Deflection factor                                                        | B TRIGGERING SOURCE so<br>volts/division, ±15%<br>B TRIGGERING SOURCE so<br>volts/division, ±20% |                                    |                                                                                                   |

| Frequency response                                                       | Dc to 5 Mc, not more than 30% down                                                               |                                    |                                                                                                   |

| Input rc characteristics (approximate)                                   |                                                                                                  |                                    | 1 megohm, paralleled by 20 pf                                                                     |

| Phase difference between X and Y amplifiers at 50 KC                     |                                                                                                  |                                    | Less than 3°                                                                                      |

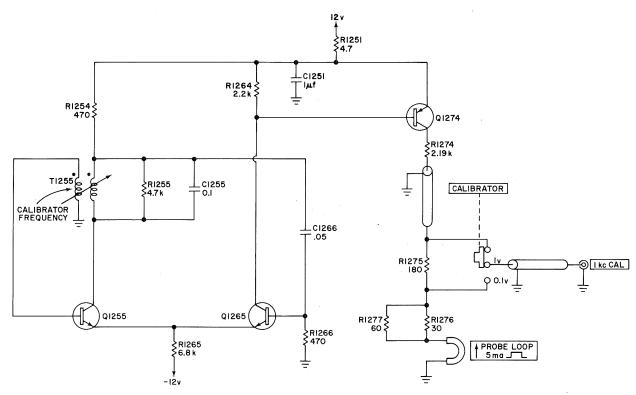

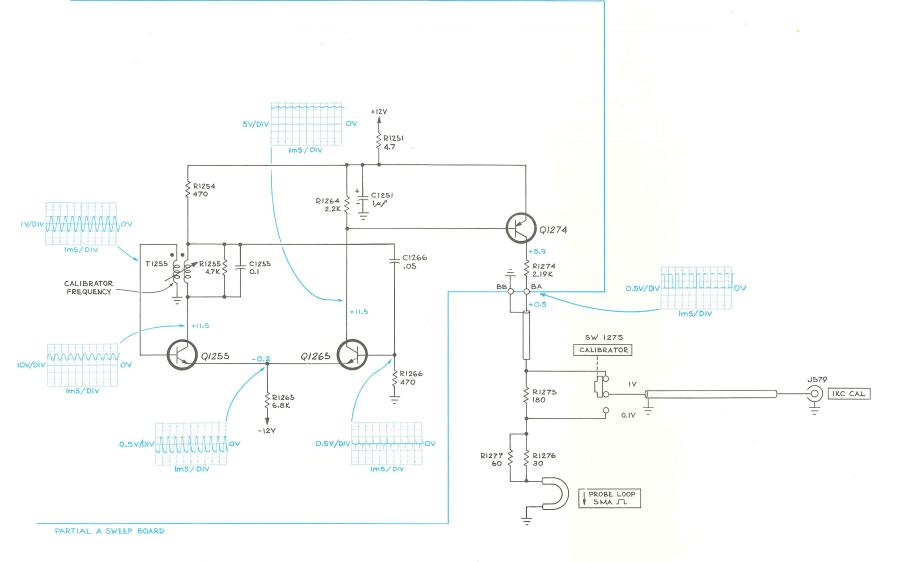

### **CALIBRATOR**

| Characteristic           | Performance Requirement                      |                  | Supplemental Information                                                      |

|--------------------------|----------------------------------------------|------------------|-------------------------------------------------------------------------------|

| Waveshape                | Square wave                                  |                  |                                                                               |

| Polarity                 | Positive going with baseli                   | ne at zero volts |                                                                               |

| Output Voltage           | 0.1 volt or 1 volt, peak to peak             |                  | Selected by CALIBRATOR switch on side panel                                   |

| Output Current           | 5-milliamps through PROBE LOOP on side panel |                  |                                                                               |

| Repetition Rate          | 1 kc                                         |                  |                                                                               |

|                          | 0°C to +40°C                                 | _15°C to +55°C   |                                                                               |

| Voltage Accuracy         | ±1%                                          | ±1.5%            |                                                                               |

| Current Accuracy         | ±1%                                          | ±1.5%            |                                                                               |

| Repetition Rate Accuracy | ±0.5%                                        | ±1%              |                                                                               |

| Risetime                 | Less than 1 microsecond                      |                  |                                                                               |

| Duty Cycle               | 49% to 51%                                   |                  |                                                                               |

| Output Resistance        |                                              |                  | Approximately 200 ohms in 1 V position Approximately 20 ohms in .1 V position |

### Z AXIS INPUT

| Characteristic         | Performance Requirement                                        | Supplemental Information                                                                                                 |

|------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Sensitivity            | 5 volt peak-to-peak signal produces noticeable modula-<br>tion |                                                                                                                          |

| Usable Frequency Range | Dc to greater than 50 Mc                                       |                                                                                                                          |

| Input Resistance at DC |                                                                | Approximately 47 kilohms                                                                                                 |

| Input Coupling         | Dc coupled                                                     |                                                                                                                          |

| Polarity of Operation  |                                                                | Positive-going input signal will<br>decrease trace intensity<br>Negative-going signal will in-<br>crease trace intensity |

| Maximum Input Voltage  |                                                                | 200 volts combined dc and peak ac                                                                                        |

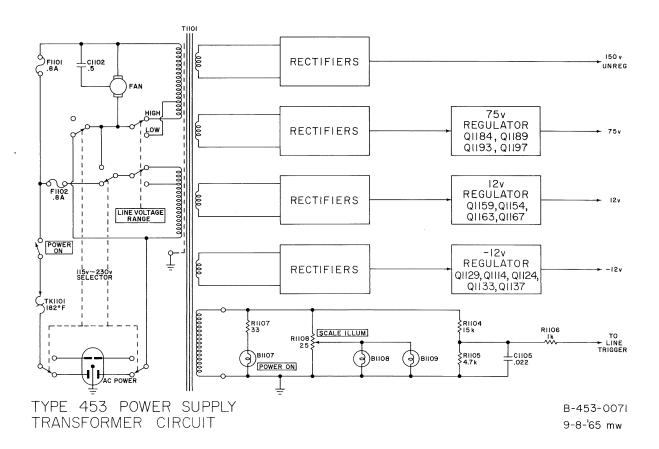

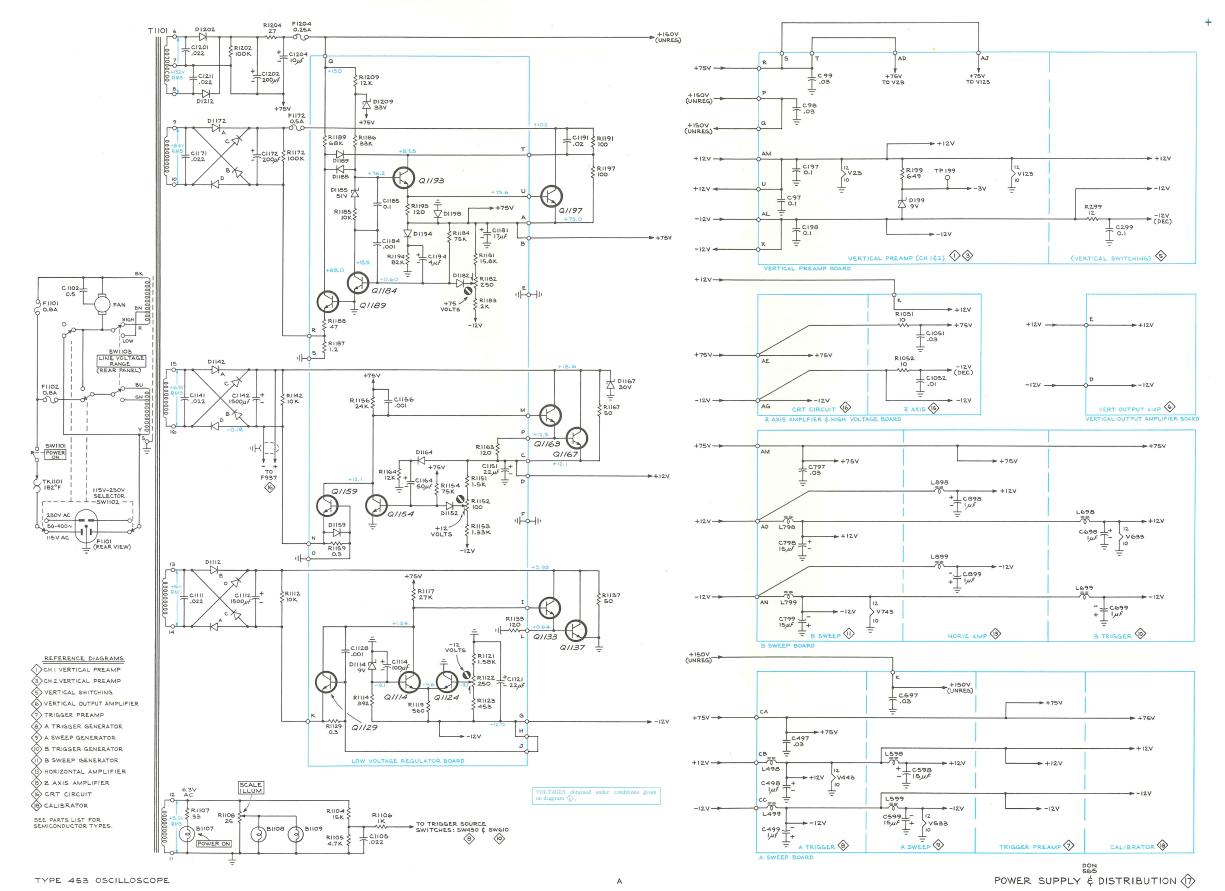

### **POWER SUPPLY**

| Characteristic       | Supplemental Information                                                                                                                             |                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Voltage Requirements |                                                                                                                                                      |                                                                   |

| 115-volt range       | LOW—96 to 127 volts, rms, ac line voltage provides regulated dc voltages HIGH—103 to 137 volts, rms, ac line voltage provides regulated dc voltages  | Applicable when line contains<br>less than 2% total harmonic dis- |

| 230-volt range       | LOW—192 to 254 volts, rms, ac line voltage provides regulated dc voltages HIGH—206 to 274 volts, rms, ac line voltage provides regulated dc voltages | tortion                                                           |

| Line Frequency       | 45 to 440 cps                                                                                                                                        |                                                                   |

| Power Consumption    |                                                                                                                                                      | Approximately 100 watts                                           |

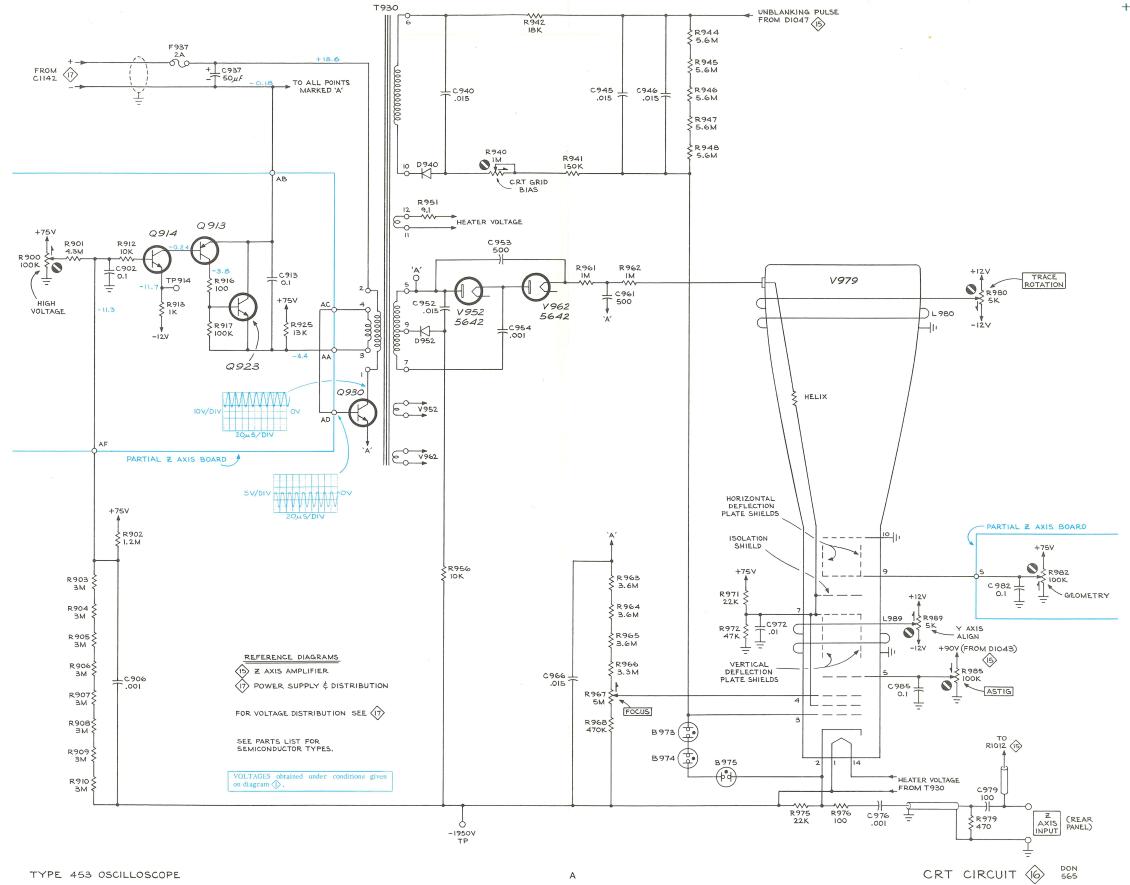

#### CATHODE-RAY TUBE (CRT)

| Characteristic              | Information                                                                          |

|-----------------------------|--------------------------------------------------------------------------------------|

| Tube Type                   | T4530-31-1 rectangular, glass envelope                                               |

| Phosphor                    | P31 standard. Others available on special order                                      |

| Accelerating Poten-<br>tial | Approximately 10 kv (gun potential, 2 kv)                                            |

| Graticule<br>Type           | Internal                                                                             |

| Area                        | 6 divisions vertical by 10 divisions horizontal. Each division equals 0.8 centimeter |

| Illumination                | Variable edge lighting                                                               |

| Unblanking                  | Dc-coupled to crt grid from<br>Sweep Generator                                       |

#### **MECHANICAL CHARACTERISTICS**

| Characteristic                                          | Information                                                                            |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|

| Construction                                            | Aluminum-alloy chassis, panel<br>and cabinet<br>Glass laminate etched-wiring<br>boards |

| Finish                                                  | Anodized panel, blue vinyl-coated cabinet                                              |

| Overall Dimensions<br>(measured at maxi-<br>mum points) | 7.25" high, 12.5" wide, 23.5" long (includes panel cover and handle)                   |

| Net Weight                                              | 29 lbs. 2 oz. (includes power cord and panel cover without accessories)                |

#### **ENVIRONMENTAL CHARACTERISTICS**

#### NOTE

The Type 453 has been designed to meet the following environmental characteristics. During production, samples of the Type 453 will be checked to assure that the instrument continues to meet the environmental characteristics. Environmental tests can be grouped into two general categories: Tests which may be repeated an indefinite number of times without physical damage to, or performance deterioration of, the instrument (Category I); and tests which should be repeated only once as they may cause minor damage to the instrument without causing it to malfunction (Category II). The following environmental characteristics will be grouped into these categories. Complete details on environmental test procedures, including failure criteria, etc., may be obtained from Tektronix, Inc. Contact your local Field Office or representative.

#### Category I

| Characteristic           | Requirement                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature<br>Operating | Type 453 will perform to limits given in this section over a temperature range of —15°C to +55°C. Maximum operating temperature must be derated 1°C/1000 feet increase in altitude from 5000 to 15,000 feet. Fan at rear of instrument blows filtered air throughout instrument. Automatic resetting thermal cutout interrupts instrument power if internal temperature exceeds a safe operating level. |

| Non-Operating            | _55°C to +75°C                                                                                                                                                                                                                                                                                                                                                                                          |

| Altitude<br>Operating    | Type 453 will perform to limits given in this section up to 15,000 feet. See derating information under 'Temperature'.                                                                                                                                                                                                                                                                                  |

| Non-Operating            | 50,000 feet maximum                                                                                                                                                                                                                                                                                                                                                                                     |

#### Category II

| Characteristic                              | Requirement                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Humidity<br>Non-Operating                   | Instrument will perform to limits given in this section following 5 cycles (120 hours) of Mil-Std-202B, Method 106A (exclude freezing and vibration).                                                                                                                                             |

| Vibration<br>Operating and<br>Non operating | Instrument will perform to limits given in this section following vibration test. Vibrated for 15 minutes along each axis at a total displacement of 0.025-inch peak to peak (4G at 55 cps) from 10-55-10 cps in 1 minute cycles. Held for 3 minutes at 55 cps. Total vibration time, 55 minutes. |

| Shock<br>Operating and<br>Non-Operating     | Instrument will perform to limits given in this section following shock test. 30G, one-half sine, 11 millisecond duration. Two shocks each direction along each axis (total of 12 shocks).                                                                                                        |

| Transportation<br>Non-operating             | Meets National Safe Transit type of test when factory packaged. Package shake test—One hour in excess of 1G. Package drop test—30-inch drops on one corner, three edges and all flat surfaces (total of 10 drops).                                                                                |

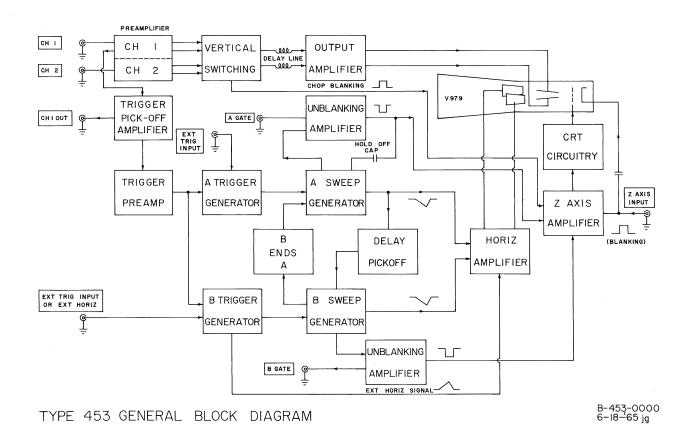

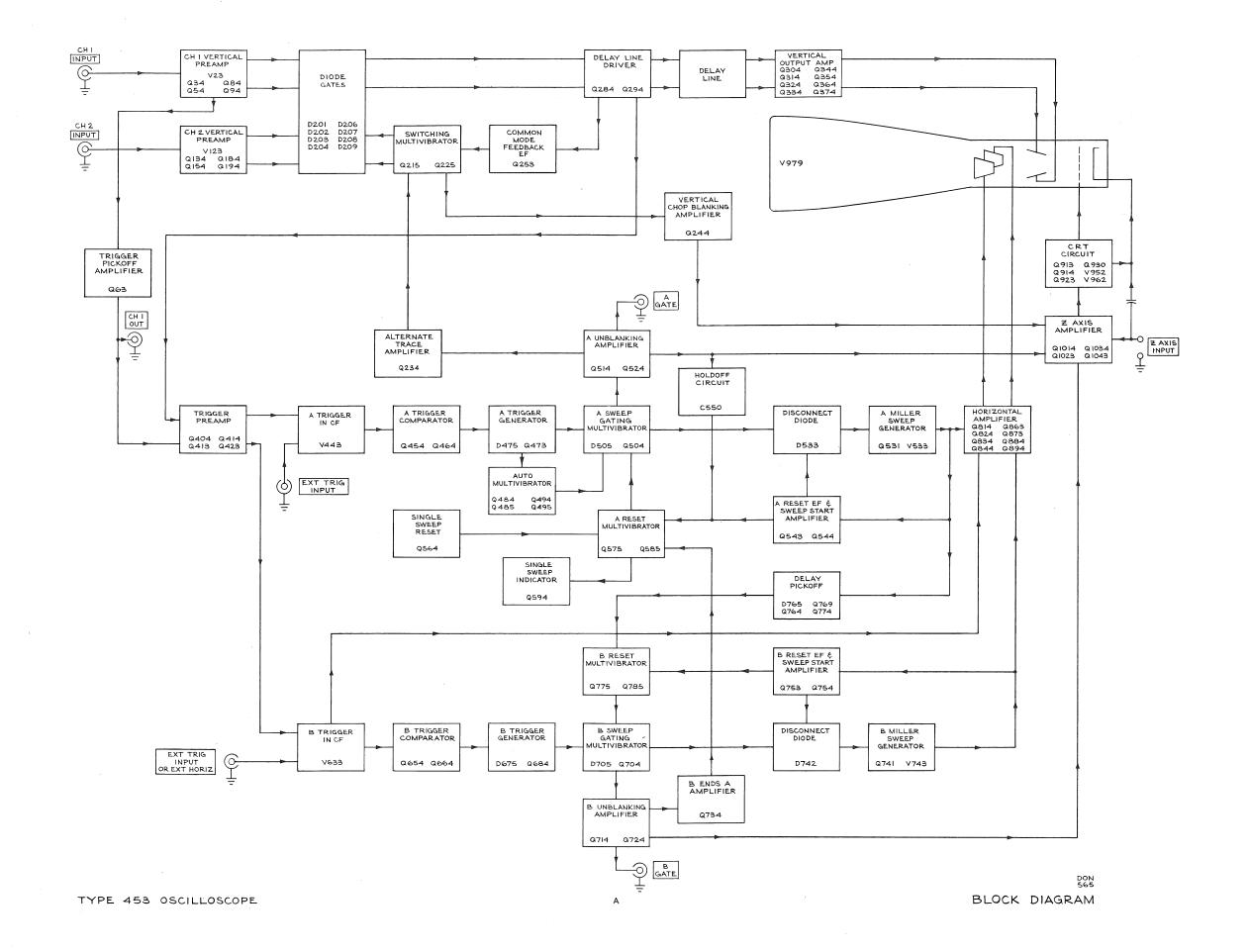

### D. Block Diagram

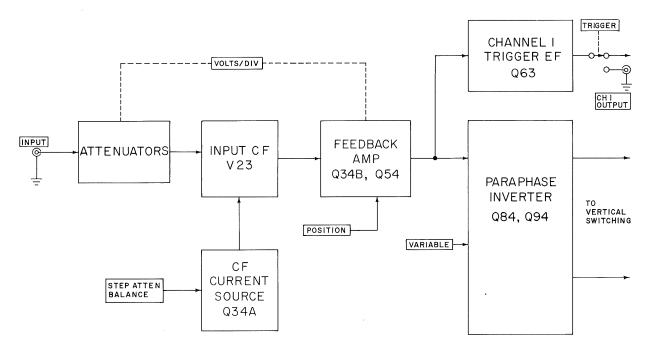

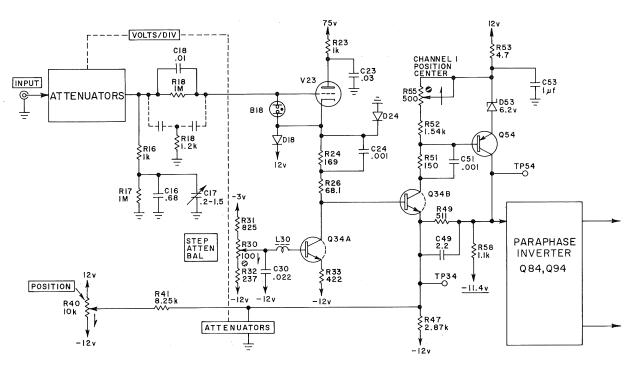

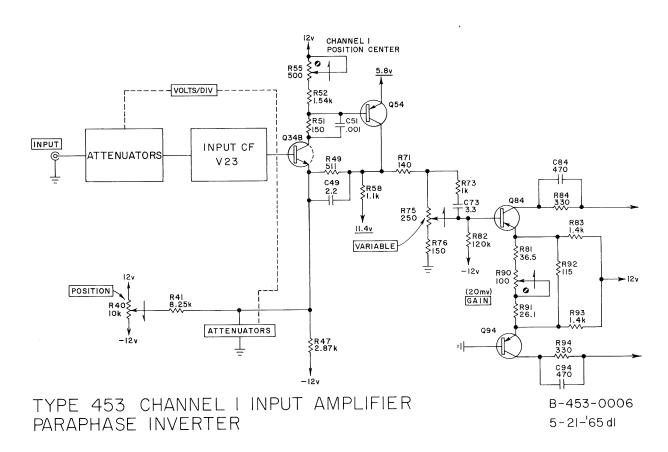

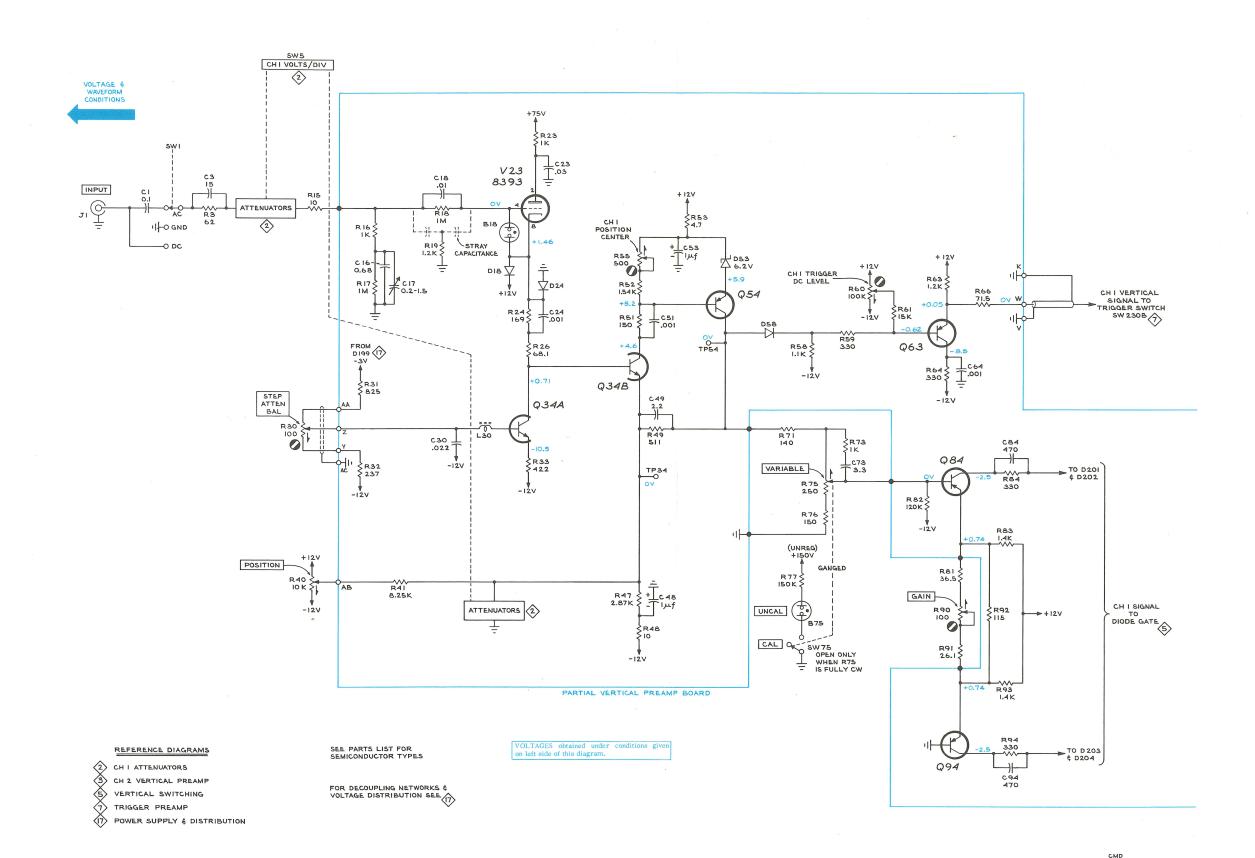

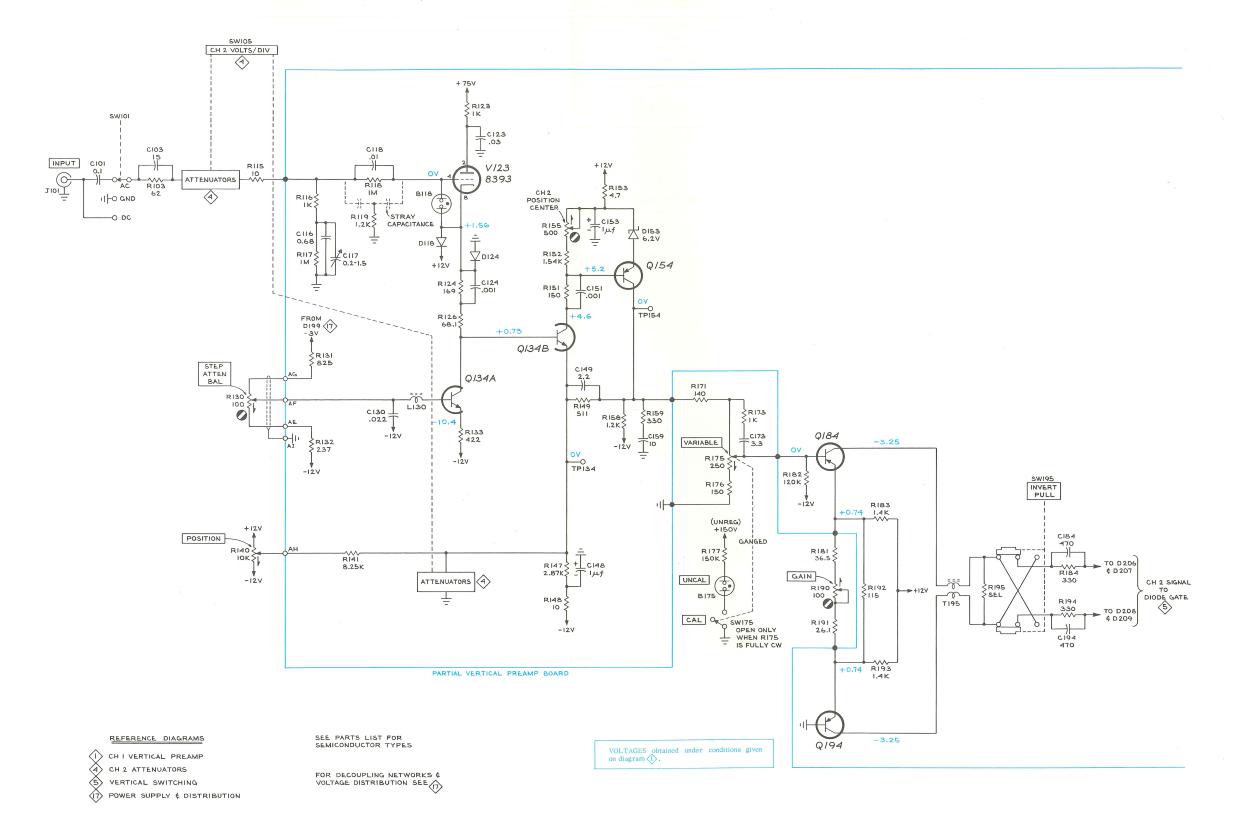

#### II. CHANNEL 1 INPUT AMPLIFIER

- A. The Channel 1 Input Amplifier amplifies and attenuates the input signal.

- The circuit provides a push-pull current drive to the Vertical

Switching circuit and the Vertical Amplifier.

- 2. A Channel 1 Trigger signal is also provided.

- B. Circuits that comprise the Channel 1 Input Amplifier.

- 1. Attenuator and Input Switches.

- 2. Input CF, V23.

- 3. CF Current Source, Q34A.

- 4. Feedback Amplifier; Q34B, Q54.

- 5. Paraphase Inverter; Q84, Q94.

- 6. Channel 1 Trigger EF, Q63.

#### C. Block Diagram

TYPE 453 CHANNEL I INPUT AMPLIFIER BLOCK DIAGRAM

B-453-000I 5-I2-<sup>1</sup>65dI

- D. Block Logic

- The Input Amplifier has a signal current output of about .5 ma/div per side.

- a. Since the amplifier has a voltage input and a current output, the signal transfer is rated as transadmittance\*.

- b. Transadmittance gain,  $T_{Y} = \frac{i_{out}}{e_{in}}$ .

- 2. Eleven sensitivity positions are available on the VOLTS/DIV switch from 5 mv/div to 10 v/div in 1, 2, 5 sequence.

- 3. Basic sensitivity of the vertical is 20 mv/div in all positions of the VOLTS/DIV switch from 20 mv/div to 10 v/div.

- 4. The amplifier changes its basic sensitivity in the 5 mv/div and 10 mv/div positions of the VOLTS/DIV switch.

- a. At 5 mv/div,  $T_Y = 100,000 \mu mhos$ .

(1)

$$T_{Y} = \frac{i_{out}}{e_{in}}$$

.

(2)

$$T_{Y} = \frac{.5 \text{ ma/div}}{5 \text{ mv/div}}.$$

(3)

$$T_{Y} = 100,000 \, \mu \text{mhos}$$

.

b. At 10 mv/div,  $T_{Y} = 50,000 \mu mhos$ .

(1)

$$T_{Y} = \frac{.5 \text{ ma/div}}{10 \text{ mv/div}}$$

(2)

$$T_{V} = 50,000 \, \mu \text{mhos}$$

.

c. At 20 mv/div and all other sensitivities (20 mv/div to 10 v/div),  $T_Y = 25,000 \text{ } \mu\text{m}$ hos.

(1)

$$T_{Y} = \frac{.5 \text{ ma/div}}{20 \text{ mv/div}}$$

(2)

$$T_V = 25,000 \mu mhos$$

.

<sup>\*</sup> See June 1963 Service Scope.

- d. Bandpass of the vertical is reduced in the 5 mv/div position to DC to 40 mc and at 10 mv/div to DC to 45 mc.

- 4. Input impedance is 1 megohm ±2% paralleled by 20 pF ±3%.

- 5. Input coupling is selected by means of a lever switch.

- a. AC, DC or GND is available.

- 6. The Input CF, a nuvistor, provides high input impedance.

- 7. A two stage transistorized feedback amplifier includes a section of the VOLTS/DIV switch that changes the basic gain of the amplifier.

- a. In the 5 mv/div position of the VOLTS/DIV switch, the Feedback Amplifier has a gain of 10.

- b. In the 10 mv position, the Feedback Amplifier gain is 5.

- c. In the 20mv position and all other positions, the Feedback Amplifier gain is 2.5.

- 8. The STEP ATTEN BAL control operating through the CF Current Source transistor, Q34A, adjusts potentials at the Feedback Amplifier so changing sensitivity positions will not shift the trace.

- 9. The POSITION control operating through the Feedback Amplifier has a range of about  $\pm 15$  divisions.

- 10. The output from the Feedback Amplifier at about 50 mv/div is fed via Channel 1 Trigger EF to the Trigger Preamp.

- a. The signal is attenuated in the EF circuit to about 25 mv/div.

- b. The EF also feeds the CH 1 OUT jack.

- 11. The single ended signal voltage output from the Feedback

Amplifier becomes a push-pull signal current in the Paraphase

Inverter.

- a. The VARIABLE VOLTS/DIV control has an attenuator range of  $\geq 2.5:1$ .

- 12. The current drive to the Vertical Switching circuit and Vertical Amplifier is about .5 ma/div per side.

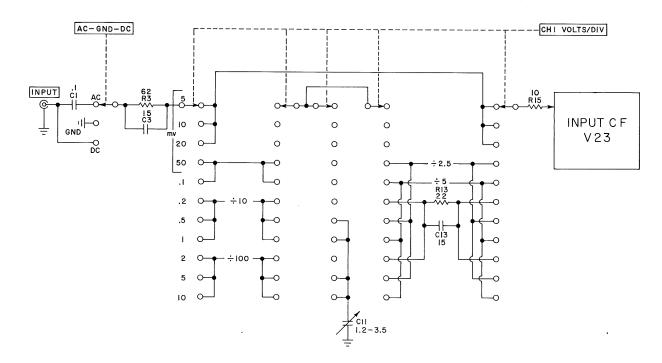

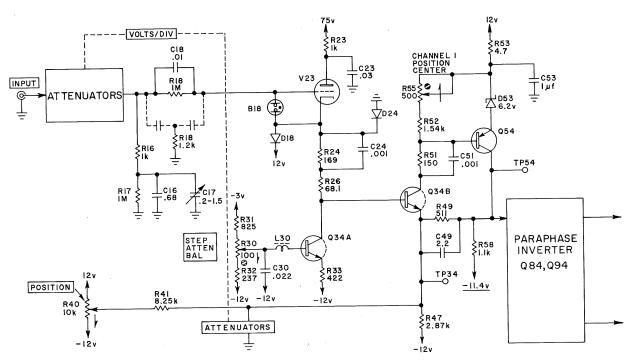

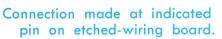

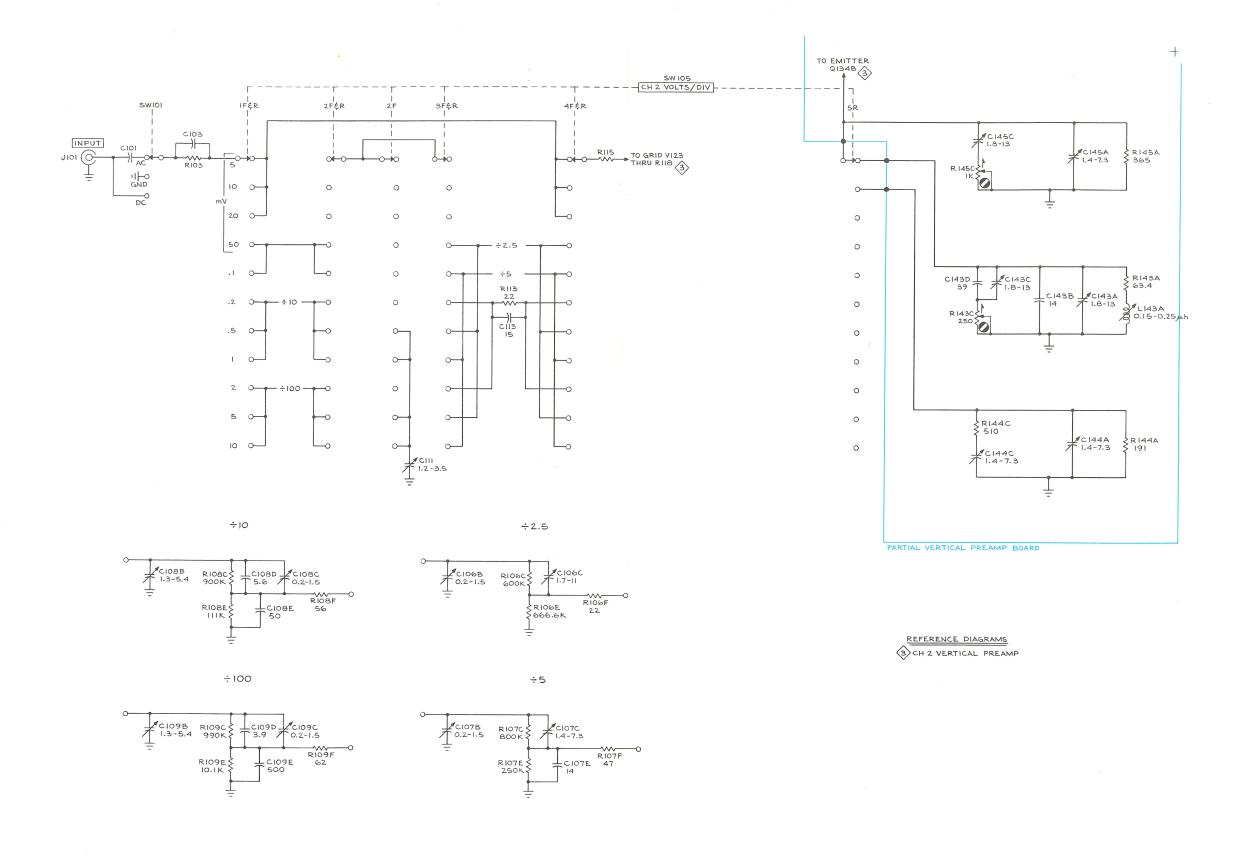

- E. Attenuators and Input Switches

- The circuit includes the Coupling Switch, a portion of the VOLTS/DIV switch and four attenuators.

TYPE 453 CHANNEL I INPUT AMPLIFIER ATTENUATOR SWITCHES

B-453-0002 5-13-<sup>1</sup>65 dl

- 2. The input jack is a BNC connector.

- 3. Input impedance is 1 megohm  $\pm 2\%$  paralleled by 20 pF  $\pm 3\%$ .

- 4. Input is limited to an excursion of  $\pm 600$  volts combined DC and peak AC.

- 5. A front panel level switch is used for coupling selection.

- a. The AC position inserts a .1 μF tubular capacitor.

- (1) Low frequency cut off is 1.59 cps.

- b. The GND position opens the input connection and grounds the Cathode Follower input through the attenuator.

- The DC position connects the input through the attenuators to CF input.

- 6. Stacked attenuators are used.

- a. The first bank (of attenuators) includes the  $\div 1$  (a straight wire), the  $\div 10$ , and  $\div 100$ .

- b. The second bank includes the  $\div 2.5$ , the  $\div 5$  and a  $\div 1$  position composed of a  $22\Omega$  anti-ringing resistor (R13) and its bypass capacitor, C13.

- 7. In the 5 mv, 10 mv and 20 mv/div positions, the attenuators are bypassed, thereby reducing stray C. The basic sensitivity of the Feedback Amplifier is changed in these three positions.

- a. Only two switch wafers are used instead of the five used in other positions.

- b. The jumper has about 3 pF capacitance.

- 8. R3 and R15 break up lead inductance, thereby prevent ringing.

- 9. In positions where attenuators are stacked (.5v, 1v, 5v and 10v positions), C11 is connected in shunt with the second attenuator bank.

- a. The X1 attenuator in the second bank has higher shunt capacitance than the  $\div 2.5$  and  $\div 5$  compensated attenuators.

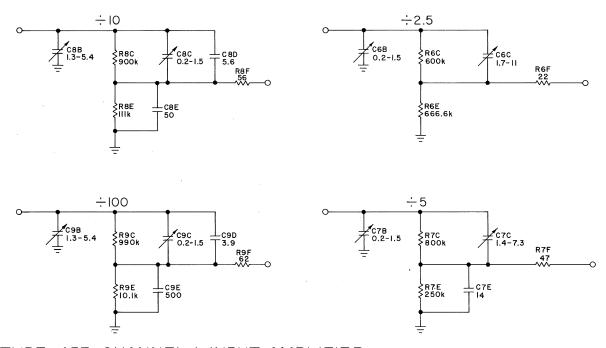

10. The attenuators are conventional compensated attenuators.

TYPE 453 CHANNEL I INPUT AMPLIFIER INPUT ATTENUATORS

B-453-0003 5-14-<sup>1</sup>65 dl

- a. 1% precision resistors are used in the X2.5 and X5 attenuators.

- b. 1/2% precision resistors are used in the X10 and X100 attenuators.

- c. Series resistors, R6F, R7F, R8F and R9F break-up lead inductance.

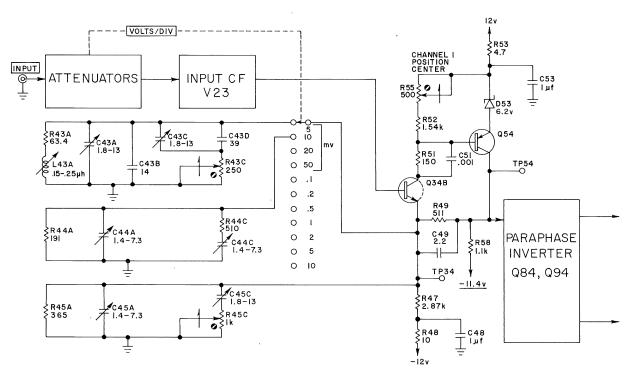

### F. Input CF, V23

The input CF provides a high Z input impedance and isolates

the input from any change in impedance as gain or sensitivity

of the amplifier is changed.

- 2. V23 grid current should not exceed 2 nanoamps.

- 3. V23 is an 8393 nuvistor with a mu of 35.

- a. The protective diodes are 6185 silicon diodes.

TYPE 453 CHANNEL I INPUT AMPLIFIER INPUT CF AND FEEDBACK AMPLIFIER

B-453-0004 5-17-<sup>1</sup>64 dl

- 4. The CF has a gain of about .97.

- a. With the high Z cathode tail through Q34A, gain is about

$$\frac{\mu}{\mu + 1}$$

- 5. Circuit protection:

- a. The input is limited to  $\pm 600v$  (including DC and peak AC).

- b. R18 limits V23 grid current to 600  $\mu a$  if the input is raised to 600 $\nu$ .

- (1) C18 bypasses the protective resistor for AC.

- (2) C18 provides charging current for V23 input C.

- c. B18 provides protection when V23 grid is dropped below its cathode.

- (1) B18 ignites at about 80v and sustains at about 60v.

- (2) V23 is protected from grid-cathode arc-over.

- d. D24 protects V23 grid during tube warm-up.

- (1) V23 cathode is prevented from dropping below -.6v.

- e. D18 protects Q34A from base-collector breakdown.

- (1) D18 conducts if V23 cathode is lifted above 12v.

- 6. C17 is used to standardize the input at 20 pF in the "straight through" positions.

- 7. R17 provides the 1M input resistance in the straight through positions.

- a. R17 is also part of the attenuator network at all VOLTS/DIV positions above 20 mv/div.

- 8. R16, C16 and C17 compensate for an increase in V23 input C as the input signal frequency increases.

- a. V23 input C is about 5 pF at low frequency.

- b. At higher frequency, the input C increases until at 100 mc it reaches about 11 pF.

- (1) Since the cathode cannot follow the grid without some delay at high frequencies, the input appears more capacitive.

- (2) The negative resistance component is about  $900\Omega$ .

- c. At low frequencies, the parallel equivalent of R16, C16, C17 and the stray capacitance of R17 appears as a very high resistance in shunt with about 2.5 pF.

- (1) This C plus additional C around R18 is in shunt with V23 input C.

- d. At high frequencies, the parallel equivalent appears as a much lower R in shunt with a much lower value of C.

- e. Since the equivalent shunt capacitance decreases as V23 input C increases, the total input and shunt C remains fairly constant.

- f. The equivalent shunt resistance matches the negative resistance input of V23.

- 9. R16, R17, R18, C18 and C16 are mounted on stand-off insulators to prevent a dielectric hook.

- a. If the components were mounted on the PC board, dielectric changes with frequency (of the PC board base material) would cause an overshoot to an increasing voltage step -hook effect.

- b. However, capacitive coupling from the stand-off insulators to the PC board dielectric still introduced hook.

- c. To correct this effect, a tie point was placed on the PC board at a point equidistant from the ends of R18.

- d. A strap was installed to the sleeve of each of the stand-off insulators supporting R18 and tied to the tie point.

- e. The tie point could have been tied to ground, thereby removing the hook.

- f. Using a 1.2k resistor (R19) to connect the tie point to ground, however, served two purposes.

- (1) The stand-off insulator's C was now returned to ground instead of to the PC board dielectric.

- (2) The series RC circuit, thus formed, supplements the circuit composed of R16, C16 in compensating for the increasing C (with frequency) of V23 input.

- 10. R23, C23 decouple V23 plate supply.

- 11. R24 and R26 set the Q34B base level.

- a. C24 improves the transient response.

#### G. CF Current Source, Q34A

- 1. Q34A is a constant current source for V23.

- a. Long tail resistance seen by the CF is about 100k.

TYPE 453 CHANNEL I INPUT AMPLIFIER INPUT CF AND FEEDBACK AMPLIFIER

B-453-0004 5-17-<sup>1</sup>64 dl

- 2. Q34A is a variable current source for V23.

- a. Using the STEP ATTEN BAL control, V23 current is adjusted so that Q34B emitter sets at zero volts DC.

- b. Under this condition, the VOLTS/DIV switch can be rotated to change Q43B emitter resistance to ground without causing a trace shift.

- 3. Q34A is half a 151-139, a silicon NPN dual transistor -- a dual 151-109.

- a. The other half is Q34B.

- b. The two transistors in one can provide temperature compensation through common environment.

- c. R33, Q34A emitter resistance matches its collector load (R24, R26 and V23  $\, Z_{\rm k}$ ).

- d. Q34A, therefore, has a gain of 1 so any thermal change in Q34A will exactly match the change in Q34B.

- 4. Q34A base, connected to the STEP ATTEN BAL control, can set voltages (at its base) from -9.4v to -10.2v.

- 5. To minimize the effect of any noise from the -12v supply on Q34A output, the base and emitter are both returned to -12v.

- a. The -3v is zener referenced to -12v so the entire STEP

ATTEN BAL control moves with any -12v supply changes.

- b. C30 AC couples -12v noise directly to Q34A base to change Q34A input C.

- 6. L30 suppresses an oscillation.

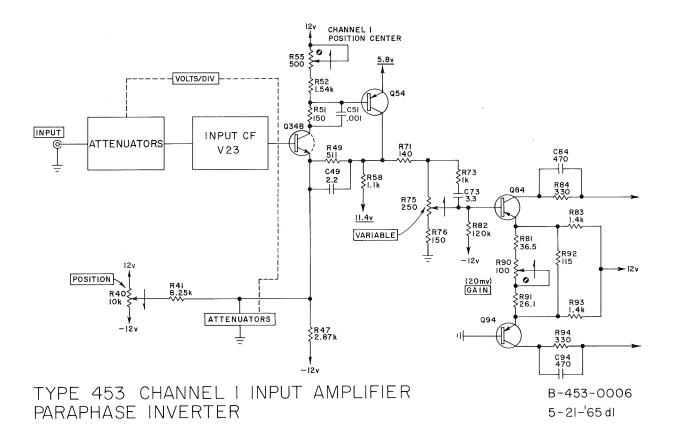

#### H. Feedback Amplifier; Q34B, Q54

- The Feedback Amplifier consists of a transistor pair in feedback configuration that controls the basic sensitivity of the CH 1 Input Amplifier.

- a. Q34B is half a 151-139 -- Q34A is the other half.

- b. Q54 is a 151-167 silicon PNP transistor.

- c. D53 is a 152-166, 6.2v, 5% zener.

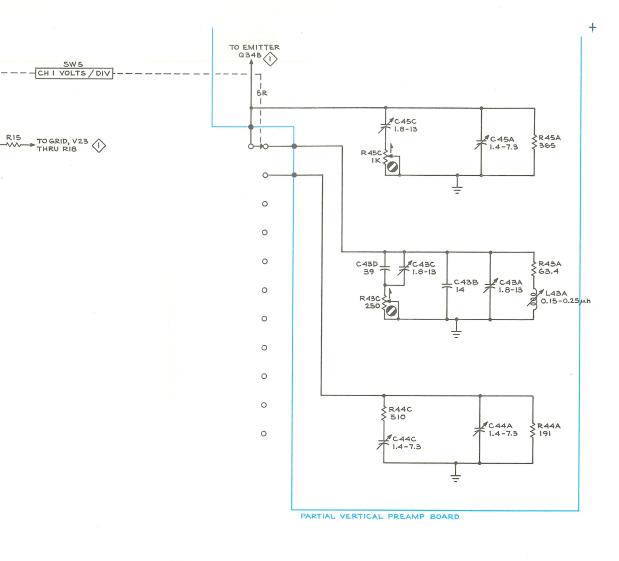

TYPE 453 CHANNEL I INPUT AMPLIFIER FEEDBACK AMP AND MV ATTENUATORS

B-453-0005 5-20-'65dl

- 2. Gain of the Feedback Amplifier is changed by settings of the VOLTS/DIV control as different values of  $R_{\alpha}$  are switched in .

- As a feedback amplifier, gain is virtually independent of transistor beta.

- a.  $A = 1 + \frac{R_f}{R_a}$

- (1)  $R_f$  is R49.

- (2) R<sub>a</sub> is primarily various values switched in by the VOLTS/DIV switch -- R47 is in shunt as part of R<sub>a</sub>.

- b. In the 5 mv position, A = 10.

- (1)  $R_a$  is R43A in shunt with R45A and R47.

- (2)  $A = 1 + \frac{511}{54}$ .

- (3)  $A \approx 10$ .

- c. In the 10 mv position, A = 5.

- (1)  $R_a$  is R44A in shunt with R45A and R47.

- (2)  $A = 1 + \frac{511}{125}.$

- (3)  $A \approx 5$ .

- d. In the 20 mv position and all other positions, A = 2.5.

- (1)  $R_a$  is R45 in shunt with R47.

- (2)  $A = 1 + \frac{511}{322}$ .

- (3)  $A \approx 2.5$ .

- 4. Proper setting of the STEP ATTEN BAL control sets Q34B emitter at 0v DC.

- a. With Q34B emitter and the VOLTS/DIV switch arm at 0v, different values of  $R_{\alpha}$  can be switched in without altering static current into the Feedback Amplifier.

- b. No trace shift occurs as the switch is rotated.

- 5. Each  $R_a$  value (switched in by the VOLTS/DIV switch) is compensated.

- a. Essentially the time constants for  $R_{\mathrm{f}}$  and  $R_{\mathrm{a}}$  should be the same.

- b. Additional RC and RL networks provide adjustable HF correction for losses in the Feedback Amplifier, thereby improving transient response.

- c. No provision is made for adjusting gain in each sensitivity position.

- (1) R49, R43A, R44A and R45A are 1% resistors.

- 6. R48, C48 decouple the emitter return from the 12v supply.

- 7. Q54 emitter is set at 5.8v by D53, a 6.2v zener.

- a. R53, C53 decouple the 12v supply.

- 8. R51 provides current limiting.

- a. If V23 cathode is raised to its 12v limit (limited by D18),

Q34B and Q54 will saturate.

- b. Without R51, a low resistance path exists through R53, D53, saturated Q54, saturated Q34B and R $_{a}$  (63 $\Omega$  in 5 mv position) to ground.

- c. About 80 ma would flow through the circuit under this condition.

- d. R51 reduces the saturation current to about 24 ma.

- (1) C51 is a speed-up cap.

- 9. The POSITION control varies trace position  $\pm 13.5$  div to  $\pm 16.5$  div.

- a. The control has a swing of  $\pm 12v$ .

- b. R41 is R; for the Feedback Amplifier.

- c. Current into Q34B emitter is varied ±1.45 ma.

- d. Since Q34B emitter is a low Z point, the value of R<sub>a</sub> (as switched in by the VOLTS/DIV switch) has practically no effect on the action of the POSITION control.

- 10. R55 (the CH 1 POSITION CENTER adj) is adjusted to place Q54 collector at ground potential\*.

- a. The POSITION control is first set with the arm at 0v.

<sup>\*</sup> See Page 2-17.

- 11. R58 supplies Q54 collector current -- 10 ma.

- 12. Signal level at the Feedback Amplifier output is about 50 mv/div.

- 1. Paraphase Inverter; Q84, Q94

- The Paraphase Inverter provides a push-pull drive to the Vertical Amplifier.

- Since the Vertical Driver Amplifier is an operational amplifier,

the Paraphase Inverter functions as a current drive.

- b. The collector load appears in the Vertical Amplifier circuit.

- c. Signal current out of the Paraphase Inverter is .5 ma/div per side.

- 2. Q84 and Q94 are 151-167 silicon PNP transistors.

- With the Feedback Amplifier output (Q54 collector) at ground potential (set by the CH 1 POSITION CENTER control), the VARIABLE control has no static current through it.

- a. R82 supplies Q84 base current, so Q84 base and the VARIABLE control arm are also at 0v DC.

- (1) Ov on Q84 base matches the grounded Q94 base.

- b. Rotating the VARIABLE control, therefore, does not change the static current into Q84 -- the trace does not shift.

- DC balance is achieved, however, only when the trace

is centered by the POSITIONING control.

- 4. R71 and R76 maintain a reasonably constant impedance as seen by Q84 base as the VARIABLE control is rotated.

- a. R76 (150 $\Omega$ ) below the control is matched by R71 plus the Feedback Amplifier output impedance above the control.

- b. The impedance seen by Q84 base swings from  $110\Omega$  to  $138\Omega$  with rotation of the control --  $138\Omega$  at control center.

- (1) This variation in impedance causes about 4% risetime degradation at the control center.

- c. R73, C73 improve the transient response of the circuit.

- 5. Signal voltage at Q84 base is about 36 mv/div with the VARIABLE control in its calibrated position and 14 mv/div fully CCW.

- a. The control has an attenuation range of a little more than 2.5:1.

- b. An UNCAL light lights when the control is moved off the fully clockwise detent.

- c. The control attenuates the range of the POSITION control to  $\pm 6$  div.

- 6. R84 and R94 provide thermal balance\* for the push-pull stage.

- a. C84 and C94 bypass the thermal balance resistors, thereby reducing miller capacitance.

- b. The capacitors prevent HF signal voltages from being developed across R84 and R94.

- c. If the paraphase inverter has no voltage gain at high frequencies, miller capacitance cannot exist.

- 7. Static collector current is 8 ma per side.

- 8. R90, the (20 mv) GAIN adj, is a front panel screwdriver adjustment.

- a. The 20 mv label indicates the recommended position of the VOLTS/DIV switch when adjusting the control.

- b. R81 and R91 limit the minimum emitter tying resistance.

- (1) Two resistors are used (one on each end of the control) as damping resistors to break up lead inductance.

- c. R92 reduces the range of the control to an effective  $27\Omega$ .

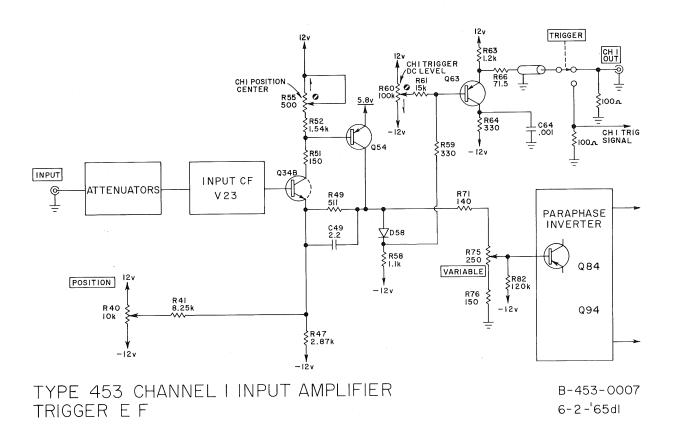

#### J. Trigger EF, Q63

- The Trigger EF supplies a single ended trigger signal to the Trigger

Preamp.

- The signal is used in the CH 1 only position of the TRIGGER

(CH 1 NORM) switch.

$i \neq j$

<sup>\*</sup> See Transistor Program, Volume 7, Page 111.

b. In the NORM position, the signal is connected to the CH 1OUT jack.

- 2. Q63 is a 151-133 silicon PNP transistor.

- a. D58 is a 6185 silicon diode.

- 3. The signal at Q63 base is about 50 mv/div.

- 4. R66 and the transistor,  $r_e$ , provide an approximate impedance match for the inter-chassis coax.

- a. The value for R66, however, was chosen to assure greater than 25 mv output to the CH 1 OUT jack.

- b. Losses through the CF and in coupling to the EF deliver slightly less than 50 mv/div at Q63 base.

- c. R66, Q63  $\rm r_e$  and a 100 $\Omega$  resistor at the CH 1 OUT form a divider that delivers about 27  $\rm vm/div$ .

- d. The "greater than 25 mv/div" output is useful when cascading CH 1 and CH 2 Input Amplifiers

- The CH 2 VARIABLE (VOLTS/DIV) control can be used to calibrate the sensitivities of the cascaded amplifiers.

- e. The ≈27 mv/div level is also useful when using the CH 1

Input Amplifier to feed an external signal to the Horizontal

Amplifier\*.

- (1) The EXT HORIZ GAIN adj is used to calibrate the total sensitivities of the CH 1 Input Amplifier, the Trigger Preamplifier and the Horizontal Amplifier.

- f. Output Z is  $\approx 50\Omega$ .

- g. Frequency response is DC to >25 mc at 30% down at <1 mv/div.</p>

- 5. D58 temperature compensates Q63 base-emitter junction.

- a. Equal currents (10 ma) through the two junctions assure

maximum matching of junction drops as temperature changes.

- 6. CH 1 TRIGGER DC LEVEL sets the DC level at zero volts at the Trigger Preamp output.

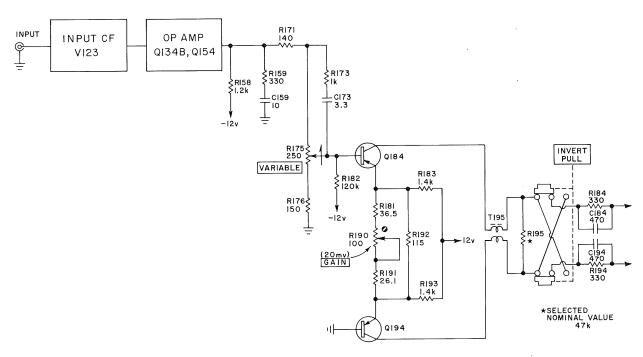

#### III. CHANNEL 2 INPUT AMPLIFIER

- A. The Channel 2 Input Amplifier is the same as Channel 1 Input Amplifier with two exceptions.

- 1. The addition of an INVERT PULL switch.

- 2. The amplifier does not have a Trigger EF.

- 3. Crosstalk between channels is 100:1 to 20 mc.

TYPE 453 CHANNEL 2 INPUT AMPLIFIER PARAPHASE INVERTER, INVERT SWITCH

B-453-0008 6-3-<sup>1</sup>65dl

#### B. Invert Switch Circuit

- 1. The INVERT PULL switch merely inverts the Channel 2 output.

- a. The inverted signal is useful when operating in the ADD mode.

- b. The trace should not shift more than  $\pm 1$  div from graticule center.

- 2. It is important that the transient response of the two input amplifiers match.

- a. The output C of Channel 2 is greater, however, by the C added by the INVERT switch.

- (1) The physical location of R184, C184, and R194, C194 at a location farther from the transistors also increases the shunt C.

- 3. R195, a selected resistor (typically 47k), is used to match the response of the two amplifiers.

- a. The  $T_c$  of Channel 2 (without R195) will always be greater than that of Channel 1.

- b. The addition and selection of R195 can be used to reduce the T<sub>C</sub> of Channel 2 to match that of Channel 1.

- c. New transistors in <u>either</u> Paraphase Inverter will probably require a new resistor.

- d. T195 suppresses an oscillation in ADD mode.

- C. There is no trigger take-off from the CH 2 Input Amplifier, therefore, no Trigger EF.

- 1. R159, C159 provide a load equal to that of the Trigger EF in the CH 1 Input Amplifier.

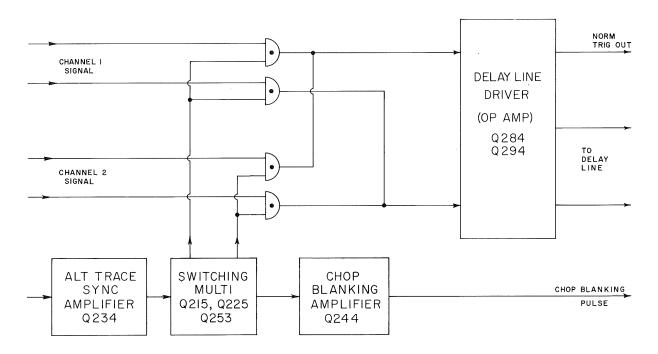

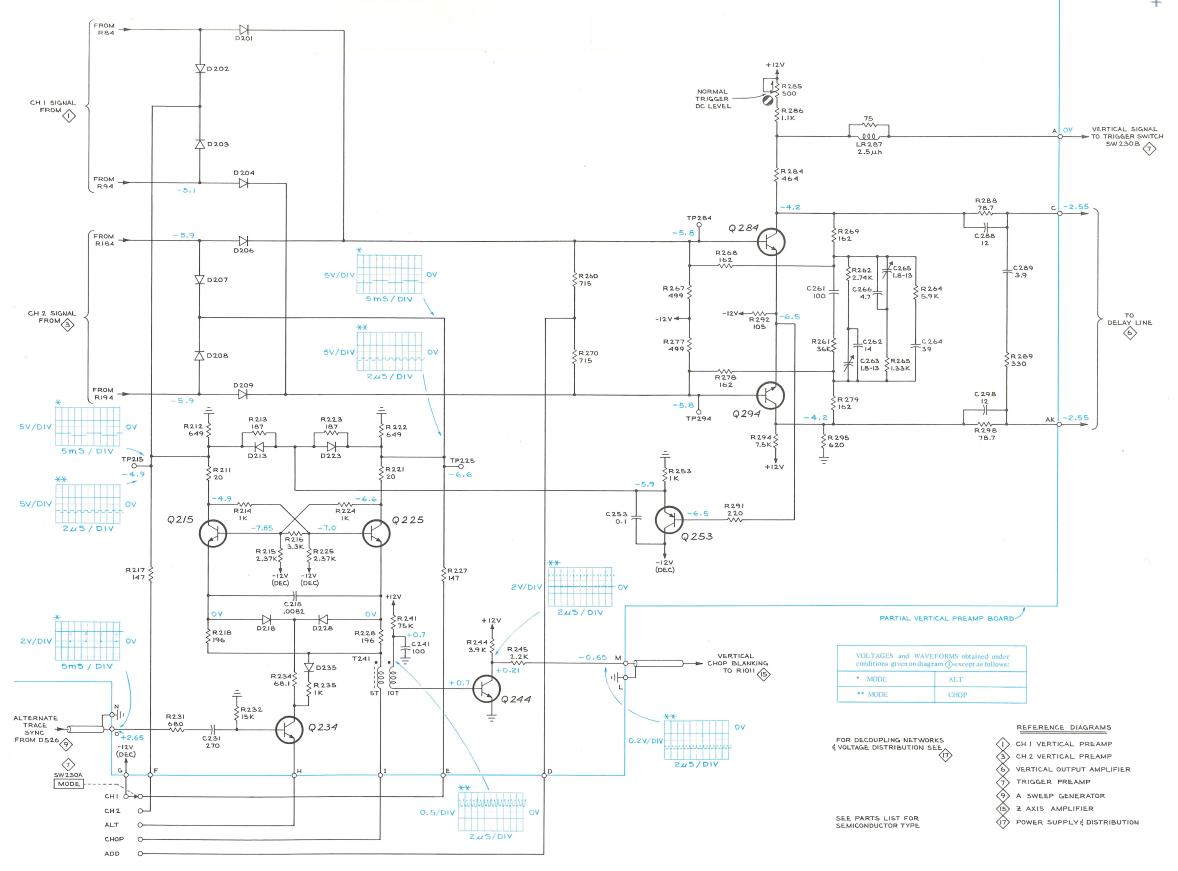

#### IV. VERTICAL SWITCHING

- A. The Vertical Switching circuit determines which of the Input Vertical Preamp signals is connected to the Vertical Output Amplifier.

- The vertical signal is amplified in the Delay Line Driver

Amplifier before being fed to the Delay Line.

- 2. A Vertical Chop Blanking pulse is generated.

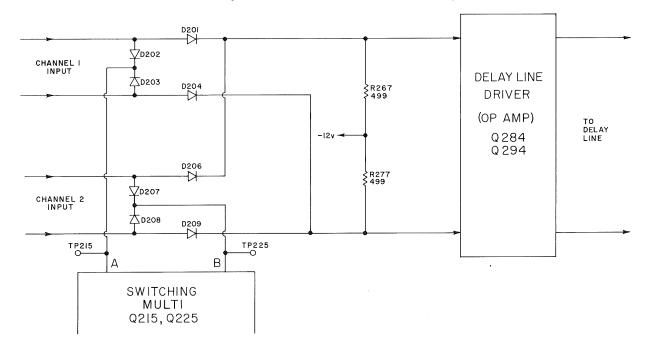

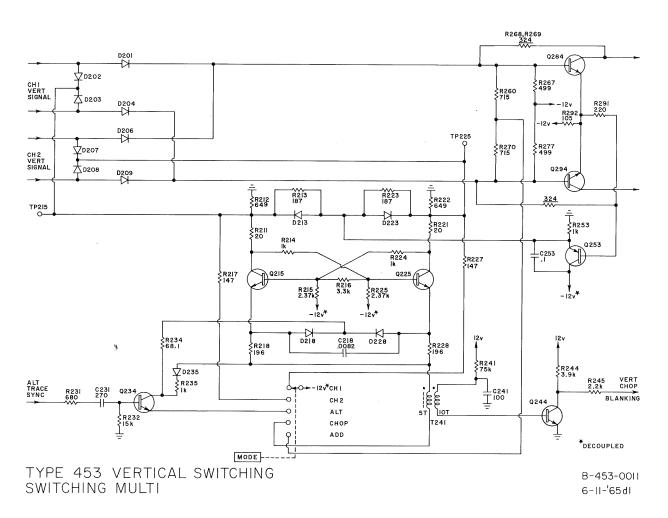

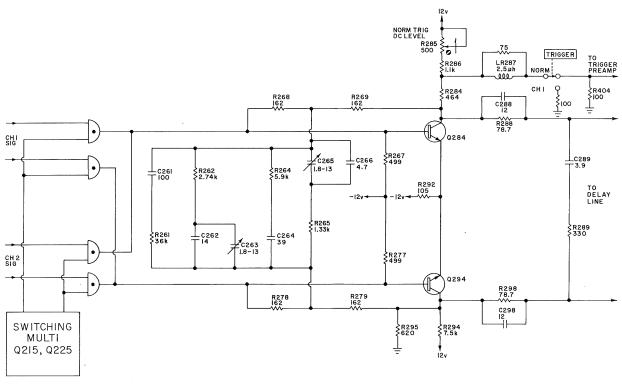

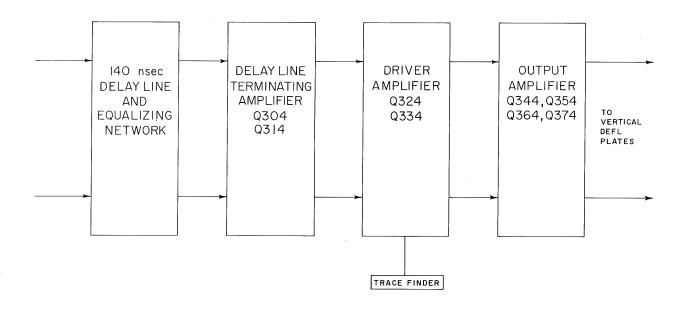

#### B. Block Diagram

TYPE 453 VERTICAL SWITCHING AND DRIVER AMP BLOCK DIAGRAM

B-453-0009 6-4-65dl

- C. Circuits that comprise the Vertical Switching circuit:

- 1. Switching Logic Gate.

- 2. Delay Line Driver Amplifier; Q284, Q294.

- 3. Switching Multi; Q215, Q225, Q253.

- 4. Alternate Trace Sync Amplifier, Q234.

- 5. Chop Blanking Amplifier, Q244.

#### D. Block Logic

- The output from each Vertical Preamp is a signal current about

5 ma/div per side.

- a. 8 ma of static current also flows in each output lead.

- b. DC level is -6v when the channel is off and -5v when connected to the Delay Line Driver Amplifier.

- c. The small change in voltage as switching occurs helps

maintain thermal balance in the CH 1, CH 2 Paraphase

Inverter.\*

- 2. The Switching Logic Gates switch the signal and static currents.

- a. When ON, the signal currents drive the Delay Line Driver

Amplifier.

- b. When OFF, the signal and static currents are shunted through the Switching Multi circuit.

- 3. The Switching Multi controls the action of the Logic Gates.

- 4. Five modes of operation may be selected by the MODE switch.

- a. CH 1: The output from the Channel 1 Input Amplifier is selected.

- b. CH 2: The output from the Channel 2 Input Amplifier is selected.

- c. ALT: The outputs from the two Input Preamplifiers are selected alternately at the end of each sweep.

- d. CHOP: Signal from Channel 1 and Channel 2 are switched at a 500 kc rate.

<sup>\*</sup> See Transistor Program, Volume 7, Page 111.

- e. ADD: The outputs from the two Input channels are added algebraically -- CMR is ≥20:1 at 20 mc for common mode signals up to 8 divisions.

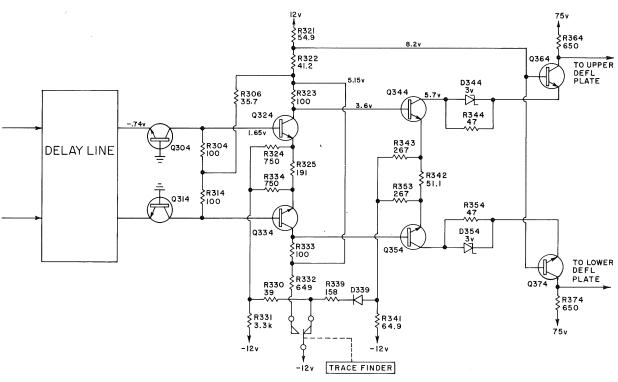

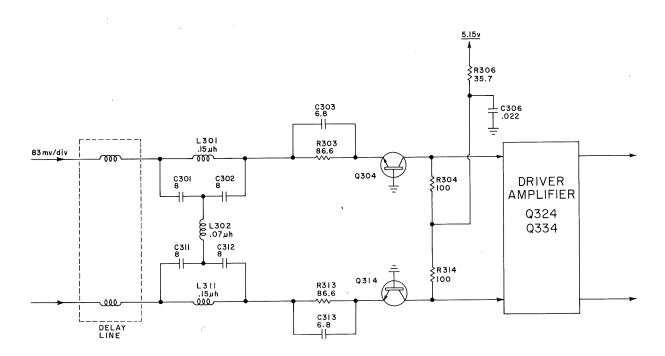

- 5. The vertical signal is amplified in the Delay Line Driver Amplifier to drive the Delay Line.

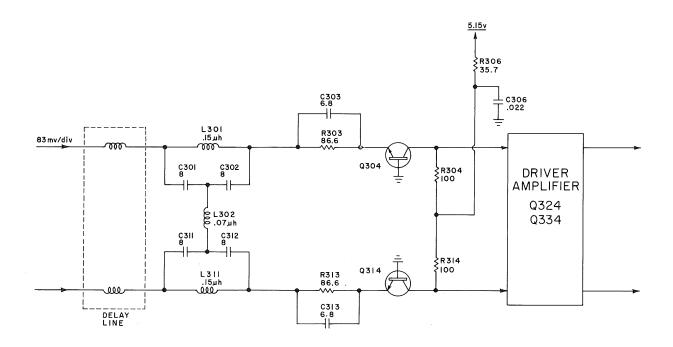

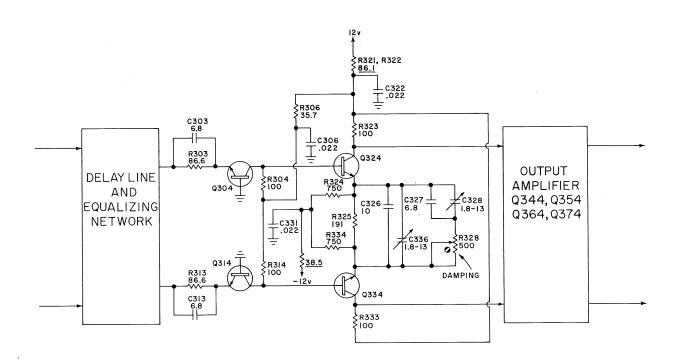

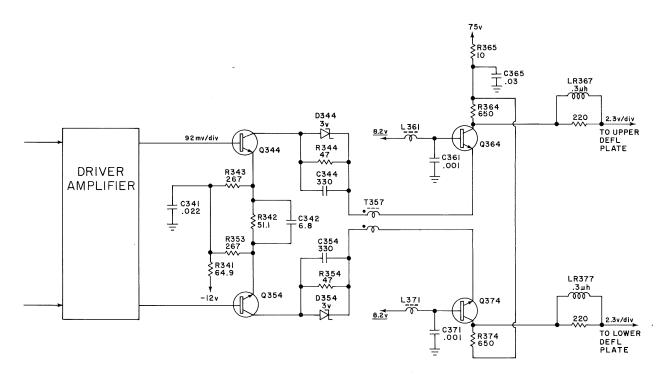

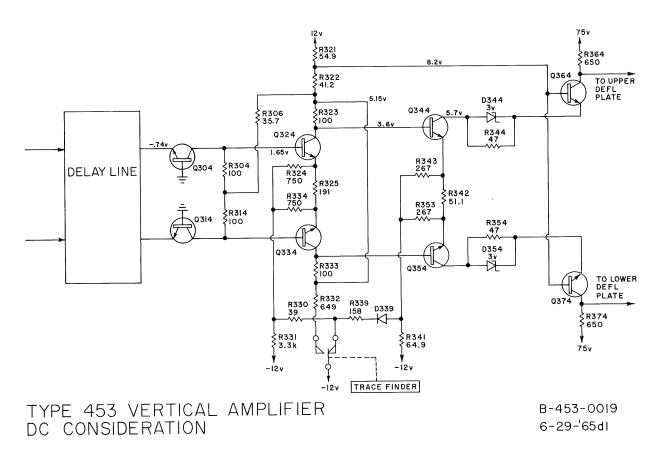

- a. Signal voltage into the delay line is 83 mv/div each side.

- b. Signal current into the delay line is .9 ma/div.

- 6. A Chop Blanking signal is fed to the CRT circuit to blank switching transients in the CHOP mode.

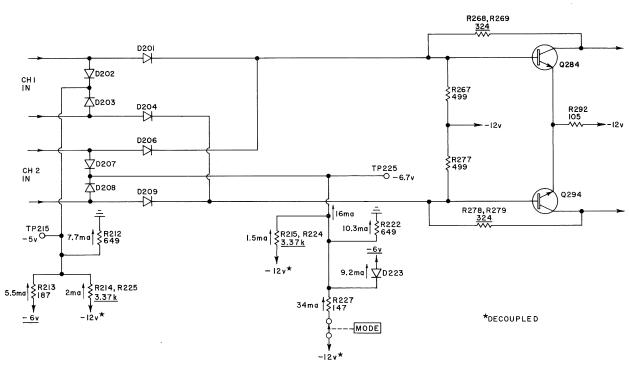

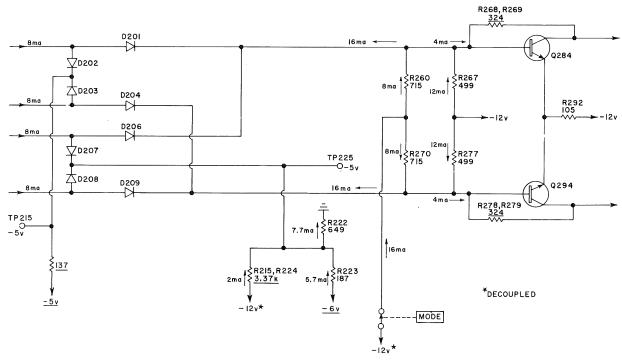

## E. Switching Logic Gates

- The Switching Logic Gates consist of two sets of four diodes in bridge configuration.

- a. One logic gate for Channel 1 and a gate for Channel 2.

- b. All eight diodes are 1N3605 silicon signal diodes.

- 2. Switching voltage for the Logic Gates is supplied by the Switching Multi.

- The switching voltage (from the Multi) swings from -5v to

-6.7v.

- 3. About 8 ma of static current flows through each of the diodes (D201, D204, D206, D209) in the signal path.

- a. The 8 ma supplies the Paraphase Inverter collectors (CH 1 and CH 2 Input Amplifiers).

- b. About .5 ma/div of signal current flows through each diode.

- c. The signal current drives the Delay Line Driver Amplifier.

- d. The static current is supplied through R267 and R277 from -12v.

- 4. The signal buses into the Delay Line Driver Amplifier set at about -6v.

- 5. When a signal path is opened by the Logic Gate, the signal current and the static current flows through the Multi circuit.

- 6. Assume that Multi output B (TP225) is at -5v and output A (TP215) is at -6.7v.

- a. D202 and D203 will conduct as their cathodes are pulled down to -6.7v.

- D201 and D204 cut off as their anodes are pulled down to -6.1v.

- c. Collector current for the CH 1 Input Amplifier Paraphase Inverter transistors is now supplied by the Multi circuit.

- d. Channel 1 is opened.

- e. D207 and D208 cathodes are lifted to -5v cutting them off.

- f. D206 and D209 conduct -- the 8 ma static current and

.5 mv/div signal current flows through each diode.

- g. Channel 2 signal current drives the Delay Line Driver.

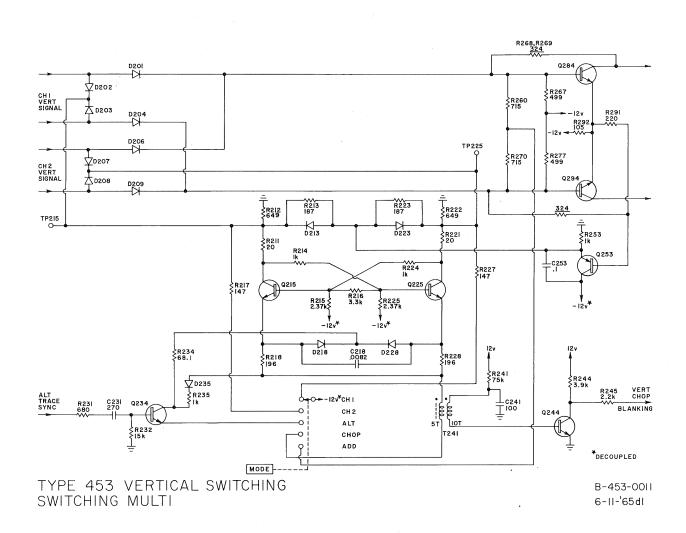

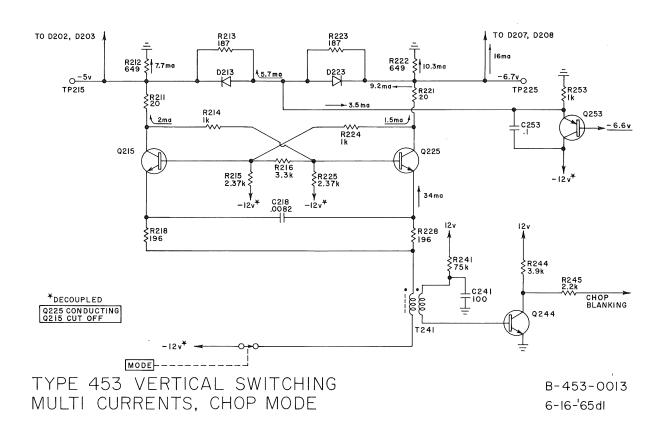

- F. Switching Multi, Alternate Trace Sync Amplifier and Chop Blanking Amplifier; Q215, Q225, Q253, Q234, Q244.

- 1. The Switching Multi is a transistorized multi that may be operated in either an astable or bistable mode.

- 2. The circuits use five transistors and four diodes.

- a. Q215 and Q225 are 151-136, 2N3053 silicon NPN transistors.

- b. Q234 and Q244 are 151-108, 2N2501 silicon NPN transistors.

- c. Q253 is a 151-087, 2N1131 silicon PNP transistor.

- d. D213 and D223 are 6185 silicon diodes.

- e. D218 and D228 are 1N3605 silicon diodes.

- The Multi transistors receive emitter current through the MODE switch.

- a. In CHOP and ALT modes, emitter current is supplied.

- b. In all other modes, the Multi is turned off.

- c. In CHOP mode, the multi is a stable; switching at a 500 kc rep rate  $\pm 20\%$ .

- d. In the ALT mode, the Multi is connected for bistable operation, switching with a trigger at the end of each sweep.

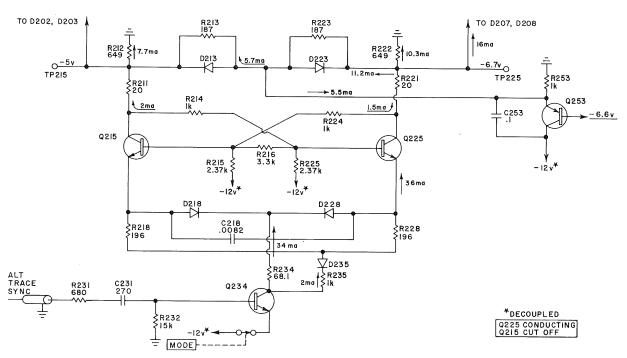

- 4. Operation in the ALT mode:

- a. Quiescently, Q234 is saturated.

- (1) The base is returned to ground.

- (2) Q234 emitter is tied to -12v\* (decoupled) through the MODE switch.

- b. Assume Q225 is conducting and Q215 is cut off.

- (1) TP225 sets at -6.7v and TP215 sets at -5v.

<sup>\* -12</sup>v decoupled sets at about -11.5v.

- c. D228 is conducting Q225 emitter current (about 34 ma through D228).

- (1) A shunt current path through R235, D235 passes about 2 ma.

TYPE 453 VERTICAL SWITCHING MULTI CURRENTS, ALT MODE

B-453-0012 6-14-<sup>1</sup>65dl

- d. Q225 collector is pulled down to -6.7v.

- e. Q225 base sets at -7.5v; Q215 base at -8.4v.

- f. Q225 emitter sets at -8.2v; Q215 emitter at -8.5v.

- (1) The divider composed of R228, D235 and R235 sets

Q215 emitter level.

- (2) C218 is charged to 300 mv.

- g. At the end of sweep, the negative going Alt Trace sync pulse cuts off Q234.

- (1) The pulse is a negative step differentiated in C231, R232.

- (2) The pulse has a time constant of about 4 µsec.

- h. Q234 cuts off for the pulse duration.

- i. Robbed of emitter current, Q225 cuts off.

- (1) Both Q215 and Q225 are cut off for the pulse duration.

- j. Q225 collector (TP225) rises to -5v.

- As Q234 again saturates (after the sync pulse has passed),

Q215 conducts.

- (1) During the time both transistors were cut off, the bases were set by the cross coupled network at -8.4v.

- (2) The 300 mv charge on C218 places Q215 emitter more negative than Q225 emitter.

- (3) The charge on C218 (the commutator capacitor) directs

Q215 to turn on.

- e. Through multi action, Q225 is held cut off until the arrival of the next sync pulse.

- 5. When Q225 is conducting, D207, D208 are pulled into conduction.

- a. Channel 2 is cut off.

- b. The 16 ma collector current for the Channel 2 Paraphase Inverter is supplied by Q225.

- c. 36 ma flows through Q225 and 1.5 ma through R224, R215.

- d. In addition to the 16 ma through D207, D208, 10.3 ma flows through R222 to ground, and 11.2 ma flows through D223.

- (1) D223 clamps TP225 negative excursion at -6.7v.

- 6. Q215 collector sets at -5v (when cut off) lifting D202, D203 to cut off.

- 7. Q253 is an emitter follower connected in a DC feedback circuit whose purpose is to maintain the same voltage drops across the gate diodes even though the DC level on the signal buses might change.

- a. Q253 base samples the DC level at Q284, Q294 common emitters (nominally -6.7v).

- The voltage on Q253 base is stepped .7v less negative to -6v at the emitter and back to -6.7v at D223 cathode (assuming Q225 conducting).

- at D206, D209 anodes to -6v.

- d. Q284, Q294 base-emitter junction in turn places their bases at -6v.

- e. D206 and D209, therefore, appear to be zero biased.

- f. Q284, Q294, however, have a slightly greater baseemitter junction drop than Q253.

- (1) Q284, Q294 each conduct about 26 ma.

- (2) Q253 conducts a maximum of 3.2 ma.

- g. The difference in junction drops reverse biases D206,

D209 about 100 mv, assuring cut-off of the channel.

- 8. When both multi transistors are cut off, for the duration of the ALT trace pulse, all four of the series diodes (D201, D204, D206 and D209) conduct.

- a. 16 ma flows through each signal bus instead of 8 ma.

- b. The signal buses rise about 1.2v for this period.

- c. Q284, Q294 emitters and Q253 base rise a like amount.

- d. Q253 emitter is held by the charge on C253.

- e. Since this is a common mode signal, it disappears in subsequent push-pull stages.

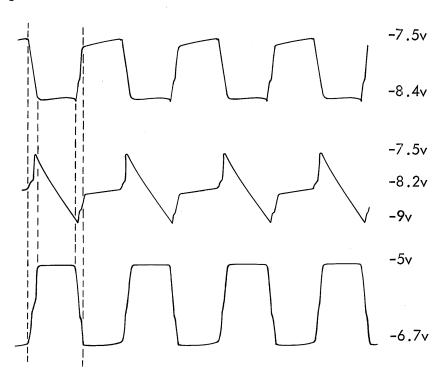

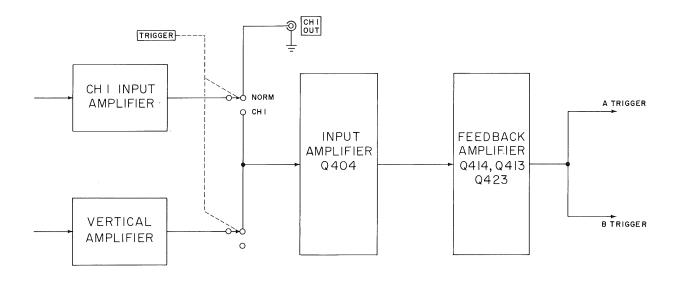

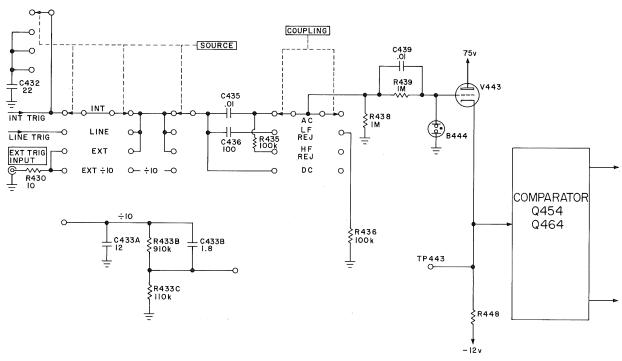

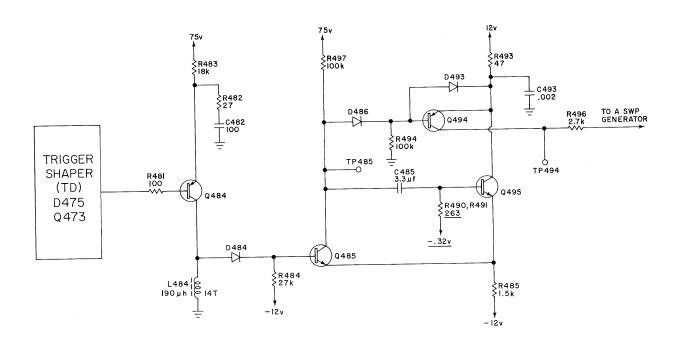

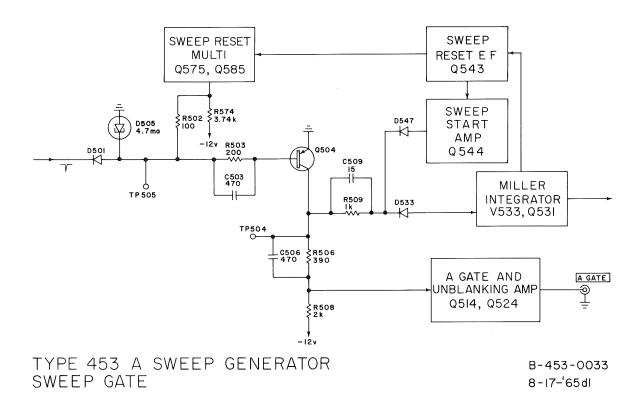

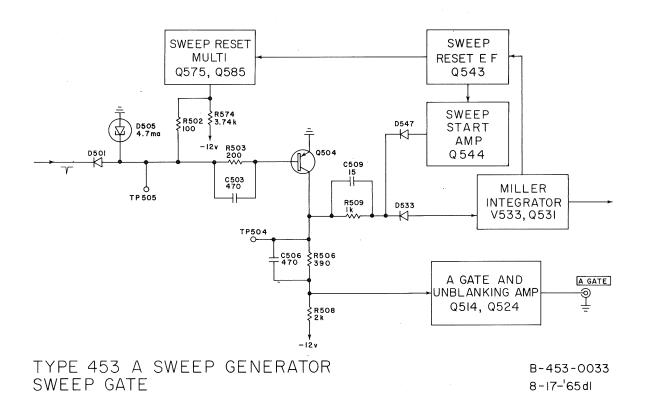

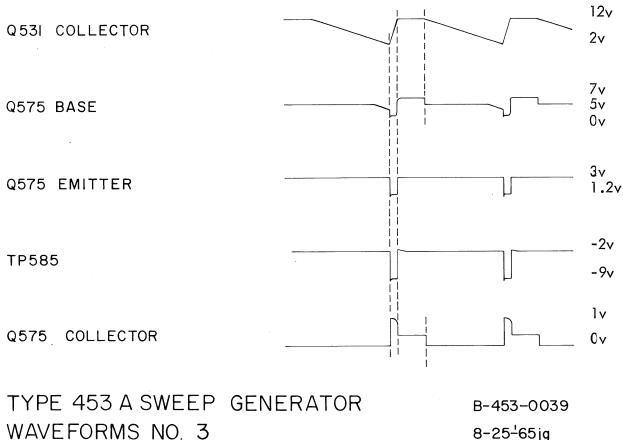

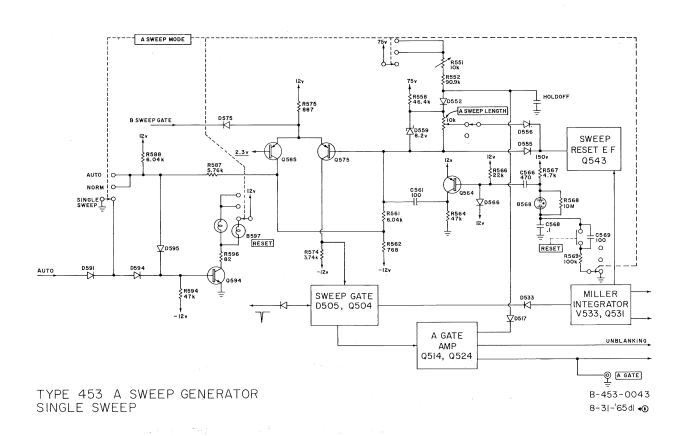

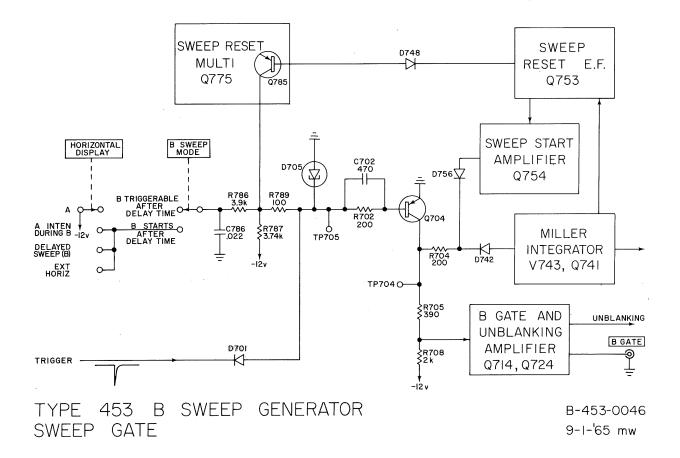

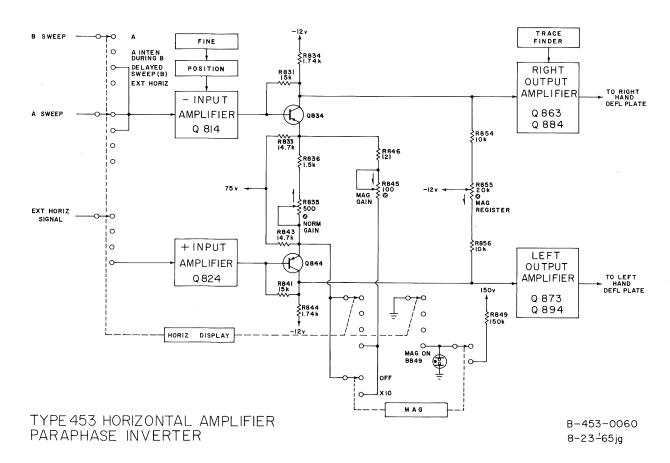

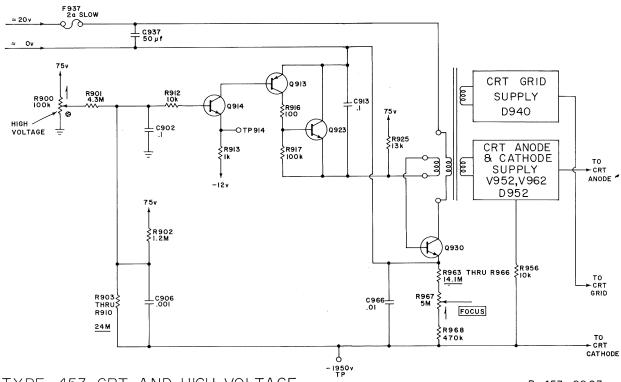

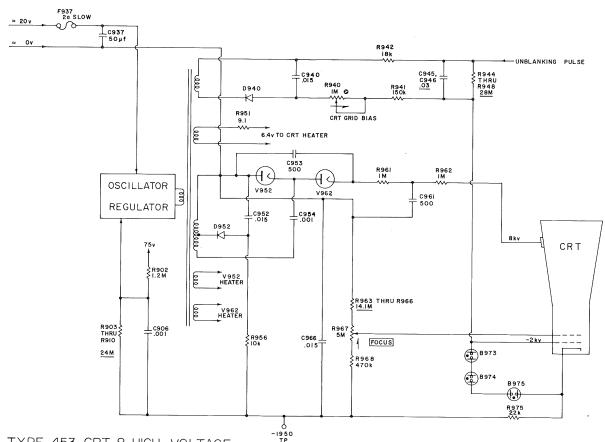

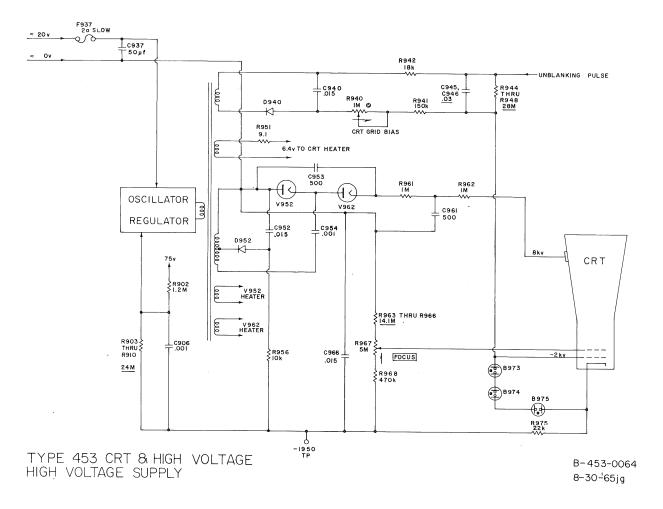

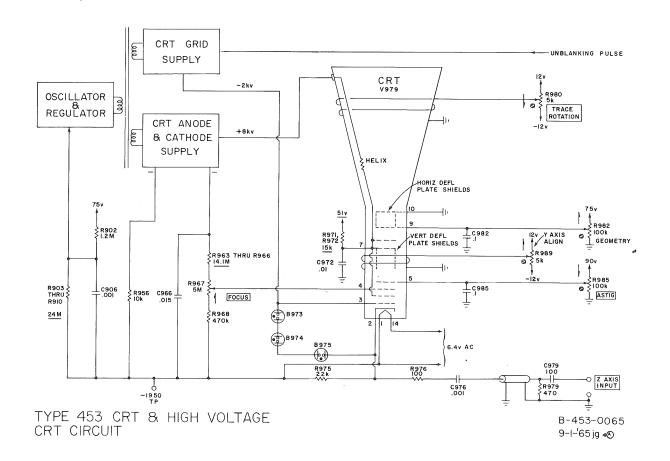

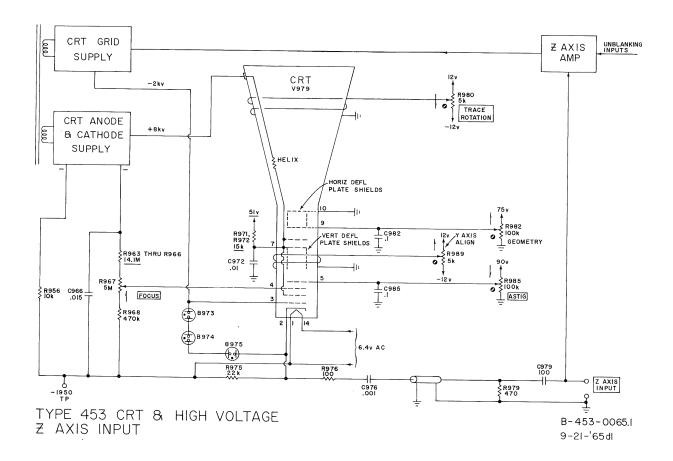

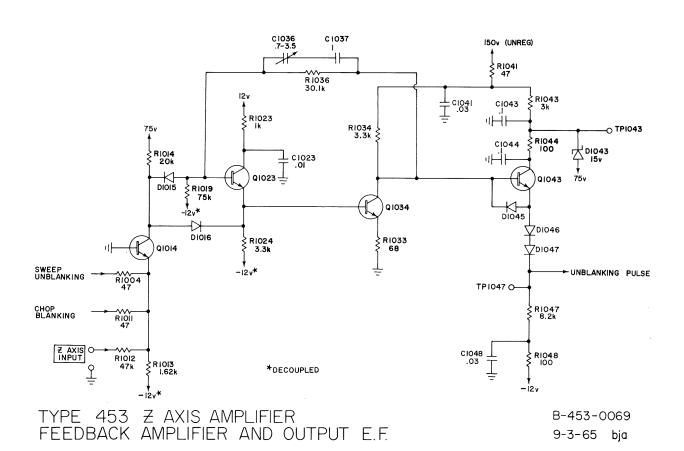

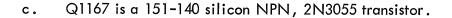

- 9. In the CHOP mode, the multi becomes a stable, running at 500 kc,  $\pm 20\%$ .