PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

> P7001/IEEE 488 **INTERFACE** 021-0206-00

INSTRUCTION MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

070-2623-00 Product Group 45 Serial Number -

First Printing JUL 1978 Revised DEC 1986

Copyright © 1978 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

#### **INSTRUMENT SERIAL NUMBERS**

Each instrument has a serial number on a panel insert, tag, or stamped on the chassis. The first number or letter designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

| B000000 | Tektronix, Inc., Beaverton, Oregon, USA            |

|---------|----------------------------------------------------|

| 100000  | Tektronix Guernsey, Ltd., Channel Islands          |

| 200000  | Tektronix United Kingdom, Ltd., London             |

| 300000  | Sony/Tektronix, Japan                              |

| 700000  | Tektronix Holland, NV, Heerenveen, The Netherlands |

# **TABLE OF CONTENTS**

| SECTION | 1 | GENERAL INFORMATION     |

|---------|---|-------------------------|

| SECTION | 2 | INSTALLATION            |

| SECTION | 3 | PROGRAMMING INFORMATION |

#### WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

| SECTION  | 4 | MAINTENANCE                     |

|----------|---|---------------------------------|

| SECTION  | 5 | DIAGRAMS                        |

| SECTION  | 6 | REPLACEABLE PARTS               |

| APPENDIX | A | DATA SHEETS                     |

| APPENDIX | В | HP 9825 PROGRAMMING INFORMATION |

| APPENDIX | С | SUPPLEMENTAL INFORMATION        |

# LIST OF ILLUSTRATIONS

| Figure | Description                              | Page |

|--------|------------------------------------------|------|

| 2-1    | Device Address Switch SW412              | 2-1  |

| 2-2    | Setting The P123 Strap Option            | 2-2  |

| 2-3    | P7001/IEEE 488 Interface Installation    | 2-3  |

| 2-4    | IEEE 488 Bus Connector Pin Assignments   | 2-4  |

| 3-1    | Data Transfer Delimiters & Terminators   | 3-5  |

| 3-2    | P7001 4K Memory Map                      | 3-8  |

| 3-3    | DPO Card Address Map                     | 3-9  |

| 3-4    | Location of Readout Words and Characters |      |

|        | (Timeslots) and Field O Addresses        | 3-12 |

| 3-5    | Status Word Formats                      | 3-14 |

| 3-6    | HSA Status Register Bit Assignments      | 3-15 |

| 4-1    | Basic Block Diagram                      | 4-2  |

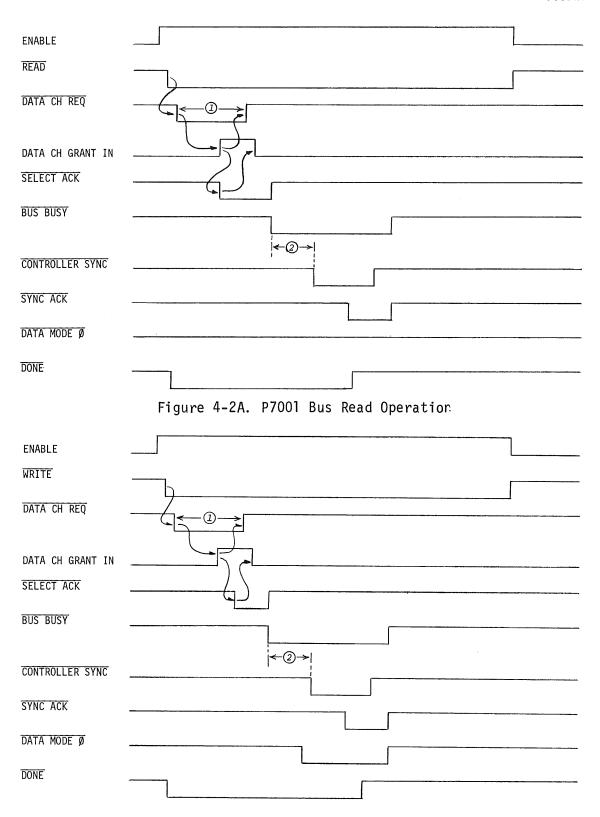

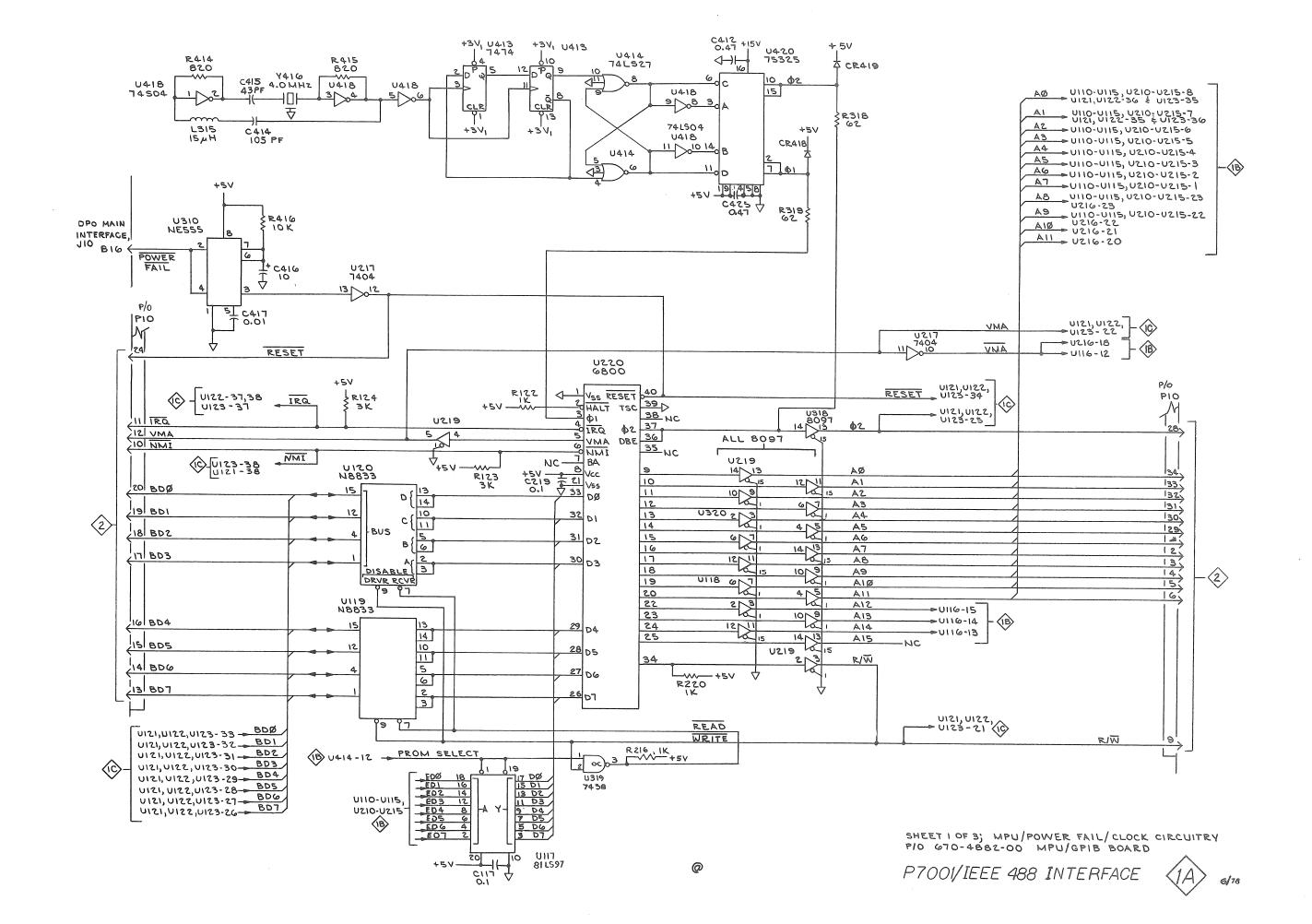

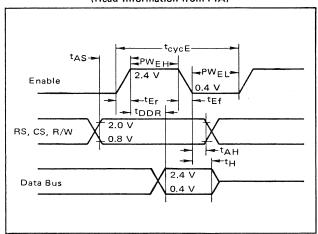

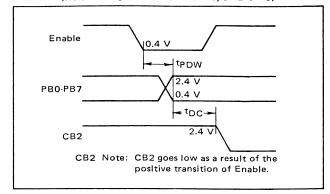

| 4-2A   | P7001 Bus Read Operation                 | 4-9  |

| 4-2B   | P7001 Bus Write Operation                | 4-9  |

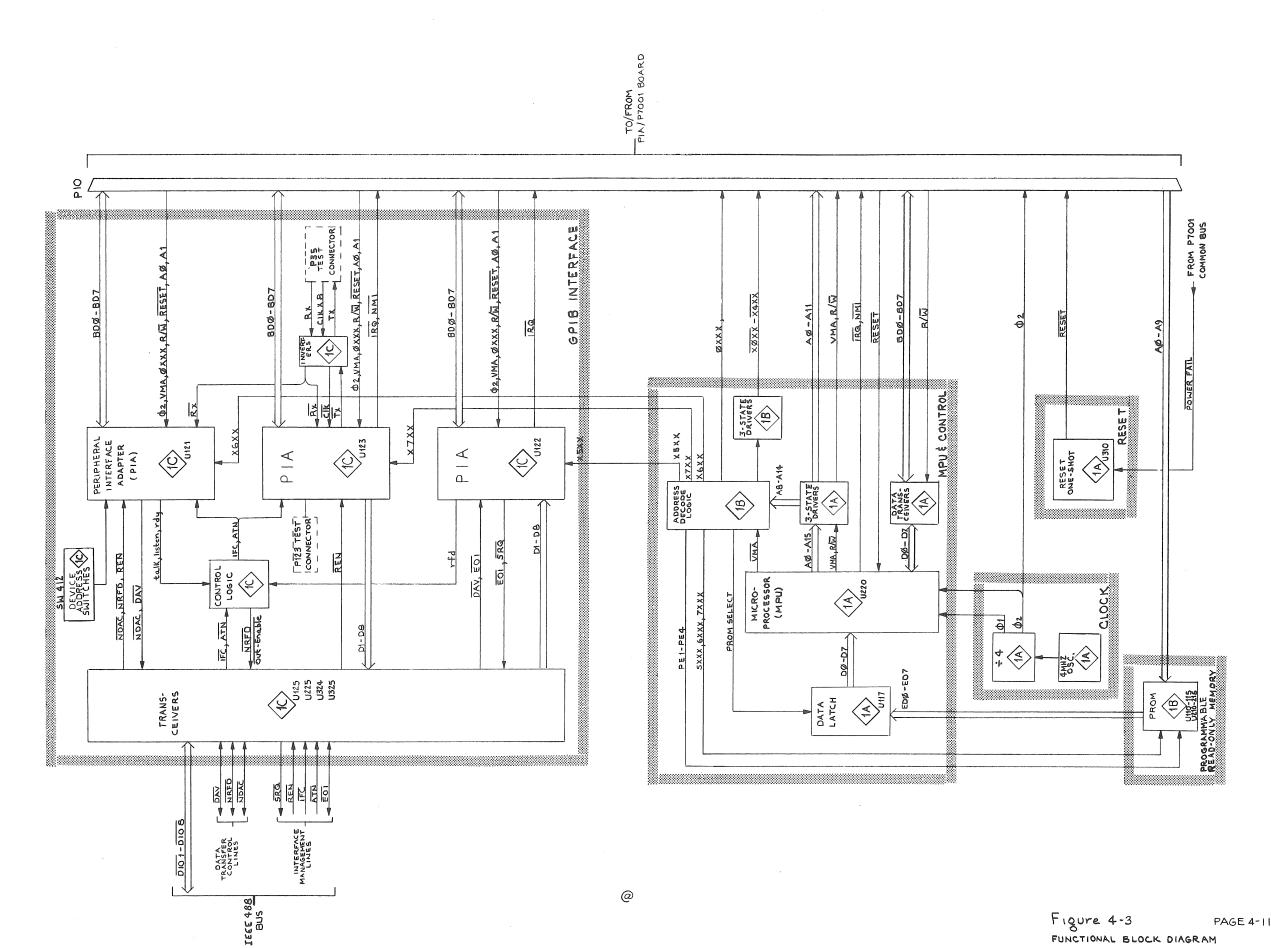

| 4-3    | Funct Block Diag., MPU/GPIB Bd &         |      |

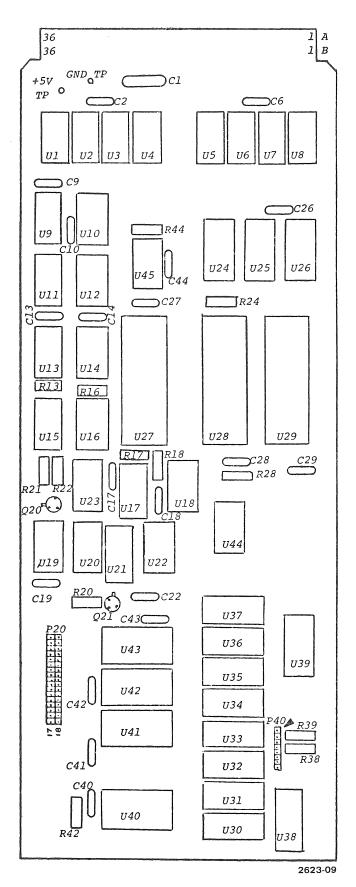

|        | Component Locator                        | 4-11 |

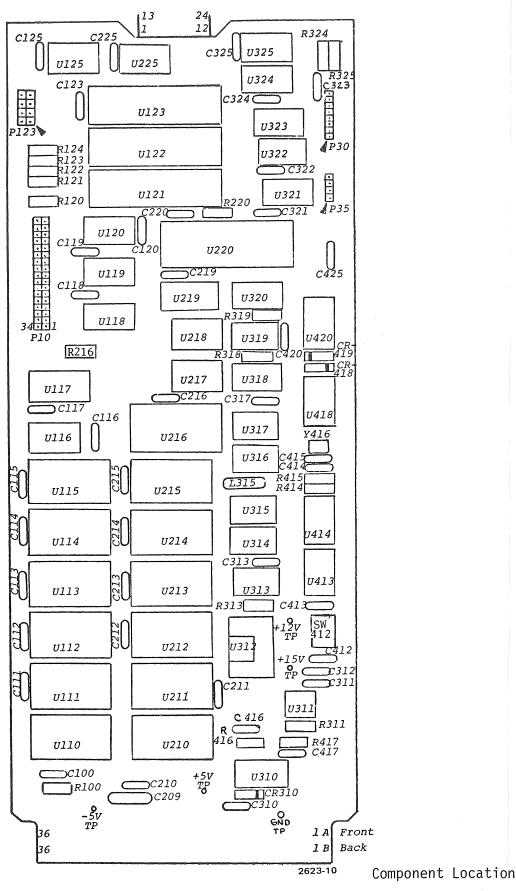

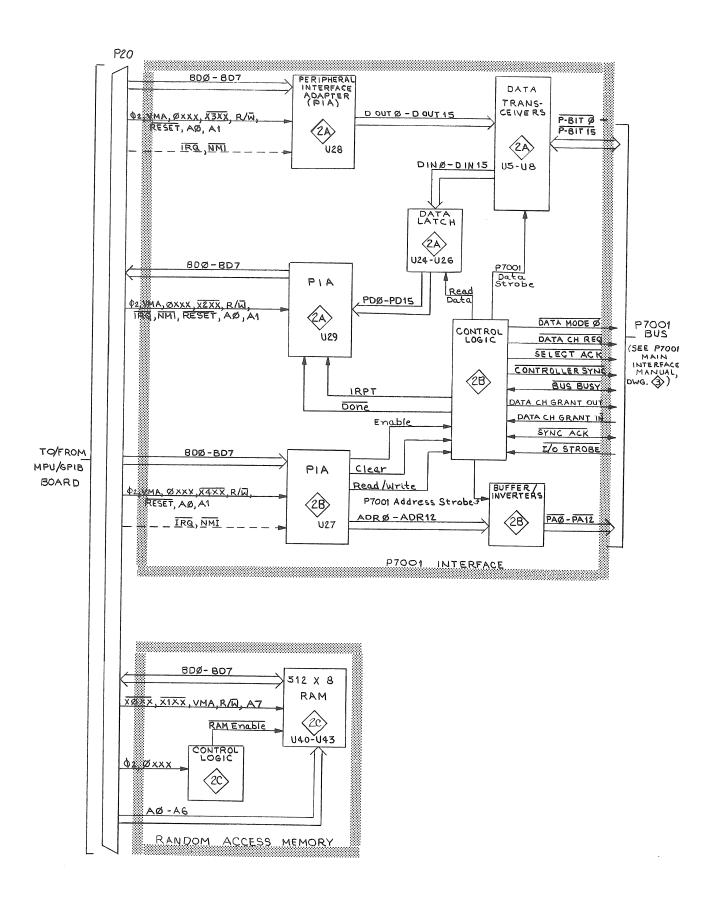

| 4-4    | Funct Block Diag., PIA/P7001 Bd &        |      |

|        | Component Locator                        | 4-12 |

|        |                                          |      |

## **LIST OF TABLES**

| Table | Description                         | Page |

|-------|-------------------------------------|------|

| 1-1   | P7001/IEEE 488 Interface Capability | 1-2  |

| 3-1   | Setting Commands                    | 3-6  |

| 3-2   | Query Commands                      | 3-7  |

# Section 1 GENERAL INFORMATION

#### INTRODUCTION

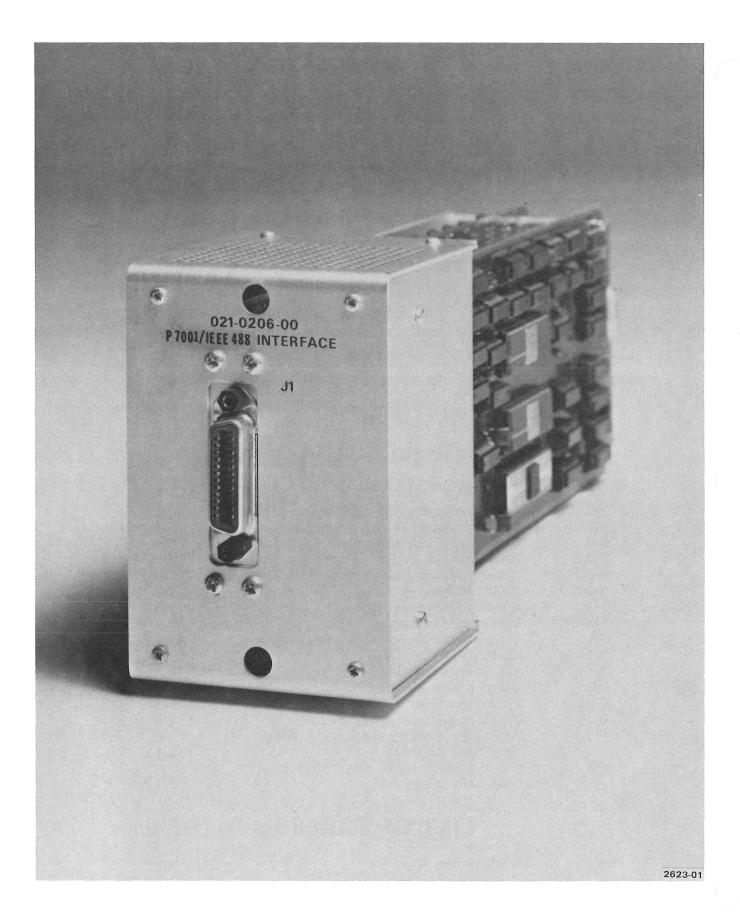

This manual contains both operational and maintenance information for the Tektronix P7001/IEEE 488 Interface, Tektronix Part No. 021-0206-00. This interface is used to interconnect the P7001 Processor section of a Tektronix Digital Processing Oscilloscope (DPO) with any of several Tektronix manufactured devices designed to operate in accordance with IEEE Standard 488-1975, "IEEE Standard Digital Interface for Programmable Instrumentation". The IEEE 488 Bus is commonly known as the General Purpose Interface Bus (GPIB), and may be referred to by that name.

A system configured from IEEE 488 compatible devices is limited to a maximum of 15 devices, and includes a system controller, such as a Tektronix 4051 Graphic System, as well as "talkers" and "listeners". The DPO in such a system functions as both a talker and a listener. As a talker, the DPO sends current status messages, data captured by the Acquisition Unit, and readout information to the system controller or other system listeners. As a listener, it receives commands and data from the system controller or other system devices.

#### IEEE 488 INTERFACE CAPABILITY

The capabilities of the P7001/IEEE 488 Interface are defined in Table 1-1 by referencing the applicable sections of the IEEE Standard 488-1975 document.

#### PHYSICAL CHARACTERISTICS

The P7001/IEEE 488 Interface is a dual card assembly designed to be installed into the interface slot of the P7001 Processor section of a DPO. All necessary operating power (+5, -5, +15 and -12VDC) is taken from the P7001 Power Supply via the P7001 Main Interface Board.

Table 1-1 P7001/IEEE 488 Interface Capability

| Interface Function         | IEEE Std. 488 Section | Interface Capability              |

|----------------------------|-----------------------|-----------------------------------|

| Source Handshake(SH)       | 2.3                   | Complete(SH1)                     |

| Acceptor Handshake(AH)     | 2.4                   | Complete(AH1)                     |

| Talker <sub>(T)</sub>      | 2.5                   | No "Talk Only" Mode <i>(T6)</i>   |

| Listener <i>(L)</i>        | 2.6                   | No "Listen Only" Mode <i>(L4)</i> |

| Service Request(SR)        | 2.7                   | Complete (SR1)                    |

| Remote-Local(RL)           | 2.8                   | None (RLØ)                        |

| Parallel Poll <i>(PP)</i>  | 2.9                   | None (PPØ)                        |

| Device Clear <i>(DC)</i>   | 2.10                  | None (DCØ)                        |

| Device Trigger <i>(DT)</i> | 2.11                  | None(DTØ)                         |

| Controller <i>(c)</i>      | 2.12                  | None (CØ)                         |

# Section 2 INSTALLATION

#### INTRODUCTION

This section of the manual contains operator/user information for the Tektronix P7001/IEEE 488 Interface, used to interconnect the P7001 Processor section of a Tektronix Digital Processing Oscilloscope (DPO) with any IEEE 488 compatible device. Included are instructions for selecting the Device Address and for setting a strap option that facilitates the use of different controllers.

#### INSTALLATION

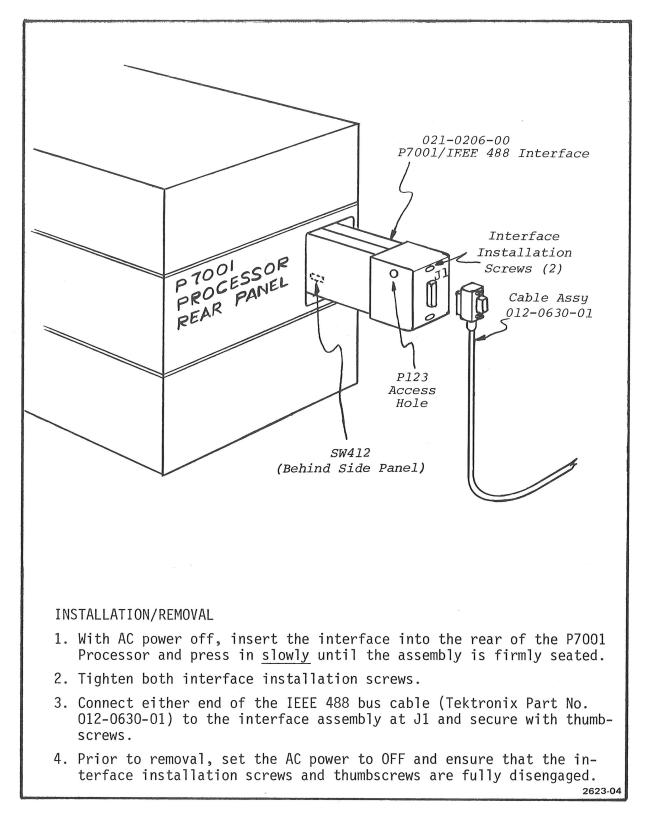

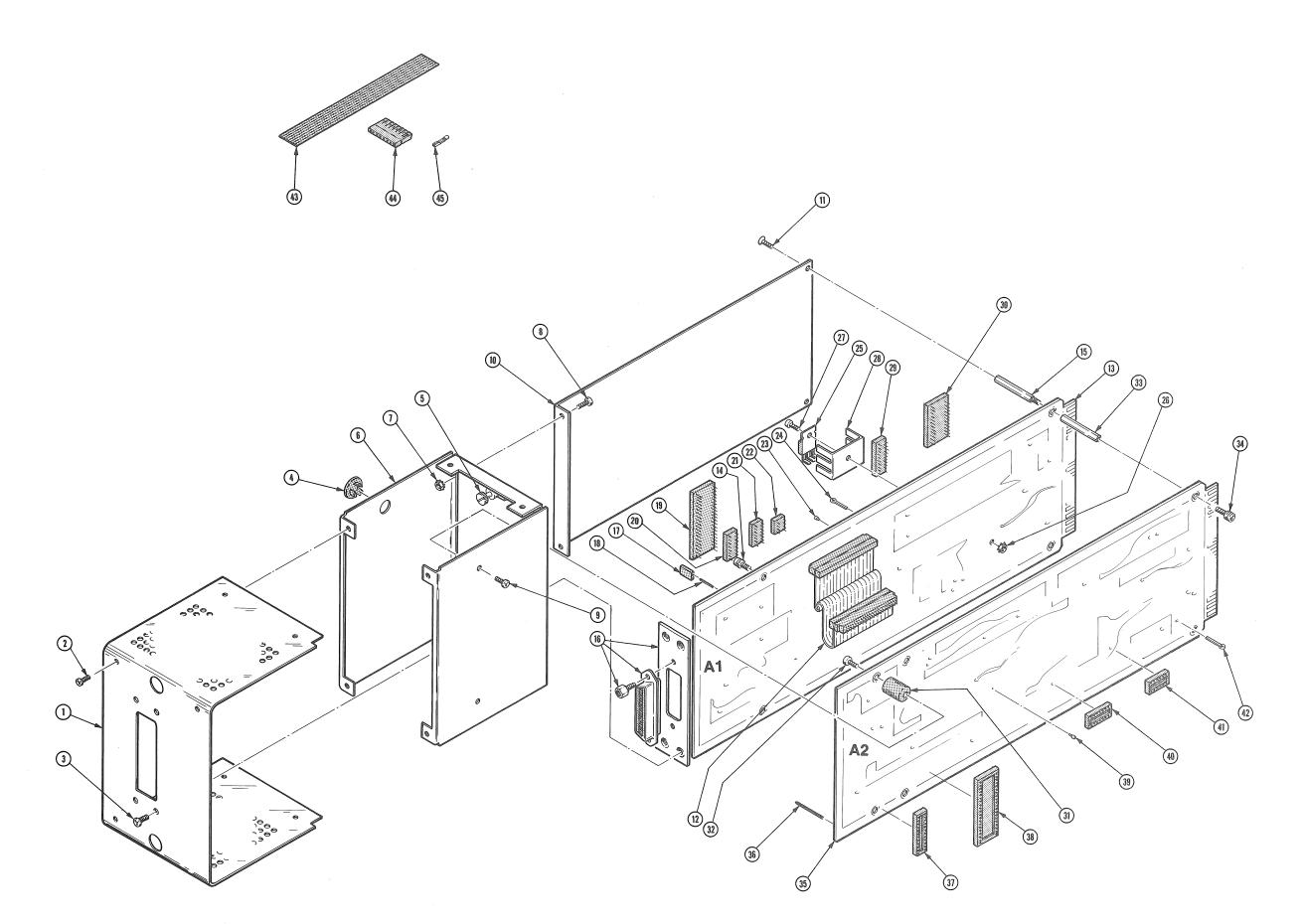

The P7001/IEEE 488 Interface assembly may be installed in a P7001 Processor using the instructional steps listed on the Installation Diagram, Figure 2-3. Before the interface is installed, however, the IEEE 488 Bus Device Address and the P123 Strap Option should be set as explained in the following paragraphs.

#### SELECTING DEVICE ADDRESS

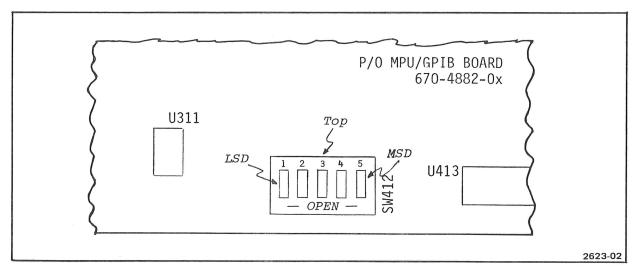

Selecting the Device Address is accomplished by setting the 5-bit DIP switch, SW412 on the MPU/GPIB board (shown in Figure 2-1), to a unique binary number. For devices with talk/listen capabilities, such as the DPO, this number must be between  $\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset$  and  $\emptyset111\emptyset$  (0 to 14 decimal), inclusive.

Figure 2-1 Device Address Switch SW412

## SELECTING DEVICE ADDRESS (Continued)

Each of the five bits is set to 1 or  $\emptyset$  by five corresponding rocker switches, numbered 1 on the left (Least Significant Digit) to 5 on the right (Most Significant Digit). Note that this is reversed from the order in which the numbers are read. When a rocker switch is pushed in at the top, that bit has been set to a binary 1; e.g., if the first two switches on the left are pushed in at the top and the other three are in at the bottom, the Device Address is set to  $\emptyset\emptyset\emptyset11$  (3 decimal).

When the DPO memory location button 'D' is pushed in, the Device Address that has been selected with SW412 will be displayed in the lower right-hand corner of the CRT. Note that when Device Address is elicited, any data previously stored at Channel 7 of memory 'D' (Field  $\emptyset$ ) will be destroyed.

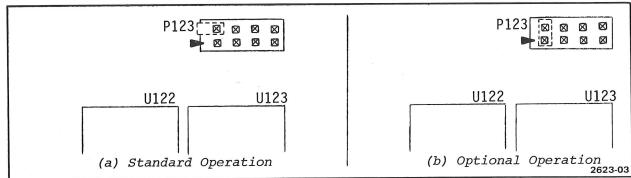

#### SETTING P123 STRAP OPTION

The P123 strap option allows the interface to operate more efficiently with different controllers. A more thorough explanation of use of the strap option may be found in Section 3 of this manual. Figure 2-2 shows connector P123 set for both "Standard" operation (jumper not installed) and "Optional" operation (pin 1 jumpered to adjacent pin - pin 1 is indicated with ▶).

Figure 2-2 Setting the P123 Strap Option

Access to the jumper is gained through a hole in the left rear of the interface housing (see Figure 2-3). To change operating modes, remove the plug from the hole and reach in with longnose pliers to re-position the jumper. To avoid loss when operating in the "Standard" mode, the jumper may be placed on pin 1 or the adjacent pin (above pin 1) with the free end extending to the left. If the DPO was energized while the jumper was re-positioned, it must now be de-energized and a "power-up" sequence performed to activate the change.

Figure 2-3 P7001/IEEE 488 Interface Installation

#### IEEE 488 BUS CONNECTOR

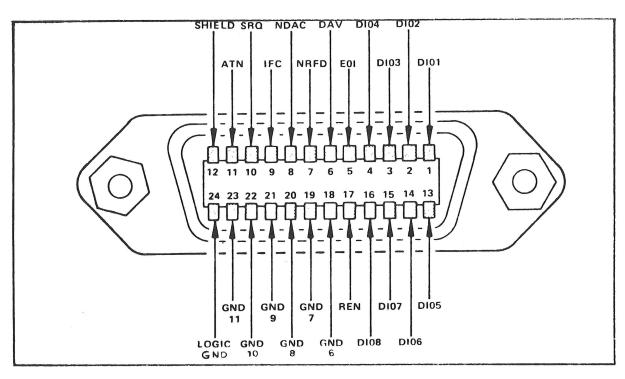

The IEEE 488 Bus Connector is located at the rear panel of the interface, as shown on Figure 2-3, and is physically attached to the MPU/GPIB Board. This 24-pin female ribbon connector has attached 16 active signal lines and 8 interlaced ground lines, and is used to interconnect the DPO with a system controller or other IEEE 488 compatible device. Figure 2-4 shows the connector pin arrangement and signal line nomenclature.

The interface also includes the mating connector and cable, Tektronix Part No. 012-0630-01 (standard 2 meter IEEE 488 cable). This connector is double-sided, with a male side to mate with the connector on the interface and a female side for connecting additional system components to the bus.

Figure 2-4 IEEE 488 Bus Connector Pin Assignments

#### Section 3

#### PROGRAMMING INFORMATION

#### INTRODUCTION

This section of the manual contains operator/user information both of a general nature and for a specific type of system utilizing the Tektronix 4051 Graphic System as system controller. Included are commands and command formats used to operate the DPO under program control from any IEEE 488 compatible controller. Examples given are in the TEK 4051 BASIC language.

For non-Tektronix controllers, such as the HP-9825 and HP-9830, familiarity with the programming language of the system controller is essential. Regardless of which controller is being utilized, familiarity with the operation of the DPO, or use of the DPO Operators Manual will be useful, as will an understanding of IEEE Standard 488-1975, "IEEE Standard Digital Interface for Programmable Instrumentation".

In addition, for non-Tektronix controllers, the paragraph entitled "Strap Option" in this section of the manual, and the corresponding instructions in Section 2 for setting the strap option, must be read and understood. Additional information on use with the HP-9825 is contained in Appendix II at the rear of this manual.

#### GENERAL INFORMATION

The P7001/IEEE 488 Interface can be used to interconnect any IEEE 488 compatible device with the P7001 bus of a Tektronix Digital Processing Oscilloscope (DPO). There are three different types of devices on the IEEE 488 bus; "controllers", "talkers", and "listeners". IEEE Standard 488-1975 allows specific listeners and talkers to be selected and de-selected independently. The responsibility of the controller is to designate which system connected instruments are to listen or to talk. The DPO in such a system functions as both a talker and a listener. As a talker, it sends data captured by the DPO (i.e., waveforms), current status messages, and graticule readout information to the bus. As a listener, the DPO receives data (waveforms), commands, and internal memory addresses from the bus.

#### OPERATING INSTRUCTIONS

Most of the operating instructions included here are specifically for use with a TEK 4051 Graphic System as system controller. Operating instructions for other IEEE 488 controllers may be inferred from a comparison of the instructions included here and those for the controller utilized. An appendix to this manual gives operating examples for the HP-9825 controller.

## Power On/Initialization

When a DPO goes through the power-on transition, it automatically generates (through the interface) an interrupt request (SRQ) signal on the IEEE 488 bus. This condition may be cleared and the nature and source of the interrupt determined by programming the controller to take a serial status poll, as shown in a subsequent paragraph entitled "Servicing Interrupts with the TEK 4051".

## Power On/Initialization (Continued)

If no interrupt handling instructions are included in the program, or for some other reason the controller does not service the interrupt, the interface must be cleared. This can be accomplished by using the "DCLb" command explained later in this section.

## Status Word

The DPO Status Word is used to indicate to the controller the reason for a DPO interrupt request (SRQ), or may be solicited with a POLL statement. When no SRQ has been generated, the interface will respond with one of the following decimal status words:

Status Word = Ø Meaning: Interface idle (Both cases return decimal : Interface busy 16 with HP controllers)

When the DPO issues an interrupt, its interface asserts the SRQ signal line on the IEEE 488 bus. The system controller should be programmed to conduct a status poll in order to release the SRQ. The interface will respond with one of the following decimal status words (the DPO will issue an interrupt request for each of these conditions):

| Status | Word = | 81  | Meaning: | DPO powered up.                        |

|--------|--------|-----|----------|----------------------------------------|

|        | =      | 82  | :        | DPO was hung but has self-corrected.   |

|        | =      | 83  | :        | DPO PROGRAM CALL button pushed.        |

|        | =      | 84  | :        | DPO Single Sweep completed.            |

|        | =      | 85  | :        | HSA aborted (if HSA is installed).     |

|        | >      | 100 | :        | Error has occurred (see following para |

|        |        |     |          | graph entitled "Error Messages").      |

## Error Messages

Four different error conditions may exist for the DPO; each will be indicated to the system controller by an SRQ. A status poll conducted after receipt of the SRQ will result in one of the following decimal status words:

| output of one one of |          |                                                                                                                                                                                                                                                                                           |

|----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Word = 113    | Meaning: | Communication Error - the data input is meaningless or impossible to implement. If the data will affect the DPO operation, the error is <u>not</u> a communication error. Examples include parity errors, unintelligible commands, or syntax errors.                                      |

| = 114                | :        | Programming Error - intelligible commands have been received which involve out of range parameters. The DPO attempts to carry out the assigned operation but finds it impossible to complete. Examples include overflowing DPO data size, and invalid addressing of the DPO internal mem- |

| = 115                | :        | ory. Internal Error - an Interface or P7001 hardware error has occurred. This may mean a permanent hardware malfunction or a transient condition.                                                                                                                                         |

| = 112                | :        | Other Error - the DPO has discovered an error which is none of the previously described cases.                                                                                                                                                                                            |

3-2

@

## Servicing Interrupts with the TEK 4051

When the DPO issues an interrupt service request (SRQ) through the interface, the 4051 is normally programmed to finish executing the current statement, then transfer to an interrupt handling routine, as shown in the following example:

```

100

ON SRQ THEN 500

500

POLL N,M;4;5;1

PRINT N<sub>3</sub>M

51Ø

520

GOTO N OF 600,700,800

---

___

800

IF M=83 THEN 4000

810

IF M=84 THEN 5ØØØ

82Ø

RETURN

---

___

4000

(service routine for DPO Front Panel PROGRAM CALL buttons)

____

4290

RETURN

(service routine for DPO Single Sweep)

5ØØØ

____

519Ø

RETURN

```

In the foregoing example, line 100 enables the 4051 to respond to an SRQ condition; the program then executes in normal sequential order. When the DPO (or any other peripheral device) signals an SRQ, the 4051 finishes the present statement, then transfers to the POLL statement at line 500. The POLL statement contains the two numeric variables N and M as parameters followed by device addresses 4;5;1. As the 4051 executes the POLL statement, it first addresses device number 4 to see if it is requesting service. Assuming the DPO has been assigned device address 1, the 4051 will continue to poll devices in the order shown until it reaches device 1. When the 4051 finds that device 1 issued the SRQ, it assigns the number  $\frac{3}{2}$  to variable N in the POLL statement, because device 1 is the third device on the list.

The DPO returns a decimal status word (previously explained) which is assigned to the variable M. Line 510 causes N and M to be printed on the 4051 screen. Line 520 sends the program to N, or the third (800) line number in the list 600,700,800. In line 800, if the status word (M) is 83 the program moves to line 4000, which begins a service routine for the DPO PROGRAM CALL buttons. Line 810 performs the same function for status word 84.

If the 4051 does not have the DPO's device address in its program (listed in the POLL statement) when an SRQ is received, processing will halt and the 4051 will "hang" pending further instructions. At this point, the operator should find the line containing the POLL statement and re-enter the statement so that the list of devices to be polled includes the DPO. Subsequent status polls will then recognize the address.

#### NOTE

This condition will not occur when using the HP-9825 as system controller, because it will time out and resume processing if unable to identify a device.

## Servicing Interrupts with the TEK 4051 (Continued)

If the TEK 4051 is being used as system controller but is idle, or does not have interrupt handling instructions in its program, the following error message will be printed on the screen when an SRQ is received:

NO SRO ON UNIT - MESSAGE NUMBER 43

To clear this condition, the operator should enter the following statement in the immediate mode (no line number):

POLL N.M; (DPO Device Address)

## Strap Option

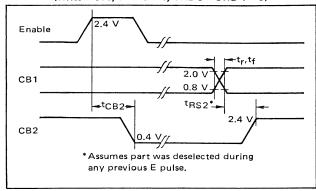

The IEEE 488-1975 standard is a hardware standard. As such, its main purpose is to confirm the electrical characteristics of the interface bus and the handshake procedures, addressable messages, unaddressable messages, and universal messages. It does not specify the delimiters and terminators that pass through the bus together with the data and command information. A strap option is provided to allow the user to set the interface to send or accept different kinds of delimiters and terminators.

Implementation of the strap option is described and illustrated in Section 2 of this manual. The option provides two operating modes, "Standard" operation and "Optional" operation. Standard operation is defined as between the DPO and a Tektronix controller, such as the TEK 4051. Optional operation should be used with Hewlett-Packard controllers, such as the HP-9825, to speed up transfer time, use less core, and ease programming.

Delimiters and terminators used for Standard data transfers are as follows:

Accepts into DPO: delimiters "," or "b" or "CR" or "LF" or any combination.

: terminators - any character with EOI asserted.

Sends to controller: delimiter "."

: terminator - the sequence of "CR", then "LF" with EOI asserted.

Delimiters and terminators used for Optional data transfers are as follows:

Accepts into DPO: delimiters - same as for Standard operation.

: terminators - "LF" without EOI asserted, or any character with EOI asserted.

Sends to controller: delimiter and terminator - same as standard operation.

The characters used above and their ASCII decimal equivalents are as follows (the complete ASCII code chart is included as a supplement to this manual):

"," = comma (ASCII 44)

"CR" = CARRIAGE RETURN (ASCII 13)

"LF" = LINE FEED (ASCII 10)

""" = space (ASCII 32)

EOI = End Or Identify (IEEE 488 bus management signal).

## Strap Option (Continued)

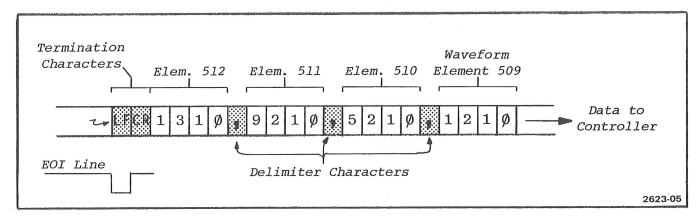

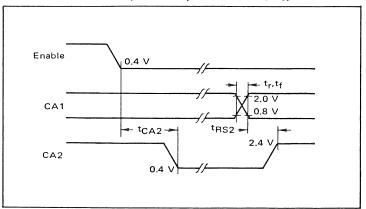

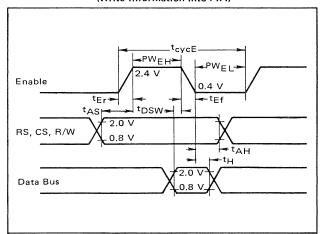

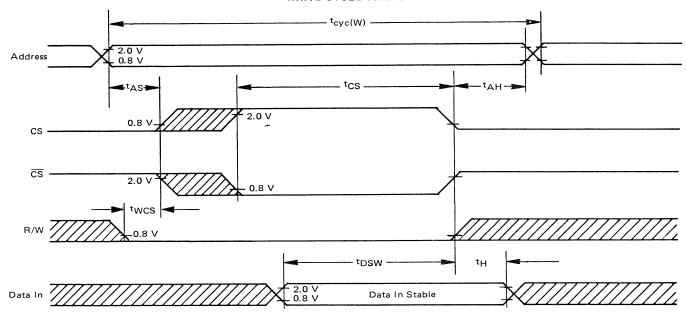

Use of the delimiters and terminators is illustrated in Figure 3-1, which shows the last four elements of a data (waveform) transfer from the DPO to the controller. The strap option is set for "Standard".

Figure 3-1 Data Transfer Delimiters and Terminators

#### COMMAND FORMAT

The general command format (the sequence in which commands occur) is as follows: (MTA or MLA)(DAB).

Where: MTA (My Talk Address) and MLA (My Listen Address) are the primary addresses used to command the DPO to transmit data (talk) or receive data (listen), respectively. MTA and MLA are identical to the I/O Address referred to in the TEK 4051 manual, and may collectively be referred to as Hardware Unit Number (HUN) or Device Address. Instructions for setting this address are in Section 2 of this manual.

DAB (Command Data Bytes) consist of three data bytes of ASCII characters followed by either a question mark or a blank space (both also ASCII).

#### NOTE

The Secondary Address (MSA) described in the IEEE 488-1975 standard is not applicable to this interface.

Depending on the intended operation, commands from the system controller may be received in one of three specific formats, as follows:

Write to DPO - This command format consists of the DPO's Device Address (MLA in this case), then a three character mnemonic from the Setting Commands of Table 3-1 followed by a space, then the data to be sent to the DPO [i.e., (MLA)(DAB))data].

## COMMAND FORMAT (Continued)

Set DPO to be - This command format consists of the DPO Listen Address, read

then a three character mnemonic from the Query Commands of Table 3-2 followed by a question mark [i.e., (MLA)(DAB?)]. This command asks the DPO a question that it (the DPO) will not be able to answer until the "Read from DPO" operation is executed.

Read from DPO - This command format consists only of the assignment of the DPO as talker, after which the requested information is sent from the DPO. The terminating characters ("CR", then "LF" with EOI asserted) are generated automatically by the interface. Before a "Read from DPO" operation can be performed, the "Set DPO to be read" operation must be executed.

Table 3-1 Setting Commands

| ADR | Address                                | Page: 3-9 |

|-----|----------------------------------------|-----------|

| CHL | Channe l                               | 3-11      |

| CLI | Clear (Front Panel) Interrupt          | 3-19      |

| DAT | Data                                   | 3-10      |

| DCL | Device Clear                           | 3-20      |

| DPA | Waveform A of DPO Memory is selected   | 3-8       |

| DPB | Waveform B of DPO Memory is selected   | 3-8       |

| DPC | Waveform C of DPO Memory is selected   | 3-8       |

| DPD | Waveform D of DPO Memory is selected   | 3-8       |

| HAV | Hardware Average (if HSA is installed) | 3-18      |

| HIS | Histogram (if HSA is installed)        | 3-18      |

| HOL | Hold                                   | 3-17      |

| OCT | Octa1                                  | 3-16      |

| SCL | Scale Factor                           | 3-13      |

| SSR | Single Sweep Reset                     | 3-17      |

| ST0 | Store                                  | 3-17      |

| TAB | Transfer Waveform A to Waveform B      | 3-20      |

| TAC | Transfer Waveform A to Waveform C      | 3-20      |

| TAD | Transfer Waveform A to Waveform D      | 3-20      |

| TBA | Transfer Waveform B to Waveform A      | 3-20      |

| TBC | Transfer Waveform B to Waveform C      | 3-20      |

| TBD | Transfer Waveform B to Waveform D      | 3-20      |

| TCA | Transfer Waveform C to Waveform A      | 3-20      |

| ТСВ | Transfer Waveform C to Waveform B      | 3-20      |

| TCD | Transfer Waveform C to Waveform D      | 3-20      |

| TDA | Transfer Waveform D to Waveform A      | 3-20      |

| TDB | Transfer Waveform D to Waveform B      | 3-20      |

| TDC | Transfer Waveform D to Waveform C      | 3-20      |

| WRD | Word                                   | 3-10      |

| X-Y | Set DPO to X-Y Display Mode            | 3-18      |

| Y-T | Set DPO to Y-T Display Mode            | 3-18      |

|     | • -                                    |           |

3-6

#### COMMAND DESCRIPTIONS

Commands from the IEEE 488 controller are structured in one of two ways. Setting Commands are used to transfer data to or set the status of the DPO, and are structured as a three-character mnemonic followed by a blank space, enclosed by quotation marks, such as "ADR $\beta$ " (the character  $\beta$  is used to designate a blank space). The Setting Commands are shown in Table 3-1.

The Query Commands, used to transfer data or status information from the DPO to the controller, consist of a three-character mnemonic followed by a question mark, enclosed by quotation marks. Using the Address command again as an example, this would look like "ADR?". The Query Commands are shown in Table 3-2.

Table 3-2 Query Commands

| ADR? DAT? DPA? DPB? DPC? DPD? FPI? OCT? SCL? | Address Data Send Waveform A of DPO memory Send Waveform B of DPO memory Send Waveform C of DPO memory Send Waveform D of DPO memory Front Panel Interrupt Octal Scale Factor | Page: 3-9 3-10 3-9 3-9 3-9 3-9 3-19 3-16 3-11 |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| SCL?<br>WRD?                                 | Scale Factor<br>Word                                                                                                                                                          |                                               |

#### DATA TRANSFER

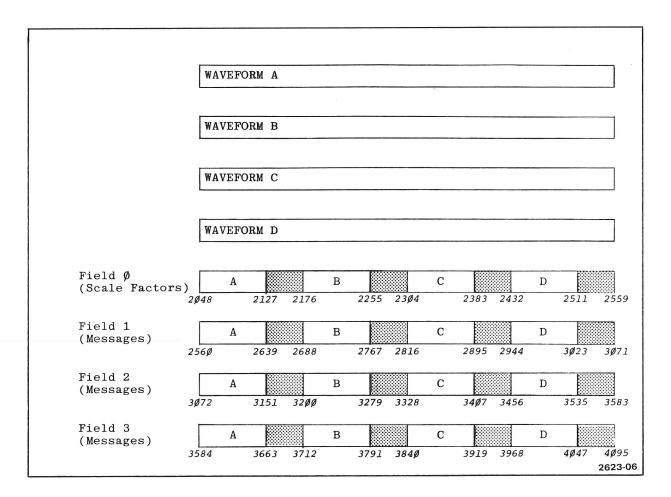

The DPO memory contains four waveform locations, designated A, B, C and D, Each waveform is a 512-element array. The data for each element is an integer in the range  $\emptyset$  to  $1\emptyset23$  (decimal). Figure 3-2 shows a memory map for a P7001 4K memory. At the top are four blocks labeled A, B, C and D. These blocks represent the four waveform locations in memory as selected from the DPO front panel. Each waveform location has an address range of 512 (decimal). Waveform A, for example, is  $\emptyset\emptyset\emptyset$  to 511, Waveform B is 512 to  $1\emptyset23$ , etc.

Data may be transferred to and from the DPO in three different ways, as follows:

- 1. Use of the DPA, DPB, DPC and DPD commands;

- 2. Use of the ADR and DAT commands;

- 3. Use of the ADR and WRD commands.

Figure 3-2 P7001 4K Memory Map

#### DPA, DPB, DPC and DPD Commands

The DPA, DPB, DPC and DPD commands are used to transfer 512 data words, or waveform elements, to or from DPO memory locations A, B, C and D, respectively. Data transfers from the DPO to the controller are normally performed after "Store" and "Hold" operations in the DPO. Store and Hold operations may be performed using the "STO $\beta$ " and "HOL $\beta$ " commands explained later, or may be executed manually from the DPO Front Panel (see DPO Operators Manual, Tektronix P/N 070-1599-00).

A single blank space after the command mnemonic, such as "DPAb" or "DPCb" indicates a data transfer from the TEK 4051 to the DPO. The command is delimited with a semicolon. The following TEK 4051 example shows how a 512-element array, Z, would be transferred from the controller to Waveform location A of a DPO with a Device Address of 1:

#### PRINT @1:"DPA ";Z;

Note the use of the delimiter (;) after the Z character. This speeds up data transfer time in the 4051. If it is not used, the 4051 will send up to six spaces between each data word, depending on the number of digits of the data.

## DPA, DPB, DPC AND DPD Commands (Continued)

When the command mnemonics DPA, DPB, DPC and DPD are followed by a question mark, such as "DPA?" or "DPC?", the interface is set up to allow data to be transferred from the DPO to the controller or other IEEE 488 bus listener. In the following TEK 4051 example, line 90 dimensions B to a 512 element array, line 100 outputs the ASCII characters "DPB?" to the bus and sets up the DPO to output the requested data, and line 110 inputs the 512 data words of the Device Address 1 (the DPO), Waveform B, into the 4051.

9Ø DIM B(512) 1ØØ PRINT @1:"DPB?" 11Ø INPUT @1:B

#### ADR Commands

The "ADR $\beta$ " (Address) command is used to set up the DPO Address Register residing in the interface. It allows the controller to select each memory cell independently. The addressable DPO memory is from decimal  $\emptyset$  to 8191. (See Figure 3-2, "P7001 4K Memory Map", and Figure 3-3, "DPO Card Address Map"). The following TEK 4051 example shows Device Address 1, the DPO, address 256 $\emptyset$  (the start of Field 1) being selected:

PRINT @1:"ADR ";256Ø

Note that the argument following the command mnemonic (256 $\emptyset$  in the above example) may also be a numeric variable that is defined elsewhere in the program.

The "ADR?" command is used to set the DPO ready to output the current status of its address register when assigned to talk. In the following TEK 4051 example, line 100 readies the DPO to talk, and line 110 assigns the DPO to talk and the controller to listen.

1ØØ PRINT @1:ADR?" 11Ø INPUT @1:P

|              | HSA 1st         | WAVEFORM *       |               |

|--------------|-----------------|------------------|---------------|

| 4096         |                 |                  |               |

| 4608         | HSA 2nd         | WAVEFORM *       |               |

| 5120         |                 |                  |               |

| 5632         |                 |                  |               |

| 6,144        |                 |                  |               |

|              |                 | HSA CONT REG*    | FRONT PANEL   |

| 6 <u>656</u> | 6               | 5912 7           | 040           |

| DISPLAY GEN  | READOUT INTFC   | A/D CONVERTER    | I/O INTERFACE |

| 7168 7       | 296 7           | 424 7            | 552           |

| DIS          | SPLAY GENERATOR | , X-Y MODE, X DA | ATA           |

| 7680         | * If HSA is i   | nstalled         | 2623          |

#### DAT Commands

The DAT (Data) commands allow 512 elements of data to be transferred to or from the DPO, with the beginning address pointed to by the DPO Address Register (set up with the "ADR" command). After execution of these commands, the DPO Address Register is advanced by decimal 512.

In the following TEK 4051 example, line 500 dimensions the array Y to 512 elements, line 510 defines Y, line 600 sets the Address Register of the DPO to 256, and line 610 actually transfers array Y from the 4051 to the DPO (into the second half of Waveform location A and the first half of Waveform location B). After line 610, the DPO Address Register will be at 768.

```

500 DIM Y(512)

510 LET Y=100

600 PRINT @1:"ADR ";256

610 PRINT @1:"DAT ";Y;

```

Note the delimiter (;) after Y in line 610. This is explained after the "DPAD" command example in a previous paragraph.

In the following TEK 4051 example, line 100 dimensions array X to 512 elements, line 110 sets the Address Register of the DPO to 256, or the address of the beginning of the second half of Waveform A (see Figure 3-2), line 120 readies the DPO to talk, and line 130 transfers the 512 data words from the DPO to the controller. After completion of this sequence, array X is holding the second half of Waveform A and the first half of Waveform B.

```

100 DIM X(512)

110 PRINT @1:"ADR ";256

120 PRINT @1:"DAT?"

130 INPUT @1:X

```

#### WRD Commands

The WRD (word) commands allow the 10 bits of a DPO data word to be transferred to or from the DPO (in decimal form). The "ADR\omega" command is used to set up the DPO Address Register. After execution of either of the WRD commands, the Address Register is automatically incremented by 1. These commands can be used to transfer an array of n elements to or from the DPO, where n is defined by the controller.

In the following TEK 4051 example, the array Y is first dimensioned to 1024 elements in line 500, Y is defined in line 510, then line 520 sets the Address Register of the DPO to 512, or the beginning of Waveform B. Lines 530 and 550 perform the FOR LOOP function of the 4051, and line 540 transfers the 1024-element array, one word at a time, to DPO memory (Waveforms B and C).

```

500 DIM Y(1024)

510 LET Y=500

520 PRINT 01: "ADR ";512

530 FOR N=1 to 1024

540 PRINT 01: "WRD ";Y(N)

550 NEXT N

```

## WRD Commands (Continued)

In the following TEK 4051 example, an array (L) is dimensioned to 128 elements in line 100 (note - a standard DPO waveform array is 512 elements, therefore this is only the first quarter of a whole waveform). In line 110, the beginning of DPO Waveform B is selected as the starting address. Line 130 sets up the DPO to output the data, line 140 reads the first data word of Waveform B into the controller array L, and line 150 (together with line 120) performs the FOR LOOP function.

100 DIM L(128)

11Ø PRINT @1:"ADR ";512

12Ø FOR I=1 to 128

13Ø PRINT @1:"WRD?"

14Ø INPUT @1:L(I)

15Ø NEXT I

## Scale Factor and Message Transfers

Below the waveform blocks in Figure 3-2 are four additional blocks designated Field  $\emptyset$ , Field 1, Field 2 and Field 3. These represent the four fields of data or messages that can be stored in DPO memory and displayed on the DPO's CRT or read into the controller. The default mode of display is Field  $\emptyset$ . Field  $\emptyset$  is the only field that can display scale factors for the plug-ins directly, and is the field in which the scale factor information is stored when a waveform is stored through the use of the Front Panel buttons. Fields 1, 2 and 3 are used mainly for displaying messages.

Each field has four designated areas for Waveforms A, B, C and D, as shown on Figure 3-2. Also shown are the addresses for each of the waveforms in the four fields (e.g., waveform C of field 2 uses addresses 3328-3407).

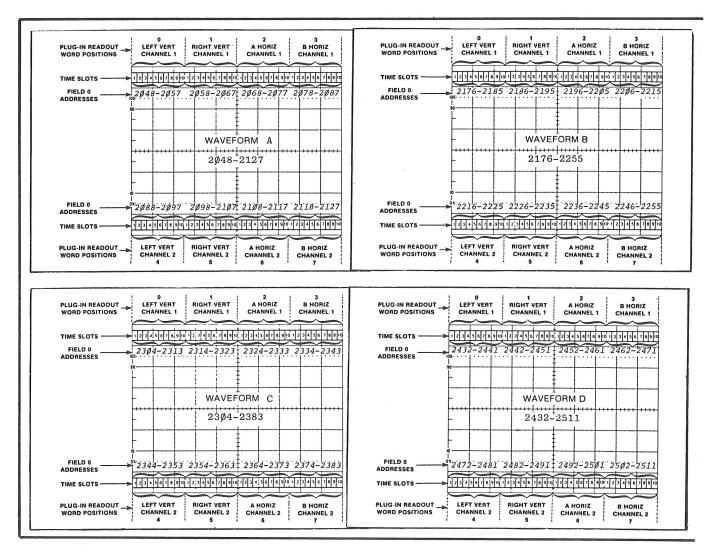

Each waveform in a Field has 80 displayable positions. These 80 positions are grouped in 8 channels, each with 10 displayable characters. This is illustrated in Figure 3-4, "Location of Readout Words & Characters (Timeslots) and Field  $\emptyset$  Addresses". Figure 3-4 shows the 8 channels (plug-in readout word positions) and corresponding addresses for Field  $\emptyset$ . The channels are shown as they appear on the CRT, numbered from left to right across the top (CH.  $\emptyset$ -3) then left to right across the bottom (CH. 4-7). Also shown are the ten characters (timeslots) for each channel.

## Reading Scale Factors

Scale factors from Field Ø may be read into the controller using the "CHL $\emptyset$ " command, which selects the waveform and channel of a scale factor transfer, followed by the "SCL?" command. In the following TEK 4051 example, line 100 selects Waveform B, Channel 3 of the DPO. Line 110 sets up the DPO to output the selected scale factors when assigned to talk, and line 120 assigns the DPO to be a talker, thus reading the selected scale factor information (Y\$) into the controller.

100 PRINT 01:"CHL ";"B3"

11Ø PRINT @1:"SCL?"

12Ø INPUT @1:Y\$

Figure 3-4 Location of Readout Words and Characters (Timeslots) and Field  $\emptyset$  Addresses

## Reading Scale Factors (Continued)

Reading scale factors or messages that <u>overlap</u> channels requires a more complex program, such as the following TEK 4051 example:

- 100 LET B\$=""

- 11Ø PRINT @1:"ADR ";2432

- 12 $\emptyset$  FOR I=1 to  $4\emptyset$

- 13Ø PRINT @1:"WRD?"

- 14Ø INPUT @1:A

- 15 $\emptyset$  LET A\$=CHR(A)

- 16Ø LET B\$=B\$ & A\$

- 17Ø NEXT I

- 18Ø PRINT B\$

## Reading Scale Factors (Continued)

In the foregoing example, line 100 initializes B\$, line 110 selects Field 0, Waveform D of the DPO, line 120 sets up the FOR LOOP function to read in 40 characters, lines 130 and 140 read in one data word, then the DPO is auto-incremented by 1. Line 150 stores the ASCII character having the decimal number A in string variable A\$. Line 160 concatenates these characters in B\$. Line 180 prints out the actual readout ASCII character string.

## Displaying Messages

Messages can be displayed on the screen (CRT) of the DPO using the "SCL\b" command. The scale factors may be accidentally overwritten by not selecting a field of display (since Field \Beta is the default condition). Messages may be written into Fields 1, 2 or 3 for display by using a special command, "OCT\b" (explained later), to set up the Readout Interface Register in the DPO. In the following TEK 4051 example, line 1\Delta selects Field 2, Waveform D of the DPO, line 11\Delta writes the message to the designated area (up to 80 characters may be displayed at a time), and line 12\Delta selects the Readout Interface Register in the DPO. Addressing the Readout Interface Register and other DPO Registers is explained in greater detail in subsequent paragraphs. Line 13\Delta sets up the Readout Interface to display the message residing at Field 2, Waveform D.

| 1ØØ | PRINT | 01:"ADR | ";3456       |       |       |     |             |                |  |

|-----|-------|---------|--------------|-------|-------|-----|-------------|----------------|--|

| 11Ø | PRINT | 01:"SCL | ";"TEKTRONIX | STILL | MAKES | THE | <b>BEST</b> | OSCILLOSCOPES" |  |

| 12Ø | PRINT | 01:"ADR | ";7296       |       |       |     |             |                |  |

| 13Ø | PRINT | 01:"OCT | ";"Ø4Ø1ØØ"   |       |       |     |             |                |  |

#### NOTE

This command does not set other registers (A/D Converter, Display Generator, Front Panel) to display Waveform D. Only the CRT readout displays the Field 2, Waveform D information. Therefore, the data previously stored at Waveforms A, B, C and D is not affected.

#### DPO Readout Characters

The set of characters that may be displayed on the DPO CRT (scale factor readout and message information) includes a portion of the 96-character ASCII Code set (the complete ASCII Code set is included as an appendix to this manual) plus some characters unique to the DPO readout. The characters available for display are: digits 0 through 9; all 26 upper case letters (upper case letter 0 shares the same character with digit 0); lower case letters c, d, m, n and p; space; and characters <, >,  $\downarrow$ ,  $\Omega$ ,  $\mu$ ,  $\Delta$ , /, +, -, and . (decimal point). All of these except  $\downarrow$ ,  $\Omega$ ,  $\mu$  and  $\Delta$  are standard ASCII characters.

The four unique readout characters ( $\downarrow$ ,  $\Omega$ ,  $\Delta$  and  $\mu$ ) are transferred (in either direction) as the following ASCII character:

| Readout Character | ASCII |

|-------------------|-------|

| <b>\</b>          | !     |

| $\Omega$          | 0     |

| Δ                 | =     |

| μ                 | u     |

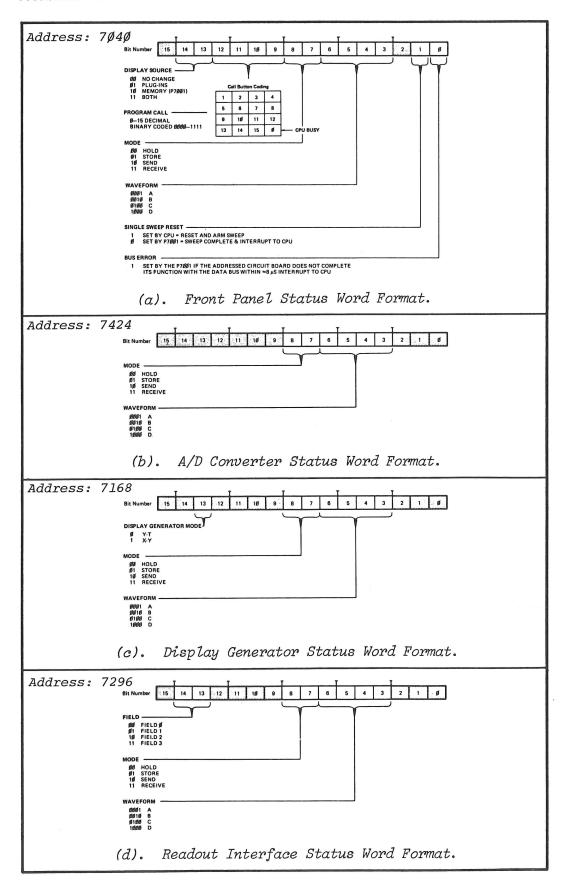

Figure 3-5 Status Word Formats

3 - 14

## Controlling the DPO

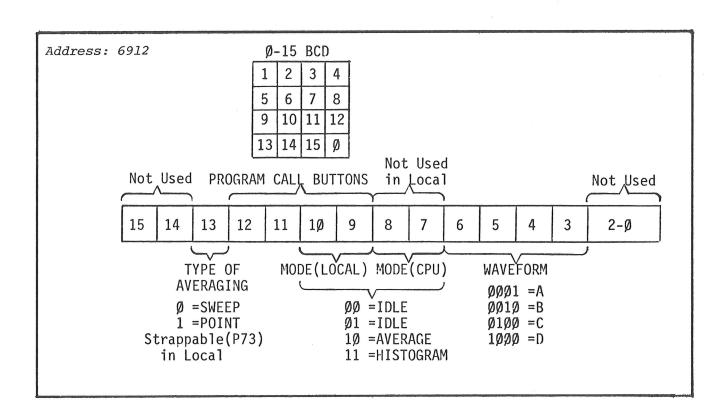

There are four (five if the HSA is installed) registers which can be programmed to control the P7001 Processor of the DPO. These are: A/D Converter, residing at decimal address 7424; Readout Interface, 7296; Display Generator, 7168; Front Panel, 7040; and Hardware Signal Averager (if installed), 6912. Further information on the registers involved in controlling the DPO may be found in the P7001 Processor Manual (Tektronix Part No. 070-1882-00), the P7001 A/D Converter Manual (070-1809-00), the P7001 Sample & Hold Manual (070-1810-00), the P7001 Readout Interface Manual (070-1609-00), the P7001 Display Generator Manual (070-1608-00), the P7001 Front Panel/Z-Axis Manual (070-1610-00), and the Hardware Signal Averager Manual (061-1344-00).

Status word format for the A/D Converter, Readout Interface, Display Generator and Front Panel Registers is illustrated in Figure 3-5. Figure 3-6 shows the HSA status word.

In most cases, the user does not have to learn to operate and set up these registers because the microprocessor residing in the interface takes over most of the operating procedures. However, there are some operations where it is necessary or desirable to control these registers bit by bit. In those cases, the "ADR\$" command is used to select the appropriate register, then the "OCT\$" command, which is explained in a subsequent paragraph, is used to set up the contents of the selected register.

Figure 3-6 HSA Status Register Bit Assignments

#### OCT Commands

The OCT (Octal) commands are used to send or receive octal representations of the 16-bit Status Words in the DPO Status Register (see Figures 3-5 and 3-6). The octal form is used to ease programming. Note that the octal numbers must be enclosed in quotation marks and treated as characters (i.e., in the form of a string literal). If not enclosed in quotation marks, the TEK 4051 will suppress the leading zero(s), which will cause the DPO to assert SRQ to the controller with a Status Word 113, indicating illegal operation. The octal representation may also be in the form of a string variable that is defined elsewhere in the program.

The DPO Address Register in the interface will not be affected after execution of the "OCT $\beta$ " or "OCT?" commands. In most cases, OCT will be immediately preceded by an "ADR $\beta$ " command to set the P7001 address on which OCT is intended to operate.

In the following TEK 4051 example, line 100 selects address 7040 (Front Panel Status Register), and line 110 sets the Front Panel Display source to P7001 Memory, Waveform A.

100 PRINT @1:"ADR ";7040 110 PRINT @1:"OCT ";"040010"

The following example may be used to transfer the contents of the Front Panel Status Register to the controller. Note that in line  $22\emptyset$ , the string variable A\$ is used rather that the numeric variable A. This is so the 4051 won't suppress the leading zero of the octal number.

200 PRINT @1: "ADR ";7040

21Ø PRINT @1:"OCT?"

22Ø INPUT @1:A\$

#### STO and HOL Commands

The "STOB" (Store) command is used to place the DPO in the Store mode, and consists of the command mnemonic followed by a one, two, three or four character string representing the DPO channels to be placed in the Store mode. The argument following the command mnemonic can be A, B, C or D or any combination in any order, as long as all adjacent characters are delimited with a comma (e.g., "A,C,D" or "D,C,A,B").

The "HOL $\beta$ " command puts the selected DPO channels in the Hold mode, and follows the same rules as the "STO $\beta$ " command for delimiters in the character string.

The "STO" and "HOLD" commands are used together to program the DPO to capture 1 to 4 input signals through the Vertical Amplifier and Time Base plug-ins. In the following TEK 4051 example, line 100 sets Channels A and B of the DPO to Store mode, lines 110 and 120 create a time delay to permit acquisition of a full waveform, and line 130 sets Channels A and B to the Hold mode.

- 1ØØ PRINT @1:"STO ";"A,B"

- 11Ø FOR I=1 to 20

- 12Ø NEXT I

- 13Ø PRINT @1:"HOL ";"A,B"

Note that the time delay required in lines 110 and 120 of the preceding example depends on the repetition rate of the input signal and the sweep speed at which the DPO is operating. A more detailed discussion of this, along with a graph showing digitizing time for various combinations of sweep speed and input signal repetition rates, may be found in the DPO Operators Manual (Tektronix Part No. 070-1599-00) starting on page 2-2 under the heading "SAMPLE & HOLD and A-D CONVERTER". Each 4051 FOR LOOP step uses approximately 4.5 milliseconds. Therefore, lines 110 and 120 in the above example insert approximately 90 milliseconds of delay into the program.

#### SSR Command

The "SSRB" (Single-Sweep-Reset) command can reset and arm the DPO triggering functions so that from one to four waveforms of single-shot events can be captured if the Time Base plug-ins are set up correctly. The command mnemonic is followed by a a one, two, three or four character string enclosed in quotation marks, as in the "STOB" and "HOLB" commands. Once again, a comma must serve as delimiter between characters.

In the following TEK 4051 example, after the programmed number of single-event waveforms (four in this example) have been captured, the DPO asserts the SRQ line to tell the controller that it has something to report. The controller should then be programmed to conduct a poll to determine the origin and nature of the SRQ. The DPO will send a status word of 84 decimal to indicate the single-sweep operation is complete.

- 100 INIT

- 11Ø ON SRQ THEN 2ØØ

- 120 PRINT @1:"SSR ";"A,B,C,D"

- 13Ø GOTO 13Ø

- 200 POLL N,M;1

- 21Ø IF M=84 THEN 3ØØ

- 22Ø RETURN

- 300 PRINT "SINGLE-SWEEP COMPLETED"

- 31Ø RETURN

## X-Y and Y-T Commands

The display mode of the DPO can be controlled either by addressing the Display Generator Status Register and using the "OCT" command to set bit 13 (as explained under OCT commands), or by using the "X-Y" and "Y-T" commands. If no display mode is specified, the program will default to the Y-T mode.

In the following TEK 4051 example, the Display Generator of the DPO is set to the Y-T mode of display (vertical input vs time).

PRINT @1:"Y-T "

In the following example, the Display Generator is set to the X-Y mode of display (horizontal input vs vertical input).

PRINT @1:"X-Y "

## Controlling the Hardware Signal Averager (HSA)

If a Hardware Signal Averager (Tektronix Part No. 644-0092-00) is installed in the DPO, it (the HSA) may be controlled with the "HAV\$" and "HIS\$" commands. The "HAV\$" command places the HSA in the averaging mode, selects the source and destination of the waveform to be averaged, specifies the number of averages to be taken, and chooses between Point and Sweep averaging. The following example shows how the "HAV\$" command is used:

PRINT @N:"HAV ";"S/D ";M;" X"

Where: N is the Device Address of the DPO, and;

- S is the source of the waveform to be averaged (DPO Waveform A, B, C or D), and;

- D is the destination of the averaged waveform, A, B, C or D (note that S/D must be followed by a space), and;

- M is a positive decimal integer from 1 to 12 (for "Sweep" averaging) or from 1 to 7 (for "Point" averaging), with the number of averages equal to  $2^{M}$ , and;

- X represents the type of averaging, "\( \bar{p}\)" for Point and "\( \bar{p}\)S" for Sweep (note that P or S \( \bar{must} \) be preceded by a space). If the type of averaging is not specified, the program will default to "Sweep".

Note that source and destination arrays may be the same if desired.

The "HISD" command, shown below, may be used to place the HSA in the Histogram mode of operation.

PRINT @N:"HIS ";"S/D/H ";M;" X"

Where: N, S, D, M and X are as described for the "HAV" command, and;

H is the destination of the Histogram, DPO Waveform A, B, C or D (note that H  $\underline{must}$  be followed by a space).

Note

The HSA must be strapped for "CPU" operation when used with the TEK 4051. See HSA Manual (TEK P/N 061-1344-00) for details.

3-18

## Front Panel Interrupts

When any one of the DPO front panel PROGRAM CALL buttons 1-15 is pushed, an SRQ is generated, then the controller should be programmed to conduct a poll. The response to the serial poll is decimal status word 83, indicating that one of the PROGRAM CALL buttons was pushed. In order to find out which button was pushed, the "FPI?" command is used, as in the following example:

100 PRINT 01:"FPI?" 110 INPUT 01:F

In the foregoing example, line 100 sets up the DPO to output the button information, and line 110 transfers the decimal number of the pushbutton (F) to the controller. If no front panel button was pushed, F in line 110 will be 0.

Since only one level of interrupt is allowed, all previous interrupts must be serviced and cleared before the PROGRAM CALL buttons become active again. It is also necessary to extinguish (clear) the CPU BUSY lamp (PROGRAM CALL button  $\emptyset$ ) if it is illuminated and it is desired to re-enable the PROGRAM CALL buttons. Previous interrupts and the CPU BUSY lamp may be cleared with the "CLI $\emptyset$ " command. This command has no effect on any other DPO status or memory. An example of the "CLI $\emptyset$ " command follows:

PRINT @1:"CLI "

The following sample routine shows a way to service the DPO PROGRAM CALL buttons. (Note - this sample routine only services Front Panel interrupts. A sample routine for Single-sweep interrupts is given under the heading "SSR Command".)

11Ø ON SRQ THEN 2ØØØ

----2ØØØ POLL N,M;1

2Ø1Ø IF M=83 THEN 21ØØ

2Ø2Ø RETURN 21ØØ PRINT @1:"FPI?"

211Ø INPUT @1:F

INIT

212Ø IF F>9 THEN 22ØØ

213Ø GOSUB F OF 31ØØ,32ØØ,33ØØ,34ØØ,35ØØ,36ØØ,37ØØ,38ØØ,39ØØ

214Ø GOTO 222Ø

22ØØ F=F-9

100

221Ø GOSUB F OF 4ØØØ,41ØØ,42ØØ,43ØØ,44ØØ,45ØØ

222Ø PRINT @1:"CLI "

223Ø RETURN

In the foregoing example, lines 3100 through 4500 are service subroutines for PROGRAM CALL buttons 1 through 15, respectively. Lines 2220 and 2230 serve to clear the Front Panel PROGRAM CALL buttons for all of the service subroutines before returning to the main program flow.

#### P7001/IEEE Interface

#### DCL Command

The "DCLb" command performs the function of the "CLIb" command (i.e., clears front panel interrupts and re-enables the DPO PROGRAM CALL buttons). In addition, execution of a "DCLb" commands the interface to go through a firmware initialization, initializes (sets to  $\emptyset$ ) the DPO Address Register, and sets all DPO operations with a default mode to the default mode. This command can also be used to clear service requests (SRQ). Device Clear can be executed as follows:

PRINT @1:"DCL "

## Transferring Waveform Arrays

Waveforms may be transferred from one DPO memory location (A, B, C or D) to another with the following command:

PRINT @1:"TAB "

Where: A is the waveform source (can be A, B, C or D), and;

B is the waveform destination (can also be A, B, C or D)...

## Acquiring and Scaling Data

The following routine is an example of how to acquire data from the DPO, to subtract a zero reference, and to appropriately scale the data. In this example, it is assumed that the left vertical plug-in slot in the 7704A mainframe is being used.

1

```

DIM W(512)

PRINT @1:"STO ";"B"

20

FOR I=1 to 3\emptyset

3Ø

40

NEXT I

PRINT @1:"HOL ";"B"

5Ø

PRINT "GROUND PROBE, PRESS RETURN"

6Ø

INPUT A$

70

PRINT @1:"STO ";"C"

80

9Ø

FOR I=1 to 3\emptyset

1ØØ

NEXT I

PRINT @1:"HOL ";"B"

110

PRINT @1:"DPC?"

12Ø

130

INPUT @1:W

14Ø

Z=\emptyset

FOR I=1 to 5\emptyset

15Ø

16Ø

Z=Z+W(I+2\emptyset\emptyset)

17Ø

NEXT I

18Ø

Z=Z/50

19Ø

PRINT @1:"DPB?"

2ØØ

INPUT @1:W

21Ø

W=W-Z

22Ø

PRINT @1:"CHL ";"BØ"

PRINT @1:"SCL?"

23Ø

INPUT @1:S$

24Ø

25Ø

V=VAL(S$)

M=POS(S$,"V",1)

26Ø

27Ø

T$=SEG(S$,M-1,1)

28Ø

M=POS("munp",T$,1)

290

V = V * 10 + (-3 * M)

W=W*(V/102.3)

300

```

In the preceding example, lines 10 through 50 "STORE" and "HOLD" a waveform in DPO memory location B. Line 60 displays a message to prompt the user to set up a ground reference waveform. Line 70 is simply a method to stop the controller until the user makes the necessary changes to ground the probe (or plug-in), then he would type in a carriage return to make the program continue (A\$ would not be used in subsequent computations). Lines 80 through 130 STORE, HOLD, and then transfer the ground reference waveform to the 4051. Lines 140 through 180 take an average of 50 elements from the middle of the ground reference waveform (to avoid end point inaccuracies) which becomes the zero reference value.

The raw data transfer of the original waveform occurs in lines 190 and 200, and the zero reference value is subtracted from the raw data in line 210. Lines 220 through 240 acquire the knob readout of the vertical plug-in which is stored in S\$. Lines 250 through 290 decode S\$ and translate it to a numerical value. Line 300 multiplies the data to the scale factor. The array W now contains the scaled data.

#### P7001/IEEE Interface

## Selecting Display Source

The following routine changes the "DISPLAY SOURCE" selector buttons of the DPO:

- 1Ø PRINT @1:"ADR ";7Ø4Ø

- 2Ø PRINT @1:"OCT?"

- 3Ø INPUT 01:S\$

- 4Ø S\$=REP("x",2,1)

- 5Ø PRINT @1:"OCT ";S\$

Where: In line 40, x=2 (plug-ins), or x=4 (memory), or x=6 (both).

In the foregoing example, lines 10 through 30 acquire the current settings of the Front Panel Status Word. Line 40 replaces the two binary bits that affect the display source setting, and line 50 outputs the new status word. It is necessary to read the status first so that the other front panel controls do not change when the new status word is sent.

## WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO. REFER TO OPERATORS SAFETY SUMMARY AND SERVICE SAFETY SUMMARY PRIOR TO PERFORMING ANY SERVICE.

# Section 4 MAINTENANCE

#### INTRODUCTION

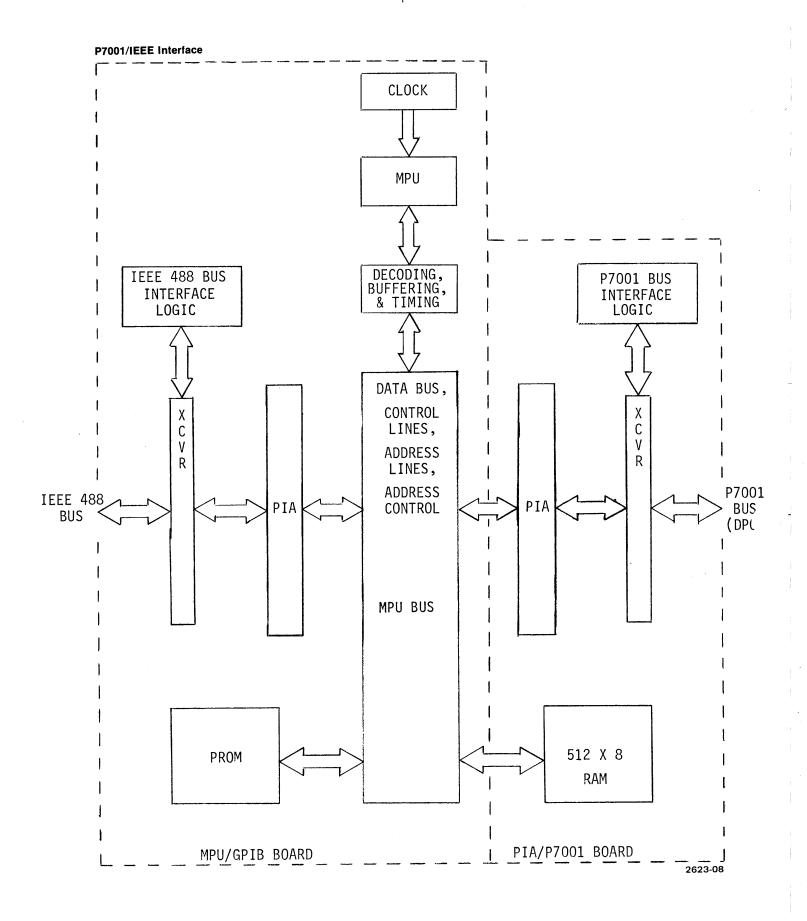

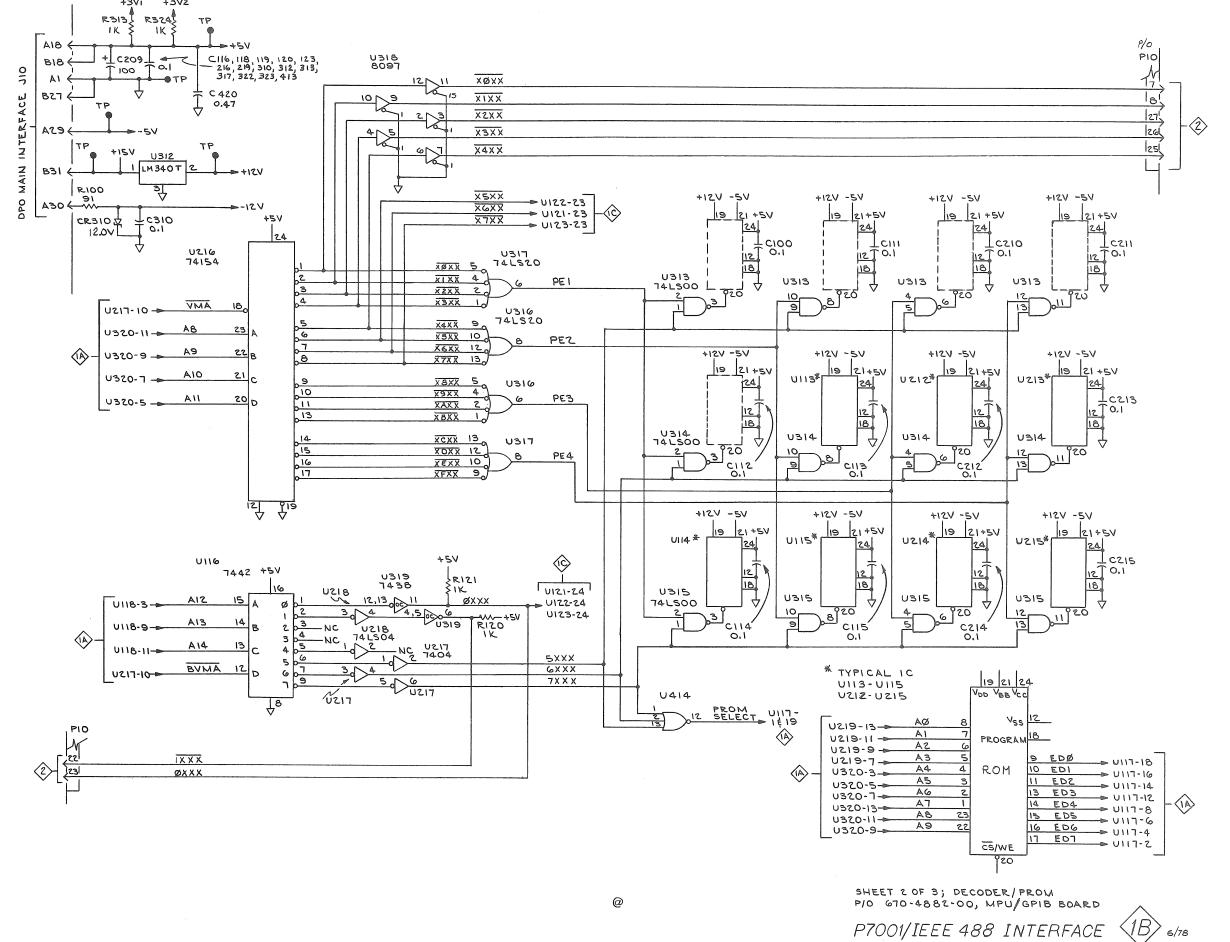

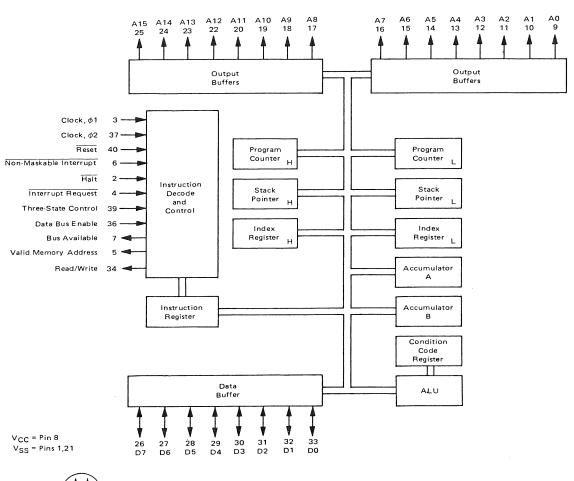

This section of the manual includes a Basic Block Diagram of the P7001/IEEE 488 Interface (Figure 4-1) and two Functional Block Diagrams (Figure 4-3, (MPU/GPIB Board) and (Figure 4-4, PIA/P7001 Board). The Basic Block Diagram provides a cursory examination of the interface's basic functions while a more detailed description is keyed to the Functional Block Diagrams. Each of the functional blocks within Figures 4-3 and 4-4 contains an alphanumeric designator enclosed in a diamond (e.g., 1A, 2B) ) that references a specific schematic diagram illustrating the circuitry involved. Where practical, IC numbers are included in the functional blocks to provide additional cross-referencing.

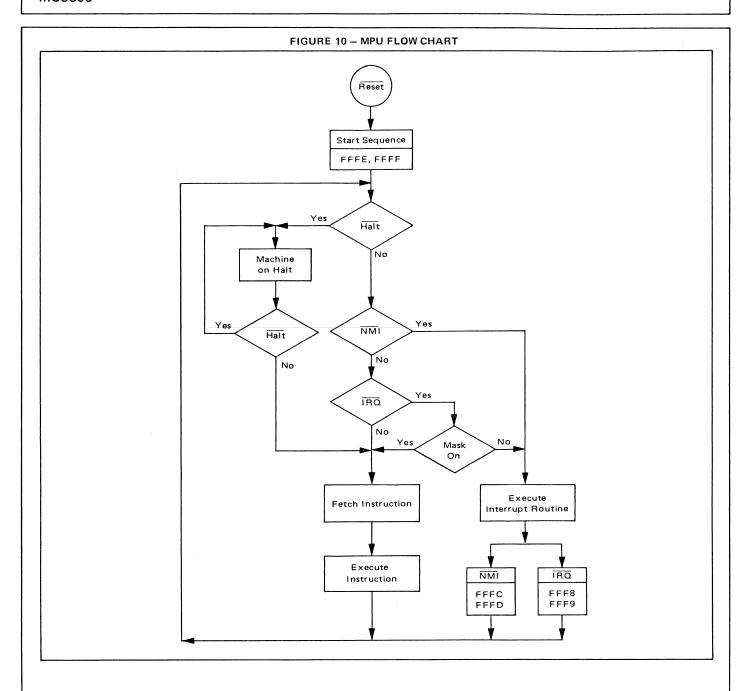

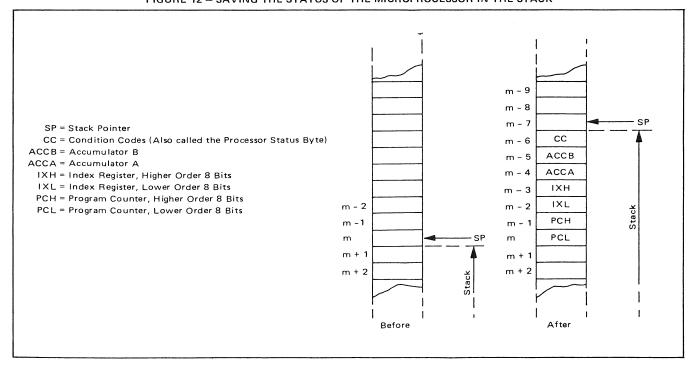

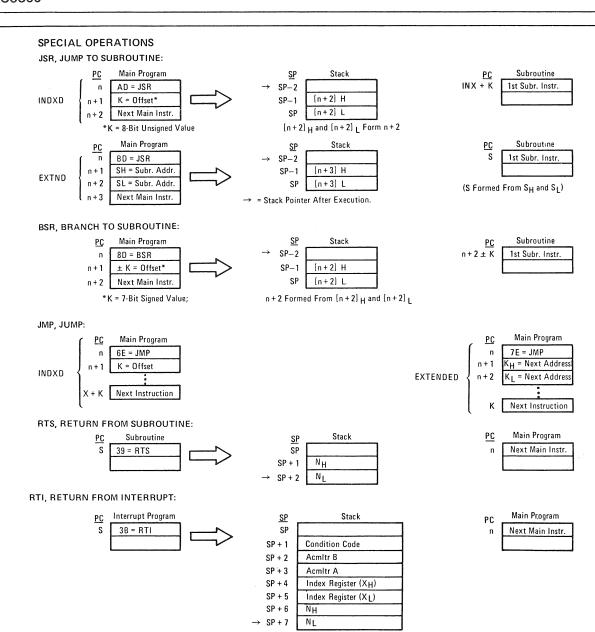

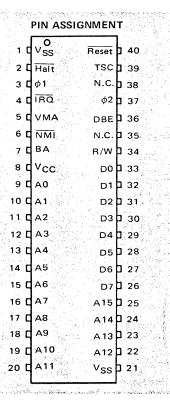

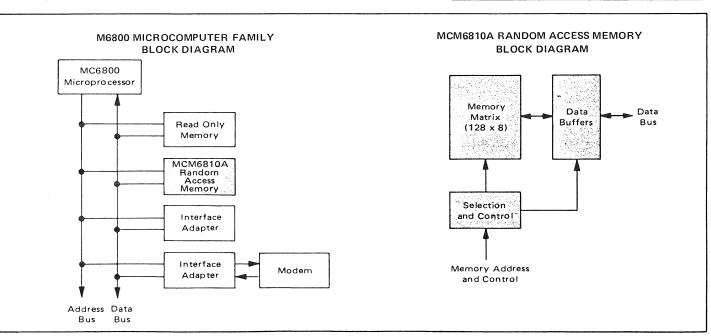

Familiarity with IEEE Standard 488-1975, "IEEE Standard Digital Interface for Programmable Instrumentation" is required for a comprehensive understanding of the IEEE 488 Bus functions and signals. For further information on P7001 data and control signals, see the P7001 Processor Service Manual (Tektronix Part No. 070-1882-00) and P7001 Main Interface Service Manual (Tektronix Part No. 070-1604-00). Signals associated with the MPU are explained in Motorola's M6800 Microprocessor Applications Manual and M6800 System Design Data Manual. Excerpts from the latter are included as an Appendix to this manual.

#### BASIC BLOCK DIAGRAM DESCRIPTION

Refer to Figure 4-1 for the following discussion. Data to be exchanged between the P7001 (Processor section of a Tektronix Digital Processing Oscilloscope) and an IEEE 488 Bus device are transferred from the bus of the "talker" through transceivers (buffers) to the PIA's (Peripheral Interface Adapters). The function of the PIA's is to adapt the data and control signals from the IEEE 488 Bus and P7001 Bus to the Microprocessor Bus.

The information from the PIA's is stored in RAM (Random Access Memory), where it is manipulated by the MPU (Microprocessor) in accordance with instructions stored in the PROM (Programmable Read-Only Memory). The informa-

Figure 4-1. Basic Block Diagram

## BASIC BLOCK DIAGRAM DESCRIPTION (Continued)

tion is then adapted to the "listener" bus by a second group of PIA's before being buffered out of the interface.

#### BLOCK DIAGRAM SIGNAL DEFINITIONS

The following signal definitions are provided as an introduction to the signal names used on the Functional Block Diagram (Figures 4-3 and 4-4) and to show their mnemonic derivations. More detailed signal descriptions may be obtained from the appropriate documents mentioned earlier in this section.

## IEEE 488 Bus Signals (Refer to Figure 4-3)

| NRFD                         | -      | Not Ready for Data |   |                                            |

|------------------------------|--------|--------------------|---|--------------------------------------------|

| NDAC                         | -      | Not Data Accepted  | _ | Data Transfer Control<br>(Handshake) Lines |

| DAV                          | -      | Data Valid         |   | (Handshake) Effics                         |

| ATN                          | -      | Attention          | 7 |                                            |

| IFC                          | -      | Interface Clear    |   |                                            |

| SRQ                          | -      | Service Request    | - | Interface Management Lines                 |

| REN                          | -      | Remote Enable      |   |                                            |

| EOI                          | -      | End or Identify    |   |                                            |

| $\overline{\text{DIO1}}$ thr | ough [ | 8 010              |   | Data Input/Output Lines                    |

## MPU (Motorola M6800) Bus Signals (Refer to Figure 4-3)

- VMA Valid Memory Address; this MPU output indicates to the PIA's, RAM and PROM that there is a valid address on the address bus.

- $R/\overline{W}$  Read when high/Write when low; this MPU output signals to the PIA's and RAM whether the MPU is in the read or write state.

- RESET This input is used to reset and start the MPU from a power-down state.

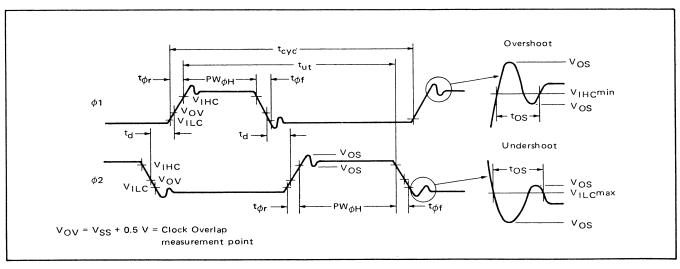

- $\varphi_{\text{1}}\,,\,\varphi_{\text{2}}\,\text{-}$  Phase 1 and Phase 2; two phases of a clock running at the  $V_{CC}$  level.

- NMI Mon-Maskable Interrupt; a low-going edge on this input requests that a non-mask interrupt sequence be generated within the MPU.

- TRQ Interrupt Request; a low level on this input requests that an interrupt sequence be generated in the MPU.

## MPU (Motorola M6800) Bus Signals (Continued)

- Data Bus Enable; this MPU input is tied to clock  $\phi_2$ . DBE

AØ through A15 - Three-state Address Bus outputs.

DØ through D7 - Bi-directional data bus.

$\overline{\text{HALT}}$ , TSC, BA - The  $\overline{\text{HALT}}$  and Three-State Control inputs, and the Bus Available output, are not used.

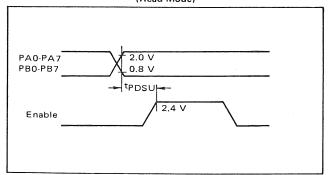

## P7001 Bus Signals (Refer to Figure 4-4)

$\overline{P-BIT\emptyset}$  through  $\overline{P-BIT 15}$  - P7001 Data Bits  $\emptyset$  (least significant) through 15.

PAØ through PA12 - P7001 Card Address Bits Ø (LSD) through 12.

- In/Out Interface Strobe from P7001 Front Panel Card I/O STROBE

Controller.

SYNC ACK - Sync Acknowledge to/from P7001 Common Bus.

- Data Mode Ø to P7001 Common Bus; functions as Read/ DATA MODE Ø

Write select in DPO.

- Data Channel Request to P7001 Front Panel Priority DATA CH REQ

Logic.

SELECT ACK - Select Acknowledge to P7001 Front Panel Priority

Logic.

CONT SYNC - Controller Sync to P7001 Common Bus.

BUS BUSY - Bus Busy to/from P7001 Common Bus.

- Data Channel Grant Input from next lower-priority DATA CH GRANT IN

card on P7001 common bus.

- Data Channel Grant Output to P7001 common bus. DATA CH GRANT OUT

POWER FAIL - Signal from P7001 common bus, engendered by DPO

turn-on.

## Internal Signals, GPIB Interface (Refer to Figure 4-3)

- "talk" enable signal from PIA U121. Used by control logic talk

circuitry to enable transceivers to send information.

- "listen" enable signal from PIA U121. Used by control logic listen

circuitry to enable the interface to control the NDAC and

NRFD lines when the DPO is listening.

- "ready" signal from PIA U121. Used by control logic circuitry to control  $\overline{\text{NRFD}}$  line. See "Acceptor Handshake State Diardy

gram" on page 21 of IEEE Standard 488-1975.

- "ready for <u>data</u>" signal from PIA U122. Used by control logic to control NRFD line. See "Source Handshake State Diagram" rfd

on page 19 of IEEE Standard 488-1975.

4-4

@

## Internal Signals, GPIB Interface (Continued)

- enabling signal from control logic circuitry to transceivers. out-enable

BDØ through BD7 - Buffered Data Bits Ø through 7.

Rx, Tx, Clk X8 - RS232C test signals, not part of Interface operation.

## Internal Signals, MPU & Control (Refer to Figure 4-3)

EDØ through ED7 - Data Bits Ø through 7 from PROM to MPU.

ØXXX - 4-digit hexadecimal number decoded from MPU address bus; 'X' indicates "don't care" condition. This line, together

with several additional lines from the MPU bus, is used to

enable the PIA's and the RAM.

5XXX, 6XXX, 7XXX - Signal descriptions same as ØXXX; these lines are used with PE1 - PE4 to enable the PROM.

$\overline{X}\emptyset \overline{X}\overline{X}$  through  $\overline{X7}\overline{X}\overline{X}$  - Signal descriptions same as  $\emptyset XXX$ ;  $\overline{X}\overline{\emptyset}\overline{X}\overline{X}$  and  $\overline{X1}\overline{X}\overline{X}$  are used for RAM enable, along with  $\phi_2$ , VMA and ØXXX.  $\overline{X2XX}$  through  $\overline{X7XX}$  are used for PIA enable, along with  $\phi_2$ , VMA and ØXXX.

PE1 through PE4 - These are the inverted, OR'ed combination of decoded hexadecimal address lines  $\overline{X\emptyset XX}$  through  $\overline{X3XX}$ ,  $\overline{X4XX}$  through  $\overline{X7XX}$ ,  $\overline{X8XX}$  through  $\overline{XBXX}$  and  $\overline{XCXX}$  through  $\overline{XFXX}$ , respectively. They are used, in conjunction with 5XXX, 6XXX and 7XXX as PROM enable lines.

#### Internal Signals, P7001 Bus Interface (Refer to Figure 4-4)

- Signal from control logic circuitry to PIA U29, indi-Done

cates P7001 bus transfer is completed.

- Interrupt signal from control logic circuitry to PIA **IRPT**

U29, indicates DPO interrupt.

- Signal from control logic enables data latch to read Read Data

incoming data.

- Signal from control logic enables data transceivers. P7001 Data Strobe

- Signal from PIA U27 clears the control logic flip-flops. Clear

Read/Write - Signal from PIA U27 tells the control logic to read

(high) or write (low) input from/to P7001 common bus.

P7001 Address Strobe - Signal from control logic enables address output buffers.

- Signal from PIA U27, positive-going edge enables the Enable

control logic to read or write input from or to P7001

common bus.

#### P7001/IEEE Interface

## Internal Signals, P7001 Common Bus (Continued)

DINØthrough DIN 15 - Data in from P7001 common bus.

DOUT Ø through DOUT 15- Data out to P7001 common bus.

PDØ through PD15 - Latched data from P7001 common bus.

## Internal Signals, RAM (Refer to Figure 4-4)

RAM enable - Signal from control logic enables RAM.

#### CLOCK

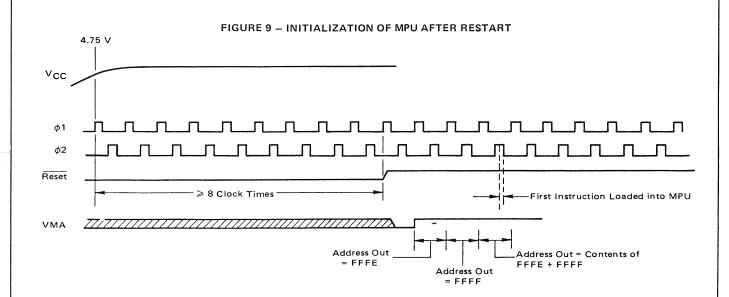

The clock circuitry consists of a crystal-controlled 4 MHz oscillator followed by a divide-by-four counter. Both output phases of the counter are used, providing the two clock phase signals,  $\phi_1$  and  $\phi_2$ .  $\phi_1$  is used by the MPU to set up its own internal registers.  $\phi_2$  is used, along with the VMA signal, to provide timing for the PIA's, the RAM and the PROM.

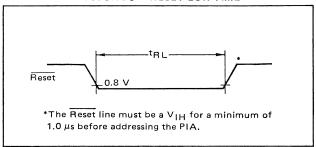

#### RESET

When power in the DPO is first turned on, the  $\overline{\text{POWER FAIL}}$  pulse is generated in the P7001 and applied from the P7001 bus to the RESET circuitry in the Interface. The RESET One-Shot, U310, delays the pulse approximately 200 milliseconds before it releases  $\overline{\text{RESET}}$ . The  $\overline{\text{RESET}}$  pulse accomplishes the following:

- 1. Initializes the MPU and the PIA's.

- 2. Under firmware control (instructions stored in PROM), initializes the RAM and programs the PIA's to the required status.

- 3. Through the Address Decode and other logic circuitry, causes PIA U122 to assert  $\overline{SRQ}$ , the GPIB Service Request line. The MPU will remember why the  $\overline{SRQ}$  was generated by storing a decimal status word (81 in the case of DPO power-up) in the SRQ table of the RAM.

#### PROM

The 1K X 8-bit UV-erasable static PROM (Programmable Read-Only Memory) contains the firmware necessary to operate the P7001/IEEE 488 Interface.

4-6

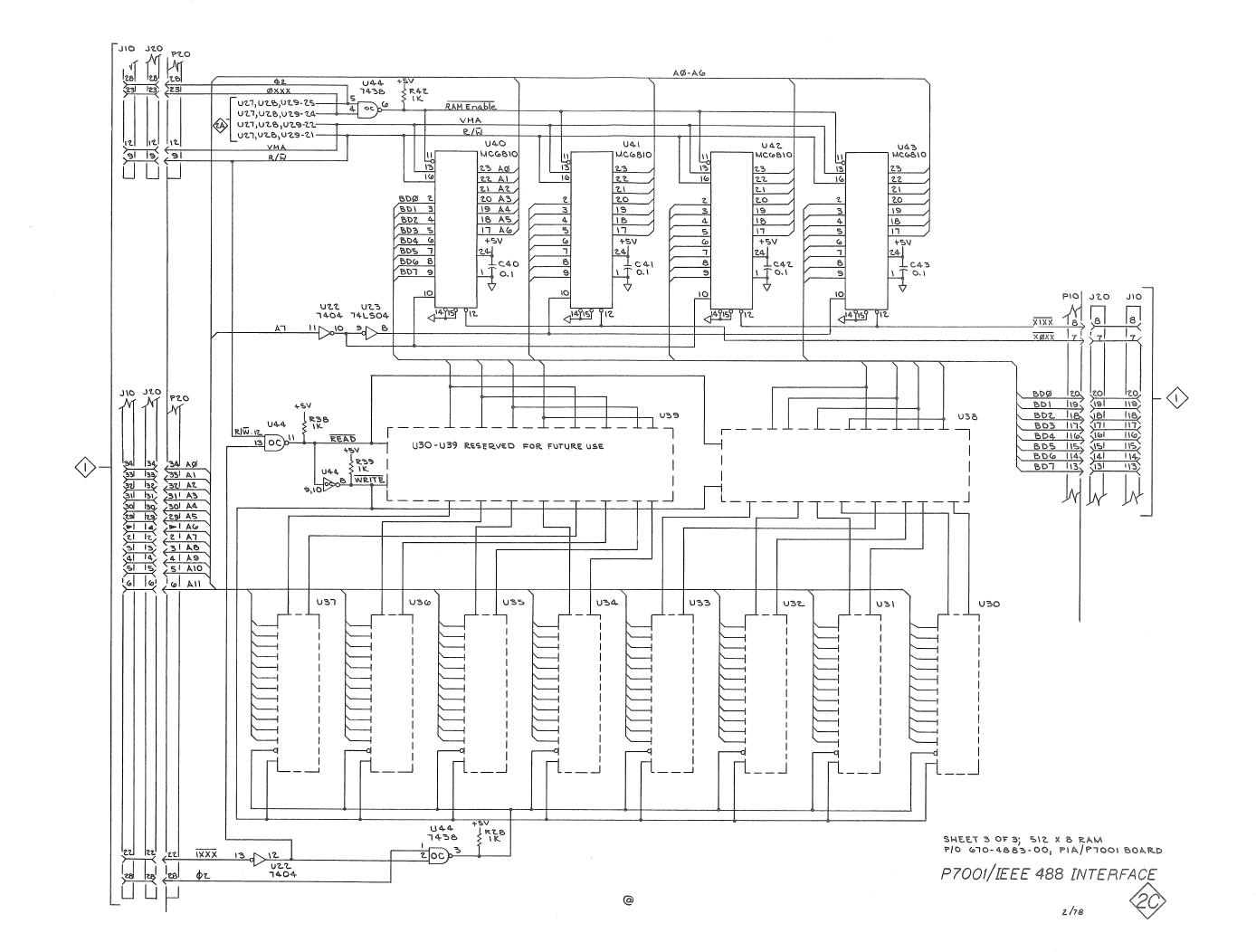

RAM

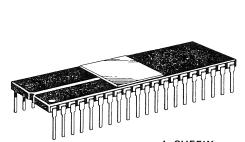

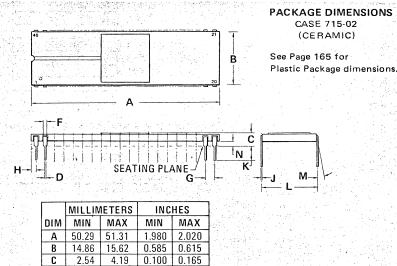

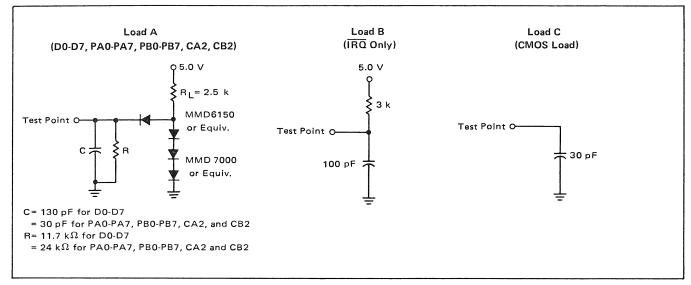

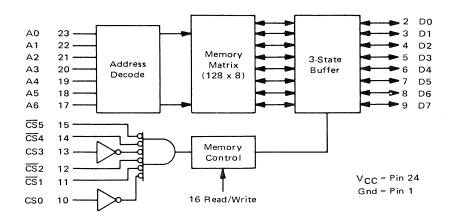

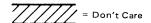

The 512 X 8-bit static RAM (Random Access Memory) contains all the read/write registers for the interface, including the DPO Address Register, DPO Data Register, DPO Status Register, and input and output buffers for the GPIB. Detailed information on these chips will be found in Motorola's MCM6810A Data Sheets, found in  $Appendix\ A$  in the rear of this manual, and the M6800 Microcomputer System Design Data Manual.

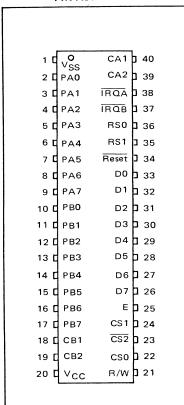

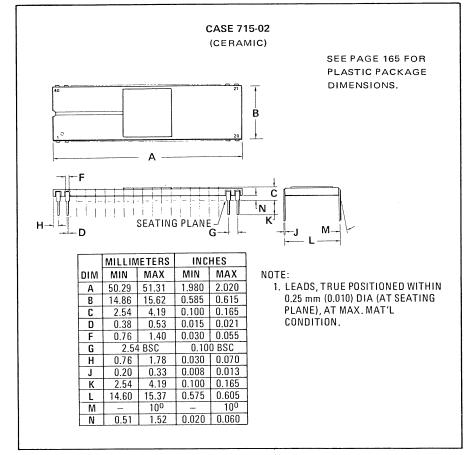

PIA

The PIA's provide a means of interfacing external devices to the MPU. Data sheets for the PIA's (Motorola MC6820) will also be found in  $Appendix\ A$  and Motorola's M6800 Microcomputer System Design Data Manual.

#### MPU & CONTROL

The MPU & Control section contains the decision-making circuitry for the interface. Operation of the MPU (Microprocessing Unit or Microprocessor) is quite complex and will not be analyzed to any great extent in this manual. Information regarding the MPU can be found in Motorola's M6800 Applications Manual, M6800 Microcomputer System Design Data Manual, or Appendix A of this manual.

The Address Decode Logic receives address lines A8 through A14 from the MPU, and when gated by the  $\overline{\text{VMA}}$  line, provides hexadecimal outputs used to address/select the PIA's, RAM and PROM.

The Data Latch (U117) is used to latch the PROM Data (EDØ - ED7) in order to provide faster access to the PROM data and decrease the capacitive load on the Data Transceivers. This provides a more reliable data transfer from the PROM to the MPU and from the Data Transceivers to the PIA's and RAM.

#### GPIB INTERFACE

The GPIB Interface includes PIA's and associated circuitry required to

#### P7001/IEEE Interface

### GPIB INTERFACE (Continued)

interface data and control signals between the MPU and IEEE  $488\,$  Bus. All control and interface management signals except  $\overline{\text{NRFD}}$  are generated or accepted from the bus under firmware control.

$\overline{\text{NRFD}}$  is under hardware control because of the limited time in which it must respond to the system controller. When  $\overline{\text{ATN}}$  is asserted by the controller, the Control Logic will cause  $\overline{\text{NRFD}}$  to be asserted in less than 200 nanoseconds, much faster than the MPU could respond. When  $\overline{\text{NRFD}}$  has been asserted, the Control Logic will respond to any interface message received or transmitted by controlling the rdy, rfd, talk or listen lines.

SW412 connected to PIA U121 is the 5-bit DIP switch used to select the Device Address of the DPO.

#### P7001 INTERFACE

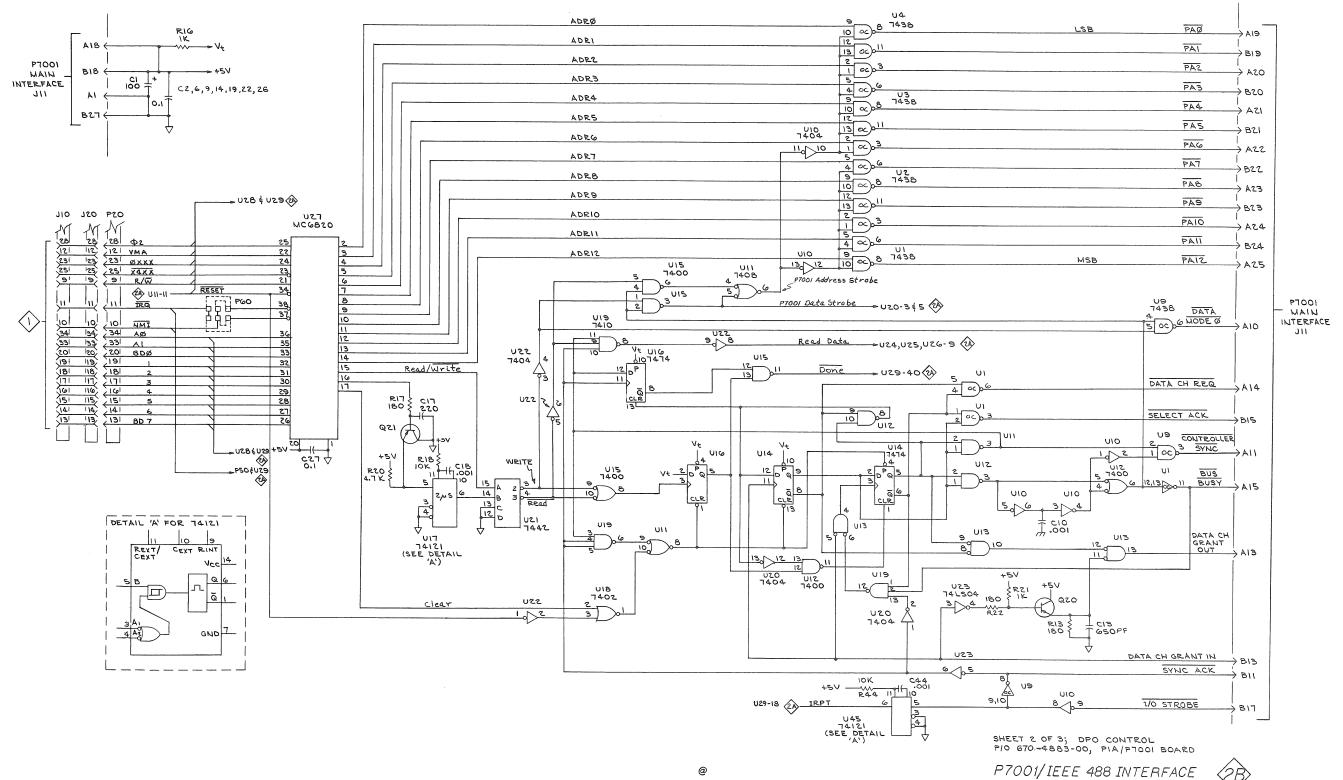

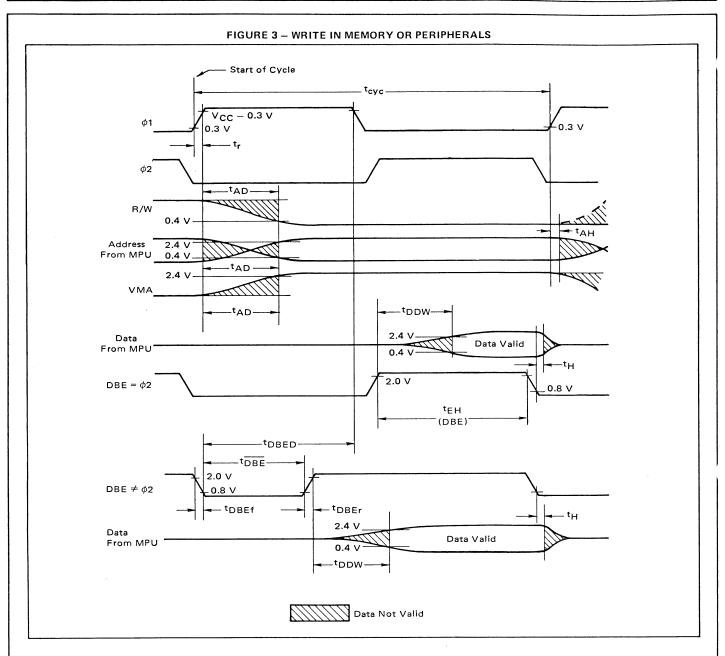

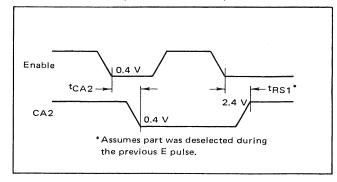

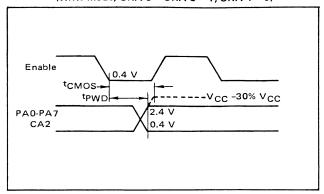

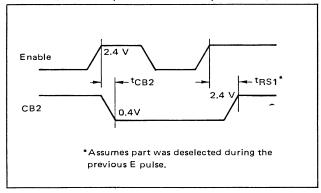

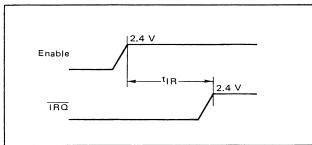

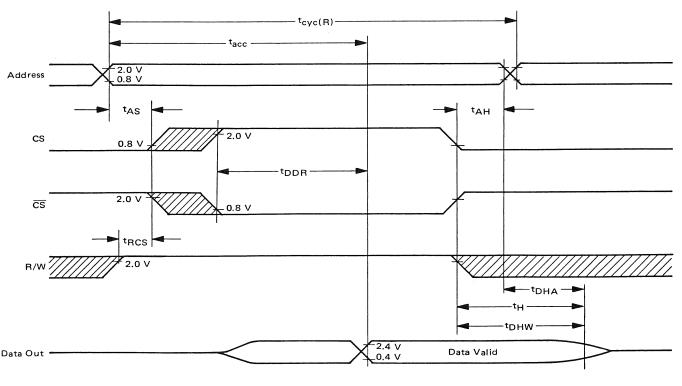

The P7001 Interface circuitry includes PIA's and associated Data Latches, Transceivers and Buffers, and control logic needed to interface the DPO's P7001 Bus to the MPU. Bus timing diagrams are shown in Figures 4-2A and 4-2B.

When the MPU wants to read data from, or write data to the DPO, it first sets up the PIA's (U29 for READ, U27 and U28 for WRITE) by programming. After a 10 microsecond delay to ensure that all Address lines, Read/Write and other control lines are settled, the Enable line (from U27) is asserted, causing the Control Logic to send out DATA CH REQ. The Front Panel Priority Logic in the P7001 replies with DATA CH GRANT IN, provided that another P7001 card (e.g., A/D Converter, Display Generator) is not in control of the bus.

As soon as DATA CH GRANT IN is received, the Control Logic will send out SELECT ACK. This returns to the P7001 Front Panel Priority Logic and terminates DATA CH GRANT IN. The Control Logic then checks to make sure SYNC ACK and BUS BUSY are not present. If not, the Control Logic goes to the Master State and gates the Address lines with P7001 Address Strobe. If the operation is a "write", the Data lines are also gated via the P7001 Data Strobe.

- NOTES: ① 3.5usec max; if greater than 3.5usec, P7001 Bus will time-out (hardware error).

- (2) 50nsec minimum.

- 3 Drawing not to scale.

Figure 4-2B. P7001 Bus Write Operation

#### P7001/IEEE Interface

## P7001 INTERFACE (Continued)

If the P7001 Front Panel is being addressed, it will now disconnect the Interface Control Logic for 500 milliseconds so that it cannot be disturbed for that 500 milliseconds. If the operation is a "write", the P7001 Front Panel will latch the status word and perform the appropriate operation. The Front Panel then sends  $\overline{\text{SYNC ACK}}$  back to the Control Logic. This sets the DPO to the idle state and terminates  $\overline{\text{BUS BUSY}}$ .

If one of the P7001 PROGRAM CALL buttons is pushed, an  $\overline{I/O~STROBE}$  is generated. The Control Logic receives the  $\overline{I/O~STROBE}$  and interrupts the MPU via PIA U29 and the IRPT signal. The MPU programs PIA U29 to ignore IRPT (to discourage continuous interrupt), and looks at the P7001 Front Panel status to determine why the  $\overline{I/O~STROBE}$  was issued. If it was for a valid reason (the MPU determines this under program control), the MPU will enable U29 to recognize IRPT again, and will assert  $\overline{SRQ}$  on the IEEE 488 Bus.

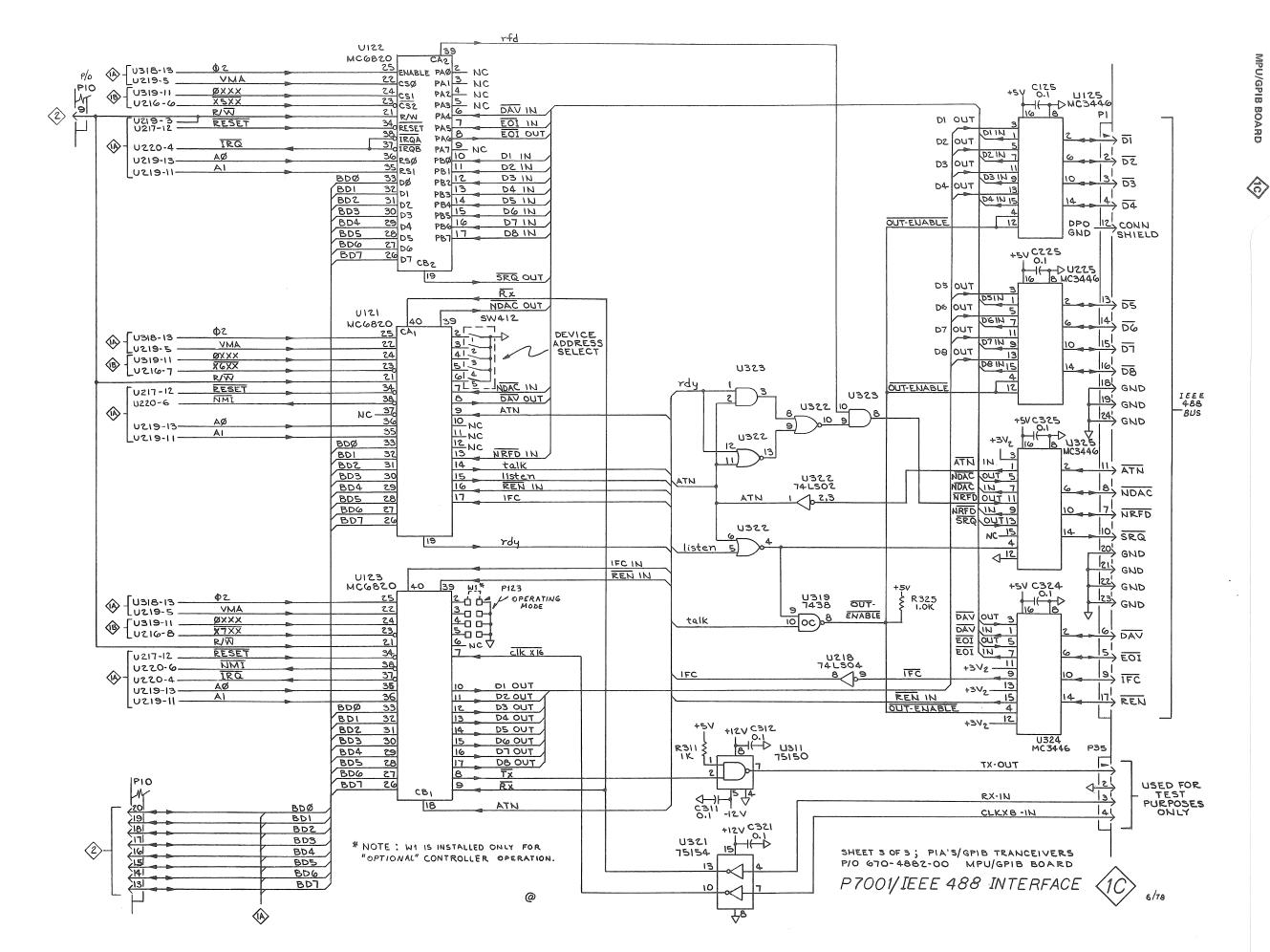

Figure 4-3 P. FUNCTIONAL BLOCK DIAGRAM PAGE 4-11 MPU/GPIB BOARD 2/78

MPU/GPIB Board

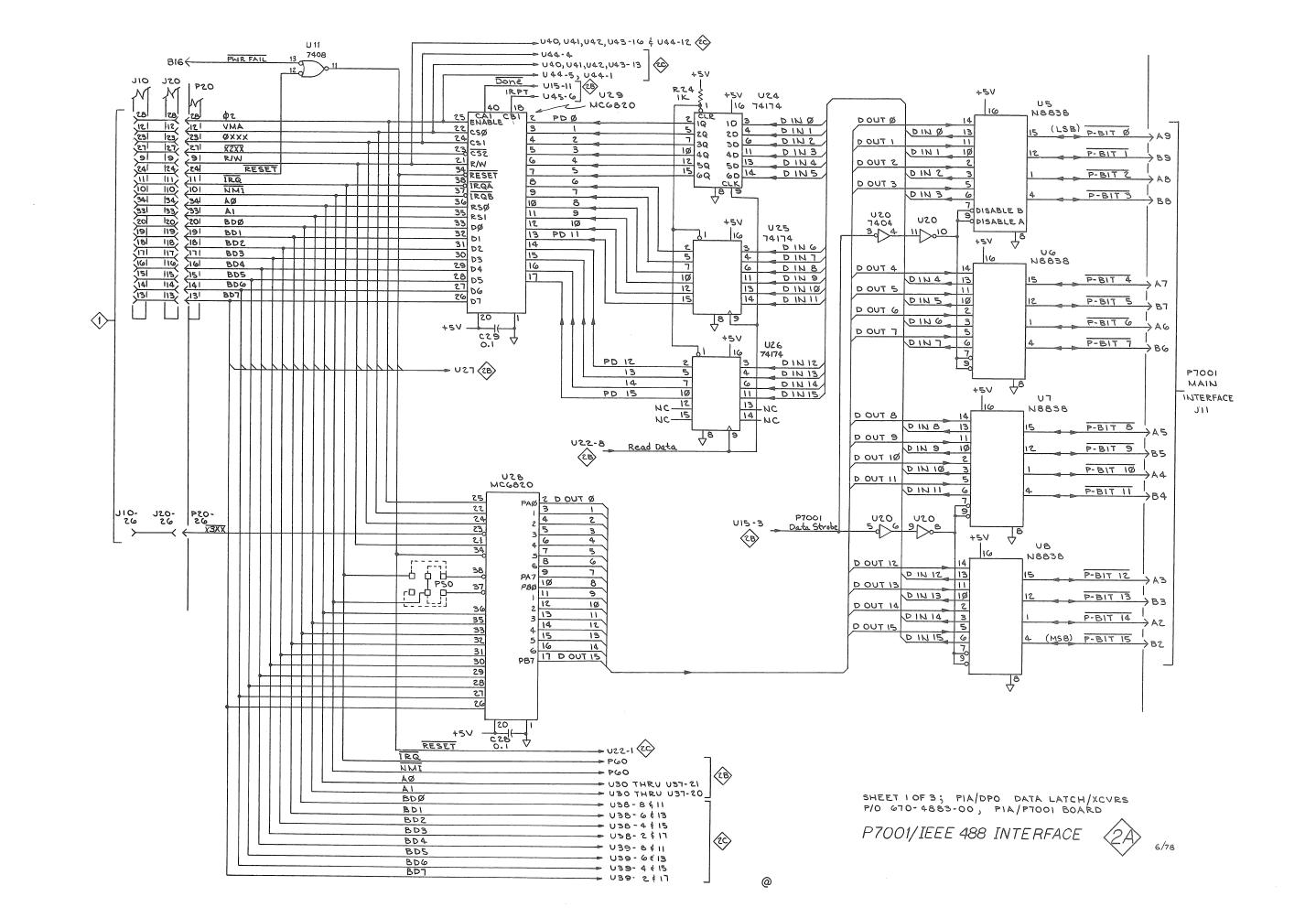

Figure 4-4 PAGE 4-12 FUNCTIONAL BLOCK DIAGRAM PIA/P7001 BOARD 2/78

Component Location

PIA/P7001 Board

## **DIAGRAMS**

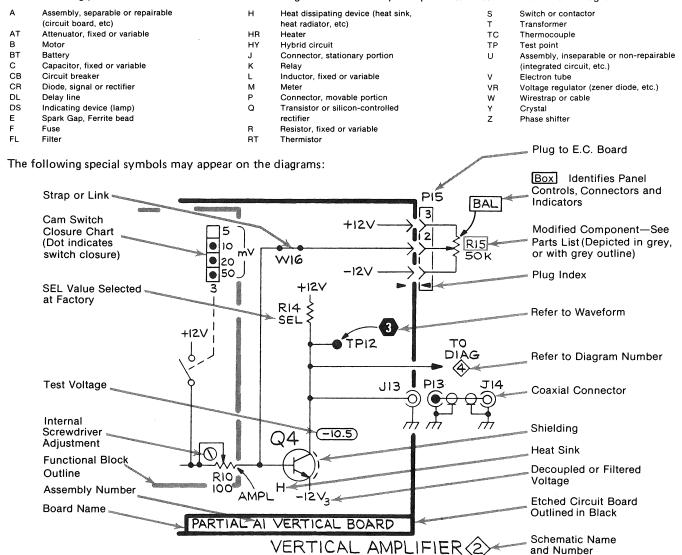

#### Symbols and Reference Designators

Electrical components shown on the diagrams are in the following units unless noted otherwise:

Capacitors = Values one or greater are in picofarads (pF).

Values less than one are in microfarads ( $\mu$ F).

Resistors = Ohms  $(\Omega)$ .

Graphic symbols and class designation letters are based on ANSI Standard Y32.2-1975.

Logic symbology is based on ANSI Y32.14-1973 in terms of positive logic. Logic symbols depict the logic function performed and may differ from the manufacturer's data.

The overline on a signal name indicates that the signal performs its intended function when it goes to the low state.

Abbreviations are based on ANSI Y1.1-1972.

Other ANSI standards that are used in the preparation of diagrams by Tektronix, Inc. are:

Y14.15, 1966 Drafting Practices.

Y14.2, 1973 Line Conventions and Lettering.

Y10.5, 1968 Letter Symbols for Quantities Used in Electrical Science and

Electrical Engineering.

The following prefix letters are used as reference designators to identify components or assemblies on the diagrams.

\$

@

# REPLACEABLE ELECTRICAL PARTS

#### PARTS ORDERING INFORMATION

Replacement parts are available from or through your local Tektronix, Inc. Field Office or representative.

Changes to Tektronix instruments are sometimes made to accommodate improved components as they become available, and to give you the benefit of the latest circuit improvements developed in our engineering department. It is therefore important, when ordering parts, to include the following information in your order: Part number, instrument type or number, serial number, and modification number if applicable.

If a part you have ordered has been replaced with a new or improved part, your local Tektronix, Inc. Field Office or representative will contact you concerning any change in part number.

Change information, if any, is located at the rear of this manual.

#### SPECIAL NOTES AND SYMBOLS

X000 Part first added at this serial number

00X Part removed after this serial number

#### ITEM NAME

In the Parts List, an Item Name is separated from the description by a colon (:). Because of space limitations, an Item Name may sometimes appear as incomplete. For further Item Name identification, the U.S. Federal Cataloging Handbook H6-1 can be utilized where possible.

## **ABBREVIATIONS**

| ACTR   | ACTUATOR             | PLSTC    | PLASTIC         |

|--------|----------------------|----------|-----------------|

| ASSY   | ASSEMBLY             | QTZ      | QUARTZ          |

| CAP    | CAPACITOR            | RECP     | RECEPTACLE      |

| CER    | CERAMIC              | RES      | RESISTOR        |

| CKT    | CIRCUIT              | RF       | RADIO FREQUENCY |

| COMP   | COMPOSITION          | SEL      | SELECTED        |

| CONN   | CONNECTOR            | SEMICOND | SEMICONDUCTOR   |

| ELCTLT | ELECTROLYTIC         | SENS     | SENSITIVE       |

| ELEC   | ELECTRICAL           | VAR      | VARIABLE        |

| INCAND | INCANDESCENT         | ww       | WIREWOUND       |

| LED    | LIGHT EMITTING DIODE | XFMR     | TRANSFORMER     |

| NONWIR | NON WIREWOUND        | XTAL     | CRYSTAL         |

|        |                      |          |                 |

## CROSS INDEX—MFR. CODE NUMBER TO MANUFACTURER

| Mfr. Code | Manufacturer                                                             | Address                                  | City, State, Zip        |

|-----------|--------------------------------------------------------------------------|------------------------------------------|-------------------------|

| 01121     | ALLEN-BRADLEY COMPANY                                                    | 1201 2ND STREET SOUTH                    | MILWAUKEE, WI 53204     |

| 01295     | TEXAS INSTRUMENTS, INC., SEMICONDUCTOR GROUP                             | P O BOX 5012, 13500 N CENTRAL EXPRESSWAY | DALLAS, TX 75222        |

| 04713     | MOTOROLA, INC., SEMICONDUCTOR PROD. DIV.                                 | 5005 E MCDOWELL RD, PO BOX 20923         | PHOENIX, AZ 85036       |

| 07263     | FAIRCHILD SEMICONDUCTOR, A DIV. OF FAIRCHILD CAMERA AND INSTRUMENT CORP. | 464 ELLIS STREET                         | MOUNTAIN VIEW, CA 94042 |

| 27014     | NATIONAL SEMICONDUCTOR CORP.                                             | 2900 SEMICONDUCTOR DR.                   | SANTA CLARA, CA 95051   |

| 32159     | WEST-CAP ARIZONA                                                         | 2201 E. ELVIRA ROAD                      | TUCSON, AZ 85706        |

| 34630     | TYCO FILTERS DIV., INC.                                                  | 3940 W. MONTECITO                        | PHOENIX, AZ 85019       |

| 50434     | HEWLETT-PACKARD COMPANY                                                  | 640 PAGE MILL ROAD                       | PALO ALTO, CA 94304     |

| 56289     | SPRAGUE ELECTRIC CO.                                                     | 87 MARSHALL ST.                          | NORTH ADAMS, MA 01247   |

| 59660     | TUSONIX INC.                                                             | 2155 N FORBES BLVD                       | TUCSON, AZ 85705        |