# PM111 PERSONALITY MODULE FOR 6809 MICROPROCESSOR

INSTRUCTION MANUAL

# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

# PM111

# PERSONALITY MODULE FOR 6809 MICROPROCESSOR

INSTRUCTION MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

070-4155-00 Product Group 57

Serial Number \_\_

First Printing SEPT 1981 Revised JUN 1982

Copyright © 1981 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and registered trademarks of Tektronix, Inc. TELEQUIP-MENT is a registered trademark of Tektronix, U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

#### TABLE OF CONTENTS

|         |                    | Page |

|---------|--------------------|------|

| LIST OF | ILLUSTRATIONS      | vi   |

| LIST OF | TABLES             | vii  |

| OPERATO | R´S SAFETY SUMMARY | viii |

#### PART 1 OPERATOR'S INFORMATION

| Section 1 | INTRODUCTION1-1                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | OVERVIEWl-1<br>ABOUT THIS MANUALl-1<br>CONVENTIONS USED IN THIS MANUALl-2                                                                                                                                                                                                                                                                                                                                                                      |

| Section 2 | OPERATING THE PM 111 PERSONALITY MODULE2-1                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | OVERVIEW.2-1MODES OF OPERATION.2-1CONNECTION INSTRUCTIONS.2-1CONNECTING THE PM 111 TO THE LOGIC ANALYZER.2-1CONNECTING THE PM 111 TO THE 6809 SYSTEMUNDER TEST.UNDER TEST.2-2POWER SOURCE.2-3STORING THE PM 111 PERSONALITY MODULE.2-3PROGRAMMING THE 7D02.2-3DATA Field.2-4ADDRESS Field.2-4FETCH1 Field.2-4FETCH1+2 Field.2-5BA Field.2-6INVAL OP Field.2-6TIMING WR Field.2-6CLOCK QUALIFICATION.2-7C9.2-9C6.2-9C7.2-9C6.2-10C4.2-10C4.2-11 |

|           | MNEMONIC DISPLAY OF ACQUIRED DATA                                                                                                                                                                                                                                                                                                                                                                                                              |

PM 111

|            | THE HEADER                        | . <b></b> 2–13                         |

|------------|-----------------------------------|----------------------------------------|

|            | DISPLAY OF NON-FETCH1 CYCLES      |                                        |

|            | DISPLAY OF FETCH-1 CYCLES         |                                        |

|            |                                   |                                        |

|            | Instruction Opcodes               |                                        |

|            | Instruction Operands              |                                        |

|            | Asterisks                         |                                        |

|            | MNEMONIC DISPLAY EXAMPLE          |                                        |

|            | ABSOLUTE DISPLAY OF ACQUIRED DATA |                                        |

|            | THE HEADER                        |                                        |

|            |                                   |                                        |

|            | DATA DISPLAY                      |                                        |

|            | ABSOLUTE DISPLAY EXAMPLE          |                                        |

|            | ADDITIONAL INFORMATION            |                                        |

|            | CONTROL LINES                     |                                        |

|            | 6809E OPERATING CONSIDERATIONS    |                                        |

|            |                                   |                                        |

|            | SPECIAL INSTRUCTION OPCODES       |                                        |

|            | HALTING THE 6809 MICROPROCESSOR   | . <b></b> 2–24                         |

|            |                                   |                                        |

| Section 3  | SPECIFICATIONS                    | 3-1                                    |

| becchion 5 |                                   | •••••••••••••••••••••••••••••••••••••• |

|            |                                   |                                        |

|            |                                   | ~ -                                    |

|            | OVERVIEW                          |                                        |

|            | SYSTEM DESCRIPTION                |                                        |

|            | SAFETY GOALS                      |                                        |

|            |                                   |                                        |

#### PART 2 SERVICE INFORMATION

#### WARNING

The following servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing other than that contained in operating instructions unless you are qualified to do so.

| SERVICING | SAFETY | SUMMARY                                                        |                                                                                                   | •••••                     | •••••  |       | • • • • • • | 4-0                                    |

|-----------|--------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------|--------|-------|-------------|----------------------------------------|

| Section 4 | THEC   | ORY OF C                                                       | PERATION                                                                                          | • • • • • • • •           | •••••• | ••••• | • • • • • • | 4-1                                    |

|           |        | OVERVIE<br>FUNCTIC<br>BLOCK E<br>CONVENT<br>THE FET<br>SELF-TE | HEORY OF OF<br>W<br>NS<br>IAGRAMS AND<br>IONS USED I<br>CH PREDICTO<br>ST CIRCUITF<br>ARDWARE CON | O SCHEMA<br>IN THIS<br>DR | ATICS  |       | •••••       | 4-2<br>4-2<br>4-2<br>4-2<br>4-3<br>4-3 |

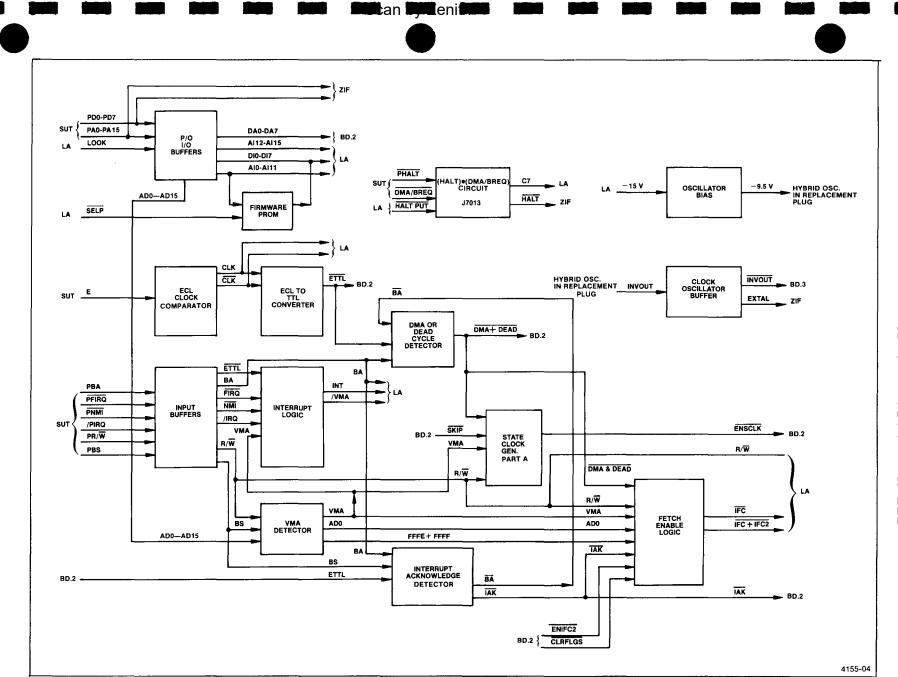

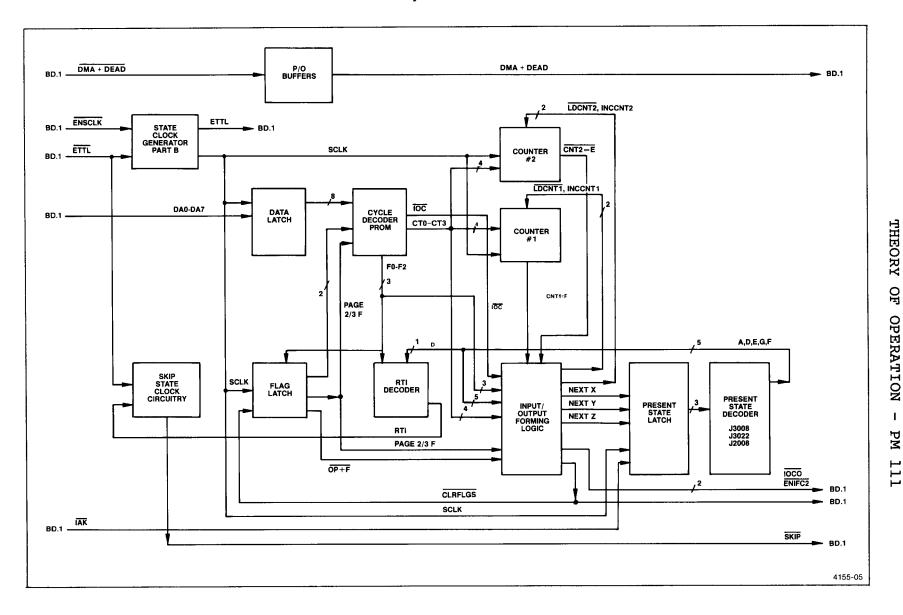

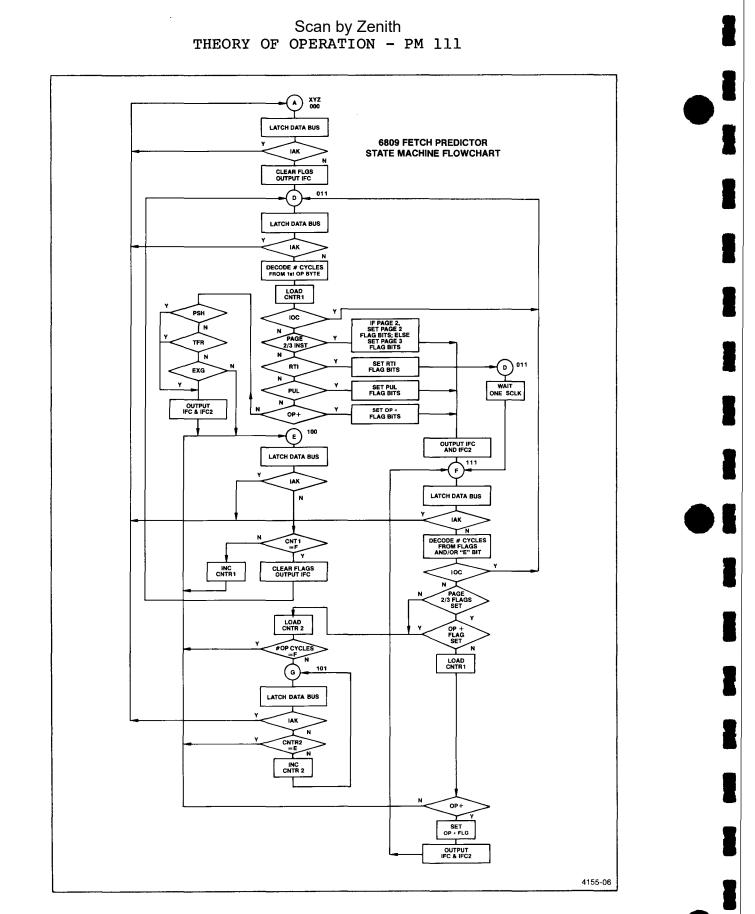

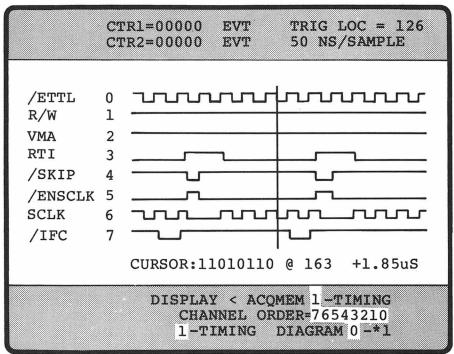

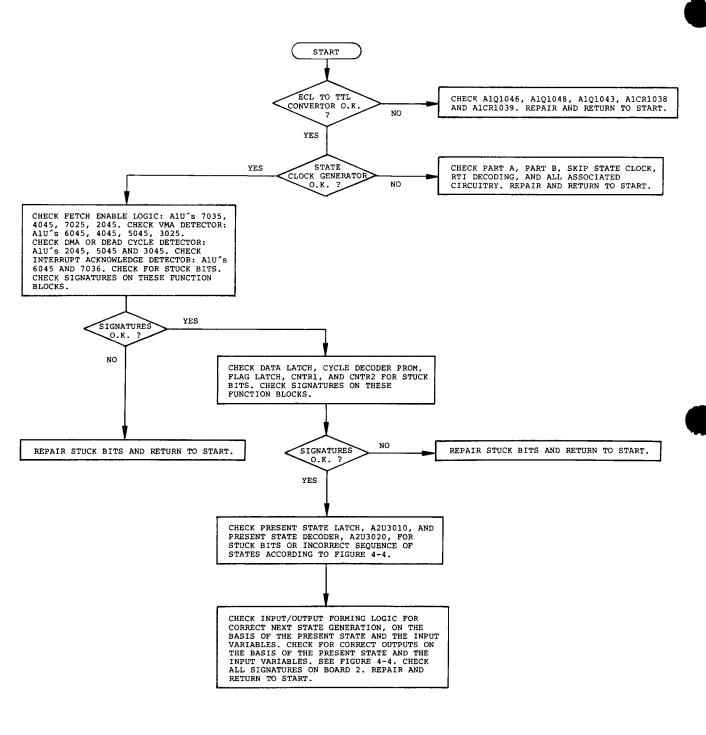

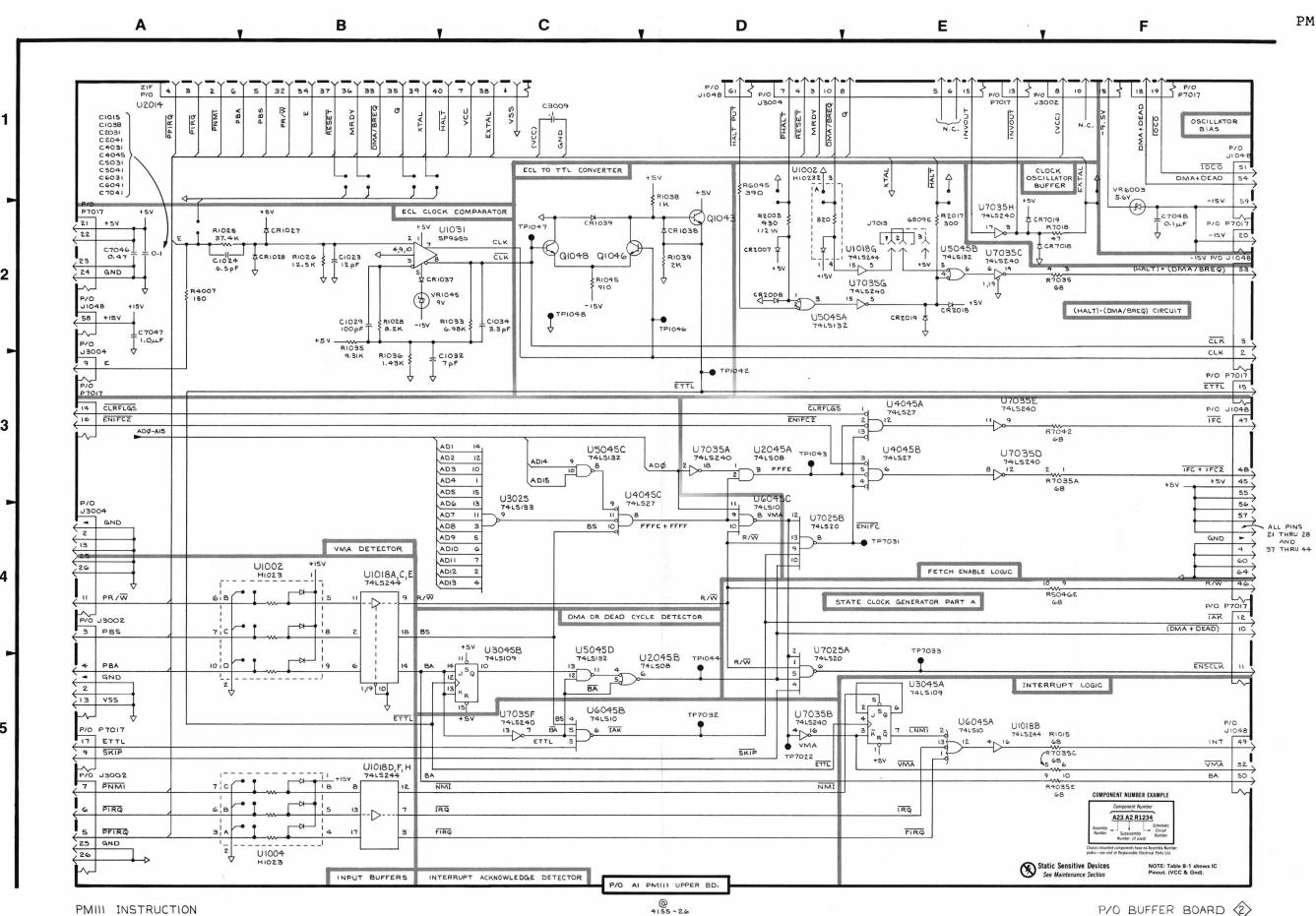

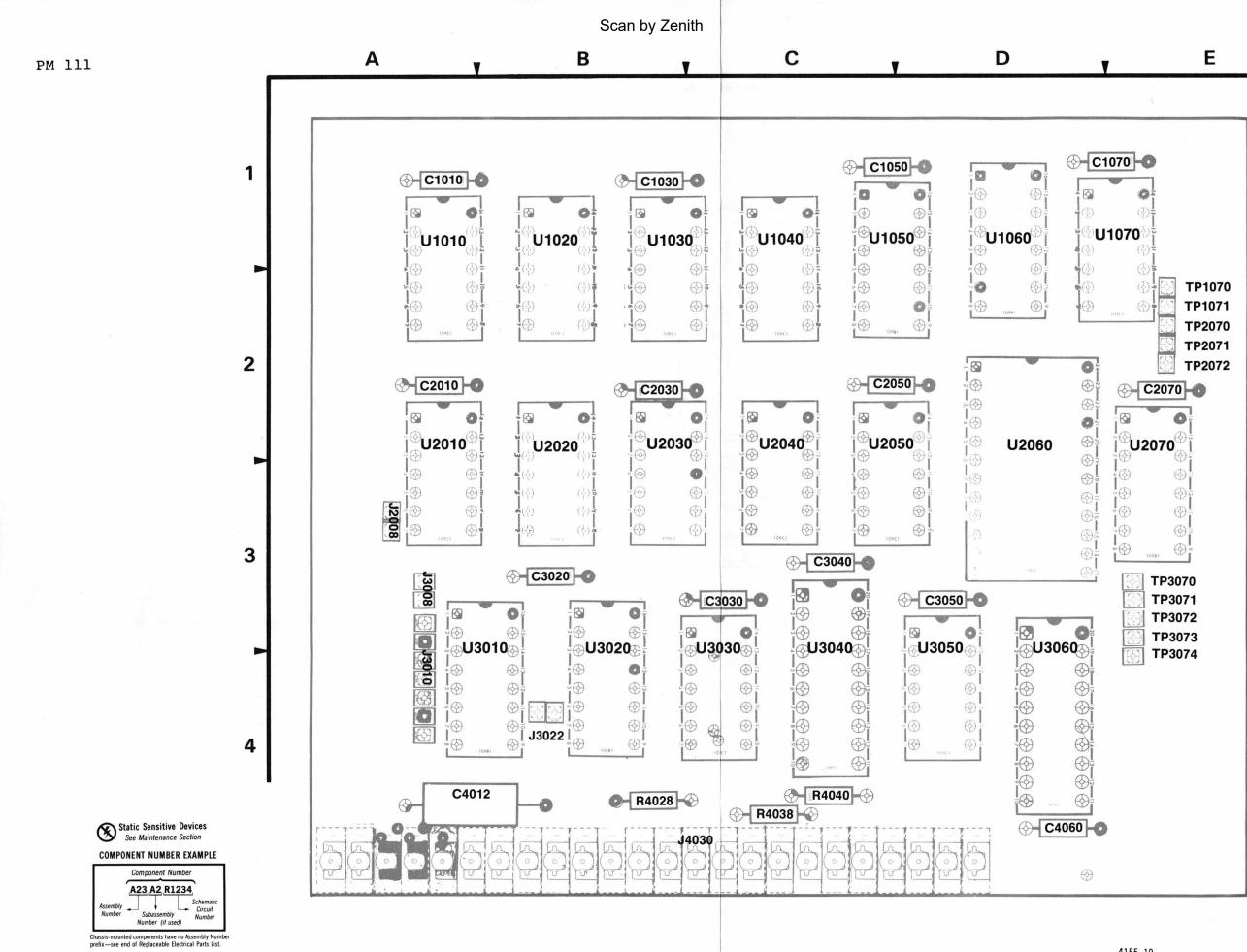

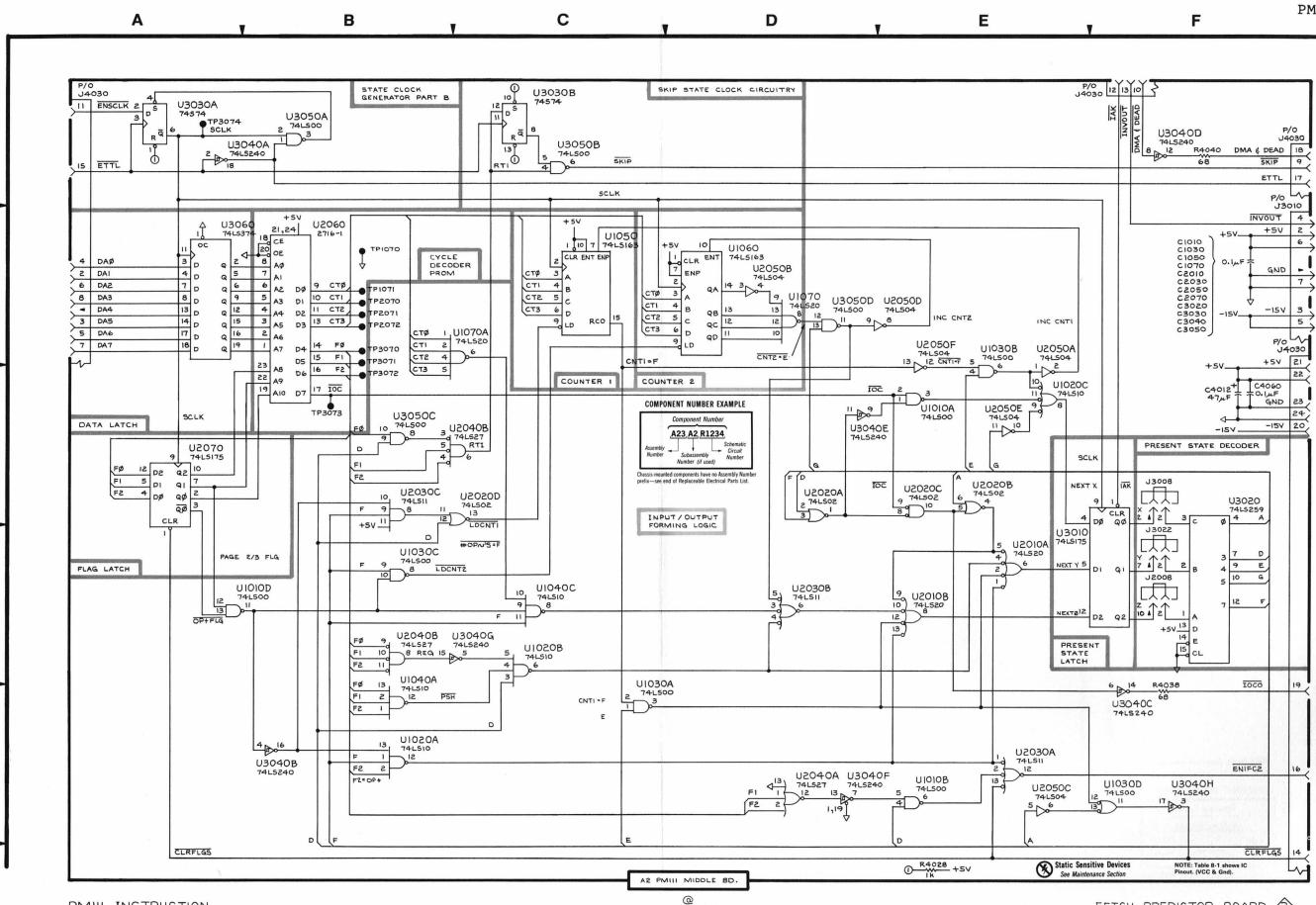

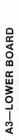

|           | BOARD 1 DETAILED CIRCUITRY DESCRIPTIONS.4-4I/O BUFFERS.4-6FIRMWARE EPROM.4-6INPUT BUFFERS.4-6ECL CLOCK COMPARATOR.4-7ECL TO TTL CLOCK CONVERTER.4-7DMA+DEAD CYCLE DETECTOR.4-7INTERRUPT ACKNOWLEDGE DETECTOR.4-7INTERRUPT LOGIC.4-8VMA DETECTOR.4-7STATE CLOCK GENERATOR PART A.4-10(HALT). (DMA/BREQ) CIRCUIT.4-10CLOCK OSCILLATOR BUFFER.4-11BOARD 2 DETAILED CIRCUIT DESCRIPTIONS.4-13FETCH PREDICTOR OPERATION.4-13Fetch Predictor Flow Chart4-14Regular Instructions.4-17Regular Instructions.4-17Page 2 or Page 3 Instructions.4-18PUL Instruction.4-18STATE CLOCK GENERATOR PART B.4-18PUL Instruction.4-18STATE CLOCK GENERATOR PART B.4-19COUNTER 1 AND COUNTER 2.4-20STATE CLOCK CIRCUITRY.4-20RTI DECODER.4-21PRESENT STATE DECODER.4-22INPUT/OUTPUT FORMING LOGIC.4-22BOARD 3 DETAILED CIRCUIT DESCRIPTIONS.4-21PRESENT STATE DECODER.4-22SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25SELF-TEST OSCILLATOR.4-25 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | CYCLE GENERATOR PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Section 5 | PERFORMANCE CHECK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PRELIMINARY SETUP. 5-3<br>DIAGNOSTIC MONITOR, PART 1. 5-5<br>OVERVIEW. 5-5<br>DIAGNOSTIC MODULE 9 (PER.MODSYS). 5-6<br>DIAGNOSTIC MODULE B (TIMING OPTION). 5-6<br>DIAGNOSTIC MONITOR, PART 2. 5-7<br>SELF-TEST ACQUISITION CHECK. 5-7<br>CONTROL LINE CHECK. 5-13<br>CLOCK QUALIFICATION CHECK. 5-14<br>PERFORMANCE CHECKS, PART 3. 5-15<br>OVERVIEW. 5-15<br>TEST 1. SETUP AND HOLD TIMES (DI0-DI7). 5-15<br>TEST 2. TIMING OPTION SETUP AND HOLD TIMES. 5-21<br>TEST 3. TEST CLOCK PERIOD. 5-26<br>TEST 4. TEST CLOCK PULSE WIDTH. 5-26<br>TEST 5. CLOCK E PERIOD. 5-26 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST 7. /PHALT DELAY (from 40-pin plug to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| microprocessor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AAINTENANCE AND TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

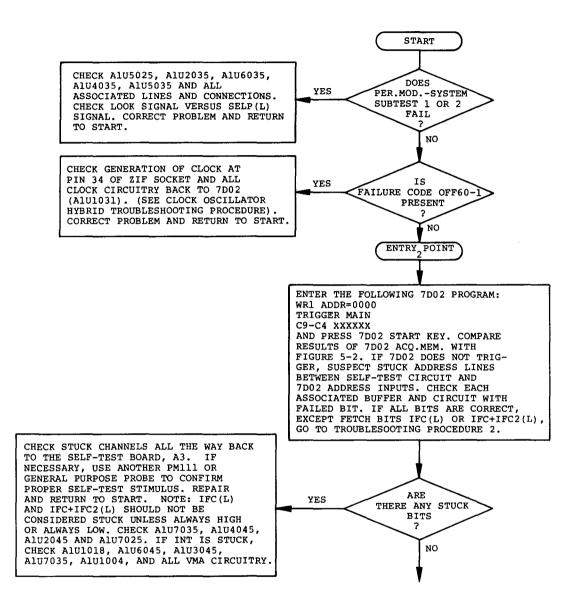

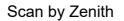

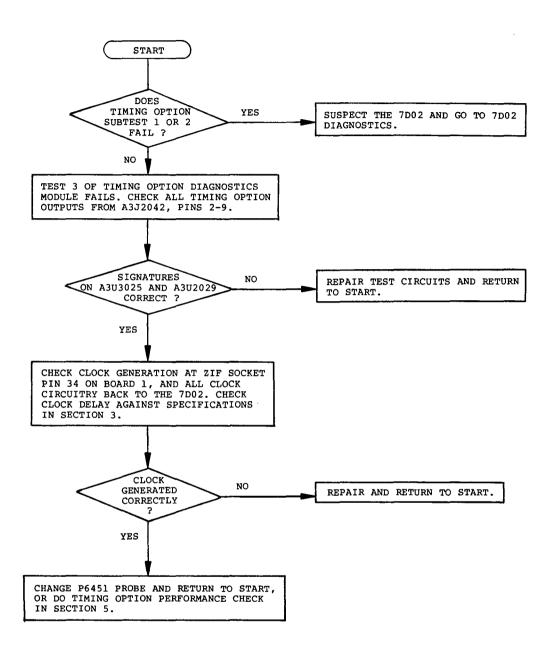

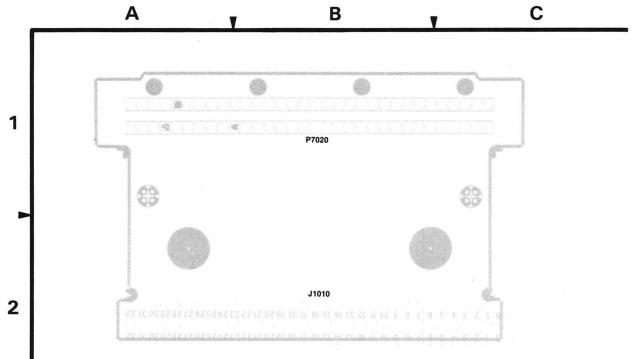

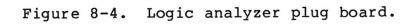

| MAINTENANCE6-1REPAIR6-1OBTAINING REPLACEMENT PARTS6-1ORDERING PARTS6-1CLEANING INSTRUCTIONS6-1Exterior6-2Interior6-2PERSONALITY MODULE DISASSEMBLY6-2LOGIC ANALYZER PLUG DISASSEMBLY6-4MICROPROCESSOR PLUG DISASSEMBLY6-4TROUBLESHOOTING6-6OVERVIEW6-6SUBSTITUTION METHOD6-6Diagnostic Module 9 PER. MODSYSTEM6-6Subtest 16-7Subtest 36-7Subtest 46-8Subtest 76-9Diagnostic Module B TIMING OPTION6-11Subtest 36-11PERFORMANCE CHECKS6-12                                                                                                                                  |

| PERFORMANCE CHECKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Section 6 M

6

F

# PM 111

| )       |    | Troubleshooting With Signature Analysis6-22<br>Preliminary Setup6-22<br>Signature Tables6-24 |

|---------|----|----------------------------------------------------------------------------------------------|

| Section | 7  | REPLACEABLE ELECTRICAL PARTS                                                                 |

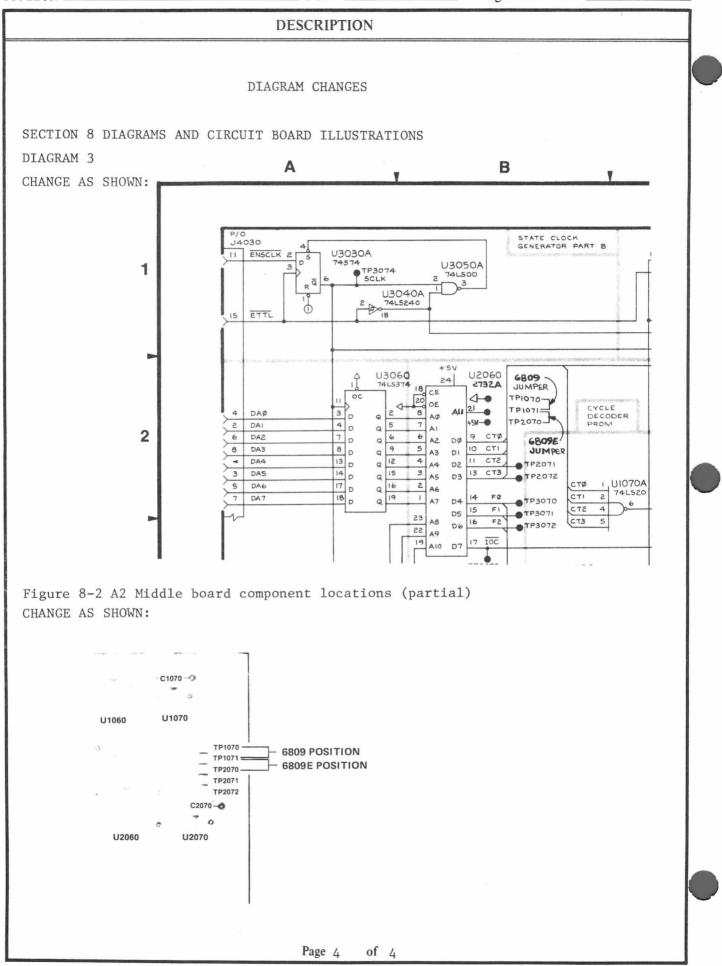

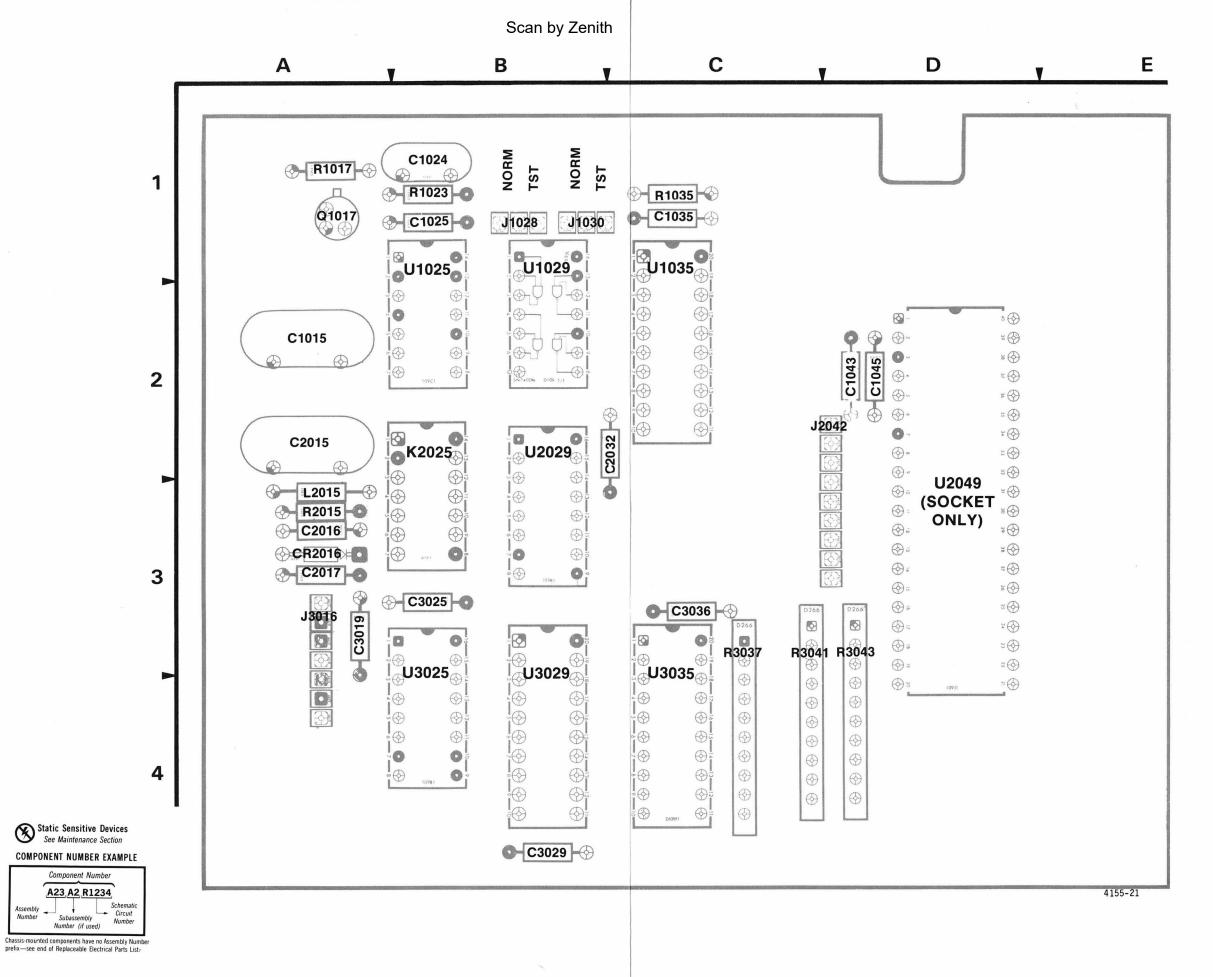

| Section | 8  | CIRCUIT BOARD DIAGRAMS AND ILLUSTRATIONS                                                     |

| Section | 9  | REPLACEABLE MECHANICAL PARTS                                                                 |

| Section | 10 | SIGNAL GLOSSARY10-1                                                                          |

ľ

## LIST OF ILLUSTRATIONS

|        |       | ersonality Module for 6809/6809E x                                              |

|--------|-------|---------------------------------------------------------------------------------|

| Figure | 2-1.  | Default state clock generation2-8                                               |

| Figure | 4-1.  | Overview block diagram4-1                                                       |

| Figure | 4-2.  | Board Al block diagram4-5                                                       |

| Figure | 4-3.  | Board A2 block diagram4-12                                                      |

| Figure | 4-4.  | 6809 fetch predictor state machine flow chart4-16                               |

| Figure | 4-5.  | Skip SCLK on RTI4-21                                                            |

| Figure | 4-6.  | End of SWI instruction; showing synchronizing on IAK and generating a fetch4-23 |

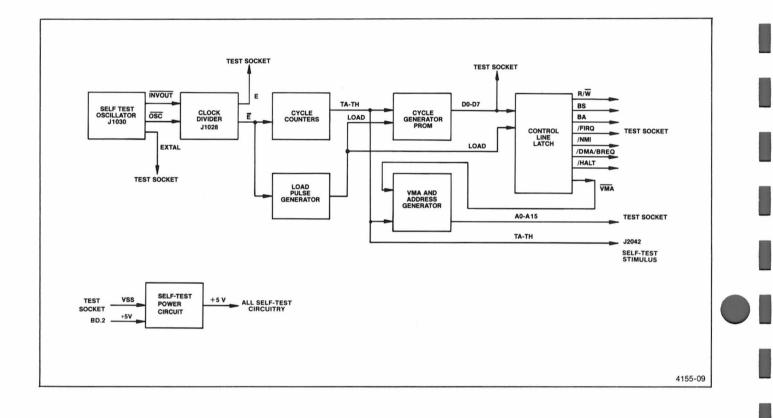

| Figure | 4-7.  | Board A3 block diagram4-24                                                      |

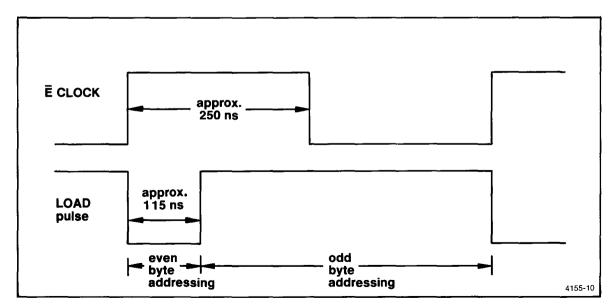

| Figure | 4-8.  | Load Pulse Generator4-28                                                        |

| Figure | 5-1.  | PM lll in the self-test configuration5-4                                        |

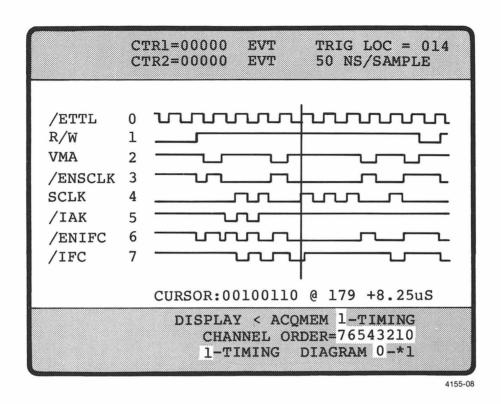

| Figure | 5-2.  | Self test acquisition5-13                                                       |

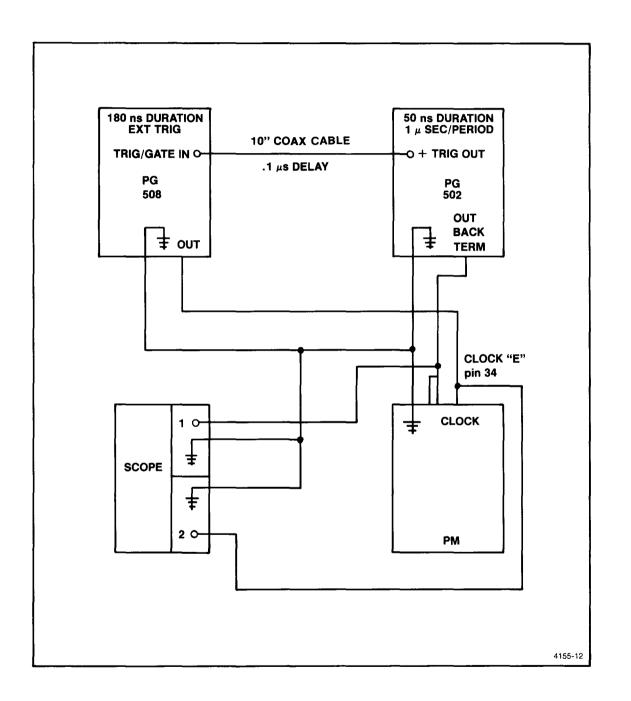

| Figure | 5-3.  | Setup and hold time test setup5-16                                              |

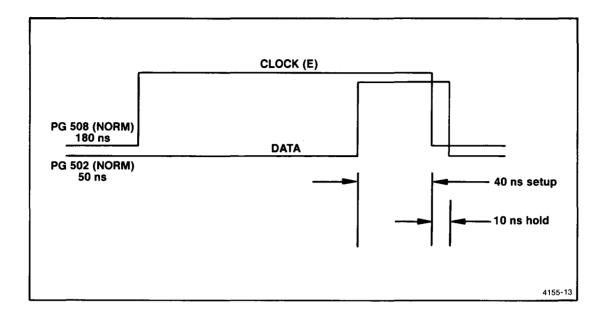

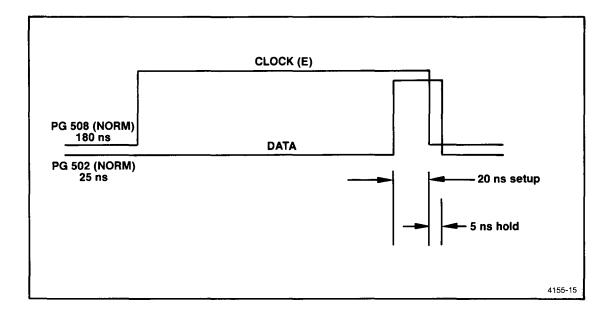

| Figure | 5-4A. | Data lines DI0-DI7 setup and hold (normal)5-20                                  |

| Figure | 5-4B. | Data lines DI0-DI7 setup and hold (complemented).5-20                           |

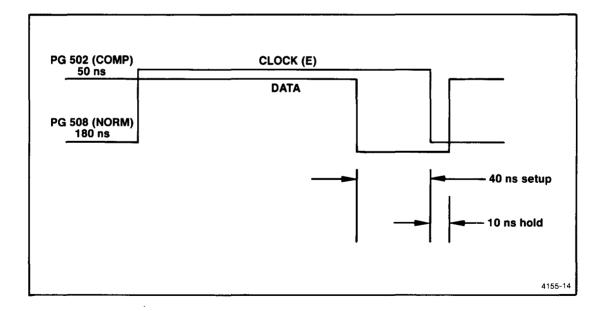

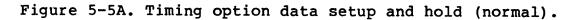

| Figure | 5-5A. | Timing option data setup and hold (normal)5-23                                  |

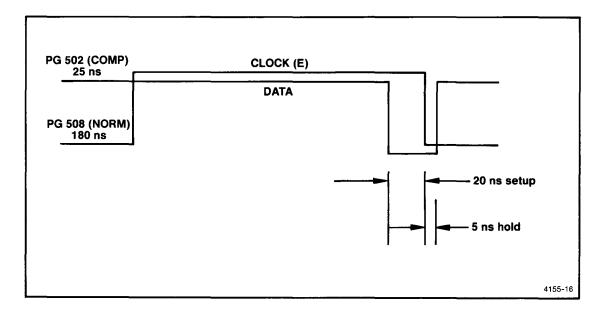

| Figure | 5-5B. | Timing option data setup and hold (complemented).5-23                           |

| Figure | 5-6.  | HALT (L) delay from 40-pin plug<br>to microprocessor5-28                        |

| Figure | 6-1.  | Board layout of disassembled PM lll<br>Personality Module6-4                    |

vi

## LIST OF TABLES

ŀ

|            | Page                                    |

|------------|-----------------------------------------|

| Table 2-1. | CONTROL LINES CO, Cl, AND C22-5         |

| Table 2-2. | RADIX SELECTION2-12                     |

| Table 2-3. | PM 111 CONTROL LINES2-22                |

| Table 3-1. | PM 111 CHARACTERISTICS                  |

| Table 3-2. | PM 111 QUALIFIERS                       |

| Table 3-3. | ELECTRICAL SPECIFICATIONS               |

| Table 3-4. | MECHANICAL SPECIFICATIONS               |

| Table 3-5. | ENVIRONMENTAL SPECIFICATIONS            |

| Table 3-6. | PM 111 LOGIC ANALYZER CABLE             |

| Table 3-7. | MICROPROCESSOR PLUG                     |

| Table 4-1. | PROCESSOR STATE INDICATOR TABLE4-8      |

| Table 4-2. | NUMBER OF BYTES DECODED PER OPCODE4-14  |

| Table 4-3. | CYCLE DECODER PROM FLAG DEFINITIONS4-20 |

| Table 5-1. | REQUIRED TEST EQUIPMENT                 |

| Table 5-2. | OPTIONAL TEST EQUIPMENT                 |

| Table 5-3. | P6451 TIMING OPTION CONNECTION5-5       |

| Table 5-4. | TEST TABLE                              |

| Table 5-5. | P6451 TIMING OPTION WIRES               |

| Table 6-1. | PM 111 JUMPER PLUGS AND TEST POINTS6-14 |

| Table 6-2. | PM 111 TROUBLESHOOTING ERROR LIST       |

| Table 6-3. | TROUBLESHOOTING PROCEDURES              |

| Table 6-4. | PM 111 SIGNATURE TABLE                  |

#### OPERATOR'S SAFETY SUMMARY

The general safety information in this part of the summary is for both operating and service personnel. Specific warnings and cautions will be found throughout the manual where they apply, but may not appear in this summary.

#### Terms in This Manual

CAUTION statements identify conditions or practices that could result in damage to the equipment or to other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### Terms As Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

Symbols in This Manual

This symbol indicates where applicable cautionary or other information is to be found.

Symbols As Marked on Equipment

$\angle \$  Attention - refer to manual.

#### Grounding the Product

This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle before connecting the product input or output terminals. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

PM 111

#### Danger Arising From Loss of Ground

Upon loss of the protective-ground connection, all accesible conductive parts (including knobs and controls that may appear to be insulating) can render an electric shock.

#### Do Not Operate in Explosive Atmosperes

To avoid explosion, do not operate this product in an explosive atmospere unless it has been certified for such operation.

#### Do Not Operate Without Covers

To avoid personal injury, do not operate this product without covers or panels installed. Do not apply power to the plug-in via a plug-in extender.

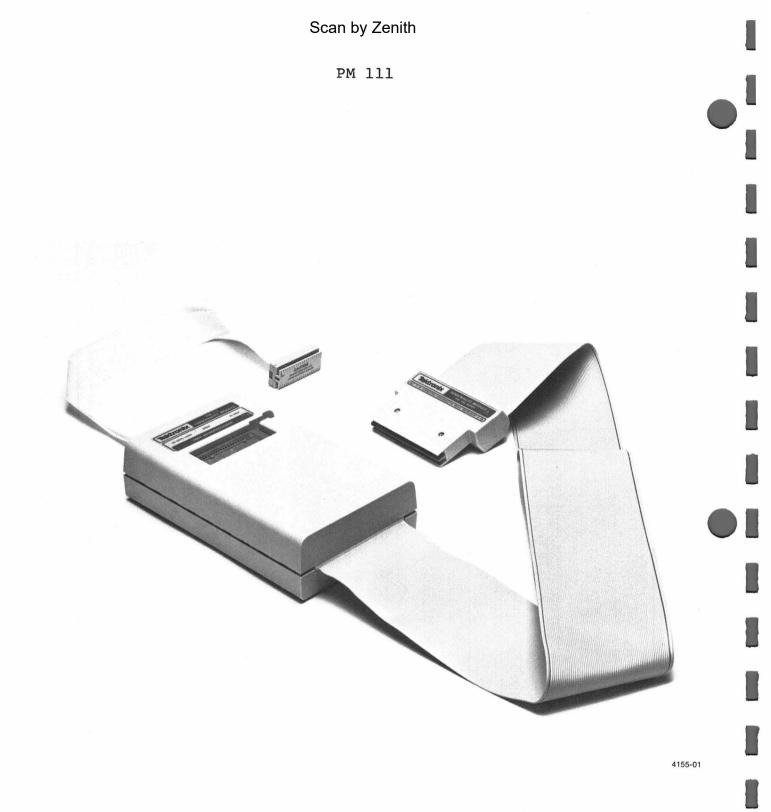

The PM 111 Personality Module for 6809/6809E microprocessors.

@

Scan by Zenith Section 1-PM 111

#### INTRODUCTION

#### OVERVIEW

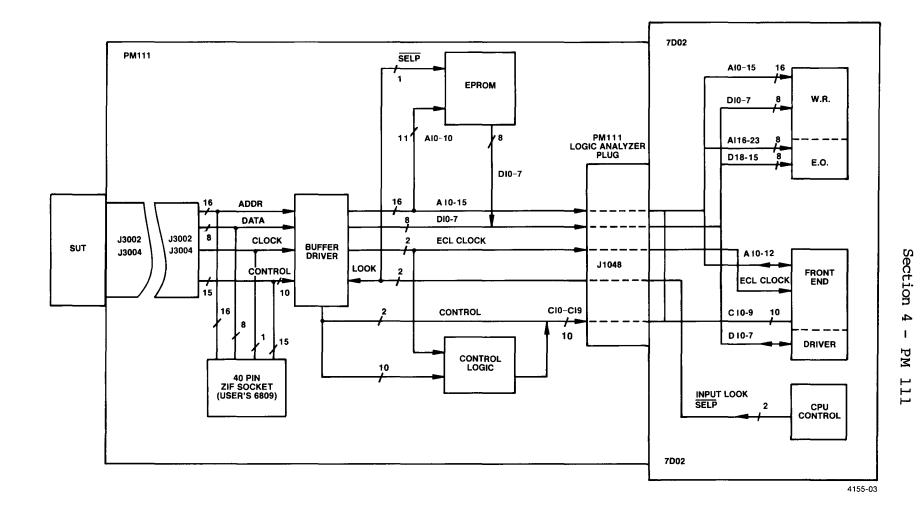

The PM 111 Personality Module personalizes the logic analyzer for use with MC6809/MC6809E microprocessors. The personality module contains firmware which modifies the display and diagnostics of the logic analyzer for use with the microprocessor. This firmware also allows the logic analyzer to disassemble the information it receives into the mnemonics of that microprocessor.

The microprocessor is removed from the system under test (SUT) and installed in the zero insertion force (ZIF) socket of the PM 111. The microprocessor plug from the PM 111 is then plugged into the socket of the SUT. As the personality module passively monitors the system under test, it does not interfere with the normal operation of the microprocessor. It does, however, collect and transfer data to the logic analyzer in a standard format that the logic analyzer can interpret.

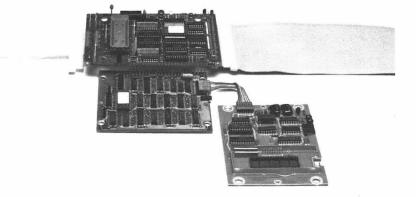

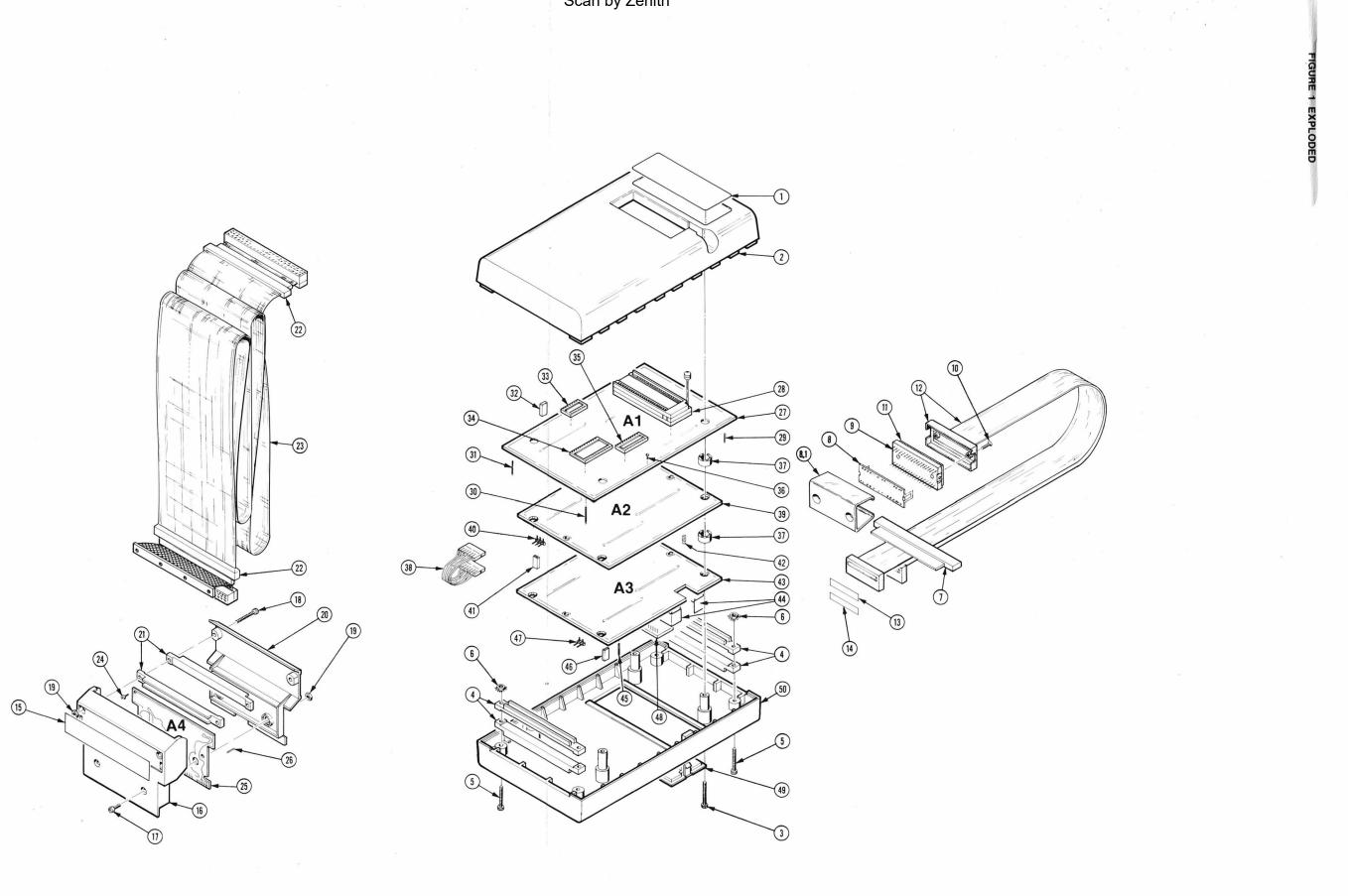

Physically, the PM 111 Personality Module consists of a pod containing three circuit boards. A four foot ribbon cable with a 64-pin connector serves as the interface to the logic analyzer, while a pair of 26 line ribbon cables with a 40-pin plug interfaces the PM 111 to the system under test. A ZIF socket, located on the top side of the module, receives the microprocessor itself. A 40-pin test socket, located on the bottom of the module, receives the PM 111 40-pin plug during the self-test mode of operation.

#### ABOUT THIS MANUAL

This manual describes the operation and servicing of the PM 111 Personality Module. The operator's portion of this manual provides an overview of the personality module, connection and operating instructions, and specifications associated with the personality module. The service portion of the manual is found after the colored divider page. It contains detailed circuit descriptions, schematics, performance check procedures, maintenance and troubleshooting information, electrical and mechanical replaceable parts lists, and a signal glossary. Refer to the Table of Contents for the specific locations of information.

#### Scan by Zenith INTRODUCTION-PM 111

To better understand the operation of the PM lll Personality Module, the operator should be familiar with the operation of the Motorola MC6809 or MC6809E series of microprocessors. The reader should be familiar with the following reference material.

"MC6809 Advance Information", Motorola Inc., 1980

"MC6809E Advance Information", Motorola Inc., 1980

"MC6809-MC6809E Programming Manual", Motorola Inc., 1981

7D02 Logic Analyzer Service Manual, Tektronix Inc., P/N 070-2919-00

7D02 Logic Analyzer Operator's Manual, Tektronix Inc., P/N 070-2918-00

The PM 111 Personality Module supports the following microprocessors:

MC6809 (l.0 MHz) MC68A09 (l.5 MHz) MC68B09 (2.0 MHz)

With minimal configuration changes, the PM lll will also support the following microprocessors:

MC6809E (1.0 MHz) MC68A09E (1.5 MHz) MC68B09E (2.0 MHz)

#### CONVENTIONS USED IN THIS MANUAL

The following provides a list of the conventions used throughout this manual.

• Whenever a reference is made to the PM 111, the information should be considered true for all versions of the MC6809 and MC6809E microprocessors, unless otherwise noted. Special considerations of the 6809E series of microprocessors are referenced in the Table of Contents, located at the front of this manual.

1-2

#### INTRODUCTION-PM 111

- A bar () over a signal name, or a portion of a signal name in the schematics, indicates that the signal is active when in the low state. For example, HALT indicates that HALT is an active low signal. R/W indicates that l=Read, 0=Write.

- An (H) or (L) following a signal name indicates that the signal is active in the high or low state. For example, LOOK(H) indicates that LOOK is an active high signal. SELP(L) indicates that SELP is an active low signal. The absence of an (L) after a signal name implies active high (H).

- A slash (/) before a signal name or portion of a signal name in the simulated screen displays, indicates that the signal name appears that way on the 7D02 screen. For example, R/W is the same as R/W for schematics and R/W(L) for the text.

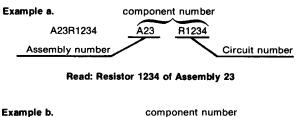

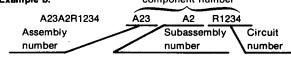

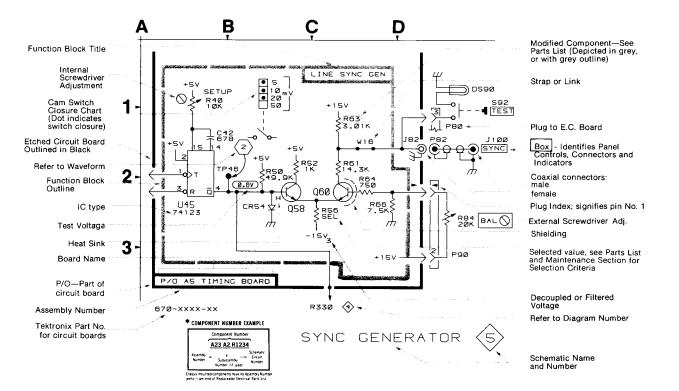

- Component numbers are composed of an assembly number and a schematic circuit number. For example, AlU1031 indicates that component U1031 is located on assembly Al (board 1) of the personality module.

- A convention of minimizing lengthy parts references is used in this this manual. For example, the reference AlU3045, AlU4045, and AlU5045 representing components on assembly Al (board 1) may be referenced as AlU's 3045, 4045, and 5045.

- The following board-related terms should be considered synonymous:

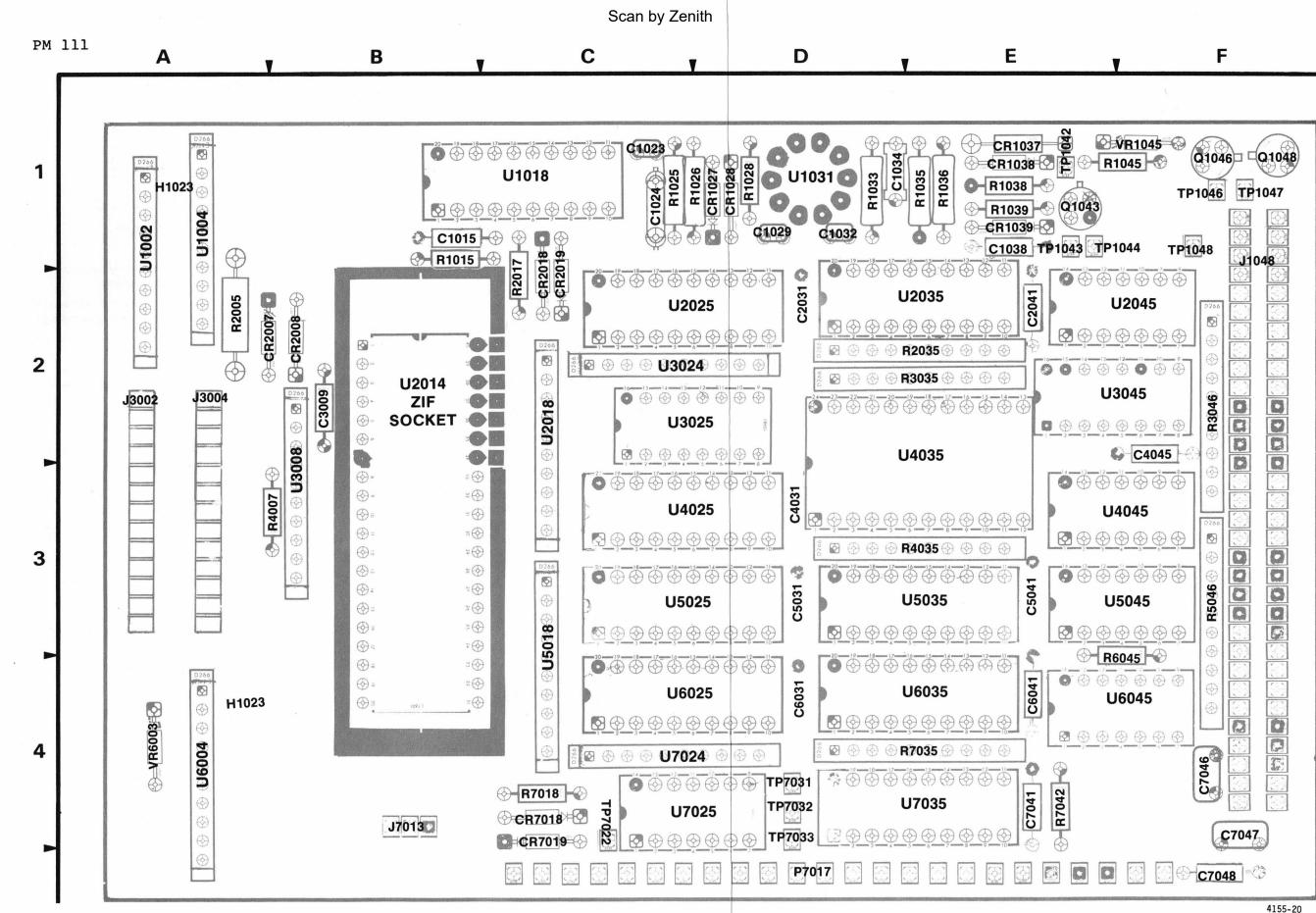

upper - top - Buffer Board - Assembly Al middle - Fetch Predictor Board - Assembly A2 lower - bottom - Self-Test Board - Assembly A3

#### Section 2-PM 111

#### OPERATING THE PM 111 PERSONALITY MODULE

#### OVERVIEW

This section of the manual provides information concerning the operation of the PM 111 Personality Module.

#### MODES OF OPERATION

The PM 111 has two basic modes of operation. The first is the normal mode of operation where the personality module acts as a passive bus monitor, collecting data and then transferring it to the logic analyzer. The second is a self-test mode that is used to verify the correct operation of the personality module. Refer to the Theory of Operation and the Maintenance and Troubleshooting sections for more information.

#### CONNECTION INSTRUCTIONS

CONNECTING THE PM 111 TO THE LOGIC ANALYZER

# CAUTION

Always be certain to turn OFF the mainframe (logic analyzer) power before connecting or disconnecting any personality module. Failure to take this precaution may result in permanent damage to the logic analyzer, the personality module, or the system under test.

Turn off the mainframe power and insert the ribbon cable connector labeled PERSONALITY MODULE - PM 100 SERIES into the receptacle on the logic analyzer labeled with the same name.

CONNECTING THE PM 111 TO THE 6809 SYSTEM UNDER TEST (SUT)

- 1. Turn off the power to the logic analyzer and the SUT.

- 2. Ground yourself to drain static electricity.

#### OPERATION-PM 111

# CAUTION

Always be certain to turn off the power to any instrument before removing the microprocessor and installing it in the zero insertion force (ZIF) socket of the personality module.

Static input protection has been provided on all zero insertion force (ZIF) socket pins except pin 7. This same protection exists on the 40-pin test socket except for pins 7, 38, and 39.

- 3. Remove the 6809 microprocessor from the SUT and install it in the ZIF socket of the personality module. If using the 6809E microprocessor, the microprocessor remains in the SUT (refer to the PM 111 connection to the 6809E system under test). Be sure to install it properly, keeping pin 1 of the microprocessor toward the lever of the ZIF socket.

- 4. Plug the personality module 40-pin plug into the SUT socket where the microprocessor was removed. Make certain that pin 1 of the 40-pin plug goes to pin 1 of the SUT socket. Pin 1 of the 40-pin plug is marked with a notch and an arrow.

- 5. Turn on the power to the logic analyzer and the SUT, and reset the SUT.

#### CONNECTING THE PM 111 TO THE 6809E SYSTEM UNDER TEST

Six pins on the 6809E series differ from the 6809. In order to accomodate these changes, pins 38 and 39 of the microprocessor must be disconnected from the PM 111. The recommended procedure is as follows:

- Clip pins 38 and 39 off a 40-pin dip socket (Tektronix P/N 136-0623-00).

- Insert this socket into a female adapter (Tektronix P/N 380-0647-00).

- 3. Connect the female adapter to the 10 cm 40-pin low profile dip clip adapter (Tektronix P/N 015-0339-00).

- 4. Clip the low profile dip clip over the 6809E (the 6809E remains installed in the system under test). Check to ensure that pin 1 of the dip clip is matched to pin 1 of the SUT.

2-2

#### OPERATION-PM 111

#### POWER SOURCE

Since the PM 111 operates only as a part of the logic analyzer system, all operating voltages and currents are furnished by the logic analyzer to which the PM 111 is connected.

#### STORING THE PM 111 PERSONALITY MODULE

Keep the personality module in a clean area where the temperature remains between -62 and +85 degrees C. Care should be taken when flexing the PM 111 cables between -62 and -15 degrees C. Humidity should not exceed 95%, non-condensing. The personality module should not be taken above 50,000 feet.

#### PROGRAMMING THE 7D02

The following 7D02 screen displays contain elements inherent to only the PM 111 Personality Module. For additional information about signal lines, refer to the Theory of Operation section, the Signal Glossary section, and the Additional Information found at the end of this section.

#### THE WORD RECOGNIZER

When the PM 111 is attached to the logic analyzer, the 7D02 WD RECOGNIZER key will produce the following display. The address and data buses have their default radices of hex. The radices of these fields may be changed to octal or binary by use of the 7D02 FORMAT key. All other fields are permanently set to binary.

TEST 1 1IF 1 WORD RECOGNIZER # 1 1 DATA=XX 1 ADDRESS=XXXX 1 FETCH1=X FETCH1+2=X R/W=X BA=X 1 INT=X INVAL.OP=X EXT.TRIG.IN=X 1 TIMING WR=X 1THEN DO 1

#### OPERATION-PM 111

#### DATA Field

The 8-bit data bus, which defaults to hexadecimal radix values, may also be displayed in octal or binary. When the START key is pressed, the logic analyzer stores the information from the data bus. It is possible to setup the Word Recognizer to recognize a specified data bus value by entering a value in the DATA field and setting all other fields to "don't care" conditions.

#### ADDRESS Field

The 16-bit address bus, which defaults to hexadecimal values, may also be displayed in octal or binary. When the START key is pressed, the logic analyzer stores the information from the address bus. It is possible to set up the Word Recognizer to recognize a specified address bus value by entering a value in the ADDRESS field and setting all other fields to "don't care" conditions.

#### FETCH1 Field

The FETCH1 field uses a binary radix. FETCH1=1 only on Fetch-1 cycles. A Fetch-1 cycle is a cycle on which the first byte (opcode) of an instruction is read from memory for execution.

The FETCH1 line is the Cl control line IFC(L). The FETCH1 information is stored in the logic analyzer acquisition memory.

#### FETCH1+2 Field

The FETCH1+2 field uses a binary radix. FETCH1+2=1 on either a Fetch-1 cycle (see FETCH1) or a Fetch-2 cycle. When FETCH1=1, then FETCH1+2=1. On a "Page 2" or a "Page 3" instruction ( i.e., one whose first byte is 10H or 11H, respectively) two bytes are required to uniquely identify the opcode. A Fetch-2 cycle is a cycle on which the second byte of a 2-byte opcode is read from memory for execution. A Fetch-2 cycle is also any cycle on which the postbyte of one of the following instructions is read: TFR, EXG, PSHS, PSHU, PULS, PULU, or any indexed instruction. An indexed Page 2 or Page 3 instruction will have two Fetch-2 cycles.

The FETCH1+2 line is the C2 control line IFC+IFC2(L). The FETCH2 information is stored in the logic analyzer acquisition memory.

## Scan by Zenith OPERATION-PM 111

#### R/W Field

The R/W (Read/Write) field uses the binary radix. R/W(L)=1 on memory reads and R/W(L)=0 on memory writes. The R/W(L) line will appear high (a Read) on any fetch cycle.

The R/W(L) line is the CO control line. This is the 6809 R/W(L) line that is stored in the logic analyzer acquistion memory.

The following Table 2-1 describes the relationship between the CO, Cl, and C2 control lines.

| C2<br>FETCH1+2 | Cl<br>FETCH1 | CO<br>R/W | CYCLE<br>TYPE |

|----------------|--------------|-----------|---------------|

| 0              | 0            | 0         | MEMORY WRITE  |

| 0              | 0            | 1         | MEMORY READ   |

| 0              | 1            | x         | ILLEGAL STATE |

| 1              | x            | 0         | ILLEGAL STATE |

| 1              | 0            | 1         | FETCH-2       |

| 1              | 1            | l ī       | FETCH-1       |

Table 2-1 CONTROL LINES C0, C1, AND C2

#### **BA Field**

The BA (Bus Available) field uses the binary radix. BA=1 on Halt, Bus Grant, and SYNC Acknowledge cycles, as well as the "Dead" cycle preceding a bus exchange. BA=0 on all other cycles such as Normal (running), Interrupt Acknowledge, and Reset Acknowledge cycles.

#### NOTE

Under default clock qualification, BA will always be low (BA=0). A user wishing to see all values of BA will have to turn off the clock qualifier C8 (i.e., set C8=X).

The BA line is the C4 control line. This is the 6809 BA line. It is not stored in the logic analyzer acquisition memory.

#### OPERATION-PM 111

#### INT Field

The INT (Interrupt Request) field uses the binary radix. The INT signal equals 1 whenever one or more of the 6809 interrupt lines NMI(L), IRQ(L), or FIRQ(L) is asserted.

The INT line is the C3 control line. This line is generated by the PM lll hardware and is stored in the logic analyzer acquisition memory.

#### INVAL.OP Field

The INVAL.OP (Invalid Opcode) field uses the binary radix. An invalid opcode is defined as one of the following:

- A Fetch-1 on which the data bus does not contain a valid opcode.

- A Fetch-2 for a Page-2 or Page-3 instruction on which the data bus does not contain a valid second opcode byte.

- An invalid postbyte (Fetch-2) for an indexed instruction.

#### NOTE

An illegal opcode will unsynchronize the fetch predictor. Any acquisition done after an illegal opcode may contain mislabeled cycles. An Interrupt Acknowledge cycle will re-synchronize the fetch predictor.

The INVAL.OP line, IOCO(L), is the C5 control line. The C5 control line is not stored by the logic analyzer acquisition memory.

#### EXT.TRIG.IN Field

The EXT.TRIG.IN (External Trigger In) field uses the binary radix. This is the External Trigger In signal from the logic analyzer front panel BNC connector. The EXT.TRIG.IN signal is not stored by the logic analyzer acquisition memory.

#### TIMING WR Field

The TIMING WR field will only be found in the Word Recognizer if the Timing Option (Option 02) is installed in the 7D02.

#### OPERATION-PM 111

#### CLOCK QUALIFICATION

When the TRIGGER key is pressed, the logic analyzer provides the user with the following screen display format.

- 1 TRIGGER 0-MAIN

- 1 O-MAIN

- 1 1-TIMING

- 1 0-BEFORE DATA

- 1 0-SYSTEM UNDER TEST CONT.

- 1 0-STANDARD CLOCK QUAL.

The last menu is of specific interest to the PM lll user. When the cursor is placed on the 0-STANDARD CLOCK QUAL. box, the following display appears:

- 1 0-STANDARD CLOCK QUAL.

- 1 0 STANDARD CLOCK QUAL.

- 1 1 USER CLOCK QUAL.

If the 1 USER CLOCK QUAL. element is selected, the following display will appear:

1 1-USER CLOCK QUAL.

1

1

- 1 1-FALLING EDGE OF CLOCK

- 0 RISING EDGE OF CLOCK

- 1 FALLING EDGE OF CLOCK

- 1 C9-C4 (ANDED CLOCKS) = X0X0XX

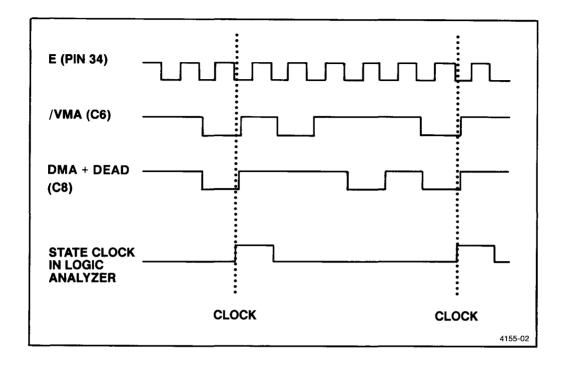

Notice the default values of 0 given to C8 and C6 in the ANDED CLOCKS field. This is the default clock qualification setup used by the PM 111. If all of the control lines are set to X's ("don't cares"), the 7D02 will use all E clock cycles but with the default clock qualification setup, the 7D02 clocks only when:

- Clock E (pin 34) is on the falling edge, and

- C8 (much like BA) is in the low state indicating the 6809 has control of the bus and is not in a DMA or Dead cycle, and

- C6 (VMA)(L) is in the low state indicating a valid address is present on the bus.

Refer to Figure 2-1 for an example of default state clock generation. Scan by Zenith OPERATION-PM 111

Figure 2-1. Default state clock generation.

The control lines C9-C4 are PM lll control lines that may be used to re-define the state clock. The selected state is ANDED with the selected state of the clock E. If both states are true, a clock is generated.

The following example shows a redefined state clock:

1 C9-C4 (ANDED CLOCKS) = XXX0XX

where C8 has been changed to X (don't care). In this example, the clock qualifier has been set to qualify on all 6809 cycles, except invalid memory address cycles.

Another example shows further redefining:

1 C9-C4 (ANDED CLOCKS)=X1X0XX

where C8 has been changed to 1. In this example, the clock qualifier has been set to qualify only on valid DMA, Dead, Halt or Sync Acknowledge cycles.

2-8

#### Scan by Zenith OPERATION-PM 111

#### NOTE

In most cases, the operator will not need to redefine the state clock. This procedure may produce unpredictable results.

If the TRIGGER-MAIN command is deleted from the program, the values last entered in the USER CLOCK QUAL. field will be retained. All fields will return to their power-up conditions when the logic analyzer is powered down, then powered back up again.

The following is a description of the clock qualification control lines:

C9

This qualifier is not used by the PM 111. C9 is always high and the user should never qualify on C9=0 (no clocks will be generated and the 7D02 will be effectively disabled).

C8

This line is essetially the same as the C4 control line (discussed later), except that (when C8=1) it qualifies all Dead cycles, not just the ones on which BA=1. The Dead cycles of the 6809/6809E usually come in pairs, one before and one after every bus exchange. The former comes when BA goes from 0 to 1, and the latter on the cycle after BA goes from 1 to 0. Refer to the MC6809 Advance Information for more explanation.

#### C7

C7=0 will qualify all cycles on which either the 6809 HALT(L) or DMA/BREQ(L) is asserted. Both these lines indicate requests from external sources; however, since the DMA/BREQ(L) line must be asserted throughout DMA operations, this line can qualify DMA cycles. The 7D02 monitors the value of this line during data acquisition and displays the message "HALT/DMA" on the top right line of the 7D02 screen whenever C7=0.

#### OPERATION-PM 111

#### NOTE

The 6809E does not have a DMA/BREQ(L) line. When the PM lll is used with a 6809E, C7=HALT(L).

C6

This line is the Valid Memory Address line generated by the PM 111 hardware. C6=1 whenever the 6809 address bus=FFFF, BS=0, and R/W(L)=1 simultaneously. This indicates a cycle on which internal operations are taking place and no valid information is on the 6809 buses. The user will normally want to qualify on C6=0, when valid bus transactions are (usually) taking place. Refer to the "MC6809 Advance Information" and the "MC6809 - MC6809E Microprocessor Programming Manual" for more information.

#### C5

This is the Invalid Opcode line generated by the PM lll hardware. Because this line is asserted the cycle after an invalid opcode is detected, it is useful for triggering but not for clock qualification.

C4

This is the Bus Available line from the 6809. C4=1 qualifies Halt, Bus Grant, and SYNC Acknowledge cycles. It also qualifies the "Dead" cycle preceding a bus exchange. C4=0 qualifies all other cycles, i.e., Normal (running), Interrupt Acknowledge, and Reset Acknowledge cycles. Refer to the "MC6809 Advance Information" for more information.

#### OPERATION-PM 111

#### THE FORMAT MODE DISPLAY

When the PM lll is connected to the logic analyzer and the Timing Option is installed in the 7D02, the 7D02 FORMAT key produces the following display:

TIMING OPTION WORD RECOGNIZER 0-BINARY WORD RECOGNIZER ADDRESS FIELD 2-HEX WORD RECOGNIZER DATA FIELD 2-HEX TIMING OPTION DATA DISPLAY 0-BINARY ADDRESS FIELD DISPLAY 2-HEX DATA FIELD DISPLAY 2-HEX HIGHLIGHT MEMORY DIFFERENCES? 1 - NO**DISPLAY GLITCHES?** 0-YES TIMING OPTION DATA INVERSION DATA=00000000

The PM lll-specific menus are:

The WORD RECOGNIZER ADDRESS FIELD menu sets the radix for the ADDRESS field in the WD RECOGNIZER display. It does not affect the acquired data display.

The WORD RECOGNIZER DATA FIELD menu sets the radix for the DATA field in the WD RECOGNIZER display. It does not affect the acquired data display.

The ADDRESS FIELD DISPLAY sets the radix for the acquired address bus values when displayed in the Absolute display mode.

The DATA FIELD DISPLAY sets the radix for the acquired data bus values when displayed in the Absolute display mode.

The following Table 2-2 lists the possible radix selections for the preceding Format display fields.

#### OPERATION-PM 111

#### Table 2-2 RADIX SELECTION

| FIELD                            | F      | RADICES |     |       |

|----------------------------------|--------|---------|-----|-------|

|                                  | BINARY | OCTAL   | HEX | ASCII |

| TIMING OPTION<br>WORD RECOGNIZER | *      | x       | x   |       |

| WORD RECOGNIZER<br>ADDRESS FIELD | х      | x       | *   |       |

| WORD RECOGNIZER<br>DATA FIELD    | х      | x       | *   |       |

| TIMING OPTION<br>DATA DISPLAY    | *      | x       | x   | x     |

| ADDRESS FIELD DISPLAY            | х      | x       | *   | x     |

| DATA FIELD DISPLAY               | х      | x       | *   | x     |

X = Possible Selection Choice

\* = Power-up Default Radix

#### MNEMONIC DISPLAY OF ACQUIRED DATA

The PM 111 - 7D02 Logic Analyzer produces a mnemonic disassembly display like the following:

| LOC | ADDR | OPE           | RATION |   | INT |

|-----|------|---------------|--------|---|-----|

| 001 | 4047 | $\mathbf{FF}$ | FETCH  | 2 | 0   |

| T   | 494A | $\mathbf{BF}$ | READ   |   | 0   |

| 003 | 494B | 6C            | READ   |   | 0   |

| 004 | 494C | 5D            | READ   |   | 0   |

| 005 | 4048 | TFR           | Α,Β    |   | 0   |

All numeric data, in the mnemonic display, is displayed in the hex radix and the radices may not be changed with the 7D02 FORMAT key. On most Fetch-1 cycles, the data and status fields (under the OPERATION column) are replaced with the disassembled instruction.

Correct disassembly by the firmware is guaranteed when default clock qualification is used. If data qualification is used, it must be such that all fetch cycles are stored (i.e., store on Word Recognizer FETCH1+2=1) for correct disassembly.

# OPERATION-PM 111

| THE HEADER                    |                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| The first line of the         | e mnemonic display will be the following                                                                                                                                                                                          |  |  |  |  |

| header:<br>LOC A              | ADDR OPERATION INT                                                                                                                                                                                                                |  |  |  |  |

| The meanings of the c         | column headers are as follows:                                                                                                                                                                                                    |  |  |  |  |

| (<br>a<br>a                   | is the column that contains a decimal number,<br>0-255, indicating the location in the logic<br>analyzer acquisition memory. In order of<br>acquisition, 000 is the oldest acquired data,<br>and 255 is the newest acquired data. |  |  |  |  |

| v                             | is the column that contains the value that<br>was on the 6809 address bus when this word of<br>data was acquired.                                                                                                                 |  |  |  |  |

|                               | is the column that contains the disassembled<br>6809 instruction (on Fetch-1 cycles), or the<br>value that was on the data bus together with<br>a label identifying the cycle type (on non-<br>Fetch-1 cycles).                   |  |  |  |  |

| :                             | is the column that contains the value of the<br>interrupt that was on control line C3 (INT)<br>when this word of data was acquired.                                                                                               |  |  |  |  |

| DISPLAY OF NON-FETCH-1 CYCLES |                                                                                                                                                                                                                                   |  |  |  |  |

| On non-Fetch-l cycles         | s, a word of data will be displayed as:                                                                                                                                                                                           |  |  |  |  |

| lll aaaa dd                   | ccccccc i                                                                                                                                                                                                                         |  |  |  |  |

| where                         |                                                                                                                                                                                                                                   |  |  |  |  |

|                               | is the acquisition memory location (000-255)<br>of the word of data displayed in this line.<br>The oldest word of data is in location 000,<br>the newest in 255.                                                                  |  |  |  |  |

| aaa                           | is the address bus value.                                                                                                                                                                                                         |  |  |  |  |

#### OPERATION-PM 111

dd is the data bus value.

cccccc

is the cycle type ( i.e., one of the following):

"FETCH 2" (Fetch-2 cycle)

"READ " (memory read cycle)

"WRITE " (memory write cycle)

"????? " (invalid cycle: a combination of control lines that should not occur).

Refer to Table 2-1 for the relationship between these cycle types and the control lines C2-C0.

i

is the value that was on control line C3 when this word of data that acquired. The value will be 1 if an interrupt request was pending, and 0 if there was no interrupt request.

The trigger word will be emphasized by displaying the letter "T" in column 4 and by replacing the memory location under the LOC header column with a horizontal bar.

---Taaaa dd ccccccc i

#### DISPLAY OF FETCH-1 CYCLES

On the first opcode fetch cycle of an instruction, the disassembled mnemonics for the instruction will appear instead of the normal data and status display. The instruction will be displayed in two blank-separated fields: the opcode mnemonic, and the instruction operand(s), if any.

Under default clock qualification, there is one exception. At the beginning of its interrupt processing sequence, the 6809 does a fetch of the first byte of what would have been the next instruction. It then discards this fetch and goes into its register stacking and vectoring. Such discarded Fetch-1 cycles are displayed in the same format as non-Fetch-1 cycles, except that the cycle label is FETCH.

#### OPERATION-PM 111

If the user modifies the clock qualifiers so that DMA cycles are stored, a similar situation will arise whenever a Fetch-1 precedes a DMA sequence. In this case, the instruction actually was executed, but its individual cycles may be strung out through and interleaved with DMA cycles. Correct disassembly is not guaranteed if default clock qualification is not used.

MC6809 instructions consist of one or two opcode bytes and 0-3 additional bytes that describe the operands of the instruction. In case of multiple-byte instructions, the firmware will search ahead in acquisition memory for the additional bytes in order to provide operands for the disassembled instructions. If the needed word is in memory, it will be used to disassemble the instruction and will also appear on its own display line (as hex data) at its location in acquisition memory.

The format of a Fetch-1 display line will be as follows:

lll aaaa mmmm oooooooooooooo i

where "lll", "aaaa", and "i" are previously described and

mmmm

is the opcode mnemonic.

represents the disassembled operand(s), if any.

The trigger word will be emphasized by displaying the letter "T" in column 4 and by replacing the space under the LOC header column with a horizontal bar.

---Taaaa mmmm oooooooooooooo i

## Scan by Zenith OPERATION-PM 111

#### Instruction Opcodes

| The f | following      | opcode | mnemoni         | cs will | be supp | orted: |      |

|-------|----------------|--------|-----------------|---------|---------|--------|------|

| ABX   | BHI            | CMPA   | EXG             | LBPL    | LSL     | PULU   | STX  |

| ADCA  | BITA           | CMPB   | INC             | LBRA    | LSLA    | ROL    | STY  |

| ADCB  | BITB           | CMPD   | INCA            | LBRN    | LSLB    | ROLA   | SUBA |

| ADDA  | $\mathbf{BLE}$ | CMPS   | INCB            | LBSR    | LSR     | ROLB   | SUBB |

| ADDB  | $\mathtt{BLS}$ | CMPU   | JMP             | LBVC    | LSRA    | ROR    | SUBD |

| ADDD  | $\mathtt{BLT}$ | CMPX   | JSR             | LBVS    | LSRB    | RORA   | SWI  |

| ANDA  | BMI            | CMPY   | LBCC            | LDA     | MUL     | RORB   | SWI2 |

| ANDB  | BNE            | COM    | LBCS            | LDB     | NEG     | RTI    | SWI3 |

| ANDCO | BPL            | COMA   | LBEQ            | LDD     | NEGA    | RTS    | SYNC |

| ASR   | BRA            | COMB   | LBGE            | LDS     | NEGB    | SBCA   | TFR  |

| ASRA  | BRN            | CWAI   | LBGT            | LDU     | NOP     | SBCB   | TST  |

| ASRB  | BSR            | DAA    | LBHI            | LDX     | ORA     | SEX    | TSTA |

| BCC   | BVC            | DEC    | LBLE            | LDY     | ORB     | STA    | TSTB |

| BCS   | BVS            | DECA   | LBLS            | LEAS    | ORCC    | STB    |      |

| BEQ   | CLR            | DECB   | $\mathbf{LBLT}$ | LEAU    | PSHS    | STD    |      |

| BGE   | CLRA           | EORA   | LBMI            | LEAX    | PSHU    | STS    |      |

| BGT   | CLRB           | EORB   | LBNE            | LEAY    | PULS    | STU    |      |

The opcode set is essentially that described in the reference material listed in the Introduction section of this manual. However, since the ASL, ASLA, ASLB, BHS, BLO, LBHS, and LBLO mnemonics are redundant to those listed below, they have not been included. The following mnemonics are synonymous with the those just mentioned, and are used instead: LSL, LSLA, LSLB, BCC, BCS, LBCC, and LBCS respectively.

On each Fetch-1 cycle, the 6809 does a prefetch of the next byte of the instruction. Normally the prefetch will be either a Read or a Fetch-2 cycle. If the instruction is only one byte long (e.g., the SYNC instruction), this prefetched byte is discarded by the processor. The PM 111 labels and displays such discarded prefetches as READ cycles. Note that if there is no change in the flow of control, the discarded byte will be refetched and executed on the next Fetch-1 cycle. This time the PM 111 will label it a FETCH1 and it will be disassembled in mnemonic displays.

An illegal opcode during disassembly will be displayed as "\*\*\*\*" and the hex value of the opcode (the value on the data bus) will be displayed in parenthesis in the operand field.

#### EXAMPLE:

| LOC | ADDR | OPERA | TION | INT |

|-----|------|-------|------|-----|

| 133 | 1700 | ****  | (lB) | 0   |

#### OPERATION-PM 111

It takes two bytes to determine the opcode mnemonic for a Page-2 or Page-3 instruction; the first byte (10H or 11H, respectively) will be displayed as an illegal opcode if the second byte (the Fetch-2 cycle) is either invalid or not stored in acqusition memory.

#### Instruction Operands

The manner in which an operand is displayed will depend on the addressing mode used, as follows:

Immediate: **#xx or #xxxx** Direct: @xx Extended: XXXX Extended Indirect: [XXXX] Register (TFR, EXG): r,r Relative/Long Relative: XXXX Push/Pull Instructions: r,r,...,r (up to 7 registers) (if all 8 registers) ALL Indexed: [,i] [?xx,i] [?xxxx,i] [a,i] ,i+ [,i++] ,-i [,--i] [?xx,PCR] [?xxxx,PCR] where x = hex digita = A, B, D (any accumulator register) r = A, B, D, X, Y, S, U, PC, DP, CC (any register [not D on Push/Pull]) i = X, Y, S, U (any index register) ? = optional "-" [] = are optional on indexed operands (presence indicates indirection) Asterisks. The asterisks displayed in the operand field indicate one of the following conditions:

- missing operands (operands that cannot be disassembled because a needed cycle was not stored in the acquisition memory). In general, one "\*" will be displayed for each hex digit or register name that is missing.

- an invalid postbyte for an Indexed instruction. The operand display in this case will always be "\*,\*", as if the post-byte were not in memory at all.

#### Scan by Zenith OPERATION-PM 111

# • an invalid register number in the postbyte of a TFR or EXG instruction. Such a postbyte consists of two 4-bit fields (one for each register number), but only 10 of the 16 possible register numbers are meaningful. One "\*" will be displayed for each invalid register number.

#### NOTE

A TFR or EXG instruction must specify two registers of equal length (8-bit or 16-bit). The PM 111 will display an instruction such as "TFR A,X" even though it is not valid.

#### MNEMONIC DISPLAY EXAMPLE

The following is a portion of a hypothetical display:

| LOC | ADDR | OPEI | RATION       |   | INT |

|-----|------|------|--------------|---|-----|

| 001 | 2662 | TFR  | A,B          |   | 0   |

| 002 | 2623 | 89   | FETCH        | 2 | 0   |

| 7   | 2624 | BEQ  | 269E         |   | 0   |

| 004 | 2625 | 78   | READ         |   | 0   |

| 005 | 269E | PSHS | А            |   | 0   |

| 006 | 269F | 02   | FETCH        | 2 | 0   |

| 007 | 3007 | 77   | WRITE        |   | 0   |

| 008 | 26A0 | ORB  | <b># * *</b> |   | 0   |

Lines 001-002 display the two cycles of a TFR instruction. Line 002 is the postbyte containing the 2 register numbers used to disassemble the "A,B" operands in line 001.

Line 003 is the trigger word. Lines 003-004 display the 2 cycles of a BEQ. Note that the 8-bit displacement (line 004) is used to produce a 16-bit absolute address in the disassembly (line 003).

Lines 005-007 show a PSHS of the 8-bit register A. Line 006 is the register mask from which the operand "A" was disassembled. Line 007 is the actual write of the contents of A to the stack.

Line 008 is the last word in acquisition memory. The instruction is an OR immediate to register B. The operand cannot be disassembled because the cycle on which the immediate data was read was not stored in memory.

#### OPERATION-PM 111

#### ABSOLUTE DISPLAY OF ACQUIRED DATA

The PM 111-7D02 Logic Analyzer produces an absolute display like the following:

| LOC | ADDRESS | DATA | I  |

|-----|---------|------|----|

| 001 | 4047    | FF   | FO |

| T   | 494A    | BF   | R0 |

| 003 | 494B    | 6C   | R0 |

| 004 | 494C    | 5D   | R0 |

In absolute data display mode, the radices in which the data and address buses are displayed are individually selectable as binary, octal, hex, or ASCII. The default for each is hex.

#### THE HEADER

The first line of the absolute display will be the following header:

LOC ADDRESS DATA I

The meanings of the column headers are as follows:

LOC

Ι

is the column that contains a decimal number, 0-255, indicating the location in the logic analyzer acquisition memory. In order of acquisition, 000 is the oldest acquired data, and 255 is the newest acquired data.

ADDRESS is the column that contains the value that was on the 6809 address bus when this word of data was acquired.

DATA is the column that contains the value that was on the 6809 data bus when this word of data was acquired.

is the column that contains the value of the interrupt that was on the C3 (INT) control line when this word of data was acquired.

#### OPERATION-PM 111

#### DATA DISPLAY

A single word of data will be displayed in the following format:

111 aaaaaaaaaaaaaa dddddddd ci

where

- 111 is the acquisition memory location (0-255) of the word of data displayed on this line. The oldest word of data is in location 000, the newest in 255.

- aaaaaaaaaaaaaaa is the address bus value. It will be 4-16 digits long (radix-dependent) and centered in the field.

- dddddddd is the data bus value. It will be 2-8 digits long (radix-dependent) and centered in the field.

С

is the cycle type, i.e., one of the follow-ing:

- "F" (opcode fetch)

- "R" (memory read)

- "W" (memory write)

"?" (invalid cycle: a combination that should not occur)

Refer to Table 2-1 for the relationship between the previous cycle types and the control lines C2-C0.

i is the value that was on control line C3 when this word of data was acquired. The value will be 1 if an interrupt request was pending, and 0 if there was no interrupt request.

The trigger word will be emphasized by displaying the letter "T" in column 4 and by replacing the space under the LOC header column with a horizontal bar.

#### OPERATION-PM 111

#### ABSOLUTE DISPLAY EXAMPLE

The following is a portion of a hypothetical display. Note that in actual use:

- The radix of the address or data bus will not change from line to line.

- The address and data buses need not be displayed in the same radix.

| LOC | ADDRESS          | DATA     | I  |

|-----|------------------|----------|----|

| 000 | 1654             | 22       | FO |

| T   | 177765           | 116      | WO |

| 002 | R <e></e>        | Т        | Rl |

| 003 | 1111000010100011 | 11001011 | R0 |

Line 000 demonstrates hex radices for both the data and address buses.

Line 001 is a trigger line with octal radices for both buses.

Line 002 is an example of ASCII radices.

Line 003 is an example of binary radices.

#### OPERATION-PM 111

#### ADDITIONAL INFORMATION

#### CONTROL LINES

The following table summarizes information concerning the control lines and their relationship to the PM lll Personality Module.

| LINE                            | DERIVED<br>FROM                | ACTIVE       | STORED | WORD<br>RECOGNIZER | CLOCK<br>QUALIFIER<br>(DEFAULT) | COMMENTS |

|---------------------------------|--------------------------------|--------------|--------|--------------------|---------------------------------|----------|

| R/W(L)<br>(C0)                  | 6809 R/W(L)<br>LINE            | (H)/(L)      | YES    | YES                |                                 | 1        |

| FETCH1<br>(Cl)                  | PM 111<br>HARDWARE             | (H) *        | YES    | YES                |                                 | 1        |

| FETCH1+2<br>(C2)                | PM 111<br>HARDWARE             | (H) *        | YES    | YES                |                                 | 1        |

| INT<br>(C3)                     | 6809 NMI(L),<br>IRQ(L),FIRQ(I  | (H)<br>2)    | YES    | YES                |                                 | 2        |

| BA<br>(C4)                      | 6809 BA LINE                   | (H)          |        | YES                | Х                               | 3        |

| INVAL.OP<br>(C5)                | PM 111<br>HARDWARE             | (H)          |        | YES                | Х                               | 4        |

| VMA(L)<br>(C6)                  | 6809 address<br>bus,BS,R/W(L)  | • •          |        |                    | 0                               | 5        |

| HALT.<br>(DMA/<br>BREQ)<br>(C7) | 6809 HALT(L)<br>DMA/BREQ       | <b>,</b> (H) |        |                    | х                               | 6        |

| DMA+DEAD<br>(C8)                | PM lll<br>hardware, BA<br>line | (H)          |        |                    | 0                               | 7        |

| (C9)                            | tied high                      | (H)          |        |                    | Х                               | 8        |

#### Table 2-3 PM 111 CONTROL LINES

\*= Asserted low in the hardware, but inverted by firmware to appear asserted high to user.

2-22

## Scan by Zenith OPERATION-PM 111

#### COMMENT FIELD NUMBERS

l= Refer to Table 2-1.

2= Interrupts sampled on the falling edge of clock E. Minimum pulse width of 1 E cycle required on NMI(L).

3= Related to C8. Always low under default clock qualification.

4= Asserted l cycle after an illegal opcode; not useful as clock qualifier.

5= Similar to the 6800 VMA line, except asserted low.

6= C7 is asserted low when HALT(L) or when DMA/BREQ(L) is low. HALT(L) line (only) when used with the 6809E microprocessor.

7= Asserted high when BA is high, and for one cycle after BA goes low.

8= Always high (H); do not use.

#### 6809E OPERATING CONSIDERATIONS

The following information pertains to the operation of the 6809E series of microprocessors.

- The 6809E may not be halted under control of the 7D02-PM 111 system.

- The 6809E does not have a DMA/BREQ(L) line. When the PM lll is used with the 6809E series of microproceesors, the control line C7= HALT(L).

- ★ The real time message DMA/HALT will flicker in the upper right hand corner of the screen while the 7D02 is waiting for a trigger. This message appears when the busy line is low. This may be remedied, if desired, by changing the PM lll internal jumper strap A2J7013 to the 6809E position.

#### SPECIAL INSTRUCTION OPCODES

Both the CWAI and the SYNC opcodes can give a slow clock indication. This occurrence is normal when executing these instructions.

#### OPERATION-PM 111

#### HALTING THE 6809 MICROPROCESSOR

The PM 111 Personality Module is a passive bus monitor, with the exception of the HALT(L) line. The PM 111 hardware permits the microprocessor in the zero insertion force (ZIF) socket to be halted by the user's system under test (SUT), and/or the 7D02 Logic Analyzer. To halt the processor from the SUT, assert the SUT's HALT(L) line low. To halt the processor from the 7D02, change the trigger menu from SYSTEM UNDER TEST CONT. to SYSTEM UNDER TEST HALT. Using the CURSOR control key, move the cursor to the field and enter a 1. Upon triggering, the 7D02 will halt the processor. It will remain halted until the 7D02 returns to acquiring data and has not yet triggered. This applies only to the 6809 microprocessor, which must remain in the user's system.

0

2 - 24

Section 3-PM 111

#### PM 111 SPECIFICATIONS

#### OVERVIEW

This section of the manual lists the following PM lll specifications:

| TABLE TYPE                                                                                                                          | TABLE NUMBER                                  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| CHARACTERISTICS<br>QUALIFIERS<br>ELECTRICAL<br>MECHANICAL<br>ENVIRONMENTAL<br>PM 111 LOGIC ANALYZER<br>CABLE<br>MICROPROCESSOR PLUG | 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7 |

Items listed in the Performance Requirements column are specifications of the instrument that can be verified as described in the Performance Check section of this manual.

If verification of these listed electrical specifications is necessary for customer incoming inspection or other purposes, the Performance Check section lists the necessary test equipment and procedures for doing so.

Items listed in the Supplemental Information column are either explanatory notes or performance characteristics for which no limits are specified. They are not tested in the Performance Check section of this manual.

The PM 111 Personality Module supports the following microprocessors:

MC6809 MC68A09 MC68B09 MC6809E MC68A09E MC68B09E

#### SPECIFICATION-PM 111

#### SYSTEM DESCRIPTION

HALT PUT(L) is an output from the logic analyzer. The PM lll generates HALT(L) from the HALT PUT(L) and P HALT(L) signals.

LOOK is a control line generated by the 7D02 that disables the AIO-AII5 and DIO-DI7 buffers in the personality module.

SELP(L) is a control line generated by the 7D02 that is used to read the PROM in the personality module.

#### SAFETY GOALS

The personality module complies with the requirements of U.L. 1244, IEC 348, and CSA 556B.

## SPECIFICATION-PM 111

#### Table 3-1 PM 111 CHARACTERISTICS

| CHARACTERISTIC                                                                           | DESCRIPTION                     |

|------------------------------------------------------------------------------------------|---------------------------------|

| Signal Inputs<br>Max. Number of Channels<br>Data Lines<br>Address Lines<br>Control Lines | 33<br>8<br>16<br>9              |

| Clock (E)<br>Maximium Frequency<br>Minimum Frequency                                     | 2 MHz (68B09/68B09E)<br>100 kHz |

| Display<br>Max. No. of Channels<br>Data Lines<br>Address Lines<br>Control Lines          | 28<br>8<br>16<br>4              |

Table 3-2 PM 111 QUALIFIERS

| LINE               |    | STORED | WORD<br>RECOGNIZER | CLOCK<br>QUALIFIER |

|--------------------|----|--------|--------------------|--------------------|

| R/W(L)             | C0 | x      | x                  |                    |

| IFC(L)             | CI | X      | X                  |                    |

| (IFC+IFC2) (L)     | C2 | x      | X                  |                    |

| INT                | C3 | X      | x                  |                    |

| BA                 | C4 |        | x                  | х                  |

| IOCO(L)            | C5 |        | x                  | X*                 |

| VMA(L)             | C6 |        |                    | x                  |

| (HALT). (DMA/BREQ) | C7 |        |                    | x                  |

| DMA+DEAD           | C8 |        |                    | X                  |

|                    |    |        | l                  | L                  |

\* NOTE: Not useful for clock qualification.

## SPECIFICATION-PM 111

## Table 3-3

## ELECTRICAL SPECIFICATIONS

| CHARACTERISTIC                                                                  | PERFORMANCE REQUIREMENTS | SUPPLEMENTAL<br>INFORMATION                                                        |

|---------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------|

| Data Input Channels                                                             |                          |                                                                                    |

| TTL Input Levels                                                                |                          | 0 V to +7 V signal<br>swing 1/2 LSTTL<br>load, except<br>PHALT(L)<br>=l LSTTL load |

| Input Capacitance                                                               |                          | 45 pF nominal                                                                      |

| Voltage in low limit<br>(operating)                                             | s<br>+0.6 V max.         | +0.0 V min.                                                                        |

| Voltage in high limi<br>(operating)                                             | ts +2.0 V min.           | +7.0 V max.                                                                        |

| Current in low limit<br>(V in low =+0.4 V)                                      | s                        | -0.2 mA max.<br>(-0.4 mA max. for<br>PHALT)(L)                                     |

| Current in high limi<br>(V in high =+7.0 V)                                     | ts                       | +0.1 mA max.                                                                       |

| Current in high limi<br>(V in high =+2.7 V)                                     | ts                       | +0.02 mA max.<br>(+0.04 mA max. for<br>PHALT)(L)                                   |

| Maximum voltage in,<br>non-operating, non-<br>destructive (all<br>except clock) |                          | -7 V to +15 V<br>continuous on any<br>two inputs<br>simultaneously                 |

| Threshold Voltage                                                               |                          | Fixed +1.4 V nom.<br>TTL compatible                                                |

| Hysteresis                                                                      |                          | +0.4 V nom.<br>+0.2 V min.                                                         |

6

¥

ľ

ł

## SPECIFICATION-PM 111

| CHARACTERISTIC                                               | PERFORMANCE REQUIREMENTS | SUPPLEMENTAI<br>INFORMATION |

|--------------------------------------------------------------|--------------------------|-----------------------------|

| Delay from logic ana-<br>lyzer HALT PUT(L) to<br>HALT(L) out |                          |                             |

| Maximum                                                      |                          | 50 ns                       |

| HALT(L) output drive                                         |                          |                             |

| V out high                                                   |                          | +2.4 V, I out=1             |

| V out low                                                    |                          | +0.5 V, I out=-             |

| Clock (E), pin 34 of microprocessor                          |                          |                             |

| Input Impedance                                              |                          | 50 kilohms nomi             |

| Input Capacitance                                            |                          | 35 pF nominal               |

| Clock Period                                                 | 500 ns min.              | 10,000 ns max.              |

| Clock Pulse Width<br>(min.)                                  |                          | 220 ns high,<br>210 ns low  |

| Voltage in low limits<br>(operating)                         |                          | +0.0 V min.,<br>+0.5 V max. |

| Voltage in high limits<br>(operating)                        |                          | +2.4 V min.,<br>+5.6 V max. |

| Threshold Voltage                                            |                          | Fixed, +1.4 V n             |

| Hysteresis                                                   |                          | +0.4 V nominal              |

| Maximum Voltage in<br>non-operating,<br>non-destructive      |                          | -15 V to +15 V              |

| Crystal Loading (MC6809)                                     |                          |                             |

| C in, pin 38                                                 |                          | Typ. 15 pF                  |

| C out, pin 39                                                |                          | Тур. 9 рF                   |

# SPECIFICATION-PM 111

| Table 3    | 3-3 | (cont)      |

|------------|-----|-------------|

| ELECTRICAL | SPE | CIFICATIONS |

| CHARACTERISTICS                                                      | PERFORMANCE REQUIREMENTS    | SUPPLEMENTAL<br>INFORMATION           |

|----------------------------------------------------------------------|-----------------------------|---------------------------------------|

| Propagation Delays<br>through personality<br>module                  |                             |                                       |

| Delay through ECL clo                                                | ck                          | +10.5 ns min.,<br>+15 ns max.         |

| Delay added to PHALT(<br>line (from 40-pin plu<br>to microprocessor) |                             |                                       |

| Channel Delay                                                        |                             |                                       |

| DMA+DEAD                                                             |                             | 145 ns max.                           |

| (HALT).(DMA/BREQ)                                                    |                             | 125 ns max.                           |

| VMA(L)                                                               |                             | 170 ns max.                           |

| IOCO(L) (clocked)                                                    |                             | 450 ns max.                           |

| INT                                                                  |                             | 155 ns max.                           |