## PM 106/PM 107 PERSONALITY MODULE FOR 8086/8088 MICROPROCESSORS

INSTRUCTION MANUAL

# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

INSTRUCTION MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

070-3473-00 Product Group 57 Serial Number \_

First Printing MAY 1981 Revised NOV 1981

Copyright © 1981 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and istered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

## TABLE OF CONTENTS

Section 2

####

## PART 1 OPERATORS INFORMATION

| Section 1 | INTRODUCTION                      |          |

|-----------|-----------------------------------|----------|

|           | ABOUT THIS MANUAL                 | 1-1      |

|           | OVERVIEW OF THE PERSONALITY       |          |

|           | MODULE                            | 1-1      |

|           |                                   |          |

|           |                                   |          |

| Section 2 | OPERATING INSTRUCTIONS            |          |

|           |                                   | 2-1      |

|           | Storing the Personality Module    | 2-1      |

|           | Connecting the Personality Module |          |

|           | to the Logic Analyzer             | 2-1      |

|           | Connecting the Personality Module | <b>L</b> |

|           | to the System Under Test (SUT)    | 2-1      |

|           | Operation                         | 2-1      |

|           | •                                 | 2-1      |

|           | The Instruction Stream Queue      |          |

|           | Monitoring the Bus                | 2-2      |

|           | The Word Recognizer.              | 2-2      |

|           | ADDRESS Field                     | 2-2      |

|           | DATA Field.                       | 2-2      |

|           | [CODEFETCH]                       | 2-2      |

|           | BHE [/QDUMP] (BHE, PM 106         |          |

|           | Only)                             | 2-2      |

|           | R/W [LST-F]                       | 2-3      |

|           | M/IO [2LS-F]                      | 2-3      |

|           | MIN/MAX MODE                      | 2-3      |

|           | HOLD ACK                          | 2-3      |

|           | QLEVEL                            | 2-3      |

|           | IRQ                               | 2-3      |

|           | EXT TRIG IN                       | 2-3      |

|           | Qualify Command                   | 2-3      |

|           | Trigger Commands                  | 2-3      |

|           | User Clock Qualification          | 2-3      |

|           | User Clock Synthesis              | 2-4      |

|           | HALTing the System Under Test     | 2-4      |

|           | Triggering Past a Loop            | 2-4      |

|           | Absolute Data Displays            | 2-4      |

|           | PM 106/107 Difference             | 2-4      |

|           | Default Radices                   | 2-4      |

|           | DATA Field (PM 106 Only)          | 2-4      |

|           | Control Line Interpretation.      | 2-4      |

|           | LST-F.                            | 2-4      |

|           | 2LS-F                             | 2-4      |

|           |                                   | 2-4      |

#### Page

#### Page

| L&2LS                              | 2-4  |

|------------------------------------|------|

| QFILL                              | 2-4  |

| QFIL?                              | 2-5  |

| /QDUMP                             | 2-5  |

| H, L, W, (PM 106 Only)             | 2-5  |

| Mnemonic Data Displays             | 2-5  |

| Radices                            | 2-5  |

| ADDRESS                            | 2-5  |

| DATA                               | 2-5  |

| Multiple Lines at One Location     | 2-6  |

| Question Marks in the Display      | 2-6  |

| Asterisks in the Display           | 2-6  |

| Missing Mnemonics                  | 2-6  |

| INTA                               | 2-6  |

| HALT                               | 2-6  |

| CODEFETCH                          | 2-6  |

| No Disassembly                     | 2-6  |

| Mnemonic Format Differences (Using |      |

| Intel Format)                      | 2-6  |

| B Suffixes                         | 2-6  |

| # Prefixes                         | 2-6  |

| Brackets [ ]                       | 2-6  |

| CS:, ES:, DS:, and SS: Locations   | 2-6  |

| A Note on IRQ Information          | 2-6  |

| Immediate-Display-Program          | 2-7  |

| Examples                           | 2-7  |

| An 8088 Example                    | 2-7  |

| An 8086 Example                    | 2-8  |

| A Second 8088 Example              | 2-10 |

| A Second 8086 Example              |      |

| •                                  |      |

**OPERATING INSTRUCTIONS (cont)**

#### Section 3 SPECIFICATION

|                      | 3-1 |

|----------------------|-----|

| OVERVIEW             | 3-4 |

| Service Test Fixture | 3-6 |

## PART 2 SERVICE INFORMATION

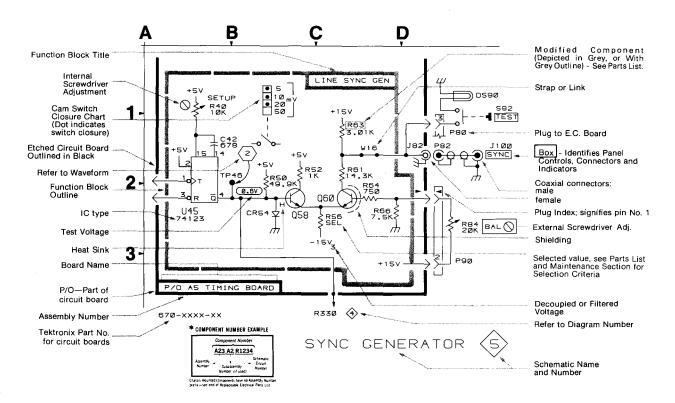

| Section 4 | THEORY OF OPERATION           |     |

|-----------|-------------------------------|-----|

|           | GENERAL THEORY OF OPERATION . | 4-1 |

|           | Overview                      | 4-1 |

|           | Function                      | 4-1 |

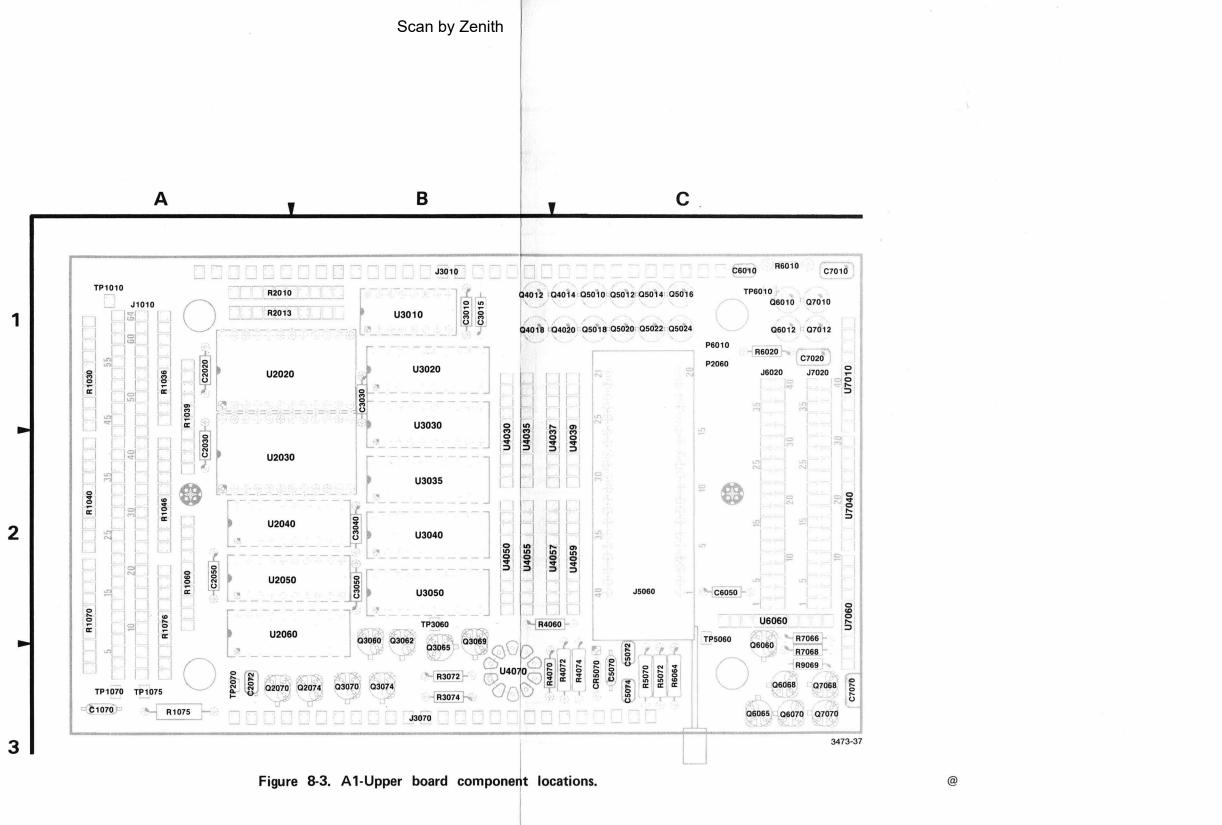

|           | Block Diagrams and Schematics | 4-1 |

|           | 8086/8088 Differences         | 4-1 |

|           | Minimum and Maximum Modes     | 4-2 |

|           | The Queue                     | 4-2 |

## **TABLE OF CONTENTS (cont)**

Section 5

### Page

Page

| Section 4 | THEORY OF OPERATION (cont)      |              |

|-----------|---------------------------------|--------------|

|           | Bus Cycle Operation             | 4-2          |

|           | Interrupts                      | 4-3          |

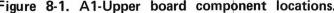

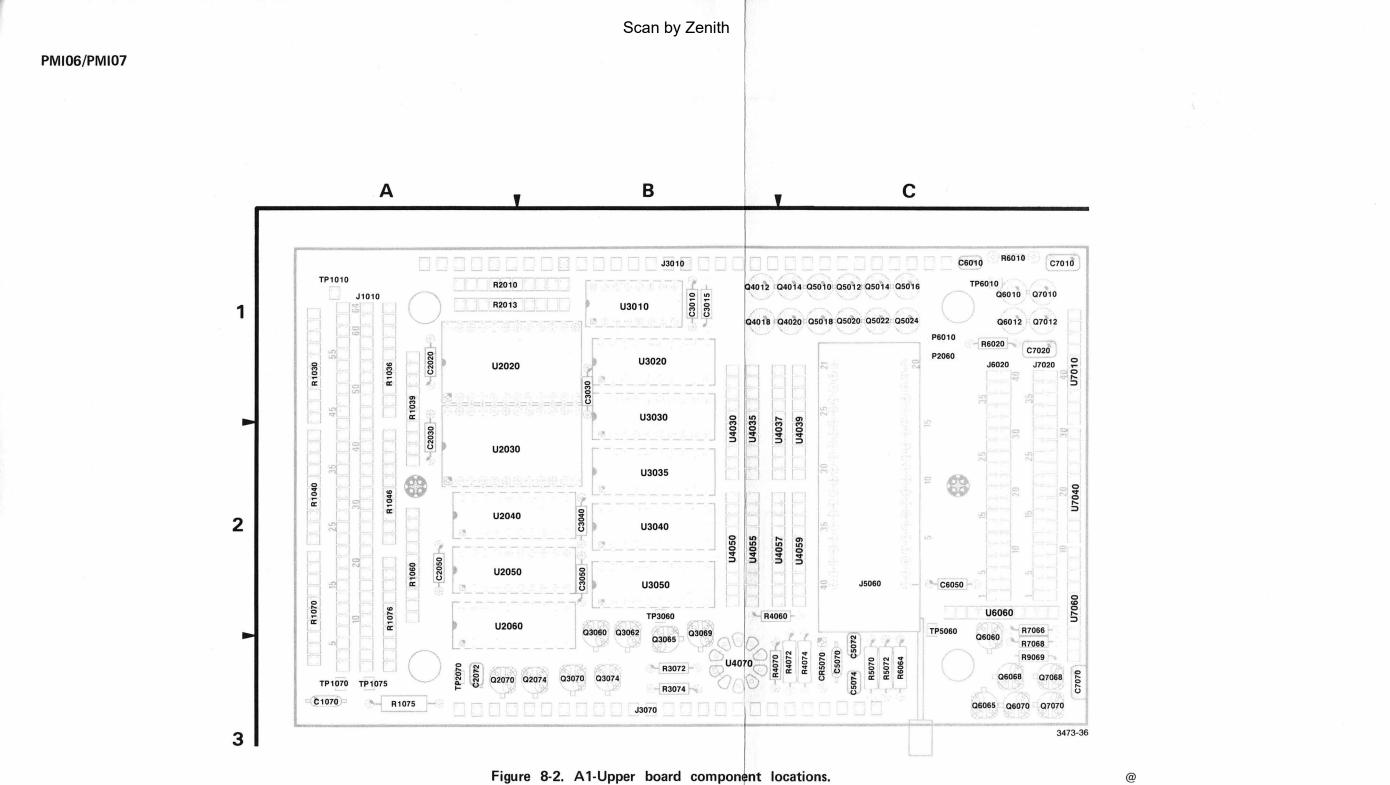

|           | DETAILED CIRCUIT BOARD DE-      |              |

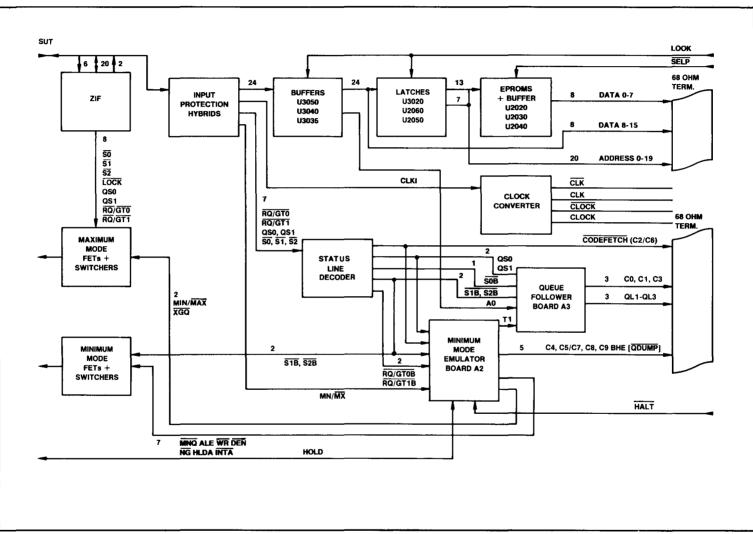

|           | SCRIPTION UPPER BOARD           | 4-3          |

|           | Overview                        | 4-3          |

|           | Address and Data Circuitry      | 4-3          |

|           | EPROMs and Buffer               | 4-5          |

|           | Maximum Mode FETs and Switchers | 4-5          |

|           | Minimum Mode FETs and Switchers | 4-5          |

|           | Buffer A1U3030                  | 4-5          |

|           | Latch A1U3020B                  | 4-6          |

|           | Demultiplexer A1U3010           | 4-6          |

|           | Clock Converter                 | 4-6          |

|           | Buffers A1U3035B and A1U3035H.  | 4-7          |

|           | Buffer A1U3020C                 | 4-7          |

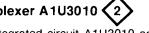

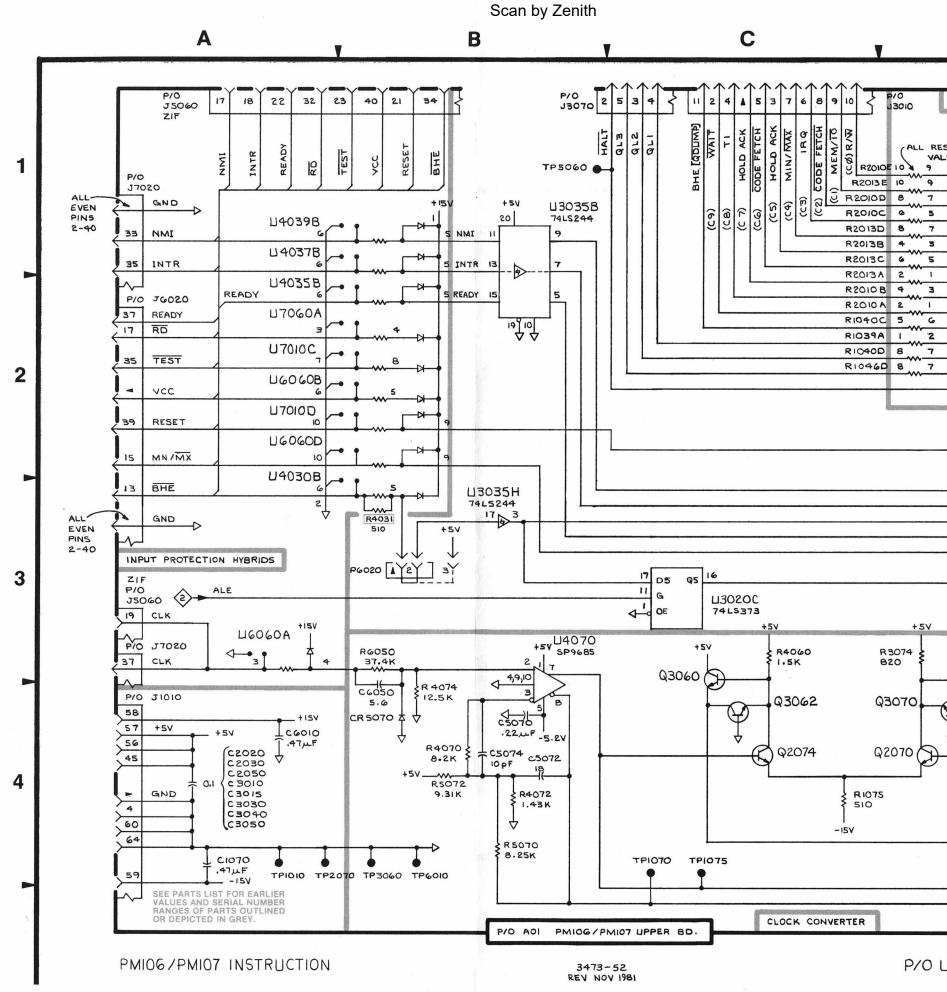

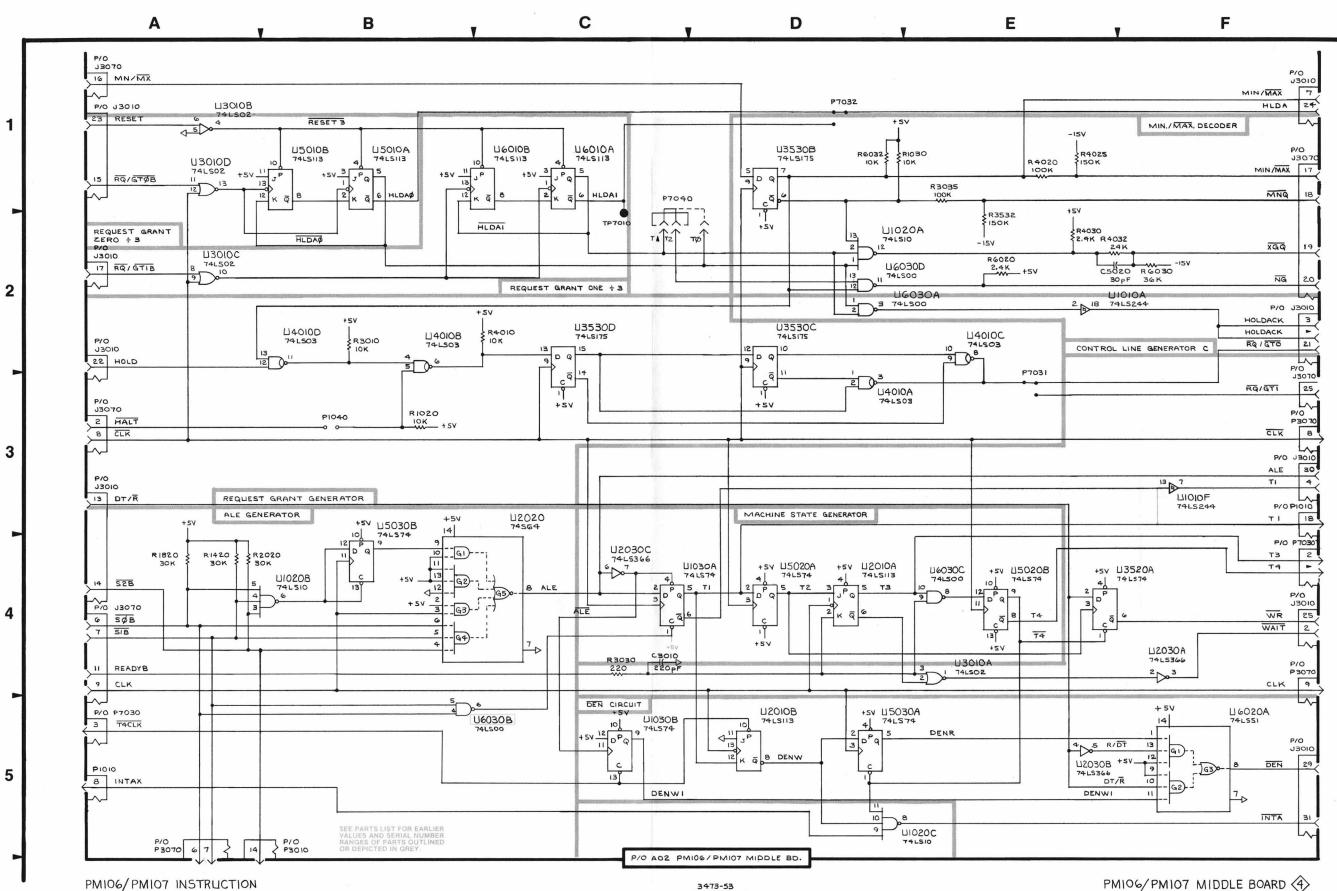

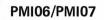

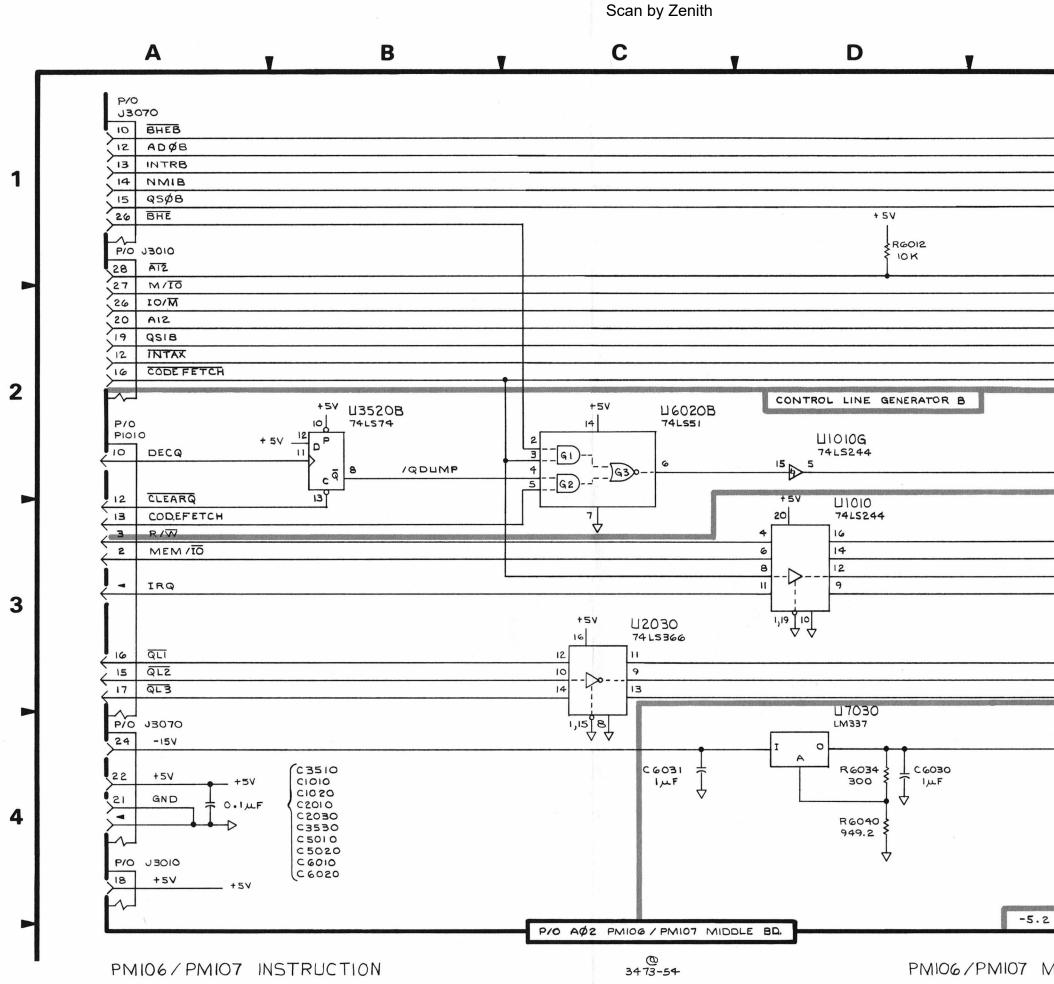

|           | MIDDLE BOARD                    | 4-7          |

|           | Overview                        | 4-7          |

|           | Machine State Generator         | 4-9          |

|           |                                 | 4-10         |

|           | DEN Circuit.                    | 4-10         |

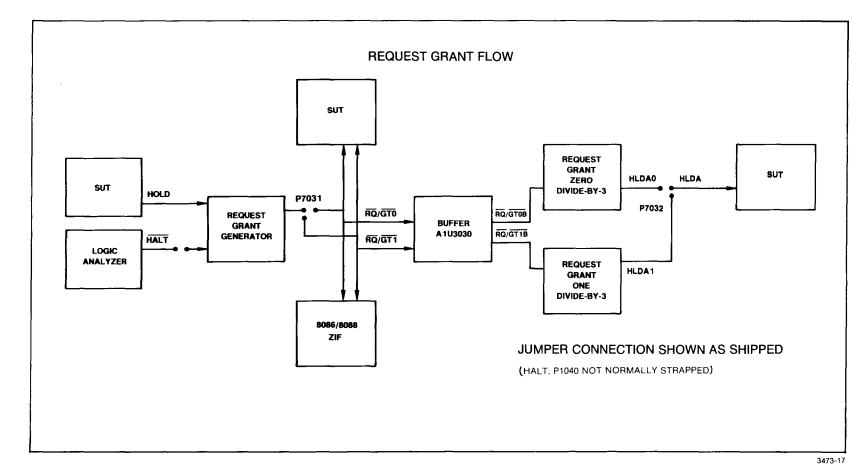

|           | Request Grant Zero Divide-By-3  | 4-11<br>4-12 |

|           | Request Grant Generator         | 4-12         |

|           | Grant                           | 4-12         |

|           | Release                         | 4-12         |

|           | Minimum/Maximum Decoder         | 4-12         |

|           | WR Flip-Flop A2U3520A           | 4-14         |

|           | INTA Gate A2U1020C              | 4-14         |

|           | RESET3 Gate A2U3010B            | 4-14         |

|           | Control Line Generator C        | 4-14         |

|           | Buffer A2U1010                  | 4-15         |

|           | Buffer A2U2030                  | 4-15         |

|           | -5 Volt Regulator               | 4-15         |

|           | Control Line Generator B        | 4-15         |

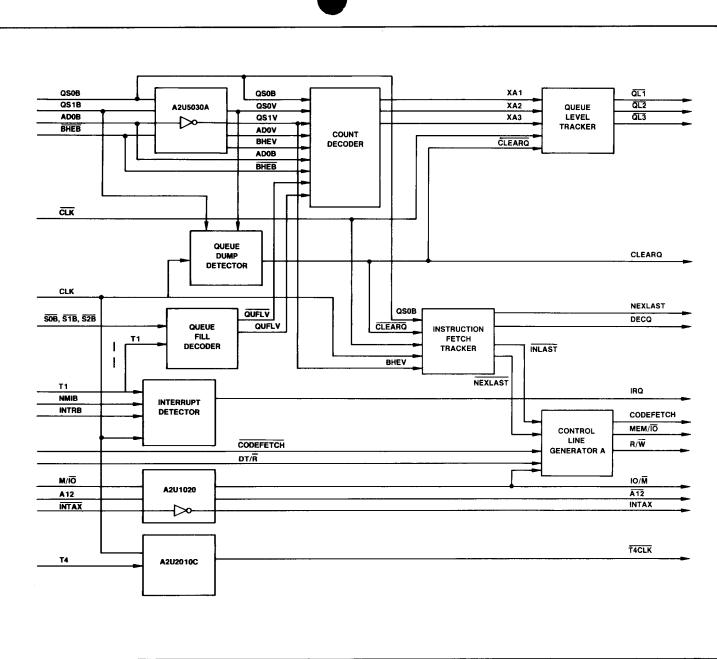

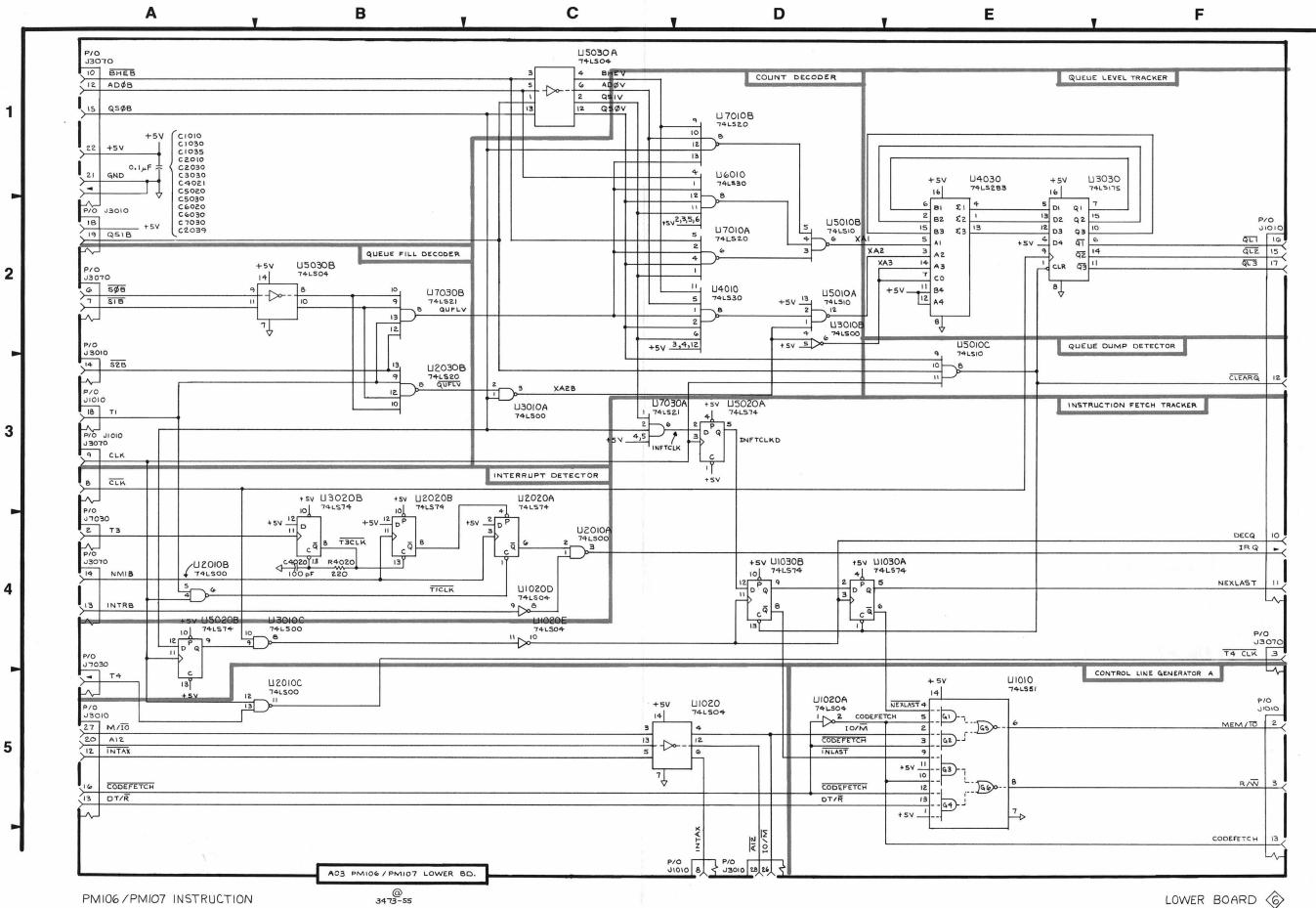

|           | BOTTOM BOARD                    | 4-16         |

|           | Overview                        | 4-16         |

|           | Queue Dump Detector             | 4-16         |

|           | Inverter A3U5030                | 4-18         |

|           | Inverter A3U1020                | 4-18         |

|           | T4CLK Gate A3U2010C             | 4-18         |

|           | Interrupt Detector              | 4-18         |

|           | Count Decoder                   | 4-19         |

|           | XA1                             | 4-19         |

|           | XA2                             | 4-19         |

|           | XA3                             | 4-20         |

|           | Queue Level Tracker             | 4-20         |

|           | Instruction Fetch Tracker       | 4-22         |

|           | Queue Fill Decoder              | 4-22<br>4-22 |

|           |                                 | 4-22         |

| PERFORMANCE CHECK              |      |

|--------------------------------|------|

|                                | 5-1  |

| Equipment List                 | 5-1  |

| Preliminary Setup              | 5-1  |

| DIAGNOSTIC MONITOR, PART I     | 5-4  |

| Overview                       | 5-4  |

| Diagnostic Module 9 PER. MOD.  |      |

| -SYSTEM                        | 5-4  |

| Diagnostic Module B TIMING OP- |      |

| TION                           | 5-4  |

| FUNCTIONAL CHECKS, PART II     | 5-5  |

| Overview                       | 5-5  |

| Base Program                   | 5-5  |

| Test 1                         | 5-6  |

| Test 2A                        | 5-6  |

| Test 3A                        | 5-9  |

| Test 3B                        | 5-12 |

| Test 3C                        | 5-12 |

| Test 4                         | 5-12 |

| PERFORMANCE CHECK, PART III    | 5-13 |

| Overview                       | 5-13 |

| Preliminary Setup              | 5-13 |

| Test 1                         | 5-14 |

## Section 6 MAINTENANCE AND

| TROUBL | ESHOOTING |

|--------|-----------|

| MAINTENANCE                         | 6-1 |

|-------------------------------------|-----|

| Repair                              | 6-1 |

| Obtaining Replacement Parts         | 6-1 |

| Ordering Parts                      | 6-1 |

| Cleaning Instructions               | 6-1 |

| Exterior                            | 6-1 |

| Interior                            | 6-1 |

| Personality Module Disassembly      | 6-1 |

| Logic Analyzer Plug Disassembly     | 6-2 |

| Microprocessor Replacement Plug     |     |

| Disassembly                         | 6-2 |

| TROUBLESHOOTING                     | 6-3 |

| Overview                            | 6-3 |

| Diagnostic Monitor                  | 6-3 |

| Functional Checks                   | 6-3 |

| Performance Checks                  | 6-3 |

| Troubleshooting Error List and Pro- |     |

| cedures                             | 6-3 |

| Substitution Method                 | 6-3 |

| Service Test Fixture                | 6-3 |

| Timing Option                       | 6-4 |

| Diagnostic Module 9 PER. MOD.       |     |

| -SYSTEM                             | 6-4 |

## **TABLE OF CONTENTS (cont)**

Section 6 MAINTENANCE AND TROUBLESHOOTING (cont) Subtest 1......

| Subtest 2                       | 6-4  |

|---------------------------------|------|

| Subtest 3                       | 6-4  |

| Subtest 4                       | 6-6  |

| Subtest 7                       | 6-8  |

| Diagnostic Module B-TIMING      |      |

| OPTION                          | 6-9  |

| TROUBLESHOOTING ERROR LIST      | 6-9  |

| PROCEDURE A                     | 6-13 |

| PROCEDURE B                     | 6-14 |

| PROCEDURE C                     | 6-14 |

| PROCEDURE D                     | 6-15 |

| TROUBLESHOOTING WITH SIGNA-     |      |

| TURE ANALYSIS                   | 6-15 |

| TROUBLESHOOTING WITH BOARD 3    | 8    |

| REMOVED                         | 6-28 |

| Preliminary Setup               | 6-28 |

| Disabled Circuits               | 6-28 |

| ADDITIONAL INFORMATION          | 6-28 |

| Delay through ECL CLOCK         | 6-28 |

| ECL CLOCK Mismatch              | 6-29 |

| Strapping Procedures            | 6-29 |

| HALT Line Strapping Procedure . | 6-29 |

Page

6-4

#### Section 7 REPLACEABLE ELECTRICAL PARTS

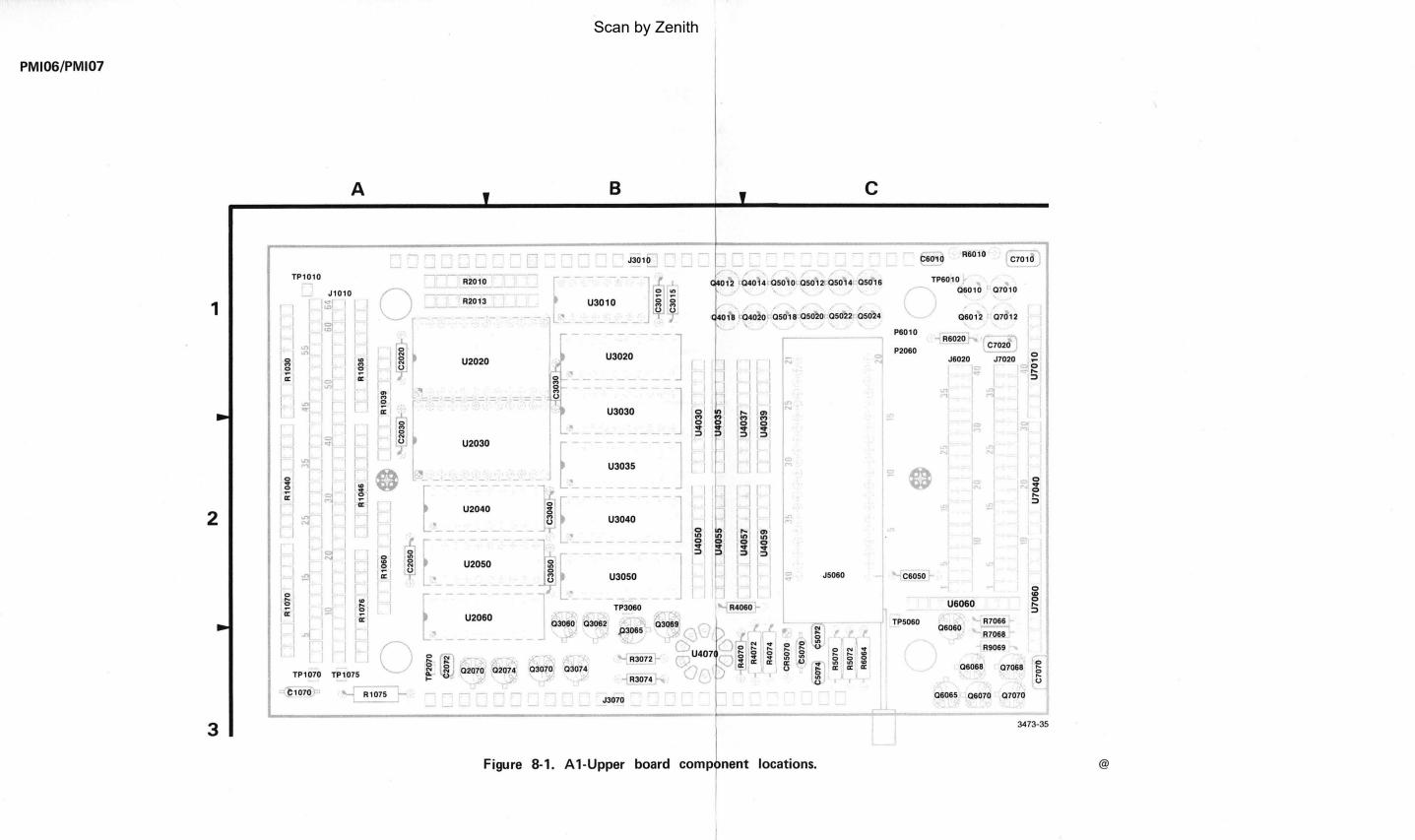

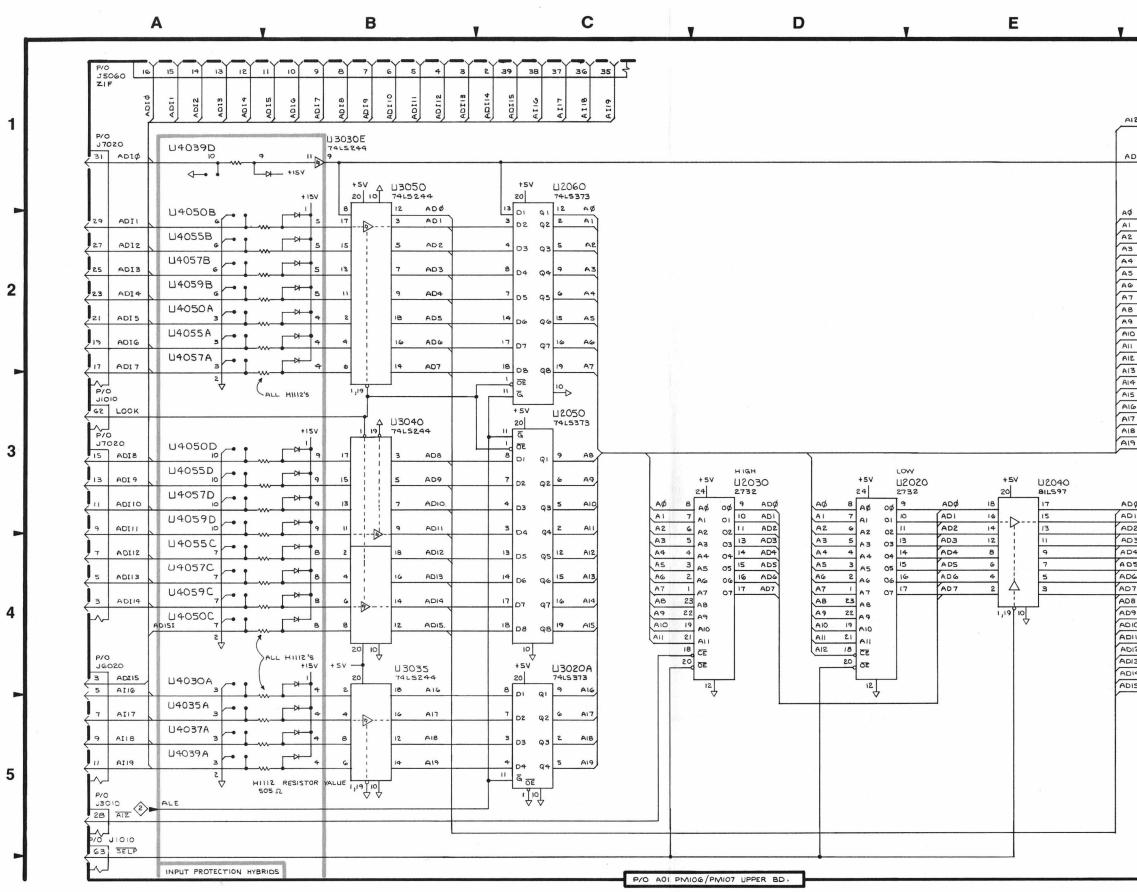

- Section 8 CIRCUIT BOARD DIAGRAMS AND ILLUSTRATIONS

- Section 9 REPLACEABLE MECHANICAL PARTS

- Section 10 SIGNAL GLOSSARY

CHANGE INFORMATION

# LIST OF ILLUSTRATIONS

| Fig.<br>No | 1                                                      | Page | Fig.<br>No. |                                                     | Page |

|------------|--------------------------------------------------------|------|-------------|-----------------------------------------------------|------|

| 2-1        | ABSOLUTE DISPLAY OF EXAMPLE PRO-                       |      | 5-1         | SYSTEM LAYOUT                                       | 5-3  |

|            | GRAM - 8088                                            | 2-7  | 5-2A        | TIMING DIAGRAM, MINIMUM MODE -                      |      |

| 2-2        | QUEUE STATUS DURING EXAMPLE PRO-                       |      |             | PM 106 ONLY                                         | 5-6  |

|            | GRAM EXECUTION - 8088                                  | 2-8  | 5-2B        | TIMING DIAGRAM, MINIMUM MODE -                      |      |

| 2-3        | MNEMONIC DISPLAY OF EXAMPLE PRO-                       |      |             | PM 107 ONLY                                         | 5-6  |

|            | GRAM - 8088                                            | 2-8  | 5-3A        | STATE DISPLAY, MINIMUM MODE -                       | E 7  |

| 2-4        | ABSOLUTE DISPLAY OF EXAMPLE PRO-                       |      |             |                                                     | 5-7  |

|            | GRAM - 8086                                            | 2-9  | 5-3B        | STATE DISPLAY, MINIMUM MODE -                       | 5-8  |

| 2-5        | QUEUE STATUS DURING EXAMPLE PRO-                       |      | <b>F</b> 4  |                                                     | 5-0  |

|            | GRAM EXECUTION - 8086                                  | 2-9  | 5-4         | TIMING DIAGRAM, MAXIMUM MODE -<br>PM 106 and PM 107 | 5-9  |

| 2-6        | MNEMONIC DISPLAY OF EXAMPLE PRO-                       | 0.40 | <i></i>     | STATE DISPLAY, MAXIMUM MODE -                       | 0-0  |

|            | GRAM 08086                                             | 2-10 | 5-5         | PM 106 and PM 107                                   | 5-10 |

| 2-7        | ABSOLUTE DISPLAY OF SECOND EXAM-                       | 0.40 | 5-6         | TIMING DIAGRAM RQ/GT1, MAXIMUM                      | 5-10 |

|            | PLE PROGRAM - 8088                                     | 2-10 | 0-C         | MODE - PM 106 and PM 107                            | 5-11 |

| 2-8        | QUEUE STATUS DURING SECOND EXAM-                       | 2-11 | 5-7A        | ABSOLUTE DISPLAY, ADDRESS 80000 -                   | 0.11 |

| • •        |                                                        | 2-11 | 5-7 A       | PM 106 ONLY                                         | 5-11 |

| 2-9        | MNEMONIC DISPLAY OF SECOND EXAM-<br>PLE PROGRAM - 8088 | 2-11 | 5-7B        | ABSOLUTE DISPLAY, ADDRESS 80000 -                   | •••• |

| 0.10       | ABSOLUTE DISPLAY OF SECOND EXAM-                       | 2-11 | 5-70        | PM 107 ONLY                                         | 5-12 |

| 2-10       | PLE PROGRAM - 8086                                     | 2-12 | 6-1         | MICROPROCESSOR PLUG DISASSEM-                       |      |

| 2-11       | QUEUE STATUS DURING SECOND EXAM-                       |      | •••         | BLY                                                 | 6-2  |

| 2-11       | PLE PROGRAM EXECUTION - 8086                           | 2-13 | 6-2         | PM 106 DIAGNOSTIC WORD                              |      |

| 2-12       | MNEMONIC DISPLAY OF SECOND EXAM-                       |      | • -         | RECOGNIZERS                                         | 6-5  |

| 2-12       | PLE PROGAM -8086                                       | 2-13 | 6-3         | PM 106 DIAGNOSTIC MEMORY DISPLAY                    | 6-6  |

| 4-1        | OVERVIEW BLOCK DIAGRAM                                 | 4-4  | 6-4         | PM 107 DIAGNOSTIC WORD                              |      |

| 4-2        | MIDDLE BOARD BLOCK DIAGRAM                             | 4-8  |             | RECOGNIZERS                                         | 6-7  |

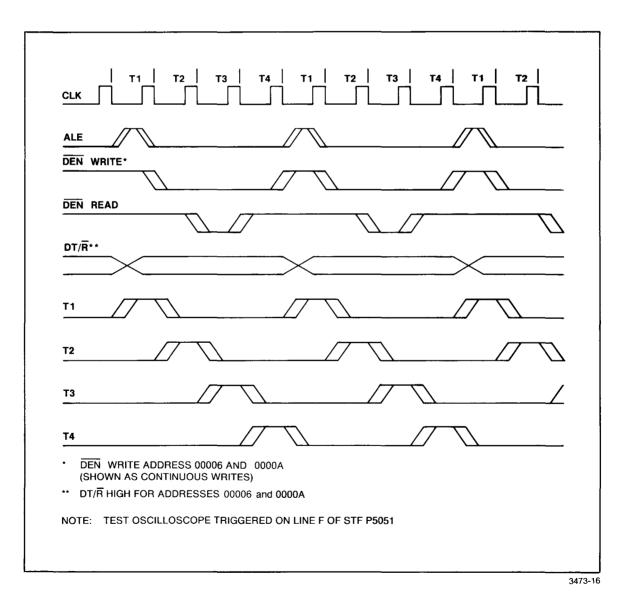

| 4-3        | BUS CYCLE TIMING DIAGRAM                               | 4-9  | 6-5         | PM 107 DIAGNOSTIC MEMORY DISPLAY                    | 6-8  |

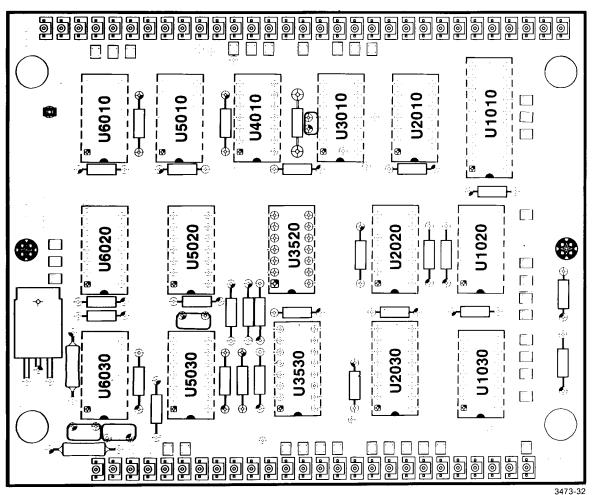

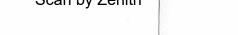

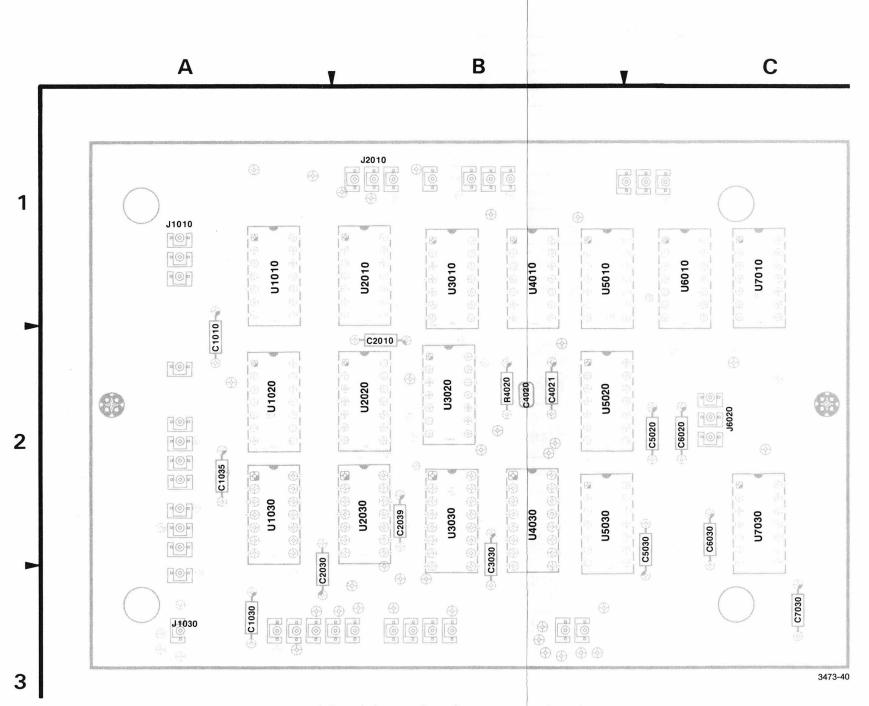

| 4-4        | REQUEST GRANT FLOW                                     | 4-13 | 6-6         | BOARD A2 COMPONENT LOCATOR                          | 6-16 |

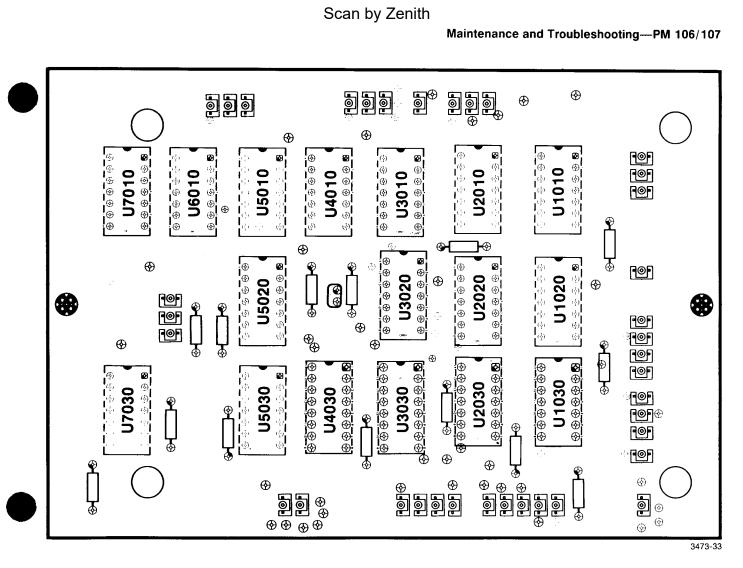

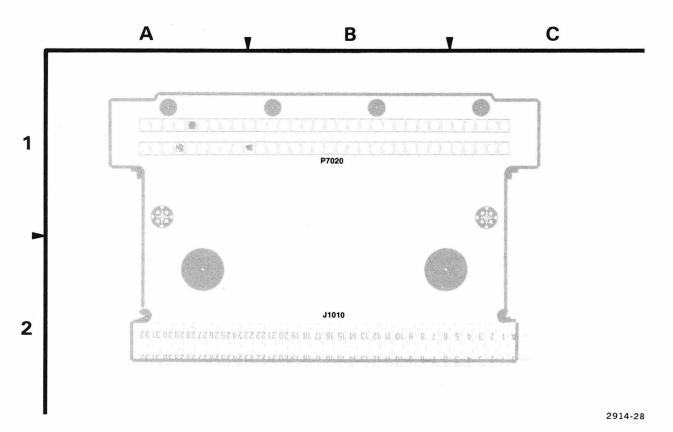

| 4-5        | BOTTOM BOARD BLOCK DIAGRAM                             | 4-17 | 6-7         | BOARD A3 COMPONENT LOCATOR                          | 6-17 |

## LIST OF TABLES

Page

#### Table No.

| 2-1 | VALID AND INVALID DATA BYTES       | 2-3  |

|-----|------------------------------------|------|

| 2-2 | ABSOLUTE STATUS DERIVATION         | 2-5  |

| 2-3 | BYTE VALIDITY                      | 2-5  |

| 3-1 | ELECTRICAL SPECIFICATIONS          | 3-1  |

| 3-2 | MECHANICAL SPECIFICATIONS          | 3-4  |

| 3-3 | ENVIRONMENTAL SPECIFICATIONS       | 3-4  |

| 3-4 | MICROPROCESSOR PLUG.               | 3-5  |

| 3-5 | LOGIC ANALYZER PLUG                | 3-6  |

| 3-6 | TIMING RESPONSE-REQUIREMENTS       |      |

|     | DIFFERENCES                        | 3-7  |

| 4-1 | STATUS LINE INPUTS                 | 4-6  |

| 4-2 | QUEUE STATUS                       | 4-6  |

| 4-3 | REQUEST GRANT ZERO DIVIDE-BY-3     | 4-11 |

| 4-4 | CONTROL LINE GENERATOR B           |      |

|     | BHE[QDUMP] LINE                    | 4-15 |

| 4-5 | BYTE SELECTION                     | 4-18 |

| 4-6 | ADDER TABLE                        | 4-20 |

| 4-7 | STATUS INDICATIONS IN THE ABSOLUTE |      |

|     | MODE                               | 4-22 |

| 5-1 | REQUIRED TEST EQUIPMENT            | 5-1  |

| 5-2 | STF JUMPERS (SELF POSITION)        | 5-3  |

| 5-3 | P6451 TIMING OPTION CONNECTION TO  |      |

|     | STF                                | 5-3  |

| 5-4 | STF JUMPERS (PROG POSITION)        | 5-5  |

| 6-1 | STF JUMPER PLUGS AND TEST POINTS   | 6-4  |

| 6-2 | PERSONALITY MODULE TEST POINTS .   | 6-15 |

| 6-3 | SIGNATURE ANALYSIS VALUES          | 6-18 |

## **OPERATORS SAFETY SUMMARY**

The general safety information in this part of the summary is for both operating and servicing personnel. Specific warnings and cautions will be found throughout the manual where they apply, but may not appear in this summary.

### TERMS

#### In This Manual

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### As Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

### SYMBOLS

#### In This Manual

This symbol indicates where applicable cautionary or other information is to be found.

#### As Marked on Equipment

DANGER — High voltage.

Protective ground (earth) terminal.

ATTENTION — refer to manual.

#### **Power Source**

This product is intended to operate from a power module connected to a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### **Grounding the Product**

This product is grounded through the grounding conductor of the power module power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle before connecting to the product input or output terminals. A protective ground connection by way of the grounding conductor in the power module power cord is essential for safe operation.

#### **Danger Arising From Loss of Ground**

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulating) can render an electric shock.

#### **Use the Proper Fuse**

To avoid fire hazard, use only the fuse of correct type, voltage rating and current rating as specified in the parts list for your product.

Refer fuse replacement to qualified service personnel.

#### **Do Not Operate in Explosive Atmospheres**

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

#### **Do Not Operate Without Covers**

To avoid personal injury, do not operate this product without covers or panels installed. Do not apply power to the plug-in via a plug-in extender.

## SERVICE SAFETY SUMMARY FOR QUALIFIED SERVICE PERSONNEL ONLY

Refer also to the preceding Operators Safety Summary.

#### **Do Not Service Alone**

Do not perform internal service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

#### Use Care When Servicing With Power On

Dangerous voltages may exist at several points in this product. To avoid personal injury, do not touch exposed connections and components while power is on. Disconnect power before removing protective panels, soldering, or replacing components.

#### **Power Source**

This product is intended to operate in a power module connected to a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

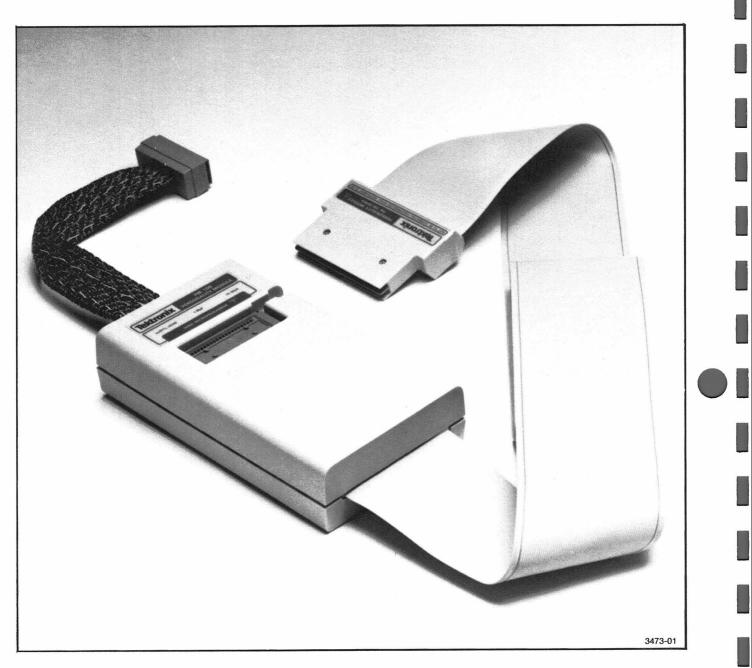

The PM 106 Personality Module used with the 8086 Microprocessor.

## INTRODUCTION

## **ABOUT THIS MANUAL**

This manual describes the operation and servicing of the PM 106 Personality Module which is used with the 8086 microprocessor, and the PM 107 Personality Module which is used with the 8088 microprocessor.

The first part of this manual, the operator's portion, provides an overview of the module, connection instructions, and operating information which supplements that in the 7D02 Operator's manual by personalizing it to the PM 106/107 Personality Modules and the 8086/8088 microprocessors.

The second part of this manual, the service portion, is found after the colored divider page. It contains maintenance information, circuit descriptions, diagnostics, schematics, and parts lists, and is intended to be used only by qualified service personnel. Refer to the table of contents for the specific location of information.

This manual makes frequent reference to the "logic analyzer"; this means the 7D02 Logic Analyzer. It is assumed that the reader has access to Operator's and Service manuals for the 7D02. This manual also makes frequent reference to *The 8086 Family User's Manual*, an Intel publication. The reader will also need access to this manual to understand the PM 106 and the PM 107.

## OVERVIEW OF THE PERSONALITY MODULES

The PM 106 and PM 107 "personalize" the logic analyzer for use with the 8086 and 8088 microprocessors. They contain firmware which modifies the display and diagnostics of the logic analyzer for use with their microprocessors. Hardware in the personality modules isolates, buffers, latches, and, in many cases, translates the data on the bus of an 8086/8088-based system under test (SUT) into a form which is recognizable by the 7D02.

The personality module passively monitors the system under test; it does not interfere with processor operation or supply its own program, it only collects data and interprets it after it is stored.

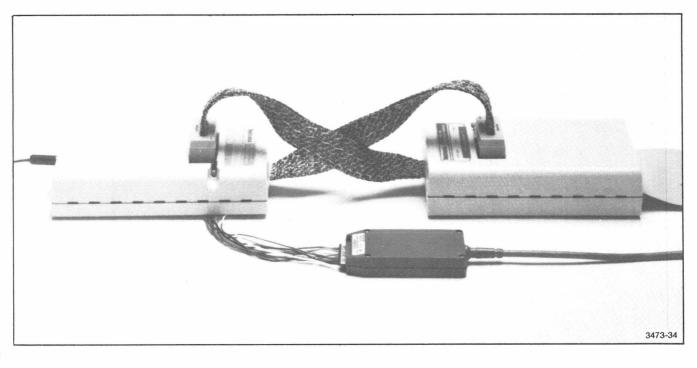

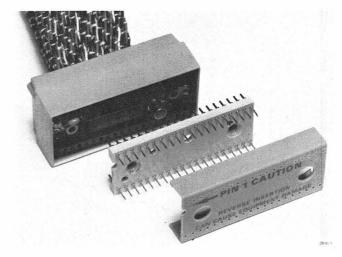

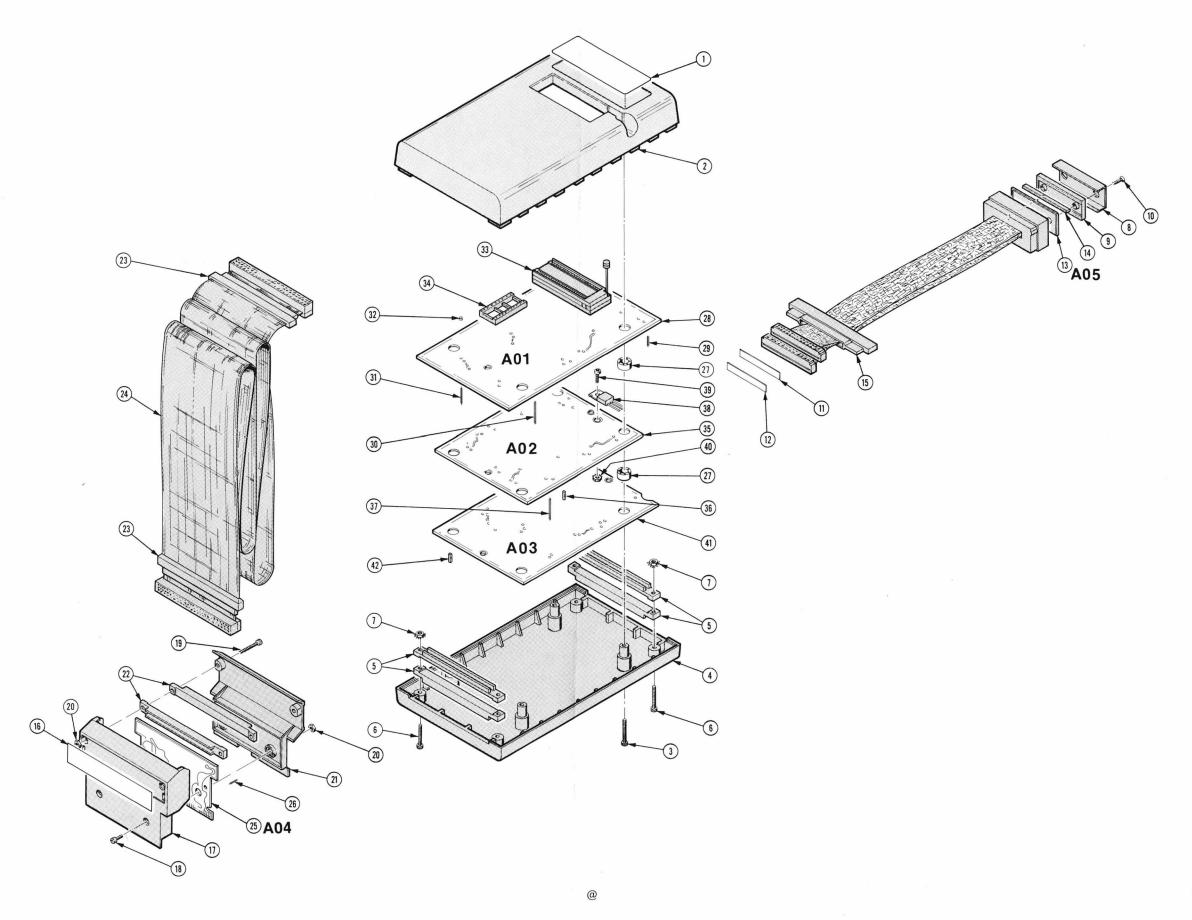

Physically, the personality modules consist of a plastic pod containing three circuit boards. A four foot ribbon cable with a 64 pin connector serves as the interface to the logic analyzer, while a twisted pair, woven cable with a 40-pin connector connects the PM 106/107 to the system under test. A zero insertion force (ZIF) socket receives the microprocessor itself.

## **OPERATING INSTRUCTIONS**

### INTRODUCTION

This section of the manual provides information concerning the operation of the PM 106/107 Personality Module.

#### Storing the Personality Module

Keep the personality module in a clean area where the temperature remains between  $-62^{\circ}$ C and  $+85^{\circ}$ C. Humidity should not exceed 95%, non-condensing. The personality module should not be taken above 50,000 feet.

When storing the module, protect the microprocessor replacement plug with the plastic protector, Tektronix P/N 200-2445-00. This prevents damage to the pins during storage and protects the personality module from static electricity.

## Connecting the Personality Module to the Logic Analyzer

Always be certain to turn OFF the mainframe (logic analyzer) power before connecting or disconnecting any personality module. Also, always be sure to turn OFF the power to the system under test before removing the microprocessor and installing the replacement plug. Failure to take these precautions may result in permanent damage to the logic analyzer, the personality module, or the system under test.

Turn off the mainframe power and insert the ribbon connector labeled PERSONALITY MODULE - PM 100 SERIES into the receptacle on the logic analyzer with the same name.

## Connecting the Personality Module to the System Under Test (SUT)

- 1. Turn off the power to the logic analyzer and the SUT.

- 2. Ground yourself to drain static electricity.

3. Remove the microprocessor from the SUT and install it in the ZIF socket of the personality module. Be sure to insert it correctly, with pin 1 of the microprocessor toward the lever of the ZIF socket.

#### NOTE

The low profile DIP clip should not be used with the PM 106 or PM 107.

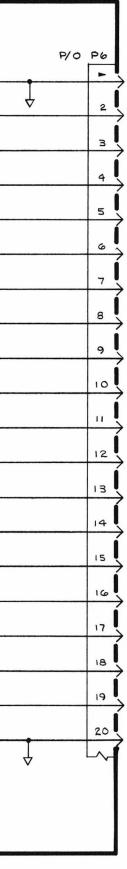

4. Plug the personality module microprocessor replacement plug into the microprocessor socket of the SUT. Make sure that pin 1 of the replacement plug goes to pin 1 of the SUT socket. Pin 1 of the microprocessor plug is marked with a notch and an arrow.

5. Turn on power to the logic analyzer and the SUT, and reset the SUT.

#### NOTE

Because of the set-up and hold times of the 7D02 and the PM 106/107, several system parameters are constrained. Refer to the Specification Section of this manual and to The 8086 Family User's Manual (an Intel publication).

#### Operation

To understand the operation of the PM 106/107 Personality Modules, the operator must also be familiar with the operation of the 7D02 Logic Analyzer and the 8086 family of microprocessors. Refer to the 7D02 Operator's Manual Tektronix P/N 070-2918-00) and *The 8086 Family User's Manual* (an Intel publication).

#### NOTE

For use with the PM 106 or PM 107, the 7D02 must be equipped with the Expansion Option. The PM 106 and PM 107 may be used with or without the Timing Option. Displays in this section are shown without the Timing Option, however.

#### Operating Instructions—PM 106/107

Many of the displays shown in the 7D02 Operator's Manual will vary when the logic analyzer is used with the PM 106 or PM 107 because the displays in the 7D02 manuals were based on a different microprocessor and personality module. The operator's portion of this manual should therefore be viewed as a personalized supplement to, and in some cases substitute for, the 7D02 Operator's Manual.

The Instruction Stream Queue. The 8086/8088 actually consists of two processors working in tandem. The execution unit executes instructions, while the bus interface unit pre-fetches instructions, reads operands and writes results. The bus interface unit contains an instruction stream queue which can hold up to six bytes of instructions in the case of the 8086, four in the case of the 8088. The actual number of bytes in the queue varies with operating circumstances. (Refer to *The 8086 Family User's Manual*, an Intel publication.)

Because of this queue, a particular instruction appears on the bus at one time, while it is going into the queue, and is executed out of it at a later time (or not at all). In order to disassemble the mnemonics the PM 106 or PM 107 must therefore have some way of finding out when the first byte of an instruction is executed. This is accomplished by using information about the queue level and two additional lines which indicate when the last or second-to-last byte executed is a fetch of a new instruction.

**Monitoring The Bus.** The 7D02 - PM 106/107 system monitors activity on an 8086 or 8088 system bus. Data on the bus may or may not be relevant. For example, a particular instruction may be pre-fetched and yet never executed. At acquisition time, the 7D02 - PM 106/107 system has no way to determine which instructions will later be executed. This is the case because all triggering and qualification are done in real time relative to data on the bus. Execution of an instruction occurs later, if at all. Consequently, it is possible to trigger the logic analyzer on an instruction that is never executed. This is likely to occur if that instruction appears just past a loop; it will be recognized by the 7D02 as it enters the instruction stream queue, even though it is not to be executed because of a program jump.

In the absolute mode, this bus activity is displayed with little interpretation. In the mnemonic mode, post-processing algorithms are employed to decode the instructions that were actually executed. These mnemonics are displayed along with their operands. In those cases where there is insufficient information in memory to guarantee accurate disassembly, a question mark is displayed before the mnemonic along with asterisks where the operand would have appeared. Heavy use of the data qualification capabilities of the 7D02 (the QUALIFY command) can lead to erroneous data or loss of data which is essential to this post-processing procedure.

#### **The Word Recognizer**

**ADDRESS Field.** The 8086 can move data in two byte segments. In this case only the even byte is addressed; the odd address does not appear on the address bus and will not be recognized by this field. In other cases, such as the case of a jump or a non-[CODEFETCH] read or write to an odd address, odd addresses do occur on the bus and will be recognized.

**DATA Field.** The byte of data on the right is associated with an even address. The byte on the left is associated with the next address, an odd address. Transfers of 16 bits of valid data on one cycle only occur from word boundaries, i.e., even addresses. If, as a result of an execution transfer, a CODEFETCH occurs from an odd address boundary, an 8 bit transfer takes place. This is then followed by normal 16 bit transfers. If a 16 bit data value is split across a word boundary, it will be read or written as two 8 bit transfers (16 bit data values are stored with the least significant byte at the low address and the most significant byte at the high address).

**[CODEFETCH].** This control line is extremely important to understanding word recognizer operation and the significance of data displays. When CODEFETCH = 1, the 8088 (or 8086) is moving one (or two) bytes of instruction data into the instruction stream queue. Note that CODEFETCH is true for any byte of an instruction, not just the opcode. When CODEFETCH = 0, the bus is in use for input, output, memory read or memory write.

[CODEFETCH] has additional significance to PM 106/107 operation, however. It controls the meaning of three other control lines from the PM 106/107 to the 7D02: BHE [/QDUMP], R/W [LST-F], and M/IO [2LST-F]. With CODEFETCH = 0, these lines have their first meaning. When CODEFETCH = 1, these lines have the meaning shown in brackets. On the 7D02 screen display, signals which are active when low are shown prefaced by a '/'. Low going signals not displayed on the screen are indicated with a bar, e.g.,  $\overline{SIG}$ .

**BHE** [/QDUMP] (BHE, PM 106 Only). When [CODE-FETCH] is low, this line carries byte high enable, BHE, information. When [CODEFETCH] is high, this line carries /QDUMP information.

BHE operates in conjunction with A0 to establish whether the high byte, the low byte, or the whole word is valid data.

When [CODEFETCH] is high, a low on the A0 line means that the data should be interpreted as a full word (high and low bytes), when A0 is high only the high byte is valid. When [CODEFETCH] is low, Table 2-1 defines which bytes contain valid data.

Table 2-1 VALID AND INVALID DATA BYTES

| BHE | <b>A</b> 0 | Valid                   | Displayed As |

|-----|------------|-------------------------|--------------|

| 0   | 0          | Low byte                | L            |

| 0   | 1          | Low byte<br>Error       | ?            |

| 1   | 0          | Both bytes<br>High byte | W            |

| 1   | 1          | High byte               | Н            |

/QDUMP is high when the 8086/8088 has just emptied its queue and pulled in the first byte (or bytes) of the next instruction.

In the PM 107, BHE is permanently set low while CODE-FETCH is low.

Caution must be applied in using /QDUMP for word recognition. This is because the coincidental occurrence of a /QDUMP and an interrupt will generate QFIL? indications in the STATUS column of the absolute display, while the word recognizer sees these QFIL?s as /QDUMPs.

**R/W [LST-F].** When [CODEFETCH] is low, this line indicates whether the current operation is a memory or inputoutput read or write. When [CODEFETCH] is high, this line will be high when the last byte executed out of the instruction stream queue of the 8086/8088 was the first byte (opcode) of an instruction.

**M**/IO [2LS-F]. When [CODEFETCH] is low, this line indicates whether the current operation was a memory access or an input-output access. When [CODEFETCH] is high, this line is high when the second-to-last byte executed out of the instruction stream queue was the first byte (opcode) of a new instruction, a Fetch.

#### Note

The preceeding four lines are stored in the acquisition memory and are therefore available for absolute and mnemonic display. The following two lines are not stored and are not available for display purposes.

MIN/MAX MODE. This signal can be used for locating and analyzing transitions between minimum and maximum modes in systems which are capable of dynamically switching between them, and for finding glitches on this line in a system which is supposed to be operating continuously in one of them. In either case, the trigger section, user clock qualification delay-by field should be set to 0. Note, however, that this will cause incorrect mnemonic disassembly because extra cycles will be stored.

HOLD ACK. This line goes high whenever the 8086/8088 grants a request in response to an external HOLD in the minimum mode or request grant 0 or request grant 1 in the maximum mode.

Setting this line in the word recognizer to 1, the trigger delay-by field in the user clock qualification area to 0, and C8 and C9 in the user clock synthesis field to X, can give information about the bus traffic occurring during a time when another device has been granted the bus.

**QLEVEL.** This is an octal field which can be set to recognize any queue level from 0 to 6 in the PM 106, and 0 to 4 in the PM 107.

**IRQ.** This line is an ORed combination of INTR and NMI. (It indicates the request for an interrupt, not the acknowledgment.)

**EXT TRIG IN.** This line is from the TRIG IN jack on the logic analyzer.

#### **Qualify Command**

Qualifying on [CODEFETCH] alone will produce correct disassembly and is extremely useful. However, excessive use of data qualification can prevent meaningful mnemonic disassembly because the disassembly process requires continuous instruction code data.

#### **Trigger Commands**

. .

**User Clock Qualification.** The default values are FALL-ING EDGE OF CLOCK and Xs for the C9-C4 ANDed clocks field.

The ANDed clocks are used to only clock data into memory on cycles in which these lines match the user defined values. Changing them from the default value of X (don't care) may cause incorrect disassembly. The C9-C4 (ANDed clocks) correspond to the following control lines.

| Line | Name                 |

|------|----------------------|

| C9   | WAIT                 |

| C8   | T1 (Machine State 1) |

| C7   | HOLDACKnowledge      |

| C6   | CODEFETCH            |

| C5   | HOLDACKnowledge      |

| C4   | MIN/MAX              |

. .

User Clock Synthesis. The default values are DELAY CLOCK BY 2, C6=X, C8=0, C7=X, and C9=0. These values cause storage on the falling edge of clock cycle T3, which is when data and status lines are valid. Use of any other values may disrupt mnemonic disassembly.

Entering a delay-by-0 allows storage of data on every clock pulse. Using a delay-by-0 is important for capturing events which do not last through other machine states. However, using delay-by-0 produces redundant data and produces meaningless information in the mnemonic mode.

HALTing the System Under Test. The PM 106/107 contains an optional HALT feature which allows the user to stop the program when a trigger occurs. If the strapping is altered to include this feature, selection of SYSTEM UNDER TEST HALT in the trigger section causes the PM 106/107 to put a pulse on the Request Grant (or Hold) line, stopping the microprocessor. When the processor has stopped, it puts a grant signal on the same line from which it received the request. The processor will then interpret the next pulse on that line as a release. It will not be able to distinguish another request (from some other device) from a release coming from the 7D02.

For example, the 7D02 Logic Analyzer requests the bus when the acquisition memory is full. The 8086/8088 grants it. The 7D02 sends a release when the START button is pushed again. If the processor has been reset before the release comes, the processor will begin running again. The release from the 7D02 START command then will cause the 8086/8088 to stop instead of start.

Because misuse of this feature can cause bus contention in a user's system, the PM 106/107 comes with jumper straps in place which disable it. If, after reading and appreciating the significance of this explanation of the dangers and difficulties of using the HALT function, the reader wishes to use it, refer to the Troubleshooting and Maintenance section of this manual for information on strapping and how to change it.

If a LOCKed instruction sequence is occurring when the 7D02 requests the bus as part of a HALT sequence, the 8086/8088 will not grant the bus until that instruction sequence has been completed. In the case of a LOCKed REPEated instruction, this may be many machine cycles.

#### **Triggering Past a Loop**

Triggering on an event which occurs just past a loop is likely to occur on the first time through the loop rather than on the last time. This is because the 8086/8088 is pre-fetching instructions into the instruction stream queue. The 7D02

sees the instruction when it enters the queue, not when it leaves it. An instruction just past a loop is therefore seen every time the end of the loop is approached, not only when it is actually executed.

The simple solution is to trigger on an instruction more than the maximum queue level beyond the loop (6 for the 8086, 4 for the 8088). This simple solution does not work for complicated cases, such as nested loops or loops and jumps in very close proximity. The /QDUMP line in the word recognizer can be used to determine when an opcode has been reached by a jump rather than by being pre-fetched.

#### **Absolute Data Displays**

**PM 106/107 Differences.** The DATA column of the display is one byte wide for the PM 107, two bytes wide for the PM 106. The PM 106 display therefore includes a column which indicates with an H, an L, or a W which byte or bytes are valid.

Default Radices. All radices default to hexadecimal.

**DATA Field (PM 106 Only).** Data associated with even addresses appears on the right of the data display. Data associated with odd addresses appears on the left side of the DATA column of the display. Refer to H, L, W (PM 106 only) following.

**Control Line Interpretation.** Table 2-2 defines the significance of the major control lines and the corresponding STA-TUS indications in the absolute mode.

**LST-F.** This indication, called last fetch, means that the last byte executed out of the queue was the first byte of an instruction.

**2LS-F.** This indication, called second-to-last fetch, means that the second-to-last byte executed out of the queue was the first byte of an instruction.

**L&2LS.** This indication, called last and second-to-last, means that both the last and the second-to-last bytes executed out of the queue were the first bytes of instructions. (The first of these instructions must have only been one byte long.)

**QFILL.** This indication, queue fill, means that the third-, fourth-, fifth-, or sixth-to-last byte executed out of the queue was the first byte of an instruction.

| ABSOLUTE STATUS DERIVATION |                            |                          |                  |                    |  |  |  |

|----------------------------|----------------------------|--------------------------|------------------|--------------------|--|--|--|

| <b>Name -</b><br>Line      | <b>[CODE FETCH]</b><br>/C2 | <b>M/IO[2LS-F]</b><br>C1 | R/W[LST-F]<br>C0 | BHE[/QDUMP]<br>A20 |  |  |  |

| I/O W <sup>a</sup>         | 0                          | 0                        | 0                | 0                  |  |  |  |

| I/O W                      | 0                          | 0                        | 0                | 1                  |  |  |  |

| I/O R                      | 0                          | 0                        | 1                | 0                  |  |  |  |

| 1/0 R                      | 0                          | 0                        | 1                | 1                  |  |  |  |

| MEM W                      | 0                          | 1                        | 0                | 0                  |  |  |  |

| MEM W <sup>b</sup>         | 0                          | 1                        | 0                | 1                  |  |  |  |

| MEM R                      | 0                          | 1                        | 1                | 0                  |  |  |  |

| MEM R                      | 0                          | 1                        | 1                | 1                  |  |  |  |

| /QDUMP                     | 1                          | 0                        | 0                | 0                  |  |  |  |

| QFILL                      | 1                          | 0                        | 0                | 1                  |  |  |  |

| ?(error)                   | 1                          | 0                        | 1                | 0                  |  |  |  |

| LST-F                      | 1                          | 0                        | 1                | 1                  |  |  |  |

| ?(error)                   | 1                          | 1                        | 0                | 0                  |  |  |  |

| 2LS-F                      | 1                          | 1                        | 0                | 1                  |  |  |  |

| ?(error)                   | 1                          | 1                        | 1                | 0                  |  |  |  |

| L&2LS                      | 1                          | 1                        | 1                | 1                  |  |  |  |

Table 2-2 ABSOLUTE STATUS DERIVATION

<sup>a</sup> This case is displayed as HALT if A0 = 1 (PM 106 only).

<sup>b</sup> This case is displayed as INTA if A0 = 1 (PM 106 only).

**QFIL?.** This indication occurs following the coincidental occurrence of a /QDUMP and an interrupt acknowledge. A queue fill is actually occurring, but the word recognizer will see a /QDUMP.

/QDUMP. This indicates a clearing of the queue caused by an interrupt, a RET, a CALL, or a JMP command. (The word recognizer will trigger on this for QFIL?s also.) /QDUMPs are only displayed on CODEFETCH cycles.

H, L, W (PM 106 only). These indications to the right of the STATUS column in PM 106 displays indicate which bytes of data are valid. H means that only the high byte, the one on the left, is valid. L means that only the low byte, the one on the right, is valid. The invalid byte shows data that happens to be on the bus at the time.

When [CODEFETCH] is high, a low on the A0 line means that the data should be interpreted as a full word (high and low bytes); when A0 is high only the high byte is valid.

When [CODEFETCH] is low, Table 2-3 indicates which bytes are valid.

Table 2-3 BYTE VALIDITY

| BHE | A0 | Valid                   | Displayed As |

|-----|----|-------------------------|--------------|

| 0   | 0  | Low byte                | L            |

| 0   | 1  | Low byte<br>Error       | ?            |

| 1   | 0  | Both bytes              | W            |

| 1   | 1  | Both bytes<br>High byte | н            |

**Q.** This column of the display indicates the instruction stream queue level after the current bytes were pulled in and any executions out have occurred. The maximum queue level is 6 for the 8086 and 4 for the 8088.

I. This column indicates an interrupt request with a 1. (An interrupt request is caused by either INTR or NMI.)

#### **Mnemonic Data Displays**

**Radices.** All radices are hexadecimal and cannot be changed in the mnemonic mode.

ADDRESS. The mnemonic display generated by the PM 106 will occasionally contain two lines and two addresses

#### Operating Instructions-PM 106/107

### Scan by Zenith

associated with one location number. This occurs whenever either of the bytes at that address is an opcode, the first byte of an instruction. The second address which is displayed never actually occurs on the bus; it is displayed for convenience.

**DATA.** In the mnemonic mode the PM 106 data display only contains relevant bytes of data. Bytes which were defined as invalid by BHE and A0 have been removed.

**Multiple Lines at One Location.** When one or two bytes at one location is an opcode, the first byte of an instruction, the mnemonic for that byte is displayed on a separate line of the display. (It is not possible to trigger on this address, since it does not appear on the bus.) Successive bytes of the same instruction are shown as CODEFETCHs with their hexadecimal value.

Because there is one instruction, TEST, whose operands may not fit on one line, there may sometimes be as many as three lines of display associated with one location.

Question Marks in the Display. When a ? appears between the address and mnemonic in the display it means an opcode may not have been executed. The PM 106 ascertains this by tracking the opcode through the queue until it is executed or a queue dump or the end of memory is found. If the queue dump or end of memory is found first, the ? is displayed. (Refer to the example programs toward the rear of this section.)

Asterisks in the Display. Asterisks in the OPERATION column indicate an illegal opcode, a legal opcode with an illegal operand, or insufficient data for the operand.

When an illegal opcode or operand occurs, three asterisks are displayed in place of the mnemonic and the hexadecimal value of the questionable instruction byte is displayed in parentheses.

When a queue dump or the end of memory occurs before the operand data is completely pulled into the queue, asterisks appear in the display (along with a question mark) in the operand field. The question mark appears before the mnemonic.

**Missing Mnemonics.** If an illegal opcode is executed, mnemonics for some opcodes may be missed. Due to the pre-fetch nature of the 8086/8088, the PM 106/107 may not disassemble the next opcode or opcodes. A similar lack of disassembly can occur at the beginning of memory if no LST-F, 2LS-F, or /QDUMP occurs for the opcode of the missing mnemonic.

**INTA.** This interrupt acknowledge indication occurs when there is a memory write with BHE and A0 high. No data is displayed.

**HALT.** This system halted indication occurs when there is an input-output write with BHE low and A0 high. No data is displayed.

**CODEFETCH.** This indication of instruction code occurs whenever CODEFETCH is high but the byte involved is not an opcode (the first byte of an instruction).

**No Disassembly.** This can occur when disassembly is impossible because a sequence of code as long as the 7D02 acquisition memory contains no instructions which generate a queue dump and no LST-F or 2LS-F occurs. No disassembly occurs as a result of certain types of user clock qualification or very long programs with a consistently high queue level and no transfers of control.

#### **Mnemonic Format Differences (using Intel format)**

**B** Suffixes. Many Intel mnemonics will appear on the logic analyzer display with a B suffix. This is additional information which distinguishes mnemonics which are applied to bytes from those which are applied to words. For example, ADC is Add-with-carry-word, while ADCB is Add-with-carrybyte.

**# Prefixes.** Many Intel mnemonics will sometimes appear with a **#** in front of an operand. This means that operand is an immediate operand.

**Brackets** []. Brackets have two uses: they surround all indirect operands and they also appear around registers used in indexed addressing.

**CS:**, **ES:**, **DS:**, **and SS: Locations.** In the PM 106/107 format these precede the instruction, coming on the line before, rather than showing up in the operands.

The S suffix indicates that an inter-segment instruction is being used.

#### A Note on IRQ Information

IRQ information is only displayed in the absolute mode, where it appears in the column labeled I.

#### Immediate - Display - Program

If this sequence of 7D02 commands is performed too quickly by the operator it may not result in a change of mode. This occurs because the display length must be increased after the IMMEDIATE button is pushed but before the PROGRAM button is. This problem is easily remedied by simply repeating the sequence of commands more slowly.

#### Examples

An 8088 Example. To illustrate the operation of the instruction stream queue and the method used by the 7D02 and PM 107 to disassemble it, the following example program is used.

| Address | Code  | Mnemonic  |

|---------|-------|-----------|

| 500     | 90    | NOP       |

| 501     | F6 E6 | MULB DH   |

| 503     | EB FB | JMP 00500 |

| 505     | 60    | XX        |

| 506     | 90    | XX        |

| 507     | 90    | XX        |

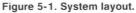

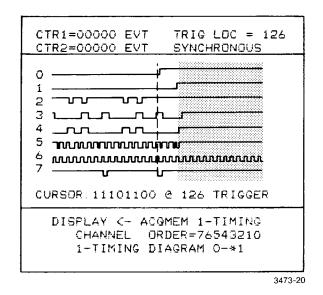

When the logic analyzer is triggered on the first address of this subroutine, using 00500 in the address field and Xs everywhere else, the following is the display of the data in the absolute mode.

|     | i=00000 |        | IG LOC = |        |

|-----|---------|--------|----------|--------|

| CRI | 2=00000 | EVI IR | IG IN TE | 5{ 1   |

| LOC | ADDRESS | 5 DATA | STATUS   | QΙ     |

| Ţ   | 00500   | 90     | QDUMP    | 10     |

| 016 | 00501   | F6     | LST-F    | 10     |

| 017 | 00502   | E6     | L&2LF    | 10     |

| 018 | 00503   | EB     | 2LS-F    | 10     |

| 019 | 00504   | FB     | 2LS-F    | 20     |

| 020 | 00505   | 60     | 2LS-F    | 30     |

| 021 | 00506   | 90     | 2L.SF    |        |

| 022 | 00507   | 90     | 2LS-F    |        |

| 023 | 00500   | 90     | QDUMP    |        |

| 024 | 00501   | F6     | LST-F    | 10     |

| 025 | 00502   | E6     | L&2LF    |        |

| 026 | 00503   | EB     | 2LS-F    |        |

| 027 | 00504   | FB     | 2LS-F    |        |

| 028 | 00505   | 60     | 2LS-F    |        |

| 029 | 00506   | 90     | 2LS-F    | • -    |

| 030 | 00507   | 90     | 2LS-F    |        |

| 031 | 00500   | 90     | QDUMP    |        |

| 032 | 00501   | F6     | LST-F    |        |

| 033 | 00502   | E6     | L&2LF    | 1 0    |

| DIS | PLAY <- | ACQMEM | 0-MAIN   |        |

|     | O-ABSOL |        |          |        |

|     |         |        |          |        |

|     |         |        |          | 3473-0 |

3473-02

Figure 2-1. Absolute display of example program - 8088.

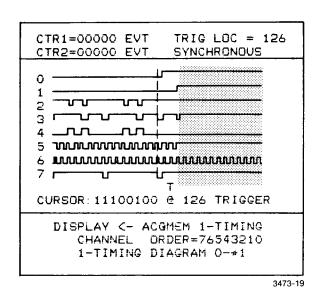

Notice that at the trigger location (the location which would be numbered 15), the first byte of our sample program appears along with a /QDUMP status indication which tells us that the queue was emptied at this point, just before the first byte of our program was pulled in. Consequently, the queue level, in the second column from the left, is now 1. Refer to Figure 2-1. Refer also to Figure 2-2, which illustrates the operation of the queue and can be used as a mental aid in figuring out how the PM 106 locates opcodes for disassembly.

At location 016 the next byte of the program has been pulled into the queue and the LST-F indication is telling us that the last byte executed out of the queue, 90, was an opcode. We know this because only one byte was executed and the absolute data display (refer to Figure 2-1) shows a LST-F in the status column.

At location 017 the next byte of our program appears in the DATA column of Figure 2-1 along with a 2LS-F indication in the status column. Notice, in Figure 2-2, that the queue level is 1. Therefore, we know that this byte is now the only one in the queue. The L&2LF indicates that the last and second-to-last bytes executed were both opcodes (the first bytes of an instruction). They are circled in Figure 2-2 to indicate that this location is the one at which the fact that these bytes are opcodes is established. With one byte entering the queue and the same level in the queue, one byte must have been executed.

#### NOTE

An opcode is the first byte of an instruction. Its location is identified by LST-F, 2LS-F, and L&2LF indications in the absolute display and is shown as its mnemonic in mnemonic data displays. Subsequent bytes are identified in the mnemonic display by CODEFETCH in the OPERATION column.

At location 018 a 2LS-F (second-to-last fetch) indicates that the byte which is 2 bytes plus the queue level bytes back must have been an executed opcode. One byte is pulled in each cycle and the queue level rose from 1 to 2, indicating that no bytes were executed this cycle. Counting back 2 + 1 bytes identifies the F6 at location 16 as the fetch. This is the same byte identified last time. The queue is being filled, but nothing is being executed out because of the time required by the execution unit (EU) for the multiplication operation.

At location 019 we have another 2LS-F status indication and the queue level has risen to 2. The EU is still busy with the multiplication operation.

At location 20 the queue level column in Figure 2-1 has risen to 3. Since one byte is pulled into the queue on each execution cycle, this indicates that no byte was executed out of the queue.

| 7D02 MEMORY<br>LOCATION NUMBER    |      | 15             | 16                     | 17       | 18                 | 19     | 20      | 21                           | 22   | 23             | 24  | 25   |

|-----------------------------------|------|----------------|------------------------|----------|--------------------|--------|---------|------------------------------|------|----------------|-----|------|

|                                   | ( IN | -              | -                      | -        | -                  | -      | -       | 90                           | Ŧ    | -              | -   |      |

| 8088 QUEUE<br>CONTENTS            |      | -              | -                      | -        | -                  | -      | 60      | 60                           | 90   | -              | -   | -    |

| CONTENTS                          | 1    | -              | -                      | -        | -                  | FB     | FB      | FΒ                           | 90   | -              | -   | -    |

|                                   | LOUT | 90†            | F6                     | E6       | EB                 | EB     | EB      | EB                           | 60   | 90†            | F6  | E6   |

| LAST FETCHED<br>(LST-F)           |      | ?              | 90*                    | F6*      | E6                 | E6     | E6      | E6                           | FB   | -              | 90* | F6*  |

| SECOND-TO-LAST<br>FETCHED (2LS-F) |      | ?              | ?                      | 90**     | F6**               | F6**   | F6**    | F6**                         | EB   | -              | -   | 90** |

| THIRD-TO-LAST<br>FETCHED          |      | ?              | ?                      | ?        | 90                 | 90     | 90      | 90                           | E6   | -              | -   | -    |

| FOURTH-TO-LAST<br>FETCHED         |      | ?              | ?                      | ?        | ?                  | ?      | ?       | ?                            | F6   | -              | -   | -    |

| NUMBER OF<br>BYTEG EXECUTED       |      | ? <sup>D</sup> | 1                      | 1        | 1                  | 0      | 0       | 0                            | 2    | ? <sup>D</sup> | 1   | 1    |

|                                   |      | * Ider         | ntified a<br>ntified a | as first | byte of<br>byte of | an ins | tructio | n by Q<br>n by LS<br>n by 2L | ST-F |                |     |      |

|                                   |      | GUC            |                        | p 000    |                    |        |         |                              |      |                |     | 347  |

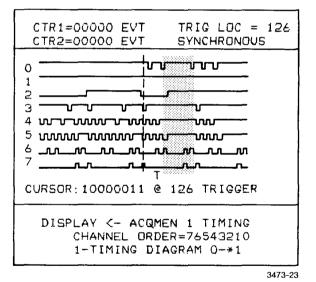

Figure 2-2. Queue status during example program execution - 8088.

We can continue using this process to locate and identify opcodes, but once the PM 106/107 finds the beginning of one instruction by using this method, the beginning of the next instruction is found from the number of bytes associated with the last instruction.

In location 20 of Figure 2-3, note the triple asterisks where the mnemonic would appear. These indicate that the 60 shown in parenthesis was an illegal opcode. Examination of locations 21 through 23 in Figures 2-1 and 2-2 reveals that this byte of code is never executed; rather, it is dumped along with two 90s at location 23.

The 90s which entered the queue at locations 21 and 22 in Figure 2-1 are not displayed as NOPs, as was the one at location 15, but rather they appear as 90 CODEFETCH in Figure 2-3. This is because the number of bytes which were part of the illegal opcode is not known.

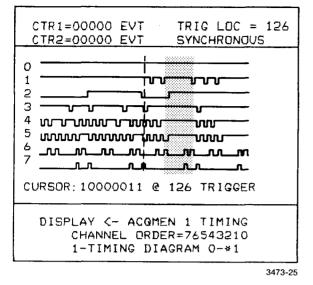

An 8086 Example. The following example illustrates the operation of an 8086 instruction stream queue and the method used by the 7D02 and the PM 106 to perform disassembly.

| Address | Code  | Mnemonic  |

|---------|-------|-----------|

| 100     | 90    | NOP       |

| 101     | F6 E6 | MULB DH   |

| 103     | EB FB | JMP 00100 |

| 105     | 60    | XX        |

| 106     | 90    | XX        |

| 107     | 90    | XX        |

|            | O EVT TRIG  |           |

|------------|-------------|-----------|

| CR12=0000  | O EVT TRIG  | IN IESI 1 |

| LOC ADDRES | S OPERATI   | ON        |

| T00500     | NOP         |           |

| 016 00501  | MULB DH     |           |

| 017 00502  | E6 CODE     | FETCH     |

| 018 00503  | JMP 00500   |           |

| 019 00504  | FB CODE     | FETCH     |

| 020 005057 |             |           |

| 021 00506  | 90 CODE     | FETCH     |

| 022 00507  | 90 CODE     | FETCH     |

| 023 00500  | NOP         |           |

| 024 00501  | MULB DH     |           |

|            | E6 CODE     | FETCH     |

|            | JMP 00500   |           |

|            | FB CODE     | FETCH     |

| 028 00505? |             |           |

|            | 90 CODE     |           |

|            | 90 CODE     | FETCH     |

| 031 00500  |             |           |

| 032 00501  |             |           |

| 033 00502  | E6 CODE     | FETCH     |

| DISPLAY <  | - ACOMEM 0- | MATN      |

| 1-MNEM     |             |           |

|            |             |           |

|            |             | 3473-04   |

0110 0

Figure 2-3. Mnemonic display of example program - 8088.

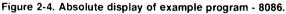

When the logic analyzer is triggered on the first address of this subroutine, Figure 2-4 is the data display in the absolute mode.

We can use the absolute data display and a mental or pictorial construct of the instruction stream queue of the 8086, as shown in Figure 2-5, to understand how the mnemonic display is generated.

At the trigger location, location 15, the first byte of our program, 90, is on the right side of the DATA column. This is address 100. The byte on the left, F6, is from address 101. LST-F (last fetch), 2LS-F (second-to-last fetch), L&2LF (last and second-to-last fetch) and /QDUMP information is available to us from the STATUS column of the display. This information allows us to identify the first and second bytes of our example program as opcodes (the first bytes of new instructions). This is accomplished by locating the byte associated with LST-F indication at location 16 and tracking it backward through the queue. To do this we need to know how many bytes are in the queue now and how many were executed during the last cycle. The Q column provides past and present queue information by noting the change in the queue level from 2 to 3, in locations 15 and 16. Knowing that the 8086 pulled in two bytes, we can find out how many bytes were executed in this case 1.

There were 3 bytes in the queue at the end of the cycle shown in location 16. The LST-F indication in the STATUS column means that the last byte executed out of the queue

|           | 1=00000 EVT  |      |              | -   | )15 | - 1 |

|-----------|--------------|------|--------------|-----|-----|-----|

| CRT       | 2=00000 EVT  | TRI  | G IN TI      | ESI | F 1 | Ľ   |

| LOC       | ADDRESS      | DATA | STATU        | 3   | G   | I   |

| T         | 00100        | F690 | GDUMP        | W   | 2   | 0   |

| 016       | 00102        | EBE6 | LST-F        | W   | З   | Ó   |

| 017       | 00104        | 60FB | 21.SF        | W   | З   | 0   |

| 018       | 00106        | 9090 | 21.SF        | W   | 5   | 0   |

| 019       | 00108        | 9090 | 2LS-F        | W   | 5   | 0   |

| 020       | 00100        | F690 | QDUMP        | W   | 2   | O   |

| 021       | 00102        | EBE6 | LST-F        | W   | З   | 0   |

| 022       | 00104        | 60FB | 2LS-F        | W   | З   | 0   |

| 023       | 00106        | 9090 | 2LSF         | W   | 5   | 0   |

| 024       | 00108        | 9090 | 2LS-F        | W   | 5   | Õ   |

| 025       | 00100        | F690 | <b>QDUMP</b> | W   | 2   | 0   |

| 026       | 00102        | EBE6 | LST-F        | ω   | З   | 0   |

| 027       | 00104        | 60FB | 2LS-F        | Ψ   | З   | 0   |

| 028       | 00106        | 9090 | 2LS-F        | W   | 5   | 0   |

| 029       | 00108        | 9090 | 2LS-F        | ω   | 5   | 0   |

| 030       | 00100        | F690 | QDUMP        | W   | 2   | 0   |

| 031       | 00102        | EBE6 | LST-F        | W   | З   | 0   |

| 032       | 00104        | 60FB | 2LS-F        | W   | З   | 0   |

| 033       | 00106        | 9090 | 2LS-F        | W   | 5   | 0   |

| DIC       | DI AV C- ACO |      | MATH         |     |     |     |

|           | PLAY <- ACG  |      | ne in        |     |     |     |

| · · · · · | O-ABSOLUTE   |      |              |     |     |     |

3473-05

| 7D02 MEMORY<br>LOCATION NUMBER    | _    | 15             | 16  | 17   | 18   | 19               | 20             | 21      | 22   | 23   | 24   | 25             |

|-----------------------------------|------|----------------|-----|------|------|------------------|----------------|---------|------|------|------|----------------|

|                                   | ( IN | -              | -   | -    | -    | -                | -              | -       | -    | -    | -    | -              |

|                                   |      | -              | -   | -    | 90   | 90               | -              | -       | -    | 90   | 90   | -              |

| 8086 QUEUE                        |      | -              | -   | -    | 90   | 90               | -              | -       | -    | 90   | 90   | -              |

| CONTENTS                          |      | -              | EB  | 60   | 60   | 90               | -              | EB      | 60   | 60   | 90   | -              |

|                                   |      | F6             | E6  | FB   | FB   | 90               | F6             | E6      | FB   | FB   | 90   | F6             |

|                                   | Ουτ  | 90†            | F6  | EB   | EB   | 60               | 90†            | F6      | EB   | EB   | 60   | 901            |

| LAST FETCHED<br>(LST-F)           |      | ?              | 90* | E6   | E6   | FB               | -              | 90*     | E6   | E6   | FB   | _              |

| SECOND-TO-LAST<br>FETCHED (2LS-F) |      | ?              | ?   | F6** | F6** | EB**             | -              | -       | F6** | F6** | EB** | -              |

| THIRD-TO-LAST<br>FETCHED          |      | ?              | ?   | 90   | 90   | E6               | -              | -       | 90   | 90   | E6   | -              |

| FOURTH-TO-LAST<br>FETCHED         |      | ?              | ?   | ?    | ?    | F6               | -              | -       | -    | -    | F6   | -              |

| NUMBER OF<br>BYTEG EXECUTED       |      | ? <sup>D</sup> | 1   | 2    | 0    | 2                | ? <sup>D</sup> | 1       | 2    | 0    | 2    | ? <sup>D</sup> |

|                                   |      | ,              |     |      | ,    | an ins<br>an ins |                | n by LS |      |      |      |                |

Queue dump occurred

D

3473-06

#### Operating Instructions—PM 106/107

was the first byte of a new instruction, an opcode. Since two bytes are pulled into the queue whenever there is room (unless there is a JUMP, etc., to an odd address), and the queue level increased by one, we know that only one byte was executed out during this cycle. From this information we can track any particular byte through the queue. For instance, by knowing that only one byte was executed and that the last byte out was an opcode, we can track the 90 that was first in the queue in location 15 to its position as last out in location 16.

At location 17 the queue level has stayed the same while two bytes were pulled in, therefore two bytes must have been executed. With two bytes executed and a 2LS-F indication, it can be seen that the byte which was first in the queue at the beginning of the cycle was the opcode. Recalling that at location 16 we had a queue level of three and two bytes pulled in, the byte which was next out of the queue in location 16 must have been the last one in at location 15, i.e., F6. Therefore the last byte in at location 15 is the one which is indicated as being the opcode by the 2LS-F at location 17.

The PM 106 uses the method described above to establish the location of the first opcode whose location can be found by this method. After that the PM 106 takes a different approach. Once one opcode is located, the next opcode is predicted from the number of bytes required by the previous opcode. Only if an illegal opcode interrupts this process does the the PM 106 revert to the queue tracking method first described.

|                                        | 1=00000 EVT TRIG LOC = 015<br>2=00000 EVT TRIG IN TEST 1 |  |  |  |  |

|----------------------------------------|----------------------------------------------------------|--|--|--|--|

| LOC                                    | ADDRESS OPERATION                                        |  |  |  |  |

| 1                                      | 100100 NDP                                               |  |  |  |  |

|                                        | 00101 MULB DH                                            |  |  |  |  |

| 016                                    | 00102 E6 CODE FETCH                                      |  |  |  |  |

|                                        | 00103 JMP 00100                                          |  |  |  |  |

| 017                                    | 00104 FB CODE FETCH                                      |  |  |  |  |

|                                        | 00105?*** (60)                                           |  |  |  |  |

|                                        | 00106 9090 CODE FETCH                                    |  |  |  |  |

| 019                                    | 00108 9090 CODE FETCH                                    |  |  |  |  |

| 020                                    | 00100 NOP                                                |  |  |  |  |

|                                        | 00101 MULB DH                                            |  |  |  |  |

| 021                                    | 00102 E6 CODE FETCH                                      |  |  |  |  |

|                                        | 00103 JMP 00100                                          |  |  |  |  |

| 022                                    | 00104 FB CODE FETCH                                      |  |  |  |  |

|                                        | 00105?*** (60)                                           |  |  |  |  |

|                                        | 00106 9090 CODE FETCH                                    |  |  |  |  |

|                                        | 00108 9090 CODE FETCH                                    |  |  |  |  |

| 025                                    | 00100 NOP                                                |  |  |  |  |

|                                        | 00101 MULB DH                                            |  |  |  |  |

| 026                                    | 00102 E6 CODE FETCH                                      |  |  |  |  |

| DISPLAY <- ACQMEM 0-MAIN<br>1-MNEMONIC |                                                          |  |  |  |  |

3473-07

Figure 2-6. Mnemonic display of example 08086.

Three asterisks in place of an opcode in the mnemonic data display (see Figure 2-6) indicates an illegal opcode. The number which follows it in parentheses is the illegal code. A question mark before an mnemonic occurs either because of a queue dump, or the end of memory, and indicates that there is uncertainty as to whether or not that byte was ever executed.

A second 8088 example. This second example program illustrates several of the more complex aspects of the mnemonic data display.

| Address | Code        | Mnemonic               |

|---------|-------------|------------------------|

| 480     | E8 7D 00    | CALL 00500             |

| 483     | 81 83 23    | ADD 0123[BP][DI],#4567 |

|         | F7 70 04    |                        |

| 500     | F7 70 24    | DIV 24[BX][SI]         |

| 503     | C3          | RET                    |

| 504     | C7 06 23 00 | MOV 0023,#XXXX         |

Figure 2-7 shows the absolute data display when the logic analyzer is triggered on address 00480. The steady queue level of 1 indicates that one byte is being executed at each location that is not a memory or input-output read or write. Therefore it is easy to see that the LST-F indication at location 16 is identifying the E8 byte that entered the queue at location 15 as the first byte of an instruction. The 2LS-F at location 17 is also identifying the E8 byte from location 15 as the first byte of an instruction. Figure 2-8 shows the status of the queue at these locations.

|     | 1=00000  |     | TR    |     | LOC  |      | 01   | - 1 |

|-----|----------|-----|-------|-----|------|------|------|-----|

| CRI | 2=00000  | EVI | TR    | 16  | TN   | 123  | 5T 3 | L   |

| LOC | ADDRESS  | 3   | DATA  | 5   | GTAT | US   | G    | I   |

| T   | 00480    |     | E8    |     | GDU  | MP   | 1    | 0   |

| 016 | 00481    |     | 7D    |     | LST  | -F   | i    | 0   |

| 017 | 00482    |     | 00    |     | 2LS  | -F   | 1    | 0   |

| 018 | 00483    |     | 81    |     | QFI  | L.L. | 1    | 0   |

| 019 | 00500    |     | F7    |     | QDU  | MP   | 1    | 0   |

| 020 | 007FD    |     | 83    |     | ME   | MW   | 1    | 0   |

| 021 | 007FE    |     | 04    |     | ME   | MW   | 1    | 0   |

| 022 | 00501    |     | 70    |     | LST  | -F   | 1    | 0   |

| 023 | 00502    |     | 24    |     | 2LS  | -F   | 1    | 0   |

| 024 | 00503    |     | СЭ    |     | QFI  | LL   | 1    | 0   |

| 025 | 00024    |     | 50    |     | ME   | MR   | 1    | 0   |

| 026 | 00025    |     | i B   |     | ME   | MR   | 1    | 0   |

| 027 | 00504    |     | C7    |     | QFI  | LL   | 2    | 0   |

| 028 | 00505    |     | 06    |     | GFI  | LL   | З    | 0   |

| 029 | 00506    |     | 23    |     | QFI  | LL   | 4    | 0   |

| 030 | 007FD    |     | 83    |     | ME   | MR   | З    | 0   |

| 031 | 007FE    |     | 04    |     | ME   | MR   | З    | O   |

| 032 | 00483    |     | 81    |     | QDU  | MP   | 1    | 0   |

| 033 | 00484    |     | 83    |     | LST  | -F   | 1    | 0   |

|     |          |     |       |     |      |      |      |     |

| DIS | PLAY <-  | ACQ | 1EM O | -M/ | AIN  |      |      |     |

|     | O-ABSOLI | JTE |       |     |      |      |      |     |

|     |          |     |       |     |      |      |      |     |

3473-08

Figure 2-7. Absolute display of second example program - 8088.

|                                   | 1                | 15             | 16  | 17   | 18 | 19             | 20 | 21 | 22  | 23   | 24 | 25 | 26             | 27 | 28 | 29 | 30 | 31 | 32             |

|-----------------------------------|------------------|----------------|-----|------|----|----------------|----|----|-----|------|----|----|----------------|----|----|----|----|----|----------------|

|                                   | ( IN             | -              | -   | -    | -  | -              | -  | -  | -   | -    | -  | -  | -              | -  | -  | 23 | -  | -  | .              |

| 8088 QUEUE<br>CONTENTS            | Į                | -              | -   | -    | -  | -              | -  | -  | -   | -    | -  | -  | -              | -  | 06 | 06 | 23 | 23 | -              |

|                                   |                  | -              | -   | -    | -  | -              | -  | -  | -   | -    | -  | -  | -              | C7 | C7 | C7 | 06 | 06 | -              |

|                                   | <sup>L</sup> OUT | E8†            | 7D  | 00   | 81 | F7†            | F7 | F7 | 70  | 24   | C3 | C3 | C3             | C3 | C3 | C3 | C7 | C7 | 81†            |

| LAST FETCHED<br>(LST-F)           |                  | ?              | E8• | 7D   | 00 | -              | -  | -  | F7• | 70   | 24 | 24 | 24             | 24 | 24 | 24 | C3 | С3 | -              |

| SECOND-TO-LAST<br>FETCHED (2LS-F) |                  | ?              | ?   | E8** | 7D |                | -  | -  | -   | F7** | 70 | 70 | 70             | 70 | 70 | 70 | 24 | 24 |                |

| THIRD-TO-LAST<br>FETCHED          |                  | ?              | ?   | ?    | E8 | -              | -  | -  | -   | -    | F7 | F7 | F7             | F7 | F7 | F7 | 70 | 70 | -              |

| FOURTH-TO-LAST<br>FETCHED         |                  | ?              | ?   | ?    | ?  | -              | -  | -  | -   | -    | -  | -  | -              | -  | -  | -  | F7 | F7 | -              |