## **TEKTRONIX**®

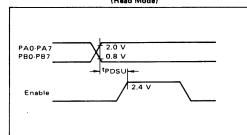

### 067-0746-00 SYSTEM TEST FIXTURE

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077 070-2304-00 Copyright © 1977 by Tektronix, Inc. Beaverton, Oregon. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without permission of Tektronix, Inc.

This instrument, in whole or in part, may be protected by one or more U.S. or foreign patents or patent applications. Information provided on request by Tektronix, Inc., P.O. Box 500, Beaverton, Oregon 97077.

TEKTRONIX is a registered trademark of Tektronix, Inc.

Portions of this manual were reprinted with permission of Motorola, Inc., Phoenix, Arizona.

This manual supports the following versions of this product: B010100 and up

# REV. DATE DESCRIPTION @ 5/77 Original Issue

#### MANUAL REVISION STATUS

i

. -

#### **CONTENTS**

| SECTION 1 | INTRODUCTION                  |

|-----------|-------------------------------|

|           | Overview                      |

|           | Standard Configuration 1-3    |

|           | Available Test Fixture Memory |

|           | Installation                  |

|           | Routine Maintenance 1-4       |

|           |                               |

WARNING

The remaining portion of this Table of Contents lists servicing instructions that expose personnel to hazardous voltages. These instructions are for qualified service personnel only.

**SECTION 2 OPERATION** Getting Started ..... 2-1 Operating Procedures ..... 2-1

| SECTION 3 | CIRCUIT DESCRIPTION         |

|-----------|-----------------------------|

|           | Introduction                |

|           | General                     |

|           | Definitions Of Signal Names |

|           | Circuitry                   |

|           | Block Diagram Overview 3-9  |

|           | Power                       |

**SECTION 4** 6800 MICROCOMPUTER SPECIFICATIONS

- **SECTION 5 REPLACEABLE PARTS**

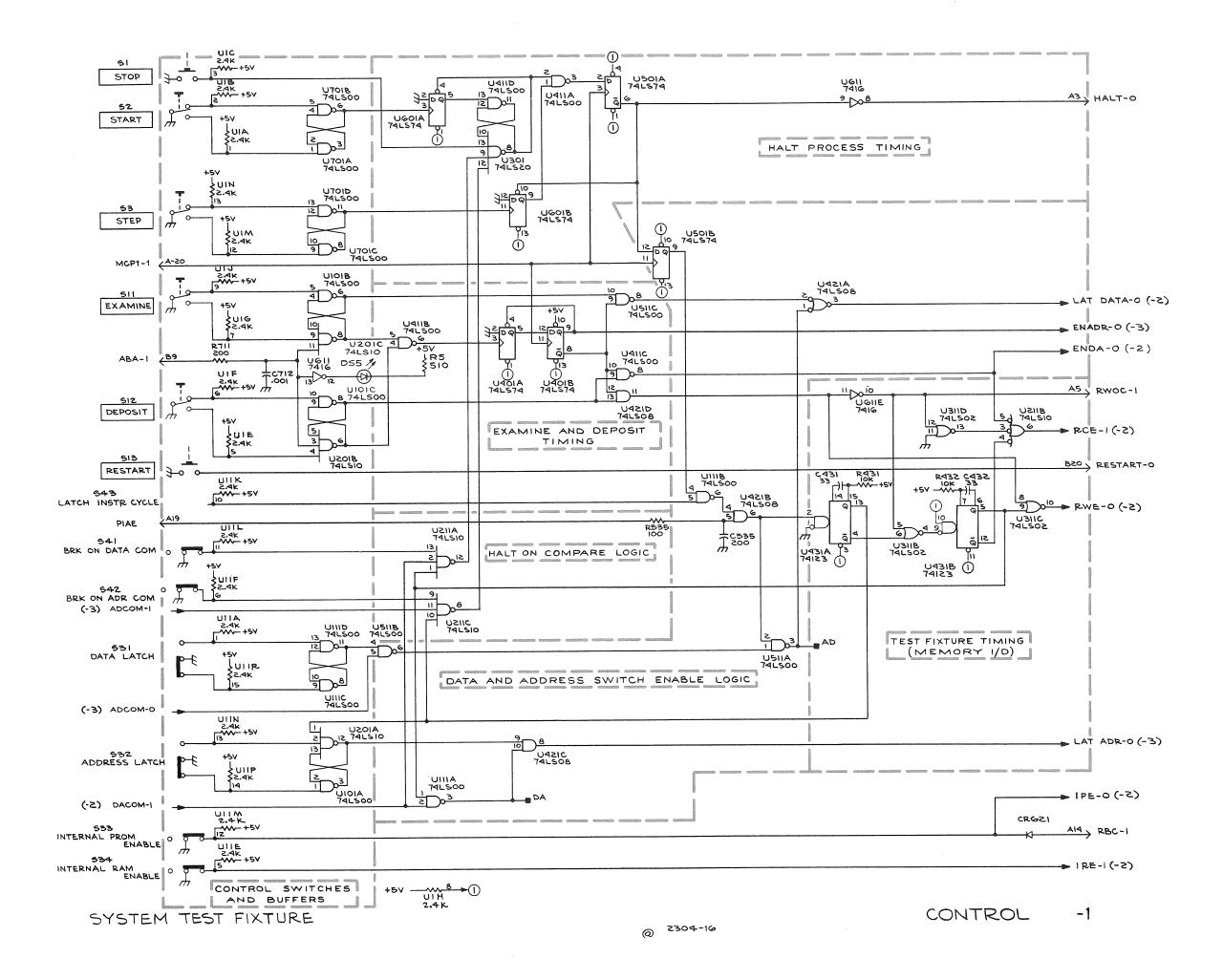

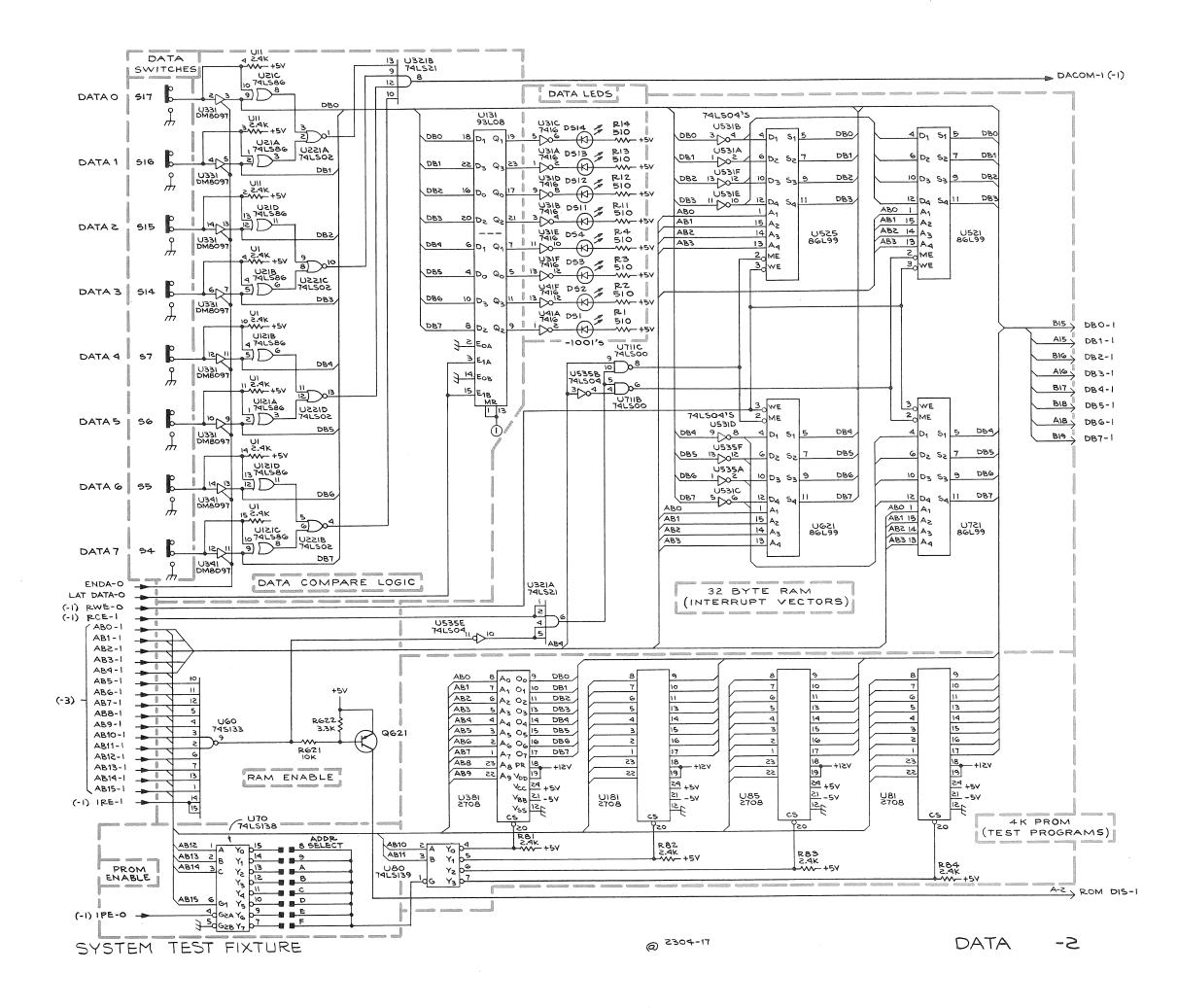

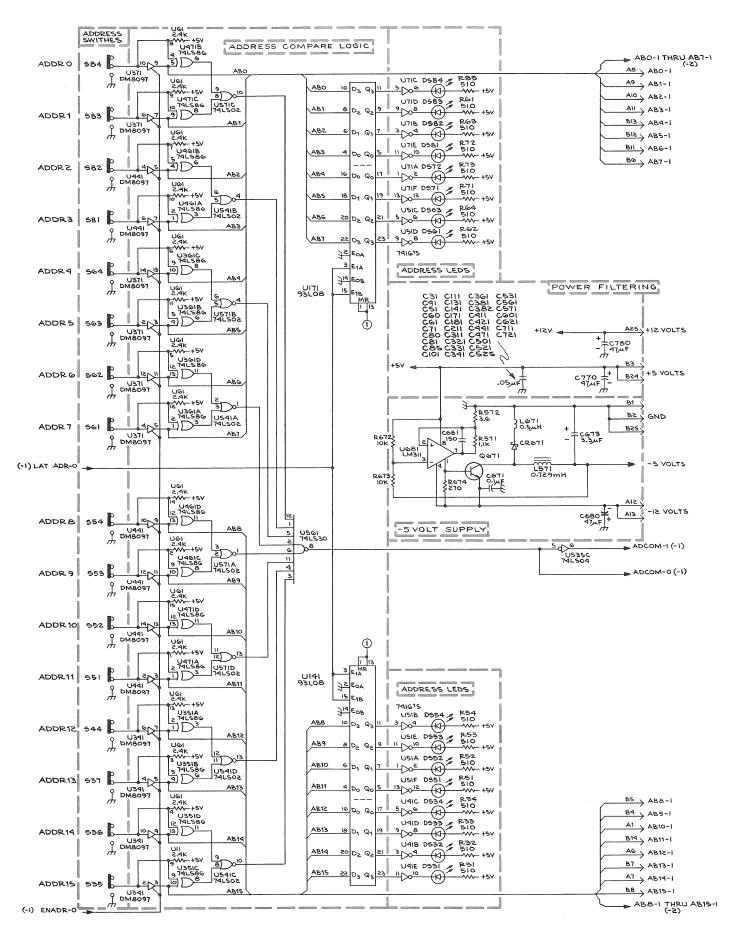

- **SECTION 6 SCHEMATICS**

- **CHANGE INFORMATION**

#### LIST OF ILLUSTRATIONS

Figure Description Page 1-1 067-0746-00 System Test Fixture 1-2 Equipment that can be tested is based on a 6800 microcomputer system ..... 1-2 1-3 Memory address space utilization ..... 1-4 1-4 System Test Fixture installation hardware ..... 1-5 3-1 System Test Fixture showing microcomputer interface 3-2 6800 Microcomputer Block Diagram ..... 3-3 3-3 3-4 EXAMINE and DEPOSIT timing ..... 3-10 3-5 System Test Fixture timing ..... 3-11 3-6 Comparative timing for memory write operations (4051 and System Test Fixture) ..... 3-13

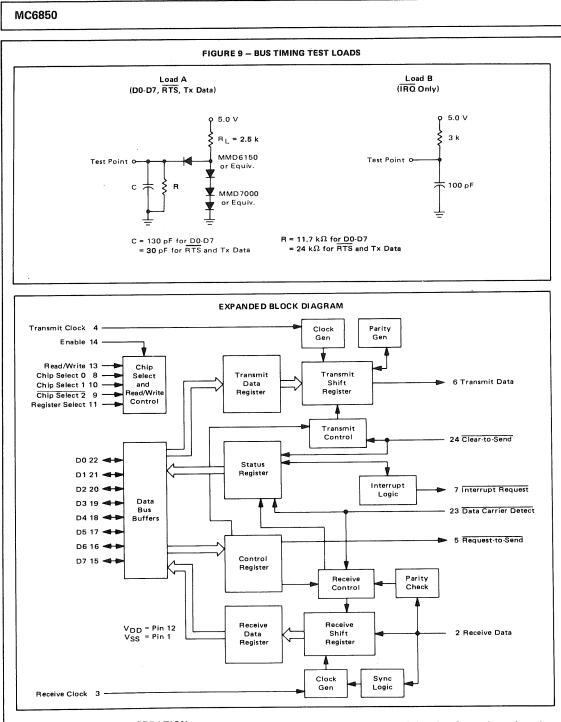

Fig. 1-1. 067-0746-00 System Test Fixture.

#### Section 1

#### INTRODUCTION

#### Overview

The 067-0746-00 System Test Fixture (Fig. 1-1) is a general purpose test device for Tektronix equipment that uses 6800 microprocessors. Several manufacturers make the 6800 microprocessors modeled after a design introduced by Motorola Semiconductor Products, Inc. Due to the sophisticated intelligence offered by these microprocessor devices, Tektronix has developed the System Test Fixture as an aid to troubleshooting these intelligent machines.

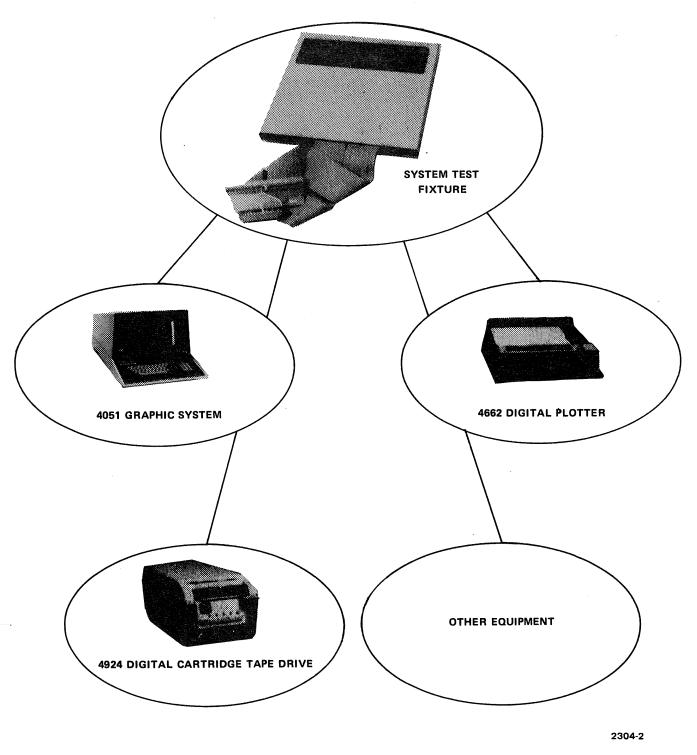

Typical systems offered by Tektronix using 6800 microprocessor technology include computing systems like the 4051 Graphic System, data storage devices like the 4924 tape unit, data display devices like the 4662 Digital Plotter and other equipment (Fig. 1-2), many of which can directly interface with the IEEE-488-1975 Standard Digital Interface for Programmable Instrumentation.

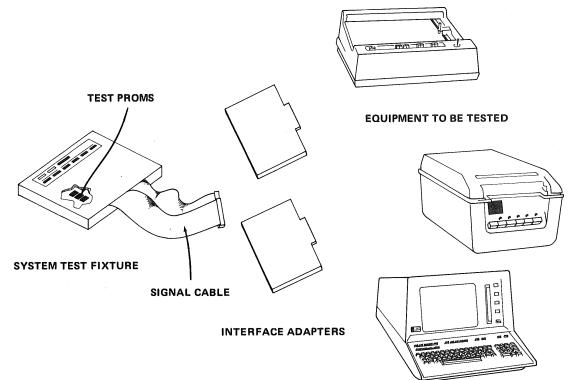

There are optional cables and accessories available to use the System Test Fixture with a number of intelligent systems offered by Tektronix, Refer to the section at the back of the manual that describes the various cables, auxiliary test boards and interface adapters for the various systems.

Microprocessors, when used as controllers for an intelligent device, must be treated much like a computer. The System Test Fixture connects directly to the microprocessor bus and control lines or their buffered equivalent. After the electrical connection is made, System Test Fixture operations closely resemble the control console operations of any mainframe computer system. Binary data can be stored and retrieved from specified addressable locations. Programs can be run. Processes can be stopped and the microinstrucitons can be executed one at a time for each pressing or a switch. Running test programs can also output data to the lights on the System Test Fixture in accordance with procedures dependent upon the operations of the specific test program.

Microprocessor devices residing in the addressable space of 65,536 possible address locations can be of various types. Most of the devices are components directly supported by the manufacturers of the 6800 microprocessors. They include random access memory (RAM) for temporary data storage, read only memory (ROM) for permanent data and program storage, and peripheral interface devices (PIA's and ACIA's) for equipment control and data transfer. Some intelligent systems may even have discrete logics that decode address information, latch data, and perform special operations.

Fig. 1-2. Equipment that can be tested is based on a 6800 microcomputer system.

#### Standard Configuration

The standard configuration of the System Test Fixture contains the test fixture, two ribbon cables and an adapter board for connecting the device to a 4051 Graphic Sytem. Other adapter boards are required if the System Test Fixture is to be used with other equipment. The two PROM devices that come standard with the System Test Fixture contain firmware tests for the 4051 Graphic System.

#### Available Test Fixture Memory

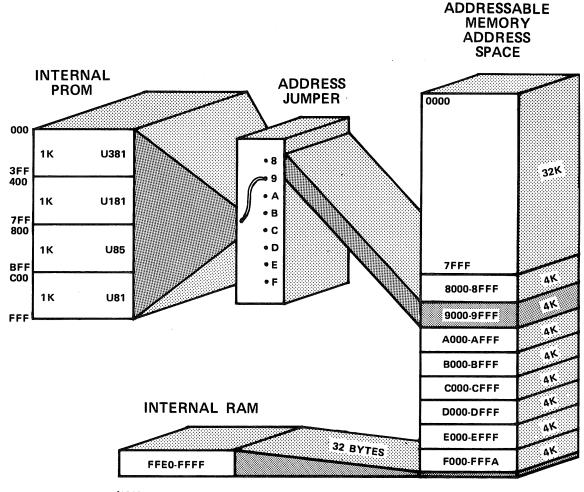

The System Test Fixture contains a possible 4K of programmable read-only memory (PRDM). Within the System Test Fixture, the address strap is set to give the PROM devices an address space in the 4K address region bounded by 9000 and 9FFF (Fig. 1-3). The internal fixture PROMs contain special test programs for the 4051 Graphic System. The strap can be changed to select any 4K address partition in the upper 32K of the microprocessor's 64K address space for PROM addressing.

System test programs can be changed by replacing the existing PROMs in the System Test Fixture with a new set.

The System Test Fixture also contains random access memory (RAM) for the highest 32 memory locations in the microprocessor's 64K address space (Fig. 1-3).

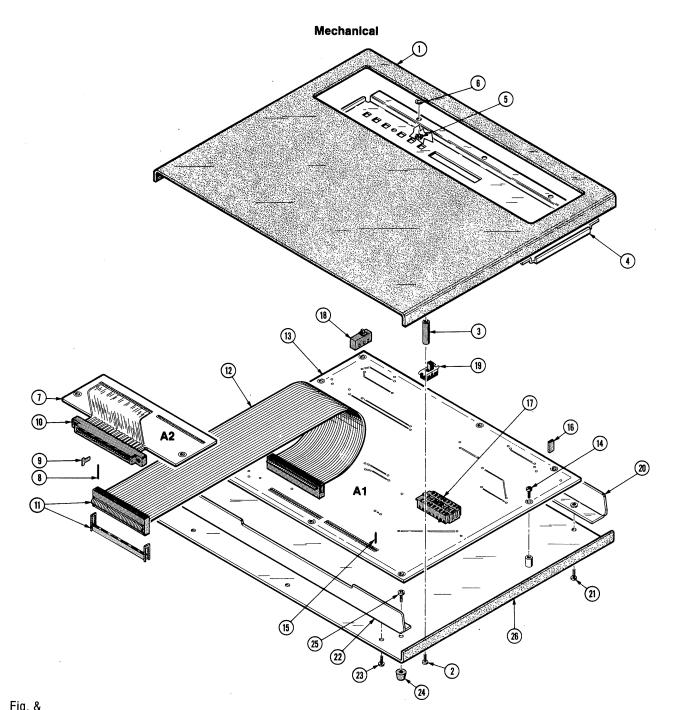

#### Installation

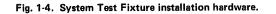

Several devices and systems manufactured by Tektronix utilize the System Test Fixture as part of the standard service equipment. Specific documentation as to the tests performed by the firmware test PROMS can be found in the appropriate service documentation that is available for each respective product. Consult the appropriate service manual for the connecting procedures for your system and the cautions to be taken. Figure 1-4 illustrates some of the devices necessary to make the System Test Fixture usable as a service troubleshooting tool.

(INTERRUPT VECTORS)

2304-3

#### Fig. 1-3. Memory address space utilization.

#### Routine Maintenance

Routine maintenance of the System Test Fixture consists of occasional cleaning. If the electronics are to be serviced, this service should be performed at a static-free work station.

There are no adjustments within the System Test Fixture housing except for the jumper that selects the PROM address space. The PROM address jumper should be set to be compatible with the system (or instrument) being tested.

1-4

#### INTRODUCTION

2304-4

.

#### Section 2

#### OPERATION

#### Getting Started

- 1. Review the service documentation for the equipment to be tested.

- 2. Check to see that the appropriate programs are installed in the System Test Fixture. The test programs are available through the regional field service centers as programmable read only memory (PROM) devices.

- Be sure you have the appropriate interface adapters and cables for the system to be tested.

- 4. Connect the System Test Fixture to your equipment as described in the appropriate service documentation for the equipment to be tested.

#### Operating Procedures

The switches and lamps on the System Test Fixture are used in a manner similar to the control console of a mainframe computer. The switches are used to load and retrieve data to and from memory. The switches are also used to execute programs, provide data input and enable data display operations under program control. Debugging breakpoints that monitor data at specified addresses or address monitoring of specified data values can be implemented by appropriate switch settings.

#### NOTE

If the HAUT line goes active during the last processor cycle of an instruction, one more instruction will be executed before the halt is affected and the microprocessor finally stops.

The switches and indicators perform the following functions.

@

All slide switches

Up = 1 or true Down = 0 or false

#### OPERATION

16 Address Switches

8 Data Switches

STOP

STEP

ABA LED

EXAMINE

DEPOSIT

AB15-AB0 left to right in groups of four switches, AB15 is the most significant and AB0 is the least significant address bit.

DB7-DB0 left to right in two groups of four switches,DB7 is the most significant and DB0 is the least significant data bit.

This signal will cause a HALT signal to be sent to the 6800 microprocessor. After completing the current instruction, the 6800 microprocessor will make the busses available for other uses and assert Bus Available (BA).

Once the microprocessor halts, the STEP switch can be used to step through the microinstructions, one instruction at a time. Each of the instructions may comprise 1, 2 or 3 memory locations (8-bits each).

This lamp turns on when the microprocessor stops and makes the busses available. The microprocessor asserts BA, which is used as ABA meaning the address bus is available.

This switch, when pressed, causes data found at a memory location determined by the address switches to be displayed in the Data LEDs. The microprocessor must be halted in order for this switch to have any affect.

This switch, when pressed, causes data found in the Data Switches to be loaded into the memory location. as determined by the Address

@

DEPOSIT (cont'd)

RESTART

LATCH DATA

LATCH ADDRESS

FIXTURE PROM

FIXTURE RAM

Switches. The microprocessor must be halted in order for this switch to have any affect.

This switch is tied directly to the RESTART line and causes a vectored restart interrupt to occur whenever this switch is pressed.

This slide switch will enable memory address comparison with the Address Switches and will capture the data contents written to or read from that memory location. The data contents will be displayed on the Data LEDS.

This slide switch will enable data comparison with the Data Switches and will capture the address bits that are active when the data comparison is sensed. The captured address is displayed in the Address LEDs. The address displayed is the location where the data was found.

This slide switch activates the INTERNAL PROM ENABLE SIGNAL. As a result, the RBC (ROM BANK CONTROL) signal is made false to disable a 4K byte memory address region in the upper 32K of the equipment under test. The firmware tests stored in the System Test Fixture on programmable read only memory (PROM) are enabled.

This slide switch activates the INTERNAL RAM ENABLE signal. As a result, the ROM DIS signal is asserted to disable the microprocessor interrupt vectors found in the equipment under test. The 32K RAM memory location can then be programmed to contain interrupt and restart vectors used by the PROM test programs.

#### Section 3

#### CIRCUIT DESCRIPTION

#### INTRODUCTION

#### General

The 067-0746-00 System Test Fixture is most effectively understood as a control panel for a 6800 microcomputer system. Using the System Test Fixture, data contents of addressable locations may be changed or examined while the processor is stopped. A restart vector can be executed. Other functions performed by computer control panels can also be performed using the System Test Fixture (see Section 2 on Operation).

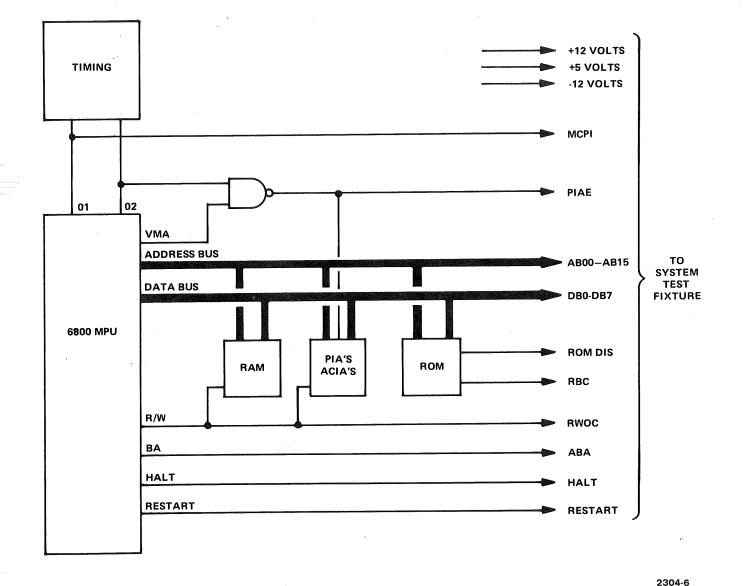

Figure 3-1 shows the System Test Fixture keyboard layout along with signals found on the microcomputer bus cables. Meanings of each signal name are described later. The pushbutton switches (STOP, START, STEP, EXAMINE, DEPOSIT and RESTART) cause the specified operation to be performed. The microprocessor must be stopped and the ABA lamp must be on in order for the STEP, EXAMINE and DEPOSIT switches to have any affect.

The seven function slide switches are to the right of the push-button switches. The microprocessor must be running for these switches, with the exception of INSTR CYCLE, to be useful. The LATCH DATA and LATCH ADDRESS switches enable data bus and address bus contents to be displayed as a program is running. The FIXTURE PROM and FIXTURE RAM switches select internal PROM and internal RAM when on. The BREAK DATA and BREAK ADDR switches forces a microprocessor halt upon a valid data or address comparison. The INSTR CYCLE, when on, allows an instructioon address and OP-CODE information to be displayed when single-stepping through a program of microcode instructions.

The DATA and ADDRESS switches are used to enter values on the microcomputer data bus and address bus. The corresponding LEDs can display data bus and address bus information.

2304-5

Fig. 3-1. System Test Fixture showing microcomputer interface signal lines.

SYSTEM TEST FIXTURE

@

3-2

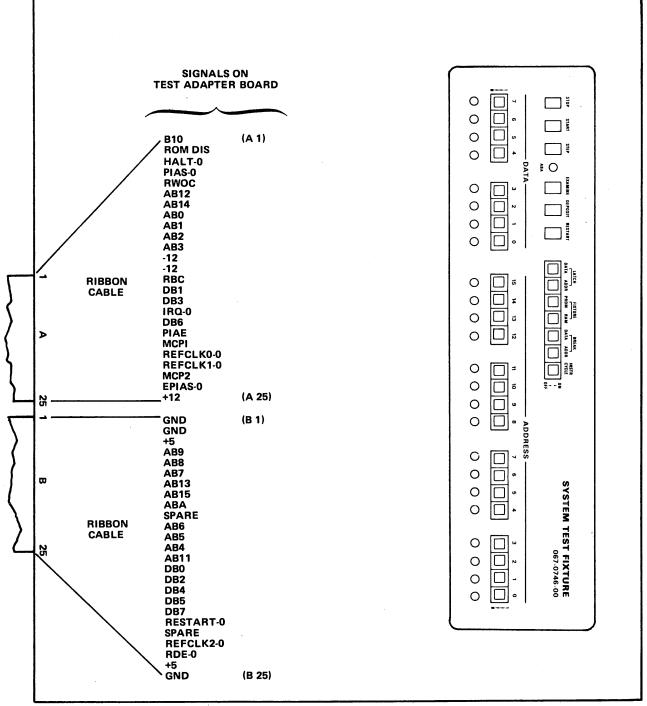

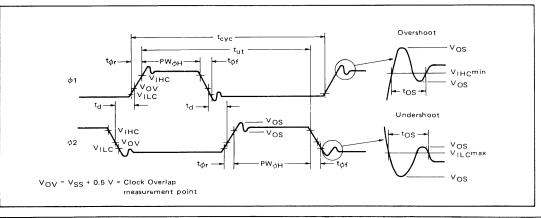

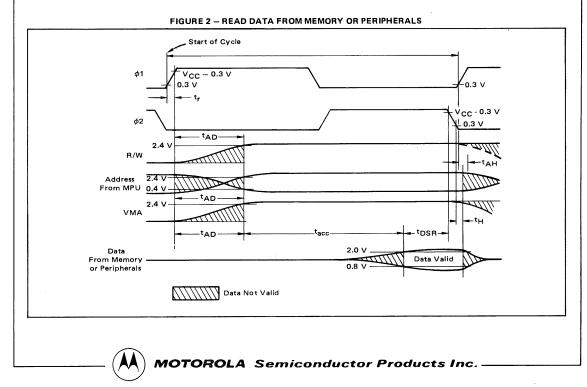

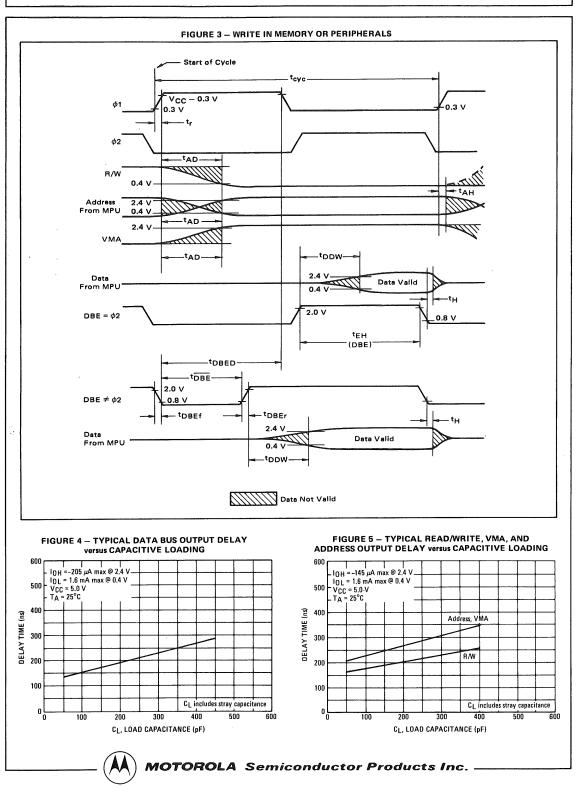

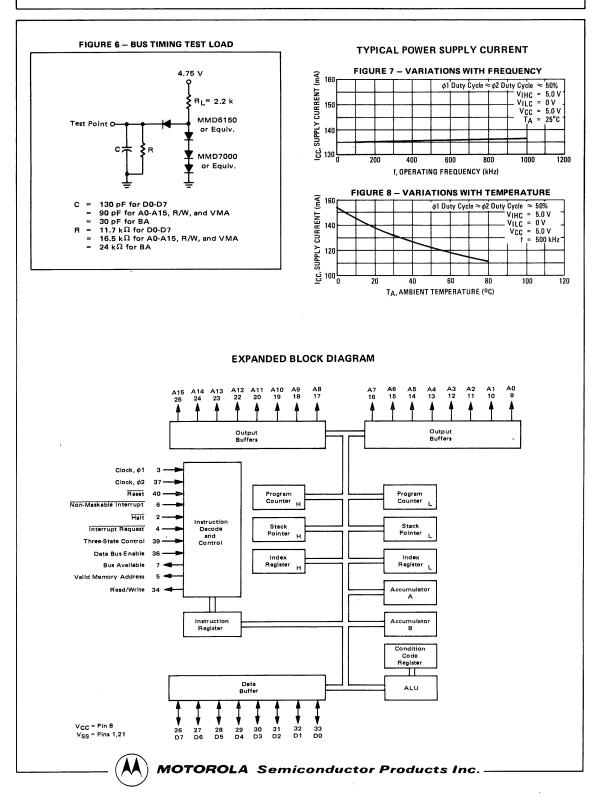

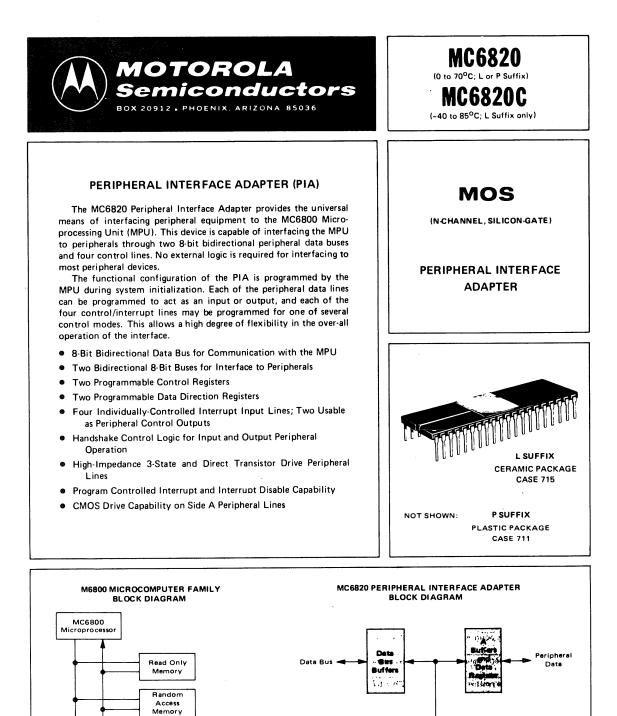

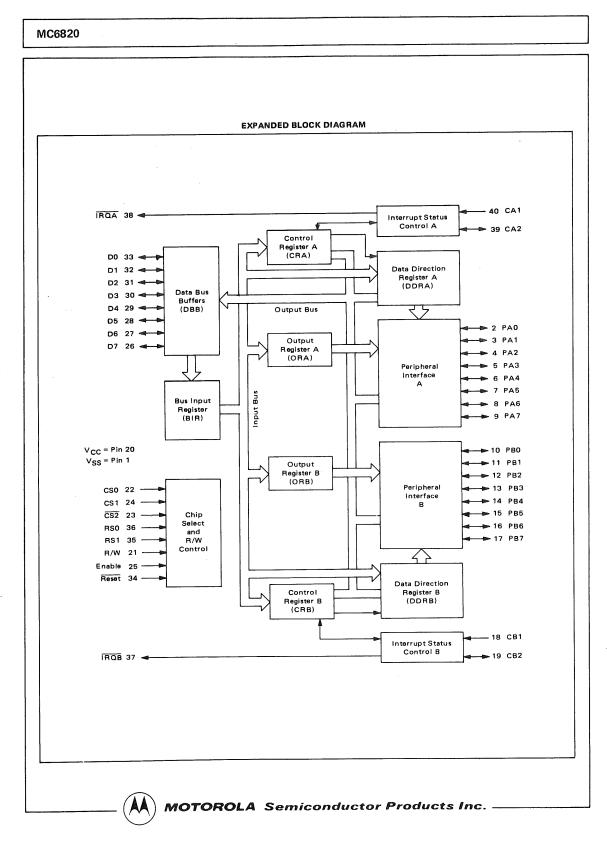

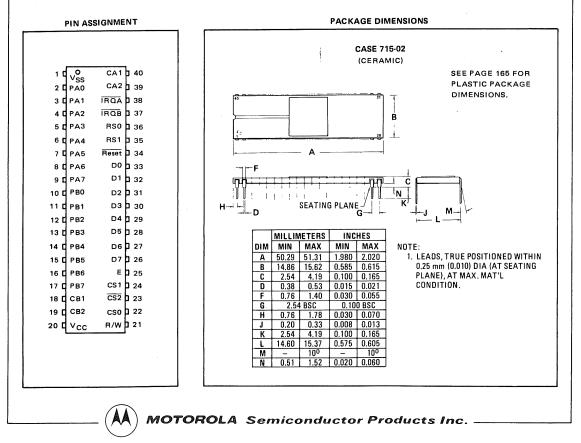

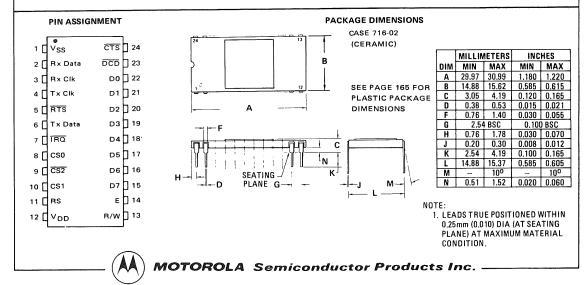

A typical 6800 microcomputer system that can be exercised by the System Test Fixture is shown in fig. 3=2. This illustration shows how the basic interfacing signals used by the System Test Fixture are generated. See the reprinted specification sheets in Section 4 of this manual for detailed 6800 microcomputer system timing and operations. These specifications are reprinted by permission of Motorola Semiconductor, Inc.

Fig. 3-2. 6800 Microcomputer Block Diagram.

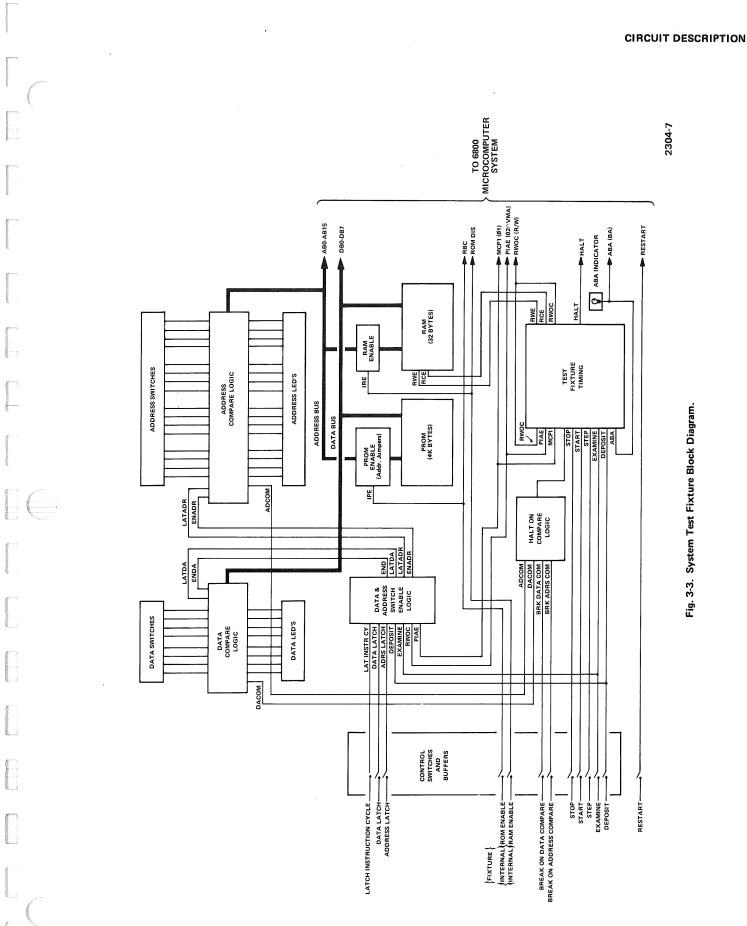

A block diagram of System Test Fixture functions (Fig. 3-3) shows the switches, circuitry being controlled, and the interface lines to a 6800 microcomputer system (Fig. 2). Detailed circuitry of each block in the diagram can be found on the schematics at the end of this section. This block diagram is a convenient map to understanding the internal circuitry of the System Test Fixture. The rest of the documentation in the manual relates to this diagram and functions being performed.

Signal mnemonics found on the schematics and in the text of this manual have the following voltage level interpretation. If the signal name is appended by a dash-one (NAME-1), then the true state of the logic signal is high. If the signal name is appended by a dash-zero (NAME-0), then the true state of the logic signal is low. If a dash-one or dash-zero is missing from a schematic mnemonic, an analog signal is generally assumed. In the text of the manual and tables, the dash-one and dash-zero are often not shown; the true state or false state mentioned for these signals is dependent upon the appended one or zero as found on the schematic diagram.

Definitions Of Signal Names

ABO thru AB15

ADDRESS BUS These signal lines are the address bus that is used by the 6800 microprocessor and its associated memories and peripheral interfaces.

The bus available (BA) on the 6800 microprocessor, when buffered, is used as the source for the ABA

ABA

AD COM

ADDRESS COMPARE This signal is true whenever the address on the address bus matches the data keyed into the Address Switches.

BRK DATA COM BREAK ON DATA COMPARE This signal reflects the state of the BREAK=DATA switch and, when ac= tive, forces a HALT signal whenever the data bus value reflects the pattern set in the Data Switches,

ADDRESS BUS AVAILABLE

@

signal.

@

SYSTEM TEST FIXTURE

3-5

BRK ADRS COM

DA COM

ENADR

ENDA

HALT

IPE

#### BREAK ON ADDRESS COMPARE

This signal reflects the state of the BREAK-ADDRESS switch and, when active, forces a HALT signal whenever the addresses on the address bus reflect the pattern keyed into the Address Switches.

#### DATA COMPARE

This signal is true whenever data on the data hus is the same as data entered into the Data Switches.

#### ENABLE ADDRESSING

The ENADR signal, when true, places the contents of the Address Switches onto the address bus. This allows the System Test Fixture to address any memory location when the microprocessor is stopped. The signal becomes true for one memory cycle when either the EXAMINE or DEPOSIT switches is pressed.

#### ENABLE DATA

The ENDA signal, when true, places the contents of the Data Switches onto the data bus, This allows the System Test Fixture to place data into memory locations and peripheral registers when the microprocessor is stopped.

HALT THE MICROPROCESSOR When this signal becomes true, the microprocessor will stop after completing the instruction in which HALT went true, When HALT goes false, microprocessor operations will again resume.

#### INTERNAL PROM ENABLE

This is the internal programmable read only memory (PROM) enable signal that is activated by a test fixture switch having the same meaning (FIXTURE PROM), This signal activates RBC to disable a bank or ROM within the device under test that occupies the same address

@

IPE (cont<sup>e</sup>d)

IRE

LAT ADR

LAT DATA

PIAE

RBC

space as the test fixture PROMS. The jumper strap should be set such that the fixture PROMS occupy the bank switched address space of the device under test.

#### INTERNAL RAM ENABLE

This is the internal random access memory (RAM) enable signal that is activated by a test fixture switch having the same meaning (FIXTURE RAM). This signal activates ROM DIS to disable the interrupt vector address space within the device under test.

LATCH ADDRESS This signal is activated by the LATCH ADDRESS switch and the data compare signal to strobe the contents of the memory address bus into the Address LEDs.

#### LATCH DATA

This signal is used to strobe the contents of the data bus into the Data LEDs. When the EXAMINE switch is pressed, the data found at the address specified by the Address Switches is displayed. When the LATCH DATA switch is true, data that accompanies the memory address as determined by the Address Switches is displayed whenever the microprocessor addresses the specified memory address location.

PERIPHERAL INTERFACE ADAPTER ENABLE This signal is true if data on the address bus is the same as the pattern found in the System Test Fixture Address Switches,

#### ROM BANK CONTROL

This signal goes false whenever the addresses for the internal PRUMS are activated. The signal is used to disable a memory address space in the device under test and make the addresses available to the Sys-

3-7

RBC (cont'd)

RCE

RESTART

ROM DIS

tem Test Fixture. This provides an area of addresses that can be used by the System Test Fixture firmware.

RAM CHIP ENABLE This signal allows the test fixture or microprocessor to address any of 32 random access memory locations in which temporary interrupt vectors may be stored.

RESTART OR INITIALIZE This signal forces a vectored interrupt to a special test program as determined by the restart interrupt vector (FFFE-FFFF).

ROM DISABLE

This is the read only memory (ROM) disable signal line that is used to disable the ROM containing the interrupt vectors for the processor. The System Test Fixture provides vector address space whenever the internal PAM enable switch is true. The switch, when true, causes the ROM DIS signal to be asserted. The internal RAM occupies the highest 32 memory locations in the 64K address space of the microprocessor.

RAM WRITE ENABLE This signal is true whenever data is to be written to memory by any other peripheral device.

READ/WRITE OUTPUT COMMAND This signal is the system read/write (R/W) signal that is generated by the microprocessor or System Test Fixture.

RWOC

CIRCUITRY

Block Diagram Overview

Refer to the block diagram of Fig. 3-3. The "control switches and buffers" block contains the microprocessor control and function switches. Also included are flip-flops on each switch to keep switching transients out of the internal control circuits.

The "data and address switch enable logic" and the "address compare logic." When ENDA is true, data from the "data switches" can be placed on the data bus (DBO=DB7). When LATDA is true, the contents of the data bus are strobed into a buffer register and displayed on the "data LEDS." Whenever the contents of the "data switches" matches the contents of the data bus, DACOM becomes true.

The "address compare logic" is controlled by LATADR and ENADR and produces ADCOM in much the same way as the "data compare logic" is controlled by LATDA and ENDA and produces DACOM.

The RAM block contains data storage registers to allow the user to modify the interrupt vectors. This data storage is addressed only when IRE is true.

The PROM block contains data storage registers for test programs. This block of memory can be addressed only if IPE is true. The "PROM enable" block contains an address jumper to determine the address space occupied by the PROMS.

HALT requests are generated by the "halt on compare logic" and by pressing the STOP switch.

"Test fixture timing" controls the time sequencing of operations necessary for data transfer operations, halt operations, single instruction execution, and any time-dependent microcomputer interface functions.

#### Power

Power for the System Test Fixture comes from power supplies within the instrument being tested. Required voltages and their usage appear in table 3-1.

@

#### Table 3-1

#### POWER REQUIREMENTS

+5 VOLTS Used by all logic circuits. +12 VOLTS Used by PROM devices. =12 VOLTS Used to generate=5 volt supply for PROMS.

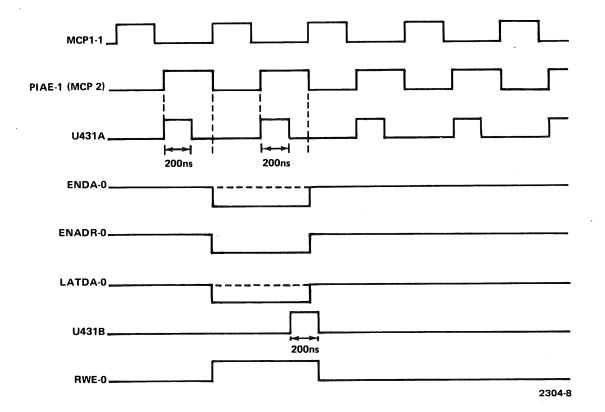

#### Test Fixture Timing

Timing for examine and deposit operations is illustrated in Fig. 3-4. U431A and U431B are two monostable devices shown on the schematic fold-out at the end of this chapter. These devices, along with microprocessor clock signals MCP1 (01) and PIAE (02) are used for System Test Fixture timing clocks. Whenever an EXAMINE or DEPOSIT switch is pressed, the value of ENADR goes true for one microprocessor cycle. If the EXAMINE switch was pressed, the LAT DA line goes true and the contents of the dta bus are strobed into the DATA LEDs. When LAT DA goes false, U431 provides timing for the memory devices. If the DEPOSIT switch was pressed, LAT DA remains false whereas RWE and ENDA go true. This causes data to be strobed into memory via U431 pulses.

Fig. 3-4. EXAMINE And DEPOSIT Timing.

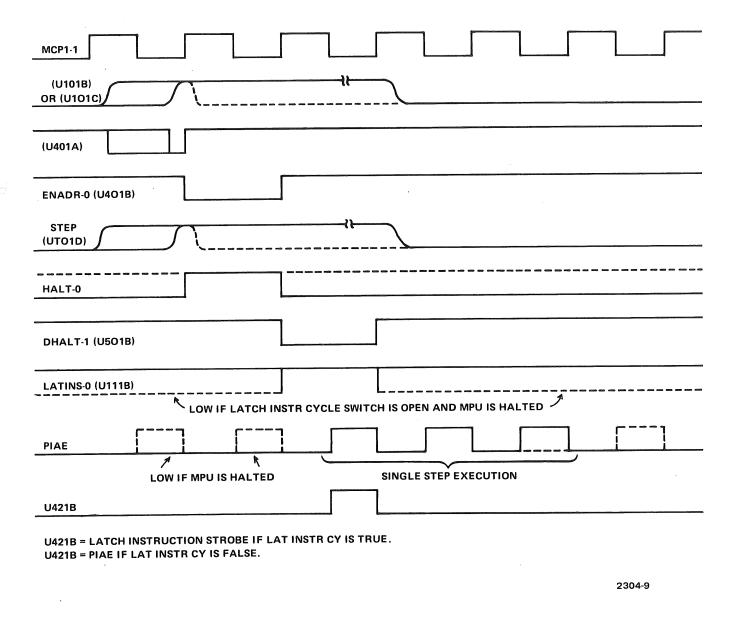

Refer to the composite timing diagram of Fig, 3-5. U101B and U101C provide debouncing for the EXAMINE and DEPOSIT switches respectively. U401A is cleared by pressing the EXAMINE switch or DEPOSIT switch and is set after MCP1 triggers U401B.

Halt mode timing and single instruction step timing are illustrated in the timing diagram of Fig. 3-5. The STEP switch has debounce flip-flops that perform much the same as flip-flops on the EXAMINE and DEPOSIT switches. If the

Fig. 3-5. System Test Fixture Timing.

microprocessor is halted, the STEP switch causes the HALT-0 signal to go high for one machine cycle thus causing a single microprocessor instruction to be executed. DHALT-1 is a delayed HALT signal that is used to latch data pertaining to the instruction being executed as a result of single-step operation, U421B provides the pulse that is used to latch the OP-CODE of the instruction being executed. Any time the HALT line goes true, the microprocessor continues to execute the current instruction and stops at the end of the current instruction except, if the HALT occurs during the last machine cycle fo an instruction, the 6800 microprocessor will continue to execute one more machine instruction before stopping.

When the microprocessor is stopped, PIAE remains false because the microprocessor cannot assert VMA. Unly when the microprocessor is operating can VMA be issued to allow the phase two microprocessor clock MCP2 (02) to become the PIAE signal used by the System Test Fixture.

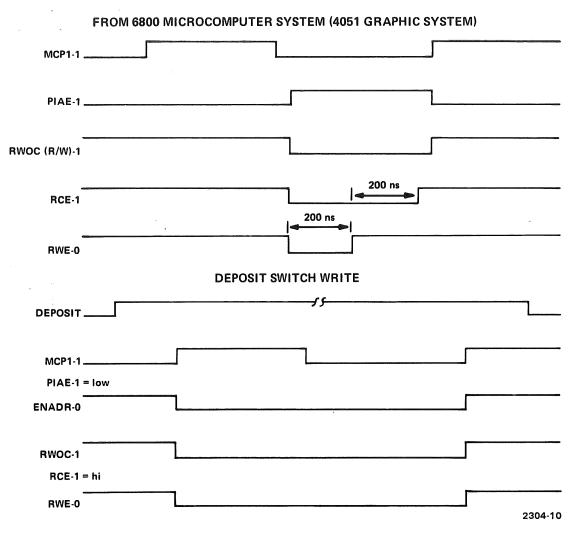

Figure 3-6 compares memory write operations between microprocessor initiated writes (RWDC line from a 4051) and System Test Fixture initiated writes using the DEPOSIT switch.

Fig. 3-6. Comparative timing for memory write operations (4051 and System Test Fixture).

SYSTEM TEST FIXTURE

, ,

#### Section 4

#### 6800 MICROCOMPUTER SPECIFICATIONS

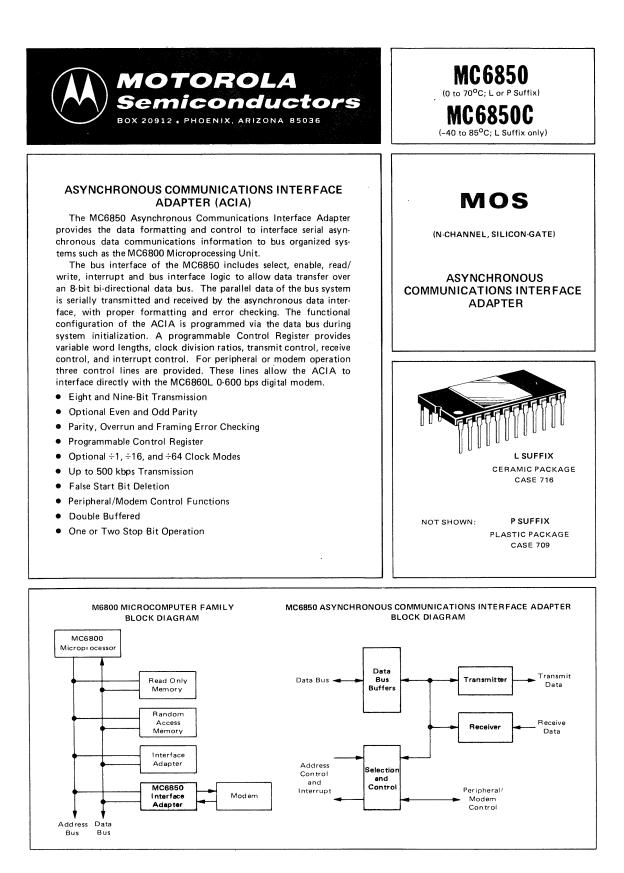

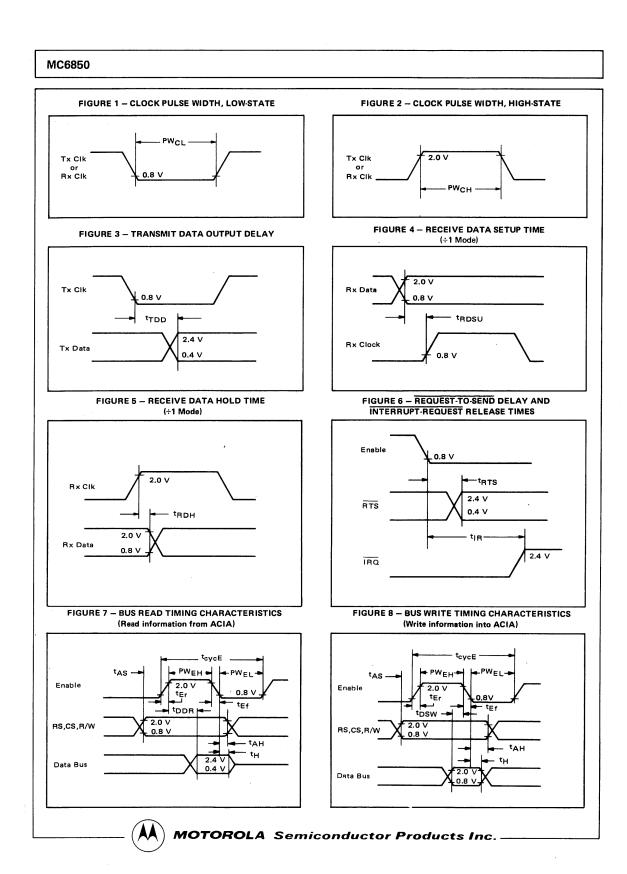

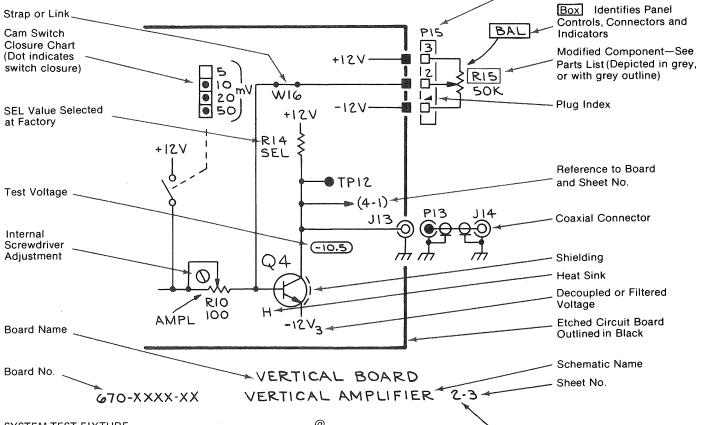

These specification sheets are reprinted by permission of Motorola Semiconductor, Inc. The specification information is current as of the first printing of this manual. Updates and corrections and design changes made by Motorola will not necessarily be reflected in later reprints of this manual.

The purpose of this section is to give users of the System Test Fixture a ready access to general specifications tht apply to most systems using 6800 microprocessors. It is advisable to understand thoroughly the specifications that apply to your system being tested as documented in the service manual for that product.

#### Data Registers Registers and Buffers Bandom Buffers Access Memory Interface Adapter ALU Input/ Interface Modem Output Control Adapter Control Address Data Bus Bus

,

#### MC6800

| Characteristic                                                                                                                                                                                    |                                              | Symbol                  | Min                                                                                              | Тур                                                                                                             | Max                                            | Unit      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------|

| Input High Voltage                                                                                                                                                                                | Logic<br>¢1,¢2                               | V <sub>IH</sub><br>VIHC | $V_{SS} + 2.0$<br>$V_{CC} - 0.3$                                                                 | -                                                                                                               | V <sub>CC</sub><br>V <sub>CC</sub> + 0.1       | Vdc       |

| Input Low Voltage                                                                                                                                                                                 | Logic<br>¢1,¢2                               | VIL<br>VILC             | $\begin{array}{c} V_{SS}-0.3\\ V_{SS}-0.1 \end{array}$                                           | -                                                                                                               | V <sub>SS</sub> + 0.8<br>V <sub>SS</sub> + 0.3 | Vdc       |

| Clock Overshoot/Undershoot – Input High Level<br>– Input Low Level                                                                                                                                |                                              | Vos                     | $\begin{array}{c} V_{CC}-0.5\\ V_{SS}-0.5 \end{array}$                                           | -                                                                                                               | V <sub>CC</sub> + 0.5<br>V <sub>SS</sub> + 0.5 | Vdc       |

| Input Leakage Current<br>{V <sub>in</sub> = 0 to 5.25 V, V <sub>CC</sub> = max}<br>(V <sub>in</sub> = 0 to 5.25 V, V <sub>CC</sub> = 0.0 V)                                                       | Logic*<br>φ1,φ2                              | lin                     |                                                                                                  | 1.0                                                                                                             | 2.5<br>100                                     | μAdc      |

| Three-State (Off State) Input Current<br>(V <sub>in</sub> 0.4 to 2.4 V, V <sub>CC</sub> = max)                                                                                                    | D0-D7<br>A0-A15,R/W                          | ITSI                    | -                                                                                                | 2.0                                                                                                             | 10<br>100                                      | μAdc      |

| Output High Voltage<br>(I <sub>Load</sub> = -205 μAdc, V <sub>CC</sub> = min)<br>(I <sub>Load</sub> = -145 μAdc, V <sub>CC</sub> = min)<br>(I <sub>Load</sub> = -100 μAdc, V <sub>CC</sub> = min) | D0-D7<br>A0-A15,R/W,VMA<br>BA                |                         | V <sub>SS</sub> + 2.4<br>V <sub>SS</sub> + 2.4<br>V <sub>SS</sub> + 2.4<br>V <sub>SS</sub> + 2.4 |                                                                                                                 |                                                | Vdc       |

| Output Low Voltage<br>(I <sub>Load</sub> = 1.6 mAdc, V <sub>CC</sub> = min)                                                                                                                       |                                              | VOL                     | -                                                                                                | -                                                                                                               | V <sub>SS</sub> + 0.4                          | Vdc       |

| Power Dissipation                                                                                                                                                                                 |                                              | PD                      | -                                                                                                | 0.600                                                                                                           | 1.2                                            | W         |

| Capacitance <sup>#</sup><br>(V <sub>in</sub> = 0, T <sub>A</sub> = 25 <sup>o</sup> C, f = 1.0 MHz)                                                                                                | φ1,φ2<br>TSC<br>D8E<br>D0-D7<br>Logic Inputs | Cin                     | 80<br><br><br><br>                                                                               | 120<br><br>7.0<br>10<br>6.5                                                                                     | 160<br>15<br>10<br>12.5<br>8.5                 | pF        |

|                                                                                                                                                                                                   | A0-A15,R/W,VMA                               | Cout                    | -                                                                                                |                                                                                                                 | 12                                             | pF        |

| Frequency of Operation<br>Clock Timing (Figure 1)<br>Cycle Time                                                                                                                                   |                                              | f<br>t <sub>cyc</sub>   | 0.1                                                                                              |                                                                                                                 | 1.0<br>10                                      | MHz<br>μs |

| Clock Pulse Width (Measured at $V_{CC} = 0.3 V$ )                                                                                                                                                 | φ1<br>φ2                                     | PW <sub>¢H</sub>        | 430<br>450                                                                                       | -                                                                                                               | 4500<br>4500                                   | ns        |

| Total $\phi$ 1 and $\phi$ 2 Up Time                                                                                                                                                               |                                              | t <sub>ut</sub>         | 940                                                                                              | · _                                                                                                             | -                                              | ns        |

| Rise and Fall Times $\phi$ 1, $\phi$ 2 (Measured between V <sub>SS</sub> + 0.3 V and V <sub>CC</sub> $-$ 0.3 V)                                                                                   |                                              | tφr, tφf                | 5.0                                                                                              | Name in the second s | 50                                             | ns        |

| Delay Time or Clock Separation (Measured at $V_{\rm OV}$ = $V_{\rm SS}$ + 0.5 V)                                                                                                                  |                                              | td                      | 0                                                                                                | -                                                                                                               | 9100                                           | ns        |

| Overshoot Duration                                                                                                                                                                                |                                              | tos                     | 0                                                                                                |                                                                                                                 | 40                                             | ns        |

\*Except IRQ and  $\overline{NM1}$ , which require 3 k $\Omega$  pullup load resistors for wire-OR capability at optimum operation. \*Capacitances are periodically sampled rather than 100% tested.

#### MC6800

#### MAXIMUM RATINGS

| Rating                      | Symbol | Value        | Unit<br>Vdc |  |

|-----------------------------|--------|--------------|-------------|--|

| Supply Voltage              | Vcc    | -0.3 to +7.0 |             |  |

| Input Voltage               | Vin    | -0.3 to +7.0 | Vdc         |  |

| Operating Temperature Range | TA     | 0 to +70     | °C          |  |

| Storage Temperature Range   | Tstg   | -55 to +150  | °C          |  |

| Thermal Resistance          | θJA    | 70           | °C/W        |  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

READ/WRITE TIMING Figures 2 and 3, f = 1.0 MHz, Load Circuit of Figure 6.

| Characteristic                                                                                                                                                                                                                                                                                                | Symbol ·                                                                    | Min                       | Тур | Max | Unit                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------|-----|-----|----------------------------------------|

| Address Delay                                                                                                                                                                                                                                                                                                 | <sup>t</sup> AD                                                             | -                         | 220 | 300 | ns                                     |

| Peripheral Read Access Time $t_{acc} = t_{ut} - (t_{AD} + t_{DSR})$                                                                                                                                                                                                                                           | t <sub>acc</sub>                                                            |                           | -   | 540 | ns                                     |

| Data Setup Time (Read)                                                                                                                                                                                                                                                                                        | <sup>t</sup> DSR                                                            | 100                       | -   |     | ns                                     |

| Input Data Hold Time                                                                                                                                                                                                                                                                                          | tн                                                                          | 10                        |     | -   | ns                                     |

| Output Data Hold Time                                                                                                                                                                                                                                                                                         | tH                                                                          | 10                        | 25  | -   | ns                                     |

| Address Hold Time (Address, R/W, VMA)                                                                                                                                                                                                                                                                         | <sup>t</sup> AH                                                             | 50                        | 75  | -   | ns                                     |

| Enable High Time for DBE Input                                                                                                                                                                                                                                                                                | teh                                                                         | 450                       | -   | -   | ns                                     |

| Data Delay Time (Write)                                                                                                                                                                                                                                                                                       | tDDW                                                                        | -                         | 165 | 225 | ns                                     |

| Processor Controls*<br>Processor Control Setup Time<br>Processor Control Rise and Fall Time<br>Bus Available Delay<br>Three State Enable<br>Three State Delay<br>Data Bus Enable Down Time During ¢1 Up Time (Figure 3)<br>Data Bus Enable Delay (Figure 3)<br>Data Bus Enable Rise and Fall Times (Figure 3) | tPCS<br>tPCr, tPCf<br>tBA<br>tTSE<br>t <u>TSD</u><br>tDBE<br>tDBED<br>tDBED | 200<br><br><br>150<br>300 |     |     | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

\*Additional information is given in Figures 12 through 16 of the Family Characteristics — see pages 17 through 20.

#### MC6800

# MPU SIGNAL DESCRIPTION

Proper operation of the MPU requires that certain control and timing signals be provided to accomplish specific functions and that other signal lines be monitored to determine the state of the processor.

Clocks Phase One and Phase Two  $(\phi 1, \phi 2)$  – Two pins are used for a two-phase non-overlapping clock that runs at the V<sub>CC</sub> voltage level.

Address Bus (A0-A15) – Sixteen pins are used for the address bus. The outputs are three-state bus drivers capable of driving one standard TTL load and 130 pF. When the output is turned off, it is essentially an open circuit. This permits the MPU to be used in DMA applications.

Data Bus (D0-D7) – Eight pins are used for the data bus. It is bi-directional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130 pF.

Halt — When this input is in the low state, all activity in the machine will be halted. This input is level sensitive. In the halt mode, the machine will stop at the end of an instruction, Bus Available will be at a one level, Valid Memory Address will be at a zero, and all other three-state lines will be in the three-state mode.

Transition of the Halt line must not occur during the last 250 ns of phase one. To insure single instruction operation, the Halt line must go high for one Clock cycle.

**Three-State Control (TSC)** – This input causes all of the address lines and the Read/Write line to go into the off or high impedance state. This state will occur 700 ns after TSC = 2.0 V. The Valid Memory Address and Bus Available signals will be forced low. The data bus is not affected by TSC and has its own enable (Data Bus Enable). In DMA applications, the Three-State Control line should be brought high on the leading edge of the Phase One Clock. The  $\phi$ 1 clock must be held in the high state and the  $\phi$ 2 in the low state for this function to operate properly. The address bus will then be available for other devices to directly address memory. Since the MPU is a dynamic destruction of data will occur in the MPU.

Read/Write (R/W) – This TTL compatible output signals the peripherals and memory devices whether the MPU is in a Read (high) or Write (low) state. The normal standby state of this signal is Read (high). Three-State Control going high will turn Read/Write to the off (high impedance) state. Also, when the processor is halted, it will be in the off state. This output is capable of driving one standard TTL load and 90 pF.

Valid Memory Address (VMA) – This output indicates to peripheral devices that there is a valid address on the address bus. In normal operation, this signal should be utilized for enabling peripheral interfaces such as the PIA and ACIA. This signal is not three-state. One standard TTL load and 90 pF may be directly driven by this active high signal. Data Bus Enable (DBE) — This input is the three-state control signal for the MPU data bus and will enable the bus drivers when in the high state. This input is TTL compatible; however in normal operation, it would be driven by the phase two clock. During an MPU read cycle, the data bus drivers will be disabled internally. When it is desired that another device control the data bus such as in Direct Memory Access (DMA) applications, DBE should be held low.

Bus Available (BA) – The Bus Available signal will normally be in the low state; when activated, it will go to the high state indicating that the microprocessor has stopped and that the address bus is available. This will occur if the Halt line is in the low state or the processor is in the WAIT state as a result of the execution of a WAIT instruction. At such time, all three-state output drivers will go to their off state and other outputs to their normally inactive level. The processor is removed from the WAIT state by the occurrence of a maskable (mask bit I = 0) or nonmaskable interrupt. This output is capable of driving one standard TTL load and 30 pF.

Interrupt Request (IRQ) - This level sensitive input requests that an interrupt sequence be generated within the machine. The processor will wait until it completes the current instruction that is being executed before it recognizes the request. At that time, if the interrupt mask bit in the Condition Code Register is not set, the machine will begin an interrupt sequence. The Index Register, Program Counter, Accumulators, and Condition Code Register are stored away on the stack. Next the MPU will respond to the interrupt request by setting the interrupt mask bit high so that no further interrupts may occur. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations FFF8 and FFF9. An address loaded at these locations causes the MPU to branch to an interrupt routine in memory.

The Halt line must be in the high state for interrupts to be serviced. Interrupts will be latched internally while Halt is low.

The  $\overline{IRQ}$  has a high impedance pullup device internal to the chip; however a 3 k $\Omega$  external resistor to V<sub>CC</sub> should be used for wire-OR and optimum control of interrupts.

**Reset** — This input is used to reset and start the MPU from a power down condition, resulting from a power failure or an initial start-up of the processor. If a high level is detected on the input, this will signal the MPU to begin the restart sequence. This will start execution of a routine to initialize the processor from its reset condition. All the higher order address lines will be forced high. For the restart, the last two (FFFE, FFFF) locations in memory will be used to load the program that is addressed by the program counter. During the restart routine, the interrupt mask bit is set and must be reset before the MPU can be interrupted by IRQ.

**MOTOROLA** Semiconductor Products Inc. —

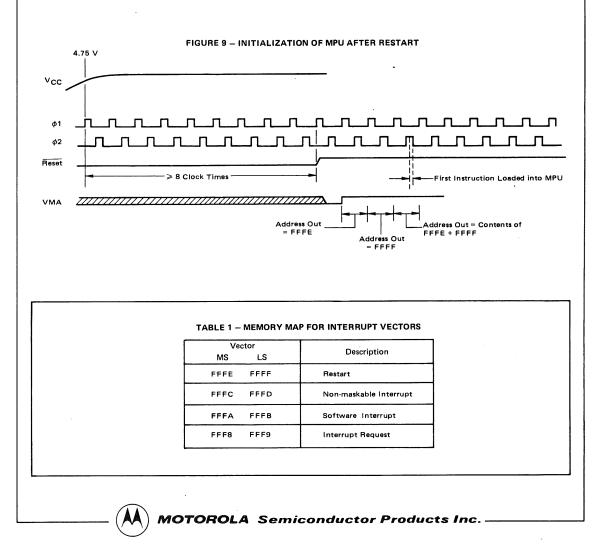

Figure 9 shows the initialization of the microprocessor after restart. Reset must be held low for at least eight clock periods after V<sub>CC</sub> reaches 4.75 volts. If Reset goes high prior to the leading edge of  $\phi 2$ , on the next  $\phi 1$ the first restart memory vector address (FFFE) will appear on the address lines. This location should contain the higher order eight bits to be stored into the program counter. Following, the next address FFFF should contain the lower order eight bits to be stored into the program counter.

Non-Maskable Interrupt (NMI) – A low-going edge on this input requests that a non-mask-interrupt sequence be generated within the processor. As with the Interrupt Request signal, the processor will complete the current instruction that is being executed before it recognizes the NMI signal. The interrupt mask bit in the Condition Code Register has no effect on NMI. The Index Register, Program Counter, Accumulators, and Condition Code Register are stored away on the stack. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations FFFC and FFFD. An address loaded at these locations causes the MPU to branch to a nonmaskable interrupt routine in memory.

$\overline{\text{NMI}}$  has a high impedance pullup resistor internal to the chip; however a 3 k $\Omega$  external resistor to VCC should be used for wire-OR and optimum control of interrupts.

Inputs  $\overline{IRQ}$  and  $\overline{NMI}$  are hardware interrupt lines that are sampled during  $\phi 2$  and will start the interrupt routine on the  $\phi 1$  following the completion of an instruction.

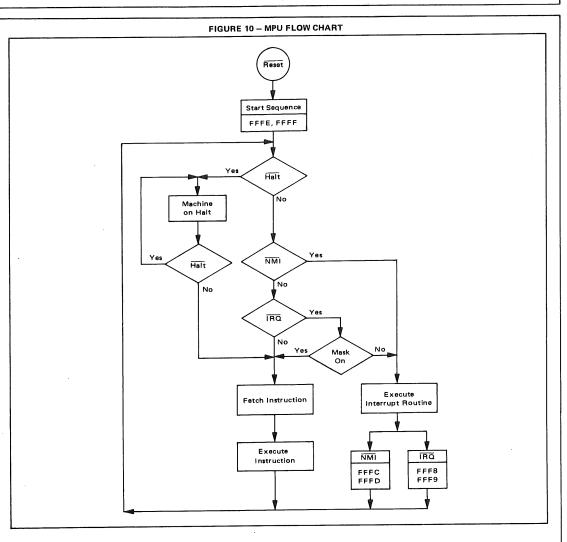

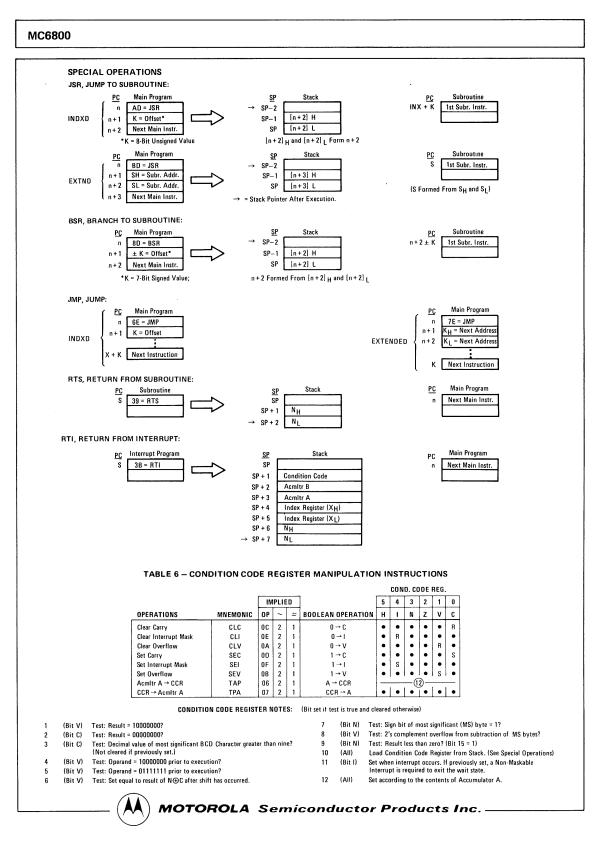

Figure 10 is a flow chart describing the major decision paths and interrupt vectors of the microprocessor. Table 1 gives the memory map for interrupt vectors.

**REPRINTED BY PERMISSION OF MOTOROLA, INC.**

@

## **MPU REGISTERS**

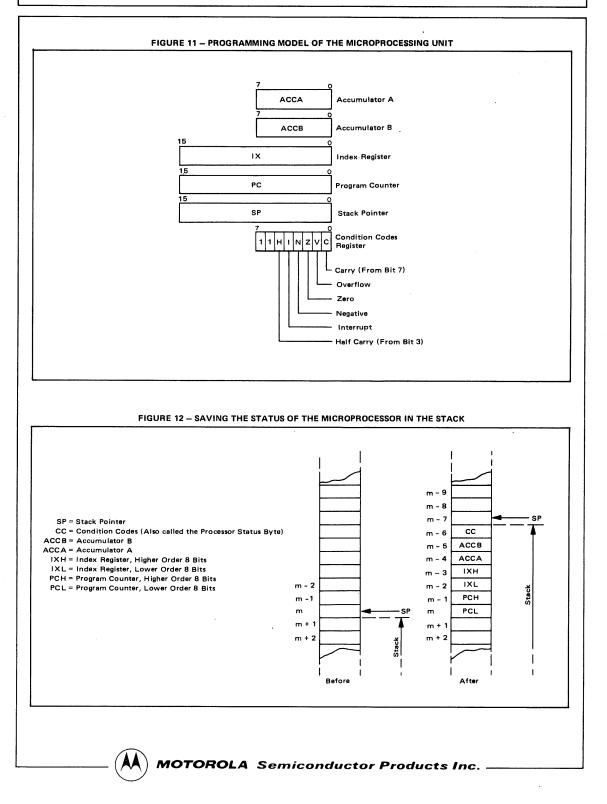

The MPU has three 16-bit registers and three 8-bit registers available for use by the programmer (Figure 11).

**Program Counter** — The program counter is a two byte (16-bits) register that points to the current program address.

Stack Pointer – The stack pointer is a two byte register that contains the address of the next available location in an external push-down/pop-up stack. This stack is normally a random access Read/Write memory that may have any location (address) that is convenient. In those applications that require storage of information in the stack when power is lost, the stack must be non-volatile.

Index Register – The index register is a two byte register that is used to store data or a sixteen bit memory address for the Indexed mode of memory addressing.

Accumulators – The MPU contains two 8-bit accumulators that are used to hold operands and results from an arithmetic logic unit (ALU).

**MOTOROLA** Semiconductor Products Inc. -

**Condition Code Register** – The condition code register indicates the results of an Arithmetic Logic Unit operation: Negative (N), Zero (Z), Overflow (V), Carry from bit 7 (C), and half carry from bit 3 (H). These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 is the interrupt mask bit (I). The unused bits of the Condition Code Register (b6 and b7) are ones.

Figure 12 shows the order of saving the microprocessor status within the stack.

#### MPU INSTRUCTION SET

The MC6800 has a set of 72 different instructions. Included are binary and decimal arithmetic, logical, shift, rotate, load, store, conditional or unconditional branch, interrupt and stack manipulation instructions (Tables 2 thru 6).

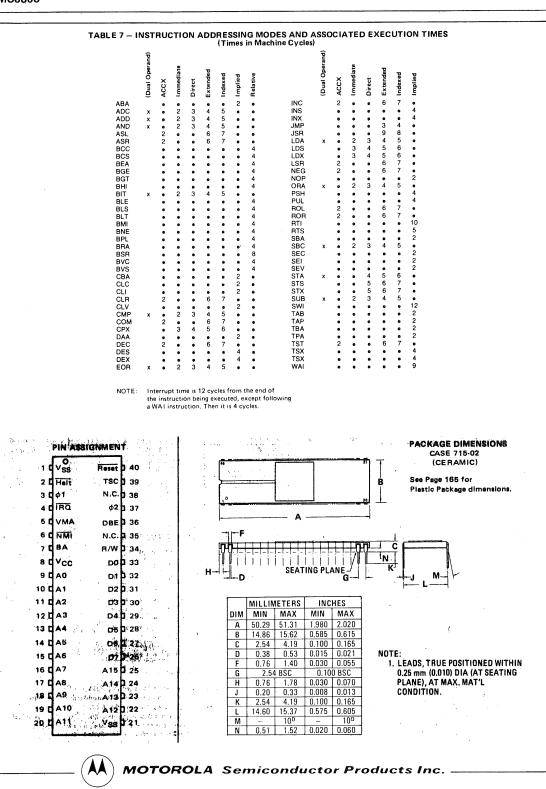

#### MPU ADDRESSING MODES

The MC6800 eight-bit microprocessing unit has seven address modes that can be used by a programmer, with the addressing mode a function of both the type of instruction and the coding within the instruction. A summary of the addressing modes for a particular instruction can be found in Table 7 along with the associated instruction execution time that is given in machine cycles. With a clock frequency of 1 MHz, these times would be microseconds.

Accumulator (ACCX) Addressing – In accumulator only addressing, either accumulator A or accumulator B is specified. These are one-byte instructions.

Immediate Addressing – In immediate addressing, the operand is contained in the second byte of the instruction except LDS and LDX which have the operand in the second and third bytes of the instruction. The MPU addresses

this location when it fetches the immediate instruction for execution. These are two or three-byte instructions.

Direct Addressing – In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes in the machine i.e., locations zero through 255. Enhanced execution times are achieved by storing data in these locations. In most configurations, it should be a random access memory. These are two-byte instructions.

**Extended Addressing** – In extended addressing, the address contained in the second byte of the instruction is used as the higher eight-bits of the address of the operand. The third byte of the instruction is used as the lower eight-bits of the address for the operand. This is an absolute address in memory. These are three-byte instructions.

Indexed Addressing — In indexed addressing, the address contained in the second byte of the instruction is added to the index register's lowest eight bits in the MPU. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are two-byte instructions.

**Implied Addressing** – In the implied addressing mode the instruction gives the address (i.e., stack pointer, index register, etc.). These are one-byte instructions.

**Relative Addressing** – In relative addressing, the address contained in the second byte of the instruction is added to the program counter's lowest eight bits plus two. The carry or borrow is then added to the high eight bits. This allows the user to address data within a range of -125 to +129 bytes of the present instruction. These are two-byte instructions.

## TABLE 2 - MICROPROCESSOR INSTRUCTION SET - ALPHABETIC SEQUENCE

| ABA        | Add Accumulators                | CLR        | Clear                                  | PUL | Pull Data                                   |

|------------|---------------------------------|------------|----------------------------------------|-----|---------------------------------------------|

| ADC        | Add with Carry                  | CLV        | Clear Overflow                         | ROL | Rotate Left                                 |

| ADD        | Add                             | CMP        | Compare                                | ROR | Rotate Right                                |

| AND        | Logical And                     | COM        | Complement                             | RTI | Return from Interrupt                       |

| ASL        | Arithmetic Shift Left           | CPX        | Compare Index Register                 | RTS | Return from Subroutine                      |

| ASR        | Arithmetic Shift Right          | DAA        | Decimal Adjust                         | SBA | Subtract Accumulators                       |

| BCC        | Branch if Carry Clear           | DEC        | Decrement                              | SBC | Subtract with Carry                         |

| BCS        | Branch if Carry Set             | DES        | Decrement Stack Pointer                | SEC | Set Carry                                   |

| BEQ        | Branch if Equal to Zero         | DEX        | Decrement Index Register               | SEI | Set Interrupt Mask                          |

| BGE        | Branch if Greater or Equal Zero | EOR        | Exclusive OR                           | SEV | Set Overflow                                |

| BGT        | Branch if Greater than Zero     |            |                                        | STA | Store Accumulator                           |

| BHI        | Branch if Higher                | INC        | Increment                              | STS | Store Stack Register                        |

| BIT        | Bit Test                        | INS        | Increment Stack Pointer                | STX | Store Index Register                        |

| BLE        | Branch if Less or Equal         | INX        | Increment Index Register               | SUB | Subtract                                    |

| BLS        | Branch if Lower or Same         | JMP        | Jump                                   | SWI | Software Interrupt                          |

| BLT        | Branch if Less than Zero        | JSR        | Jump to Subroutine                     | TAB | Transfer Accumulators                       |

| BMI        | Branch if Minus                 |            | •                                      | TAP | Transfer Accumulators to Condition Code Reg |

| BNE        | Branch if Not Equal to Zero     | LDA<br>LDS | Load Accumulator<br>Load Stack Pointer | TBA | Transfer Accumulators                       |

| BPL        | Branch if Plus<br>Branch Always | LDS        | Load Index Register                    | TPA | Transfer Condition Code Reg. to Accumulator |

| BRA<br>BSR | Branch to Subroutine            | LSR        | Logical Shift Right                    | TST | Test                                        |

| BVC        | Branch if Overflow Clear        |            | <b>v</b>                               | TSX | Transfer Stack Pointer to Index Register    |

| BVS        | Branch if Overflow Set          | NEG        | Negate                                 | TXS | Transfer Index Register to Stack Pointer    |

|            |                                 | NOP        | No Operation                           |     | •                                           |

| CBA        | Compare Accumulators            | ORA        | Inclusive OR Accumulator               | WAI | Wait for Interrupt                          |

| CLC        | Clear Carry                     |            |                                        |     |                                             |

| CLI        | Clear Interrupt Mask            | PSH        | Push Data                              |     |                                             |

**MOTOROLA** Semiconductor Products Inc.

|                                           |                 | [ ]      | MMED    | , 1  | D        | REC    |        | DRES         | NDE)   |        |                | XTN    | D      | IA       | APLI   | ED | BOOLEAN/ARITHMETIC OPERATION<br>(All register labels                                                                                                                                                                              | -      | _          | 2 1      |                  |

|-------------------------------------------|-----------------|----------|---------|------|----------|--------|--------|--------------|--------|--------|----------------|--------|--------|----------|--------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------|------------------|

| OPERATIONS                                | MNEMONIC        | OP       | ~       | =    | OP       | ~      | =      |              | ~      | =      |                | ~      | =      |          | ~      |    | refer to contents)                                                                                                                                                                                                                |        |            | zν       |                  |

| Add                                       | ADDA<br>ADD8    | 88<br>CB | 2<br>2  | 2    | 98<br>D8 | 3<br>3 | 2<br>2 | A8<br>E8     | 5<br>5 | 2      | BB<br>FB       | 4      | 3<br>3 |          |        |    | $A + M \rightarrow A$<br>$B + M \rightarrow B$                                                                                                                                                                                    | 1<br>t | • 1        |          |                  |

| Add Acmitrs                               | ADDB            | LB       | 2       | -    | UB       | 3      | 2      | 68           | 5      |        | FB             | 4      |        | 18       | 2      | 1  | $B + M \rightarrow B$<br>A + B $\rightarrow A$                                                                                                                                                                                    |        | • ‡        | 11       |                  |

| Add with Carry                            | ADCA<br>ADCB    | 89<br>C9 | 2<br>2  | 2    | 99<br>D9 | 3<br>3 | 2      | A9<br>E9     | 5<br>5 | 2<br>2 | 89<br>F9       | 4<br>4 | 3<br>3 |          |        |    | $A + M + C \rightarrow A$<br>$B + M + C \rightarrow B$                                                                                                                                                                            |        | • 1        | 1.1.     |                  |

| And                                       | ANDA            | 84       | 2       | 2    | 94       | 3      | 2      | A4           | 5      | 2      | 84             | 4      | 3      |          |        |    | A·M→Ą                                                                                                                                                                                                                             | •      | • 1        | t F      | 3 •              |

| Bit Test                                  | ANDB<br>BITA    | C4<br>85 | 2<br>2  | 2    | D4<br>95 | 3<br>3 | 2<br>2 | E4<br>A5     | 5<br>5 | 2<br>2 | F4<br>85       | 4      | 3<br>3 |          |        |    | B·M→B<br>A·M                                                                                                                                                                                                                      | :      | • 1        | 1.1.     |                  |

|                                           | BITB            | C5       | 2       | 2    | D5       | 3      | 2      | E5           | 5      | 2      | F5             | 4      | 3      |          |        |    | B · M                                                                                                                                                                                                                             | •      | • 1        | t F      | •                |

| Clear                                     | CLR<br>CLRA     |          |         |      |          |        |        | 6F           | 7      | 2      | 7F             | 6      | 3      | 4F       | 2      | 1  | $00 \rightarrow M$<br>$00 \rightarrow A$                                                                                                                                                                                          | :      | • R<br>• R |          | R<br>R<br>R      |

| •                                         | CLRB            |          |         |      |          |        |        |              |        |        |                |        | •      | 5F       |        | 1  | 00 → B                                                                                                                                                                                                                            | •      | • R<br>• t | I S F    | R R              |

| Compare                                   | CMPA<br>CMPB    | 81<br>C1 | 2<br>2  | 2    | 91<br>D1 | 3<br>3 | 2<br>2 | A1<br>E1     | 5<br>5 | 2<br>2 | 81<br>F1       | 4<br>4 | 3<br>3 |          |        |    | A – M<br>B – M                                                                                                                                                                                                                    |        | • 1        | 1111     |                  |

| Compare Acmitrs<br>Complement, 1's        | CBA<br>COM      |          |         |      |          |        |        | 63           | 7      | 2      | 73             | 6      | 3      | 11       | 2      | 1  | A – B<br>M → M                                                                                                                                                                                                                    | :      | • 1        |          |                  |

|                                           | COMA            |          |         |      |          |        |        |              |        | -      |                |        | Ĩ      | 43       |        | 1  | $\overline{A} \rightarrow A$                                                                                                                                                                                                      | •      | • 1        | 1 F      | 3 8              |

| Complement, 2's                           | COMB<br>NEG     |          |         |      |          |        |        | 60           | 1      | 2      | 70             | 6      | 3      | 53       | 2      | 1  | $\overline{B} \rightarrow B$<br>$00 - M \rightarrow M$                                                                                                                                                                            |        | •          |          | IS<br>D          |

| (Negate)                                  | NEGA            |          |         |      |          |        |        |              |        | _      |                |        |        | 40       |        | 1  | 00 – A → A                                                                                                                                                                                                                        | •      | • 1        | 10       | DØ               |

| Decimal Adjust, A                         | NEGB<br>DAA     |          |         |      |          |        |        |              |        |        |                |        |        | 50<br>19 |        | 1  | 00 B → B<br>Converts Binary Add. of BCD Characters                                                                                                                                                                                |        | • ;        |          | 0                |

|                                           |                 |          |         |      |          |        |        | 64           | 7      | •      | 7A             | c      | 3      |          |        |    | into BCD Format                                                                                                                                                                                                                   |        | • :        |          |                  |

| Decrement ,                               | DEC<br>DECA     |          |         |      |          |        |        | οA           | '      | 2      | / <sup>^</sup> | U      | 3      |          | 2      |    | $ \begin{array}{c} M - 1 \rightarrow M \\ A - 1 \rightarrow A \end{array} $                                                                                                                                                       | •      | • 1        | 1 4      | • • •            |

| Exclusive OR                              | DECB<br>Eora    | 88       | 2       | 2    | 98       | 3      | 2      | A8           | 5      | 2      | B8             | 4      | 3      | 5A       | 2      | 1  | $B - 1 \rightarrow B$<br>$A \oplus M \rightarrow A$                                                                                                                                                                               | :      | • 1        |          | *   •  <br>*   • |

|                                           | EORB            | C8       | 2       | 2    | D8       | 3      | 2      | E8           | 5      | 2      | F8             | 4      | 3      |          |        |    | B⊕M→B                                                                                                                                                                                                                             | •      | • ‡        | ‡ F      | 3 •              |

| Increment                                 | INC<br>INCA     |          |         |      |          |        |        | 6C           | 7      | 2      | 70             | 6      | 3      | 4C       | 2      | 1  | $ \begin{array}{c} M + 1 \rightarrow M \\ A + 1 \rightarrow A \end{array} $                                                                                                                                                       | :      | • :        |          |                  |

| Load Apple                                | INCB            |          | •       |      | 00       | •      |        |              | F      | •      | Pr             |        | •      |          | 2      |    | B + 1 → B                                                                                                                                                                                                                         | •      | • 1        | 10       | 9•               |

| Load Acmitr                               | LDAA<br>LDAB    | 86<br>C6 | 2<br>2  | 2 2  | 96<br>D6 | 3<br>3 | 2<br>2 | A6<br>E6     | 5<br>5 | 2<br>2 | 86<br>F6       | 4<br>4 | 3<br>3 |          |        |    | M → A<br>M → B                                                                                                                                                                                                                    |        | •          |          | ₹ •<br>₹ •       |

| Or, Inclusive                             | ORAA<br>ORAB    | 8A<br>CA | 2<br>2  | 2    | 9A<br>DA | 3<br>3 | 2      | AA<br>EA     | 5<br>5 | 2<br>2 | BA<br>FA       | 4<br>4 | 3<br>3 |          |        |    | $ \begin{array}{c} A + M \rightarrow A \\ B + M \rightarrow B \end{array} $                                                                                                                                                       | 1:     | • 1        | 1.1.1    |                  |

| Push Data                                 | PSHA            | UA       | 2       | -    | UA       | 3      | '      | LA           | 5      | 2      | 1              | 4      | 3      | 36       |        | 1  | $A \rightarrow M_{SP}, SP - 1 \rightarrow SP$                                                                                                                                                                                     |        | • •        | • • •    | • •              |

| Pull Data                                 | PSHB<br>PULA    |          |         |      |          |        |        |              |        |        |                |        |        | 37       | 4      | 1  | $B \rightarrow M_{SP}, SP \rightarrow 1 \rightarrow SP$<br>SP + 1 $\rightarrow$ SP, M_{SP} $\rightarrow$ A                                                                                                                        | :      | •          |          | 1 1              |

|                                           | PULB            |          |         |      |          |        |        | <b>c</b> 0   | 7      | 2      | 70             | 6      | 2      | 33       | 4      | 1  | $SP + 1 \rightarrow SP, M_{SP} \rightarrow B$                                                                                                                                                                                     | :      | • •        | • • •    | . 1 1            |

| Rotate Left                               | ROL<br>ROLA     |          |         |      |          |        |        | 69           | '      | 2      | /9             | D      | 3      | 49       | 2      | 1  |                                                                                                                                                                                                                                   |        | • 1        | 10       |                  |

| Rotate Right                              | ROLB            |          |         |      |          |        |        | 66           | 7      | 2      | 76             | 6      | 3      | 59       | 2      | 1  | B C b7 - b0                                                                                                                                                                                                                       | :      | •          |          |                  |

| notate ragin                              | RORA            |          |         |      |          |        |        |              | '      | ·      |                | U      | Ŭ      |          | 2      |    |                                                                                                                                                                                                                                   | •      | • 1        | 10       | D t              |

| Shift Left, Arithmetic                    | RORB<br>ASL     |          |         |      |          |        |        | 68           | 7      | 2      | 78             | 6      | 3      | 56       | 2      | 1  | B C b7 - b0                                                                                                                                                                                                                       | :      | • •        |          |                  |

|                                           | ASLA<br>ASLB    |          |         |      |          |        |        |              |        |        |                |        |        | 48<br>58 | 2<br>2 | 1  | $ \begin{vmatrix} A \\ B \end{vmatrix} = \begin{pmatrix} - & - & - & - & - & - & - & - & - \\ \hline B & C & b7 & b0 \end{pmatrix} = \begin{pmatrix} A \\ b & - & - & - & - & - & - & - \\ \hline B & C & b7 & b0 \end{pmatrix} $ | :      | • 1        |          |                  |

| Shift Right, Arithmetic                   | ASR             |          |         |      |          |        |        | 67           | 7      | 2      | 77             | 6      | 3      |          |        |    | M)                                                                                                                                                                                                                                | •      | • 1        | 10       |                  |

|                                           | ASRA<br>ASRB    |          |         |      |          |        |        |              |        |        |                |        |        | 47       |        | 1  |                                                                                                                                                                                                                                   | :      | • 1        | 1.12     |                  |

| Shift Right, Logic                        | LSR             |          |         |      |          |        |        | 64           | 7      | 2      | 74             | 6      | 3      |          |        |    | [M] -                                                                                                                                                                                                                             | •      | • 8        |          |                  |

|                                           | LSRA<br>LSRB    |          |         |      |          |        |        |              |        |        |                |        |        | 44<br>54 |        | 1  | $ \begin{vmatrix} A \\ B \end{vmatrix} \qquad \begin{array}{c} 0 - \begin{array}{c} - \end{array} \\ b7 \\ b7 \\ b0 \\ \end{array} \\ \begin{array}{c} c \\ c \\ \end{array} $                                                    |        | • R<br>• R |          |                  |

| Store Acmitr.                             | STAA<br>STAB    |          |         |      | 97<br>D7 | 4<br>4 | 2      | A7<br>E7     | 6<br>6 | 2<br>2 | 87<br>F7       | 5<br>5 | 3<br>3 |          |        |    | A → M<br>B → M                                                                                                                                                                                                                    | :      | • 1        | 1.1.     |                  |

| Subtract                                  | SUBA            |          | 2       | 2    | 90       | 3      | 2      | AO           | 5      | 2      | во             | 4      | 3      |          |        |    | A – M → A                                                                                                                                                                                                                         | •      | • 1        | 11       |                  |

| Subtract Acmitrs.                         | SUBB<br>SBA     | CO       | 2       | 2    | 00       | 3      | 2      | EO           | 5      | 2      | FO             | 4      | 3      | 10       | 2      | 1  | $B \rightarrow M \rightarrow B$<br>$A - B \rightarrow A$                                                                                                                                                                          | :      | • 1        |          |                  |