## TEK-MADE INTEGRATED CIRCUITS CATALOG

#### **COMPANY CONFIDENTIAL**

The contents of this catalog are for the exclusive use of TEKTRONIX, INC. employees. Any unauthorized use may constitute a theft.

#### **PURPOSE AND USE**

This catalog contains integrated circuits that have had a Component Engineering Release by the publication date.

Data sheets are included for parts that are recommended for new designs. The data sheets, with a few exceptions, are intended to contain sufficient information so that a part may be designed into a new instrument design. For further applications information please call (phone 627-1037).

#### CORRECTIONS AND SUGGESTIONS

Corrections or suggestions for improvement are encouraged at any time. Mail to delivery station 59-355. A special form for this purpose is included in this catalog.

#### CATALOG DISTRIBUTION

Catalog distribution is automatic to all Electrical Engineers and E.E. managers. If you are not in this job category, please write to Applications Engineering, delivery station 59-355—include name, payroll code, and delivery station.

#### **TEK-MADE I.C. QUESTIONNAIRE**

We want to serve you better. If you are considering using a TEK-made I.C. for a new instrument design, we would like to hear from you.

| I.C. Part Number                                                |     |

|-----------------------------------------------------------------|-----|

| Do you need any additional information? Yes D No D              |     |

| Information Needed                                              |     |

| Name                                                            |     |

| Delivery Station Phone                                          |     |

| Projected volume of new application                             | /yr |

| Approximate introduction date                                   |     |

| Send to: ICM Application Engineering<br>Delivery Station 59-355 |     |

#### **TEK-MADE I.C. QUESTIONNAIRE**

We want to serve you better. If you are considering using a TEK-made I.C. for a new instrument design, we would like to hear from you.

| I.C. Part Number                                                |            |

|-----------------------------------------------------------------|------------|

| Do you need any additional information? Y                       | ′es □ No □ |

| Information Needed                                              |            |

| Name                                                            |            |

| Delivery Station                                                | Phone      |

| Projected volume of new application                             | /yr        |

| Approximate introduction date                                   |            |

| Send to: ICM Application Engineering<br>Delivery Station 59-355 |            |

-------

If we have slipped up and you feel there is room for improvement, please tell us at once. You will be doing us a great favor if you call a problem to our attention.

| our<br>ame                             | Address                                                                                        | Phone                                        |

|----------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                        |                                                                                                |                                              |

| RORS, OMISSIONS                        | , SUGGESTIONS:                                                                                 |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

| ······································ |                                                                                                |                                              |

|                                        |                                                                                                |                                              |

|                                        | SEND TO: IC                                                                                    | CM APPLICATIONS ENGINEERING<br>D.S. 59-355   |

|                                        |                                                                                                |                                              |

| Jser                                   |                                                                                                |                                              |

| Jser                                   | If we have slipped up and you                                                                  | will be doing us a great favor if you        |

| Jser<br>Feedback                       | If we have slipped up and you<br>please tell us at once. You                                   | will be doing us a great favor if you        |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You                                   | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>Seedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>eedback                        | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio |                                              |

| User<br>Feedback                       | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>eedback                        | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

| Jser<br>eedback                        | If we have slipped up and you<br>please tell us at once. You<br>call a problem to our attentio | will be doing us a great favor if you<br>on. |

D.S. 59-355

### TABLE OF CONTENTS

·

.

### **TABLE OF CONTENTS**

#### Page No.

| SECTION 1 | TABLE OF CONTENTS                              |

|-----------|------------------------------------------------|

|           | Index by Function                              |

|           | Index by Part Number                           |

|           | Index by M Number                              |

| SECTION 2 | NEW DESIGN INFORMATION                         |

|           | Preferred for New Designs                      |

|           | Suitable for New Designs 2-2                   |

|           | Do Not Use for New Designs 2-3                 |

|           | Call Applications Engineering Before Using 2-4 |

| SECTION 3 | Q. A. PROGRAM                                  |

|           | Q. A. Program                                  |

| SECTION 4 | RELIABILITY                                    |

|           | Reliability                                    |

#### SECTION 5 PACKAGED PARTS (DATA SHEETS)

PREFERRED FOR NEW DESIGNS-COST EFFECTIVE OR STATE-OF-THE-ART

#### Page No.

#### Packaged Parts

| 155-0012-00 | Z axis signal conditioner                  |                  |

|-------------|--------------------------------------------|------------------|

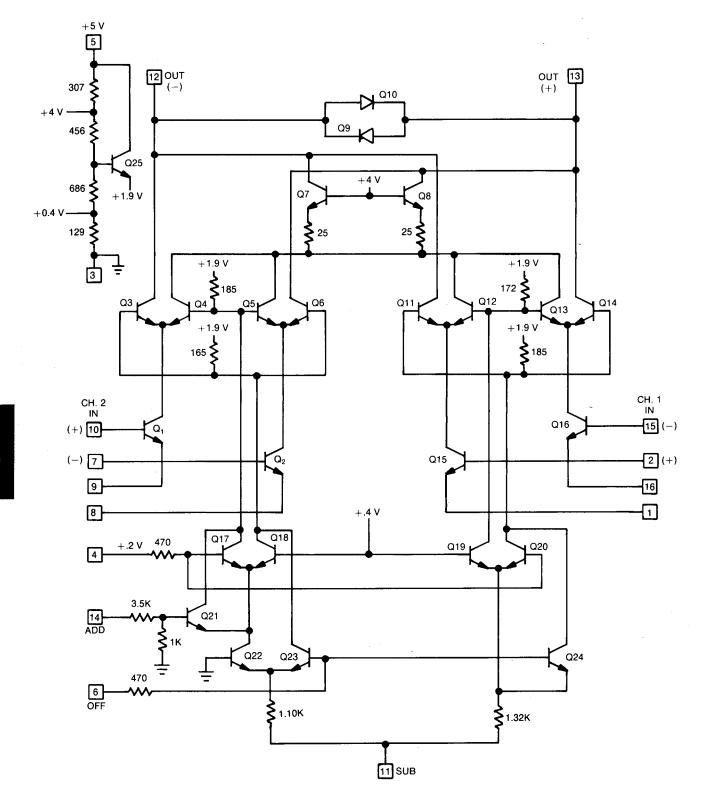

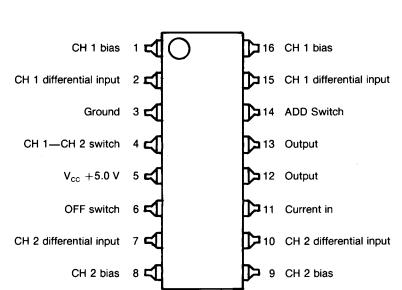

| 155-0022-00 | 2 input channel switch Ins Rt              | 5-7              |

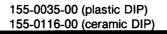

| 155-0035-00 | Quad Op Amps, 80 MHz gain bandwidth        | 5-11             |

| 155-0038-02 | 5-bit precision D/A                        | 5-17             |

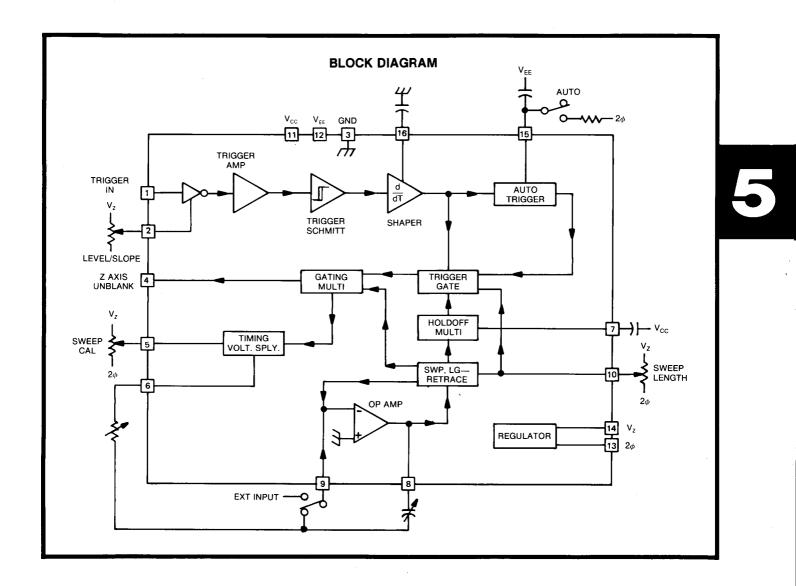

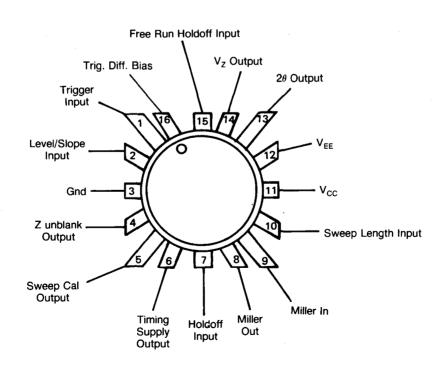

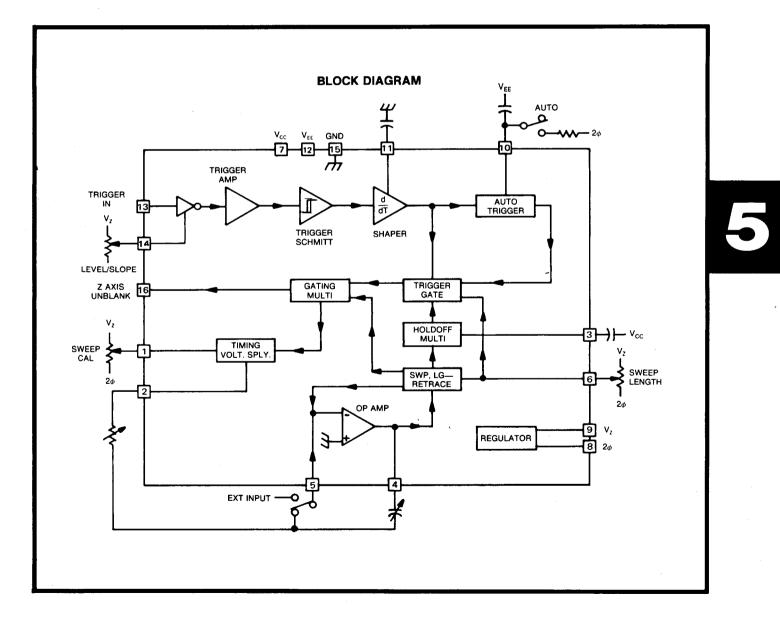

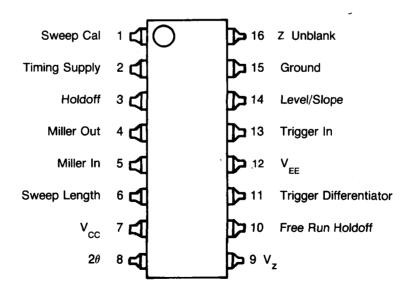

| 155-0048-01 | 5 MHz trigger and 1 V/µs sweep             | 5-21             |

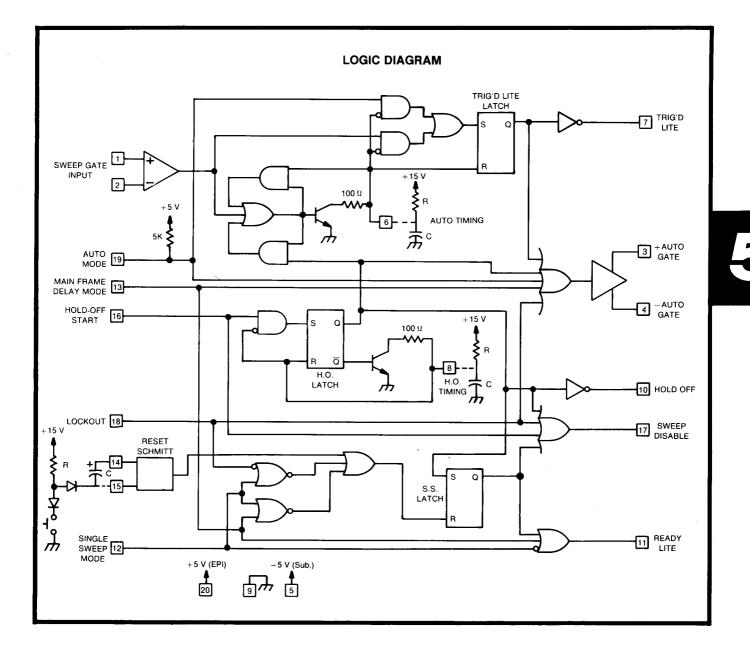

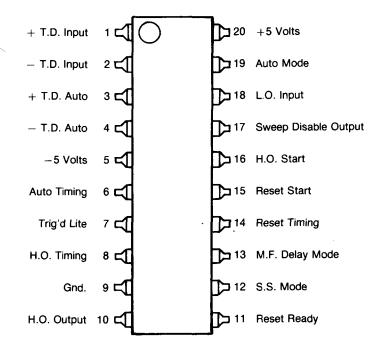

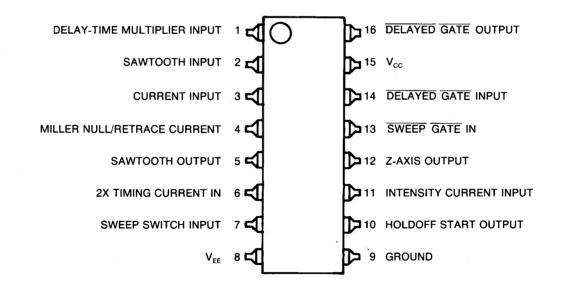

| 155-0049-02 | Sweep control                              | 5-27             |

| 155-0055-00 | 5 MHz trigger and 1 V/µs sweep             | 5-35             |

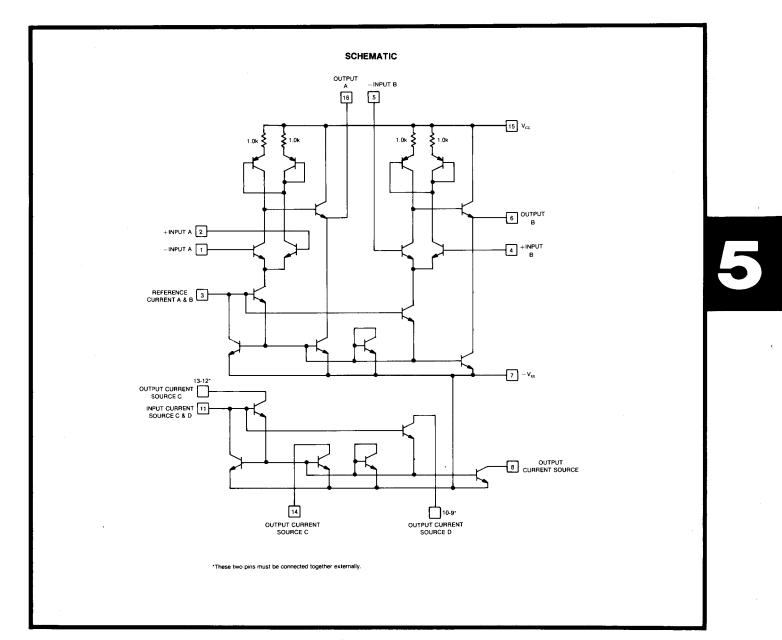

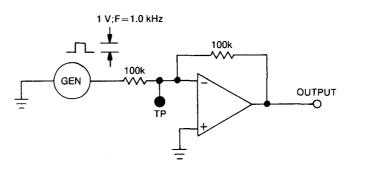

| 155-0057-00 | Dual Op Amp, current source                | 5-41             |

| 155-0067-02 | DC to DC controller                        | 5-47             |

| 155-0078-10 | Differential/variable/invert amplifier     | 5-53             |

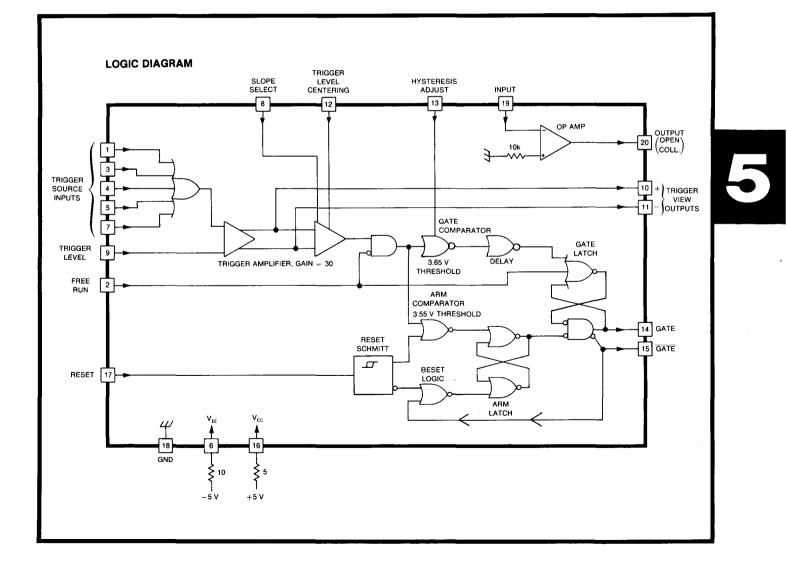

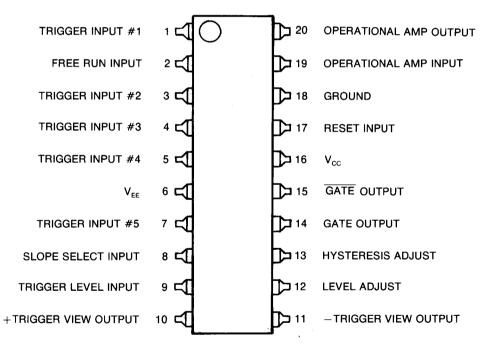

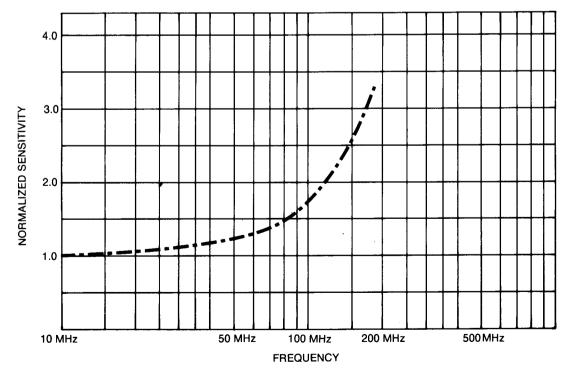

| 155-0109-01 | 350 MHz trigger                            | 5-61             |

| 155-0116-00 | Quad Op Amps, 80 MHz gain bandwidth        | 5-6 <del>9</del> |

| 155-0122-00 | Sweep control                              | 5-75             |

| 155-0123-00 | 50 ns sweep and delay pickoff              | 5-81             |

| 155-0124-00 | 5 ns/div horizontal preamplifier           | 5-87             |

| 155-0144-00 | TV sync stripper                           | 5-93             |

| 155-0145-00 | Controlled risetime amplifier              | 5-99             |

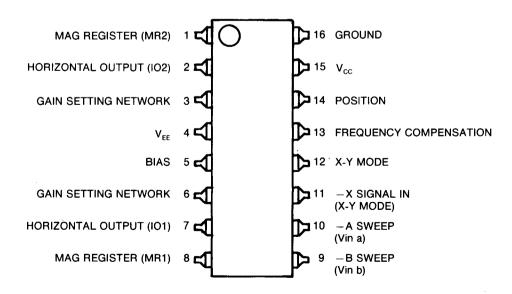

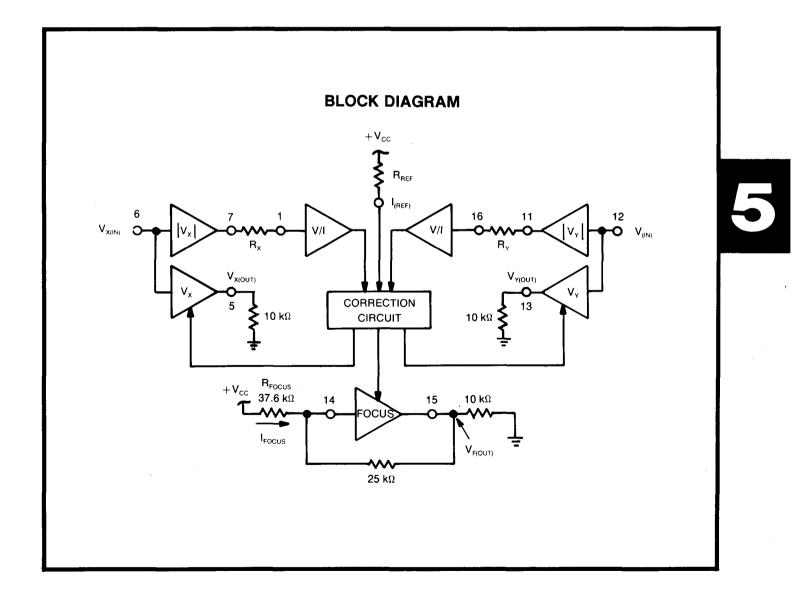

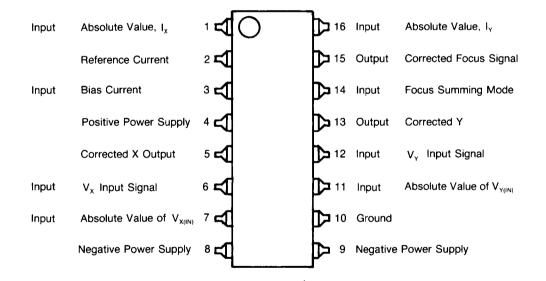

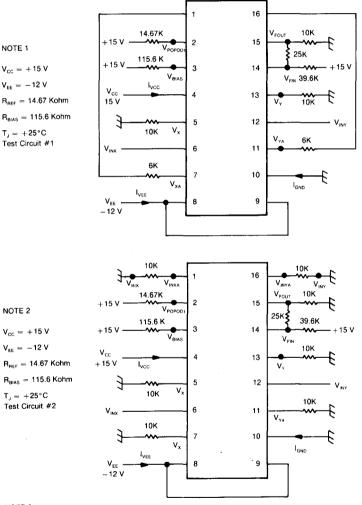

| 155-0152-01 | Magnetic deflected CRT geometry correction | 5-103            |

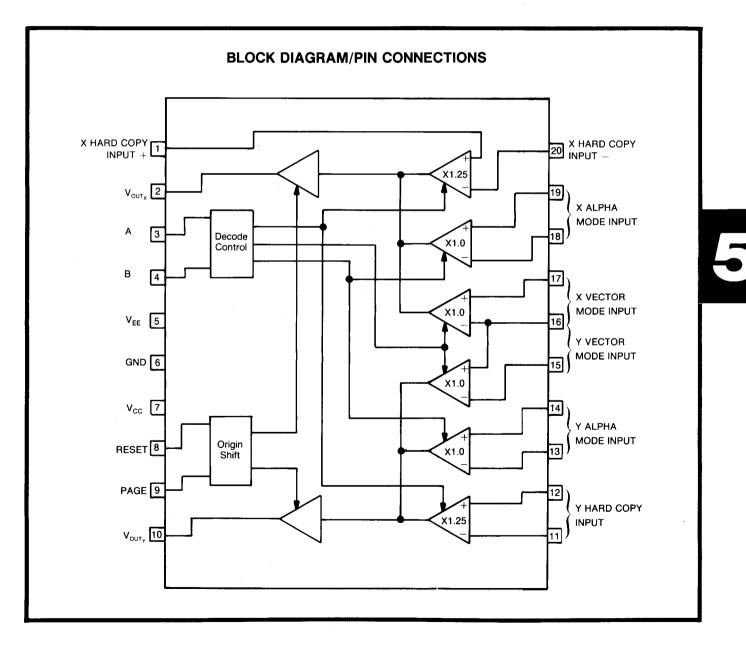

| 155-0154-00 | 3-input multiplexer                        | 5-111            |

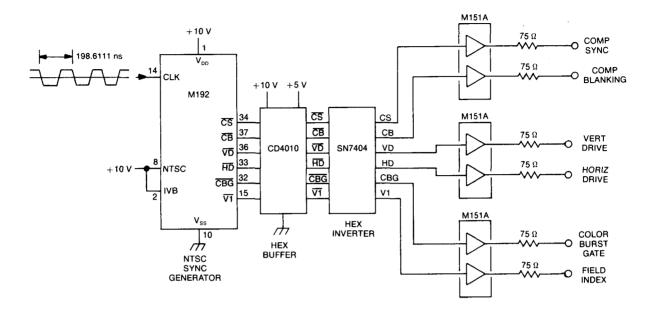

| 155-0188-00 | TV sync generator                          | 5-117            |

| 155-0196-00 | 100 MHz trigger                            | 5-125            |

| 155-0215-00 | Logic analyzer input                       |                  |

| 155-0217-00 | Amplifier                                  |                  |

| 155-0218-00 | 100 MHz vertical output                    |                  |

|             |                                            |                  |

### **TABLE OF CONTENTS (cont)**

#### Page No.

#### SECTION 5 PACKAGED PARTS (DATA SHEETS) (cont)

| 155-0244-00 | Scope logic interface 5                  | -149 |

|-------------|------------------------------------------|------|

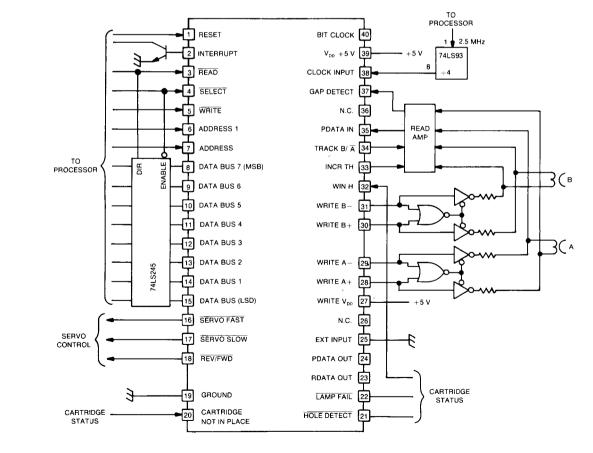

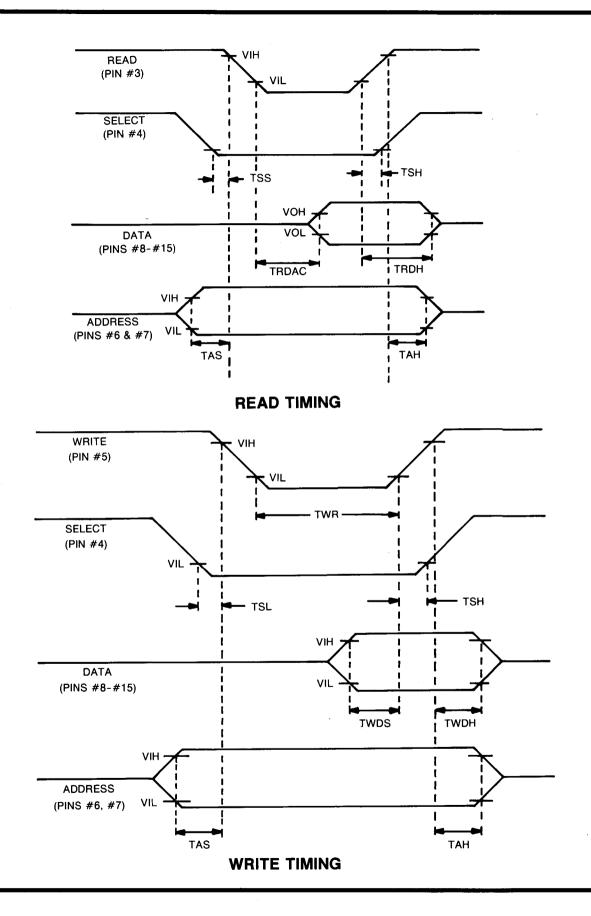

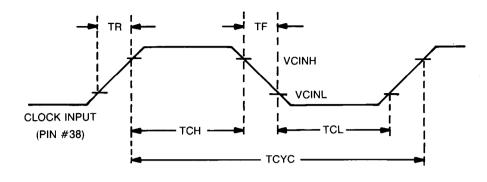

| 155-0247-00 | Tape controller                          | -163 |

| 155-0253-00 | Schmitt trigger 5                        | -171 |

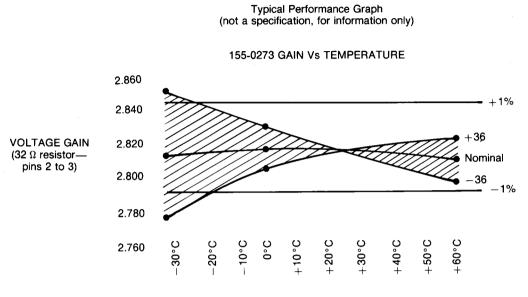

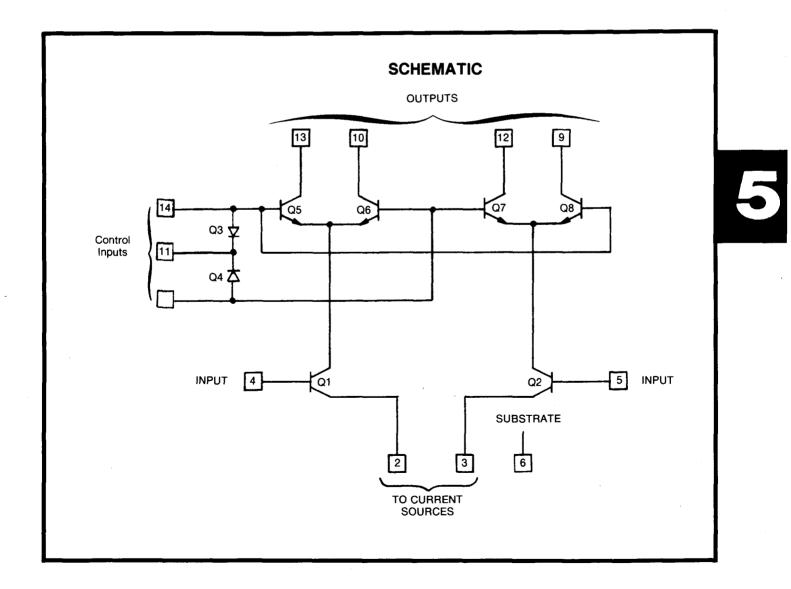

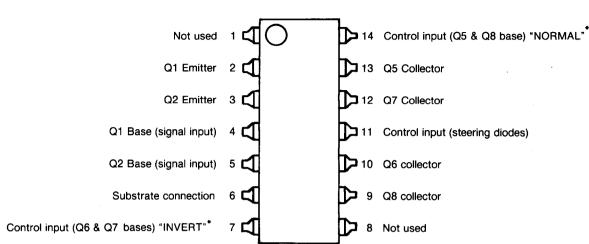

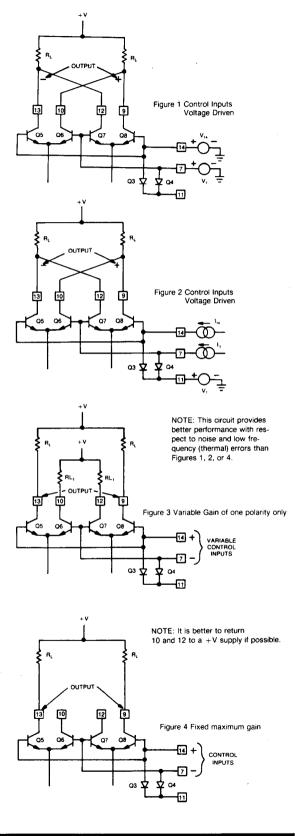

| 155-0273-00 | Differential/variable/invert amplifier 5 | -175 |

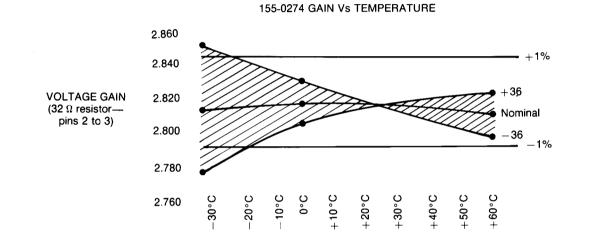

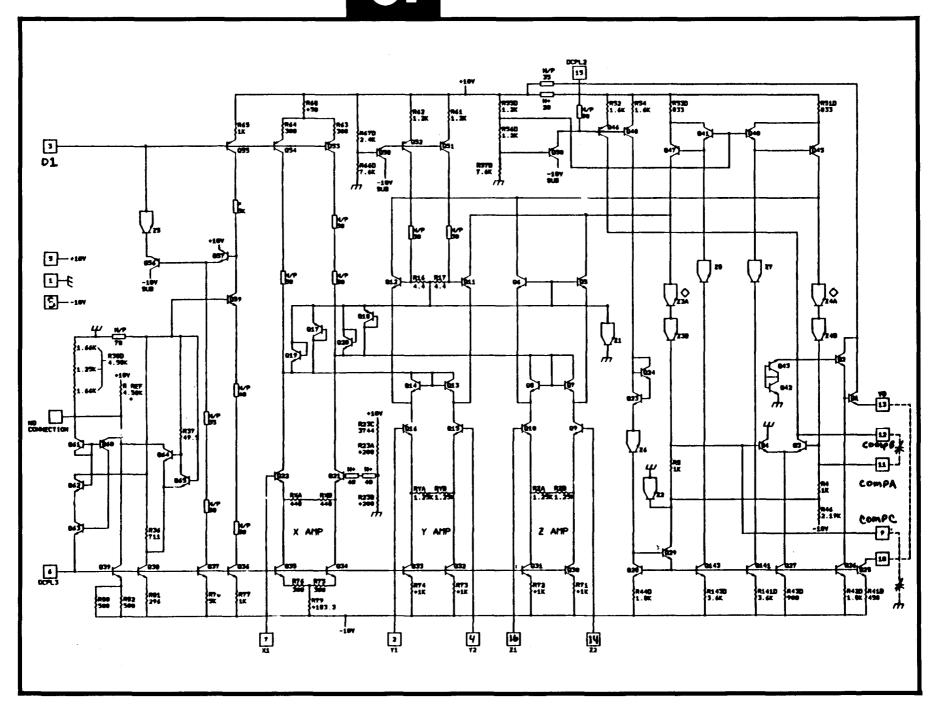

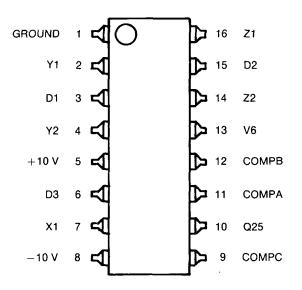

| 155-0274-00 | Differential/variable/invert amplifier 5 | -181 |

| 155-0283-00 | Video multiplier                         | -187 |

| 206-0248-00 | Platinum temperature probe tip5          | -193 |

#### SECTION 6 DIE (DATA SHEETS)

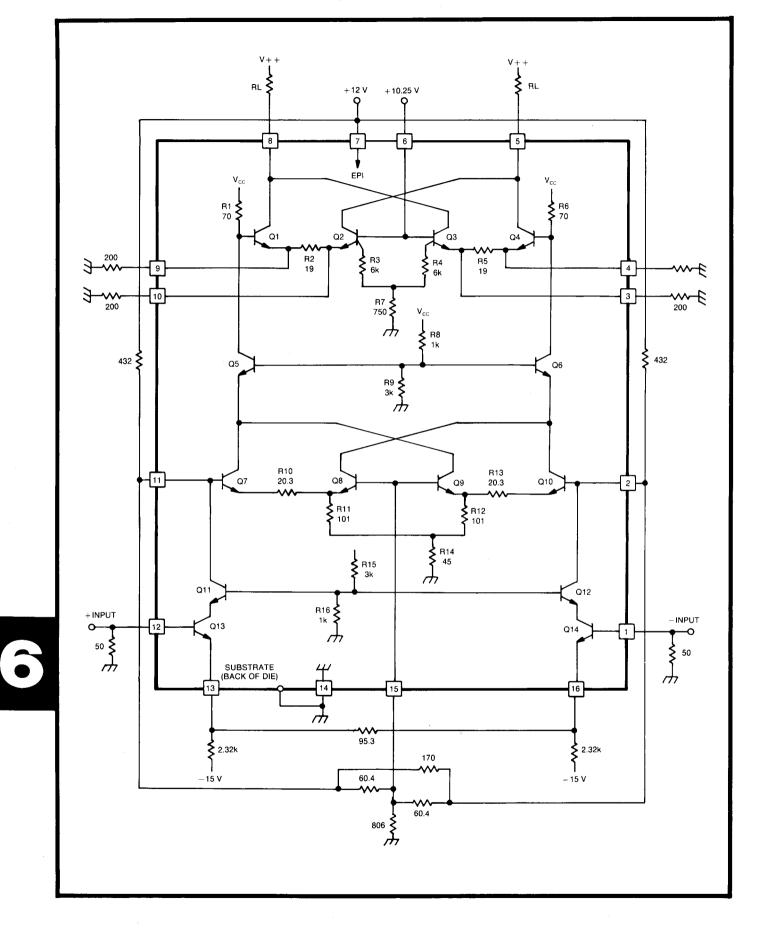

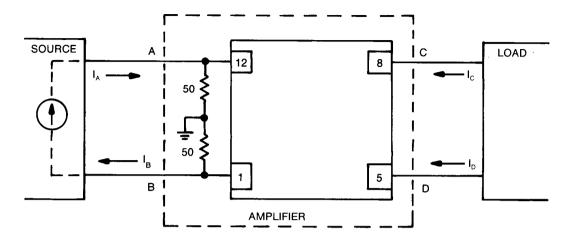

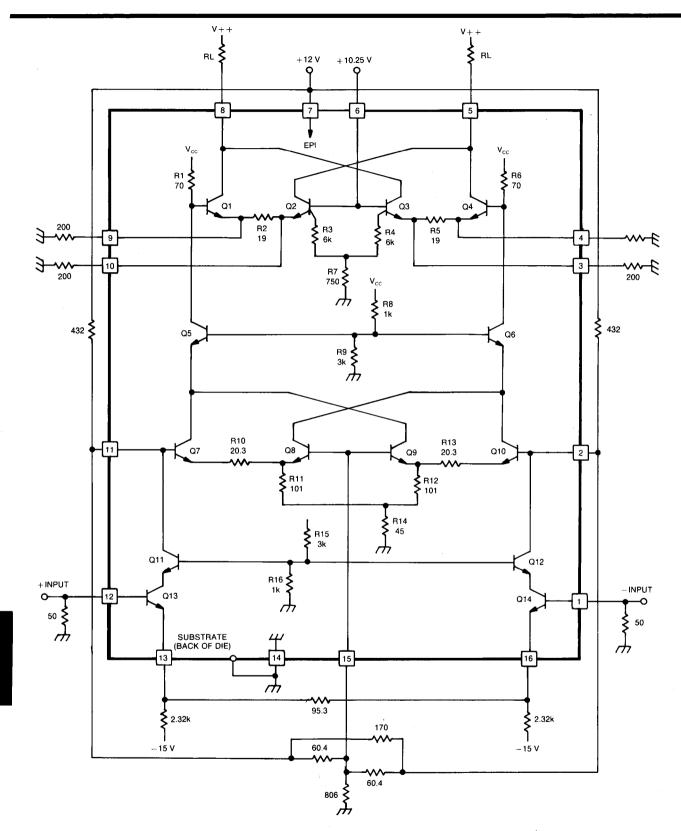

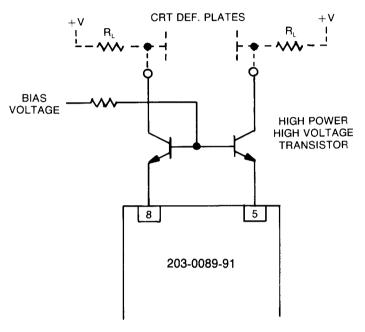

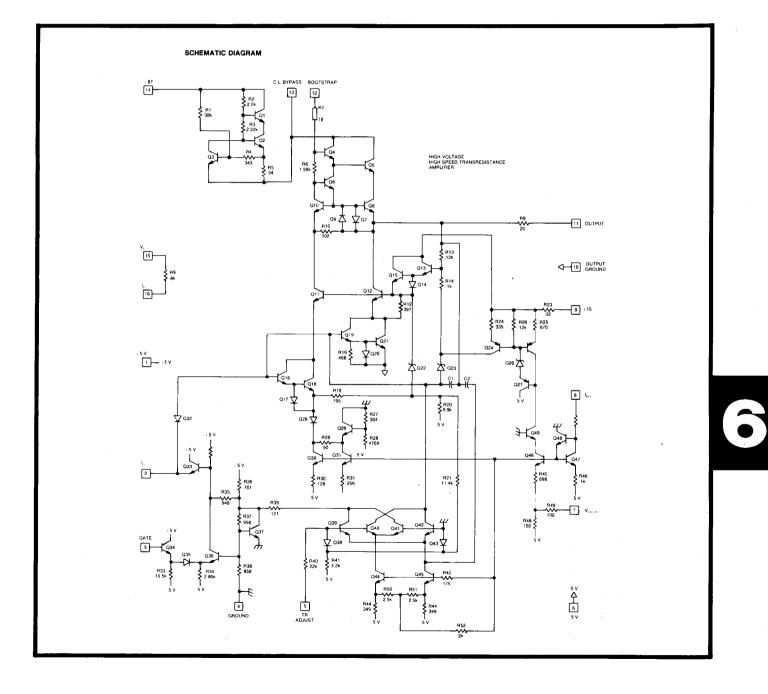

| 203-0084-90 | Differential/variable/invert amplifier |

|-------------|----------------------------------------|

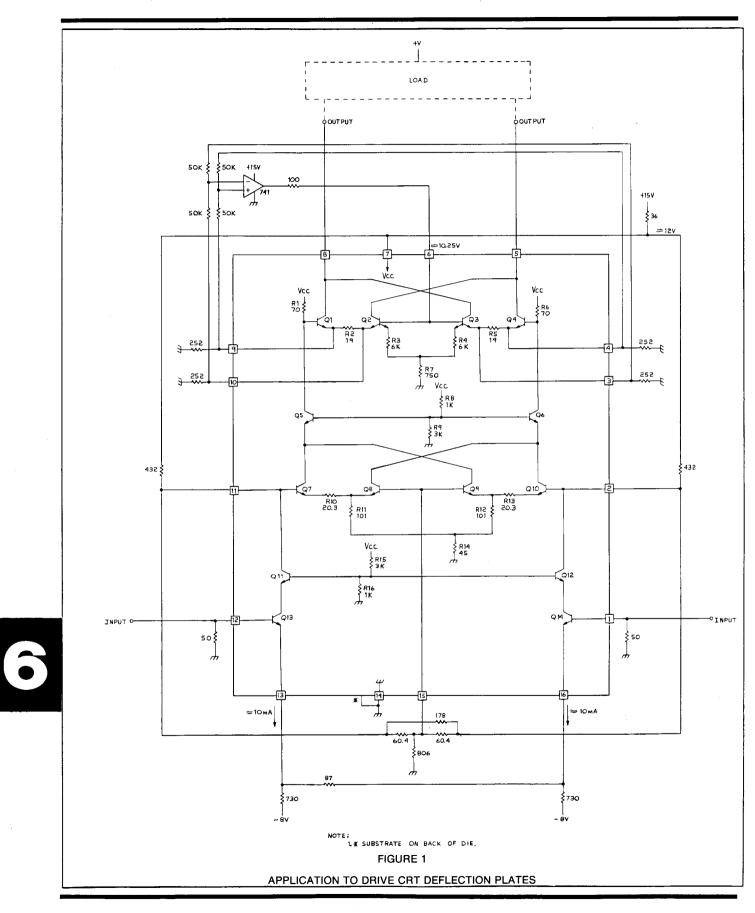

| 203-0089-91 | Vertical output amplifier 6-7          |

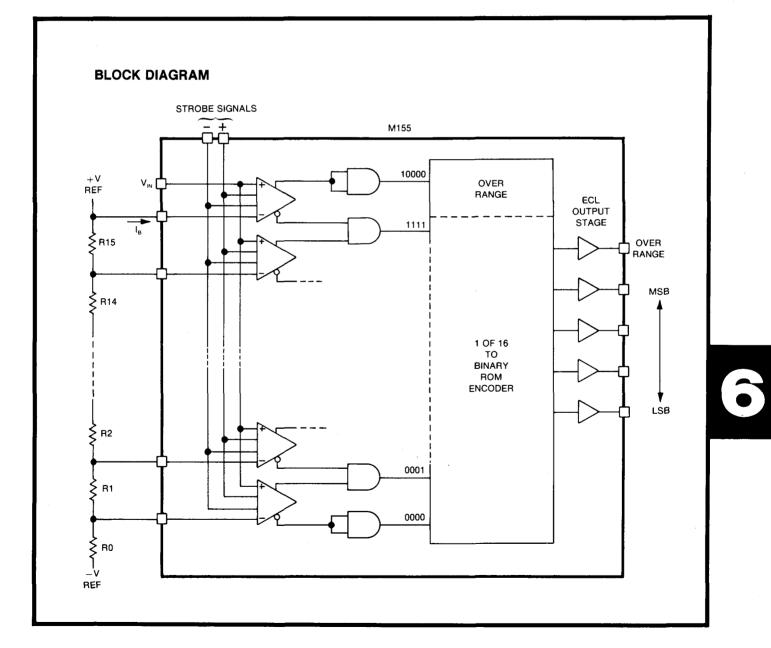

| 203-0155-91 | 4-bit 80 MHz clock flash A/D converter |

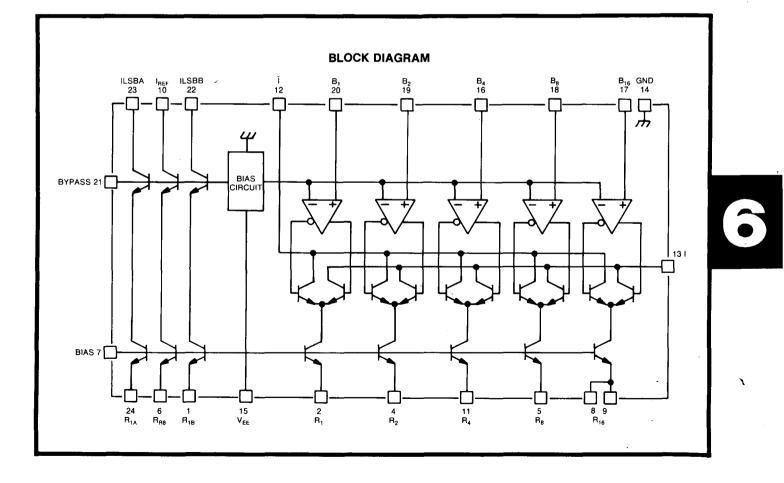

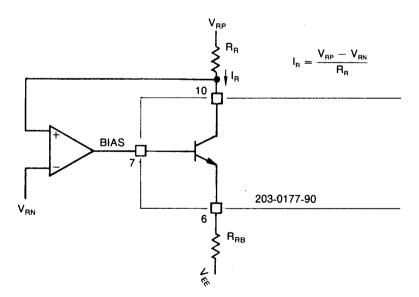

| 203-0177-90 | 5-bit DAC 6-23                         |

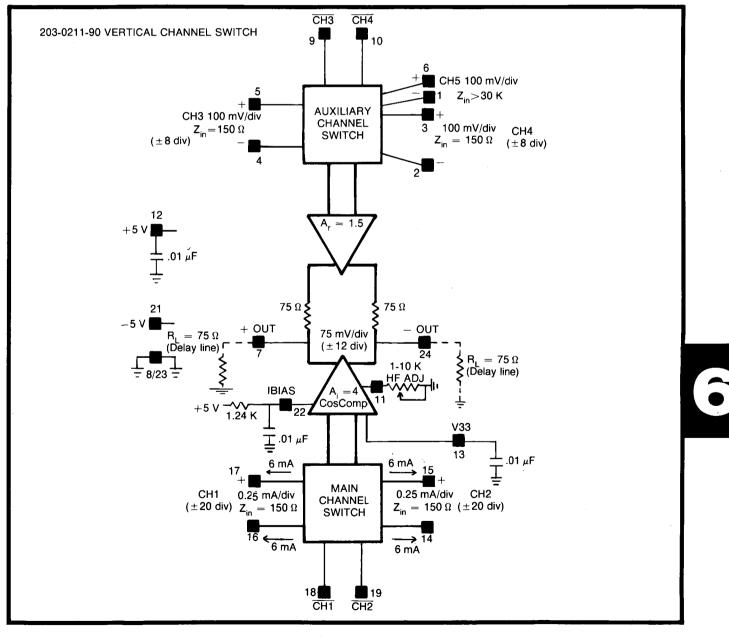

| 203-0211-90 | Channel switch                         |

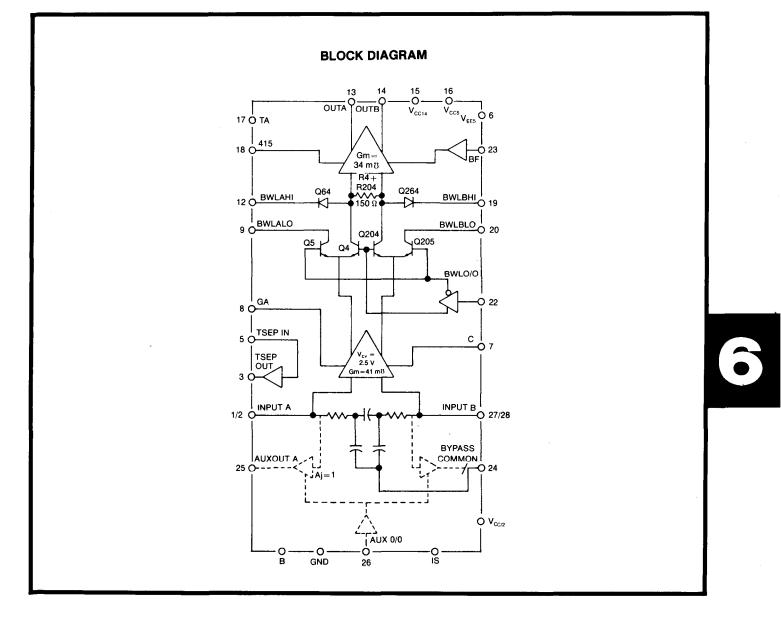

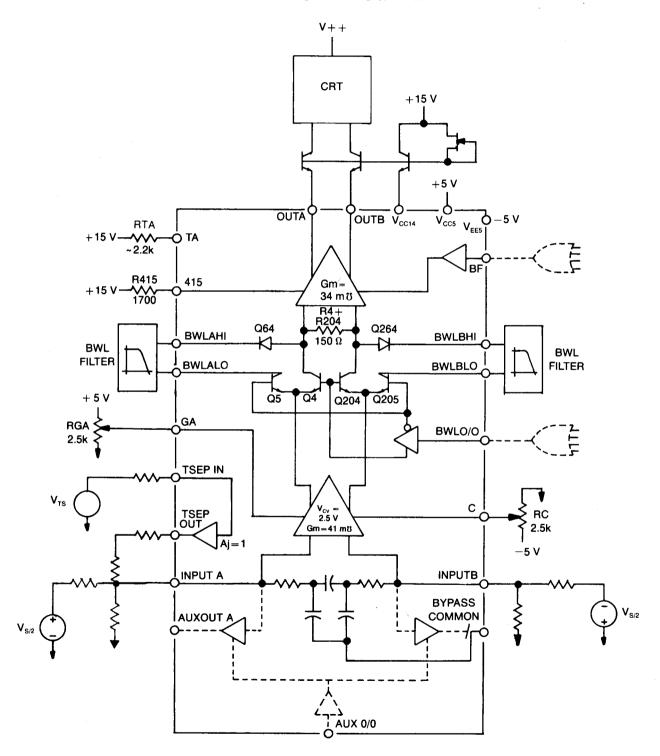

| 203-0212-90 | Vertical output                        |

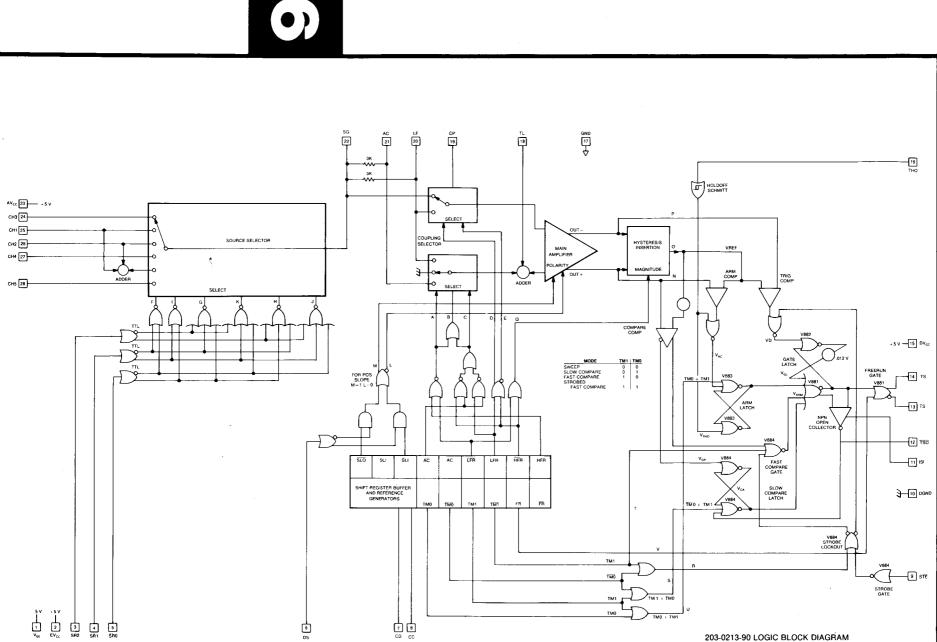

| 203-0213-90 | 600 MHz trigger 6-43                   |

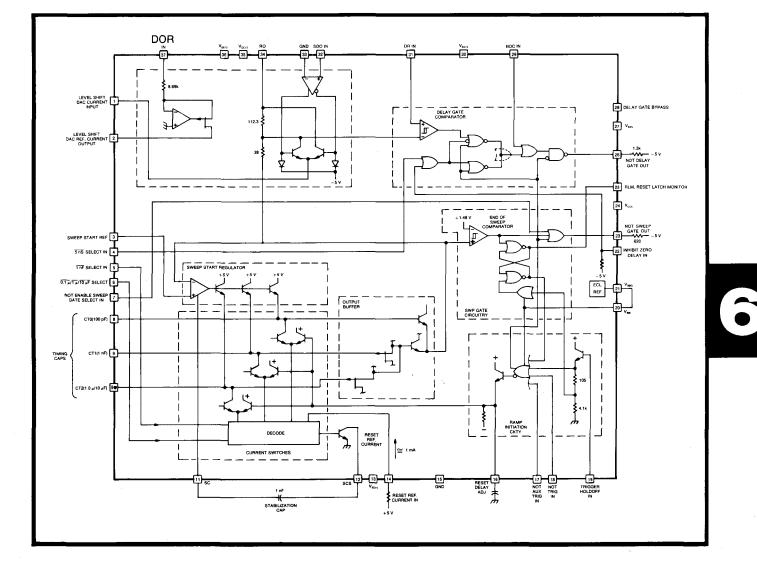

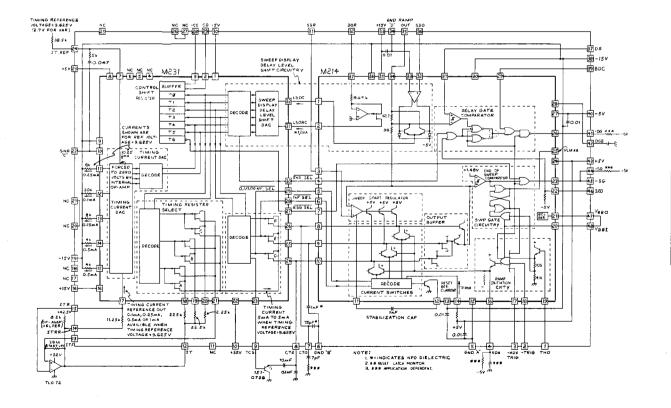

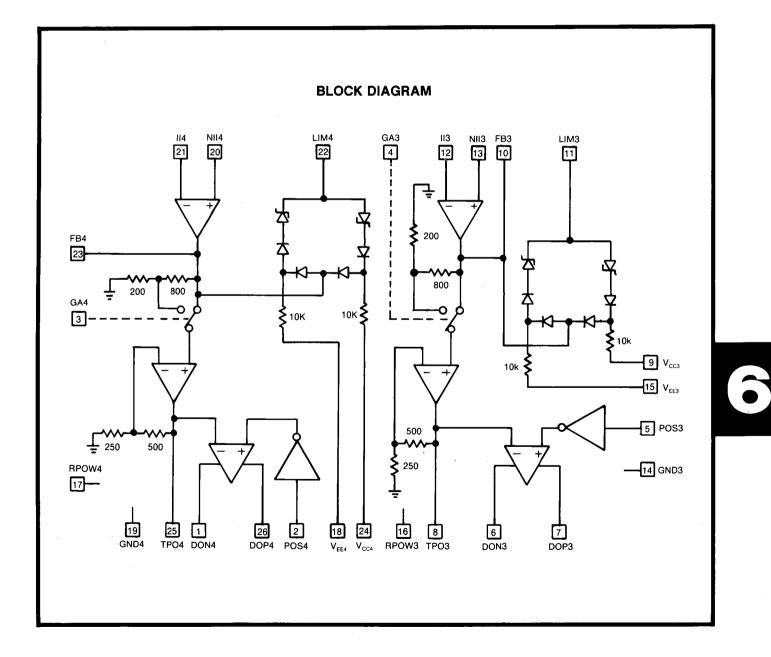

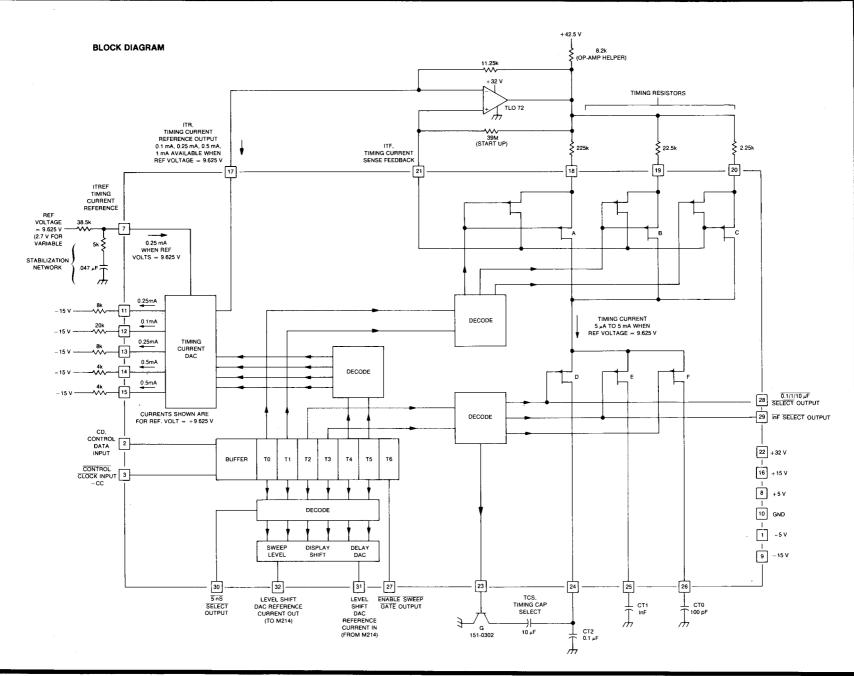

| 203-0214-90 | Sweep DAC & logic 6-53                 |

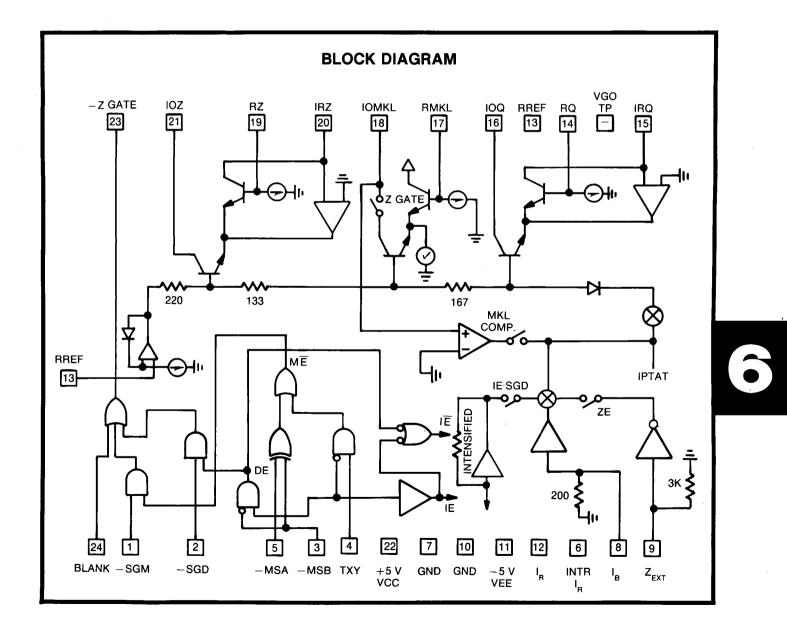

| 203-0216-90 | Z-axis, autofocus amplifier 6-61       |

| 203-0227-90 | Z-axis driver                          |

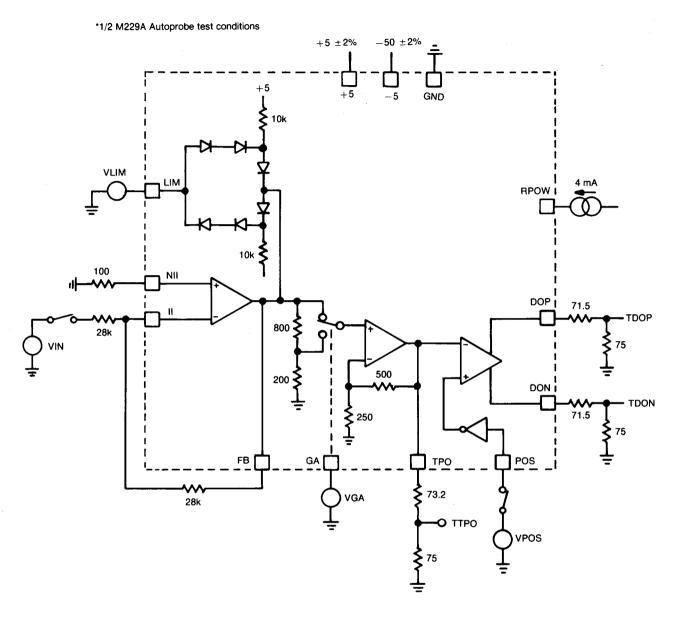

| 203-0229-90 | 300 MHz trigger amplifier 6-73         |

| 203-0231-90 | Sweep integrator 6-81                  |

#### SECTION 7 COSTING

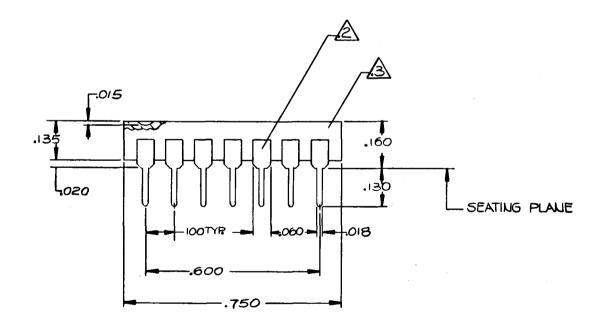

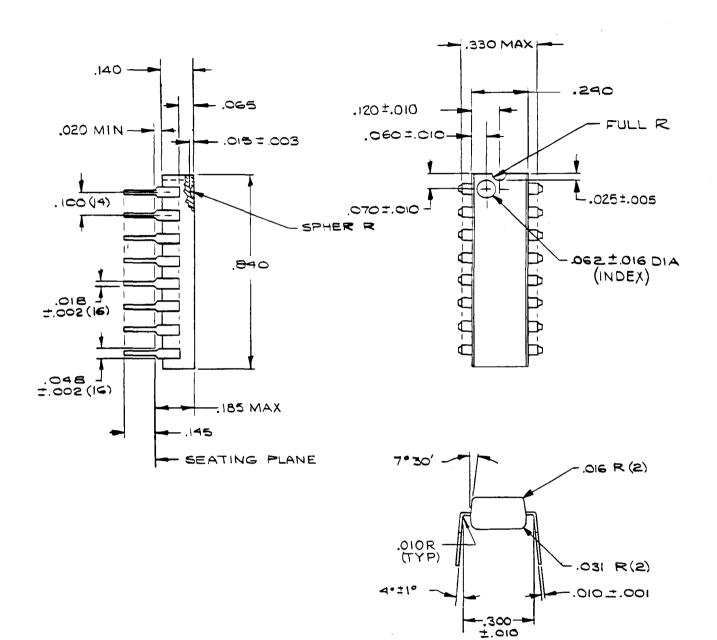

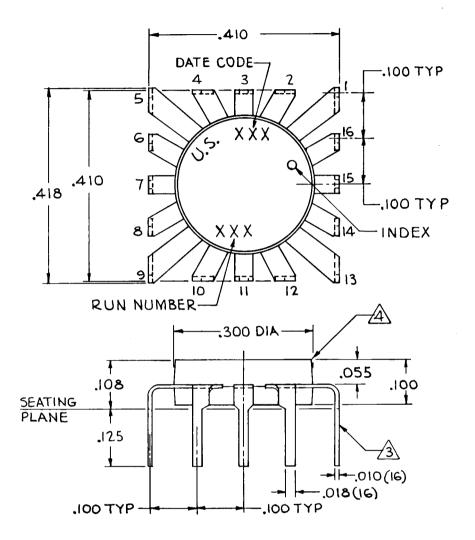

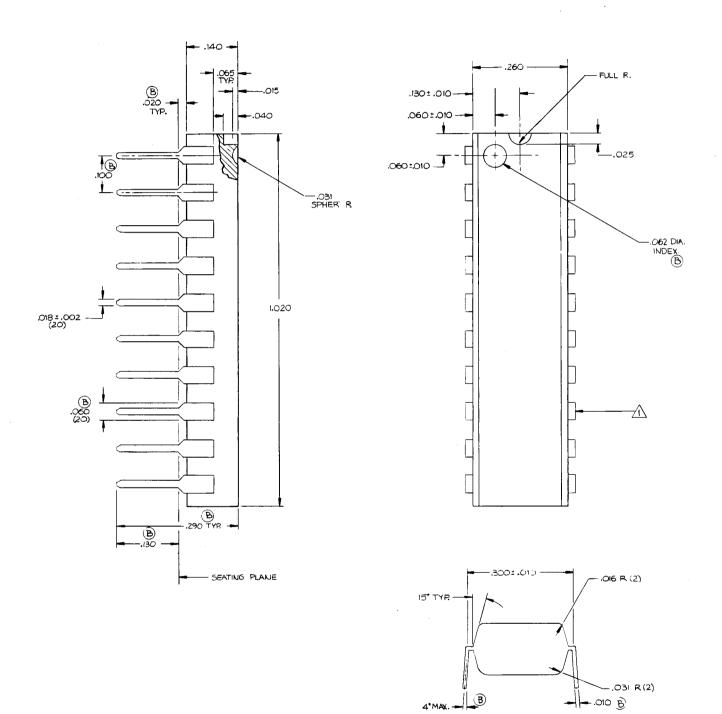

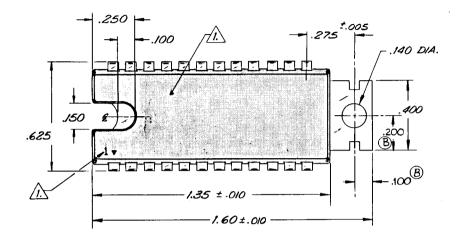

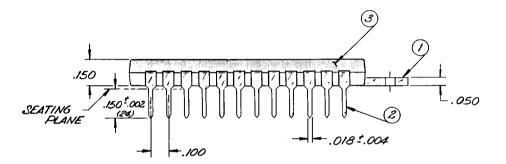

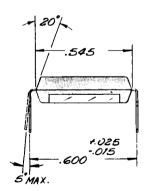

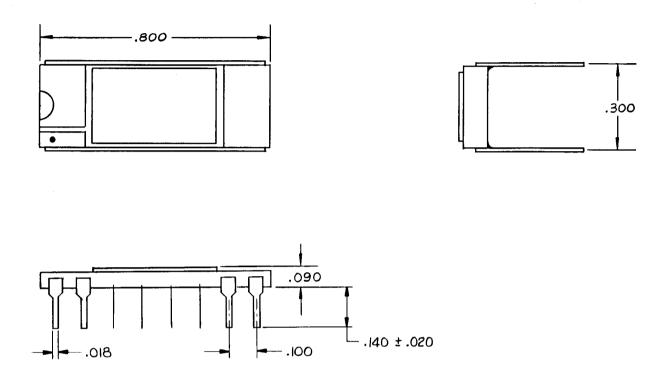

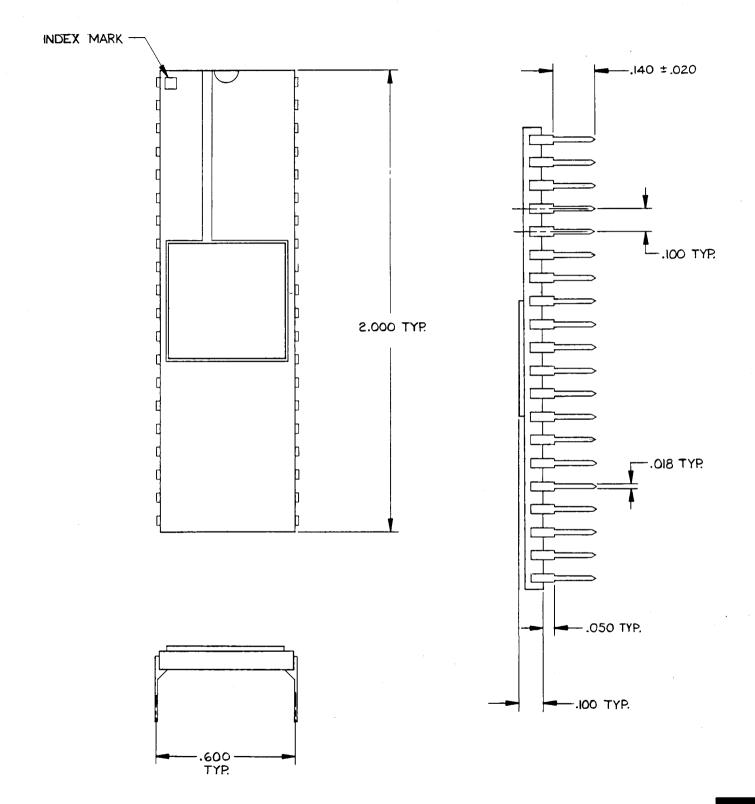

| SECTION 8 | PACKAGE INFORMATION      |

|-----------|--------------------------|

|           | 14-Pin DIP               |

|           | 16-Pin DIP               |

|           | 16-Pin MINIPAC           |

|           | 20-Pin DIP               |

|           | 24-Pin Power Plastic 8-5 |

|           | 16-Pin DIP CER 8-6       |

|           | 40-Pin DIP CER           |

### **INDEX BY FUNCTION**

| Part Number              |                                    | <b>N</b> 1    | Deshawa          | <b>D</b>    |

|--------------------------|------------------------------------|---------------|------------------|-------------|

| Packaged Parts<br>or Die | Description                        | New<br>Design | Package<br>Style | Page<br>No. |

|                          | GENERAL CIRCUITS                   |               |                  |             |

| 155-0022-00              | Channel Switch                     | Ρ             | 16 DIP           | 5-7         |

| 155-0022-01              | Channel Switch                     | S             | 16 DIP           | а           |

| 155-0031-01              | Quad Timing                        | х             | 16 DIP           | а           |

| 155-0047-00              | Dual Output Amplifier              | С             | 16 DIP           | а           |

| 155-0067-02              | Power Supply Controller            | Р             | 16 DIP           | 5-47        |

| 155-0091-00              | Channel Switch                     | S             | 16 Lead TO 8     | а           |

| 155-0106-00              | Normalizing Circuit                | х             | 24 DIP           | а           |

| 155-0111-01              | LED Array                          | Х             | Special          | а           |

| 155-0112-01              | Phototransistor Array              | х             | Special          | а           |

| 155-0145-00              | Pulse Output Amplifier             | Р             | 16 DIP           | 5-99        |

| 155-0157-00              | Digital Storage Vertical Control   | Х             | 40 DIP           | а           |

| 155-0158-00              | Digital Storage Horizontal Control | Х             | 40 DIP           | а           |

| 155-0199-00              | Vertical Control                   | х             | 40 DIP           | а           |

| 155-0205-00              | Channel Switch                     | х             | 16 DIP           | а           |

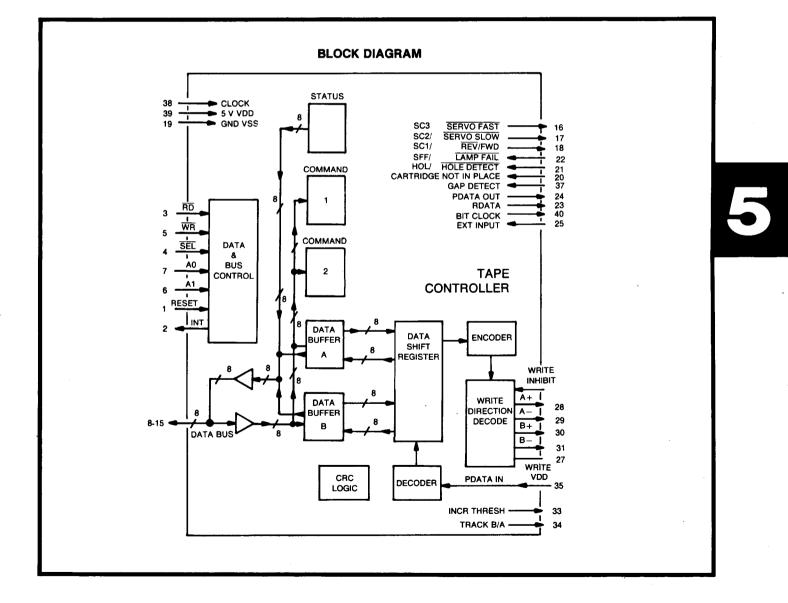

| 155-0247-00              | Tape Controller                    | Р             | 40 DIP           | 5-163       |

| 155-0253-00              | Hi Speed Schmitt Trigger           | Р             | 16 MINIPAC       | 5-171       |

| 155-0283-00              | Video Multiplier                   | Р             | 16 DIP CER .     | 5-187       |

|                          | OPERATIONAL AMPLIFIERS             |               |                  |             |

| 155-0035-00              | Quad Op Amp                        | Р             | 16 DIP           | 5-11        |

| 155-0057-00              | 2 Op Amps, 2 Current Sources       | P             | Plastic          | 5-41        |

| 155-0083-00              | Dual Op Amp and 2 Current Sources  | S             | 16 MINIPAC       | а           |

| 155-0116-00              | Quad Op Amp                        | P             | 16 DIP CER .     | 5-69        |

|                          | OSCILLOSCOPE LOGIC                 |               |                  |             |

| 155-0009-00              | Horizontal Lockout Logic           | S             | 16 DIP           | а           |

| 155-0010-00              | Chop Divider & Blanking            | S             | 10 Lead TO-5     | а           |

| 155-0011-00              | Clock and Chop Blanking            | S             | 16 DIP           | а           |

| 155-0012-00              | Z Axis Logic                       | P             | 16 DIP           | 5-1         |

| 155-0013-00              | Horizontal Chop & Alt Binary       | S             | 10 Lead TO-5     | а           |

| 155-0244-00              | Scope Logic Interface              | Р             | 40 DIP CER .     | 5-149       |

|                          | KNOB READOUT SYSTEM                |               |                  |             |

| 155-0014-01              | Analog to Digital Converter        | S             | 16 DIP           | а           |

| 155-0015-01              | Data Switch                        | S             | 16 DIP           | а           |

| 155-0017-00              | Decade Counter                     | С             | 16 DIP           | а           |

| 155-0018-00              | Zero Logic                         | С             | 16 DIP           | а           |

| 155-0019-00              | Decimal Point & Spacing            | S             | 16 DIP           | а           |

| 155-0020-00              | Output Assembler                   | S             | 16 DIP           | а           |

| 155-0021-01              | Timing Generator                   | S             | 16 DIP           | а           |

| 155-0023-00              | Character Generator                | S             | 16 DIP           | а           |

| 155-0024-00              | Character Generator                | S             | 16 DIP           | а           |

| 155-0025-00              | Character Generator                | S             | 16 DIP           | а           |

| 155-0026-00              | Character Generator                | S             | 16 DIP           | а           |

| 155-0027-00              | Character Generator                | S             | 16 DIP           | а           |

| 155-0086-00              | Legend Generator                   | х             | 20 DIP           | a           |

|                          |                                    |               |                  |             |

NEW DESIGN CODE

زر

$\begin{array}{l} \mathbf{P} \ = \ \mathbf{Preferred} \\ \mathbf{S} \ = \ \mathbf{Suitable} \\ \mathbf{X} \ = \ \mathbf{Do} \ \mathbf{Not} \ \mathbf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

anot included in this catalog.

### **INDEX BY FUNCTION (cont)**

| Part Number              |                                   | New    | Package Page    |

|--------------------------|-----------------------------------|--------|-----------------|

| Packaged Parts<br>or Die | Description                       | Design | Style No.       |

|                          | KNOB READOUT SYSTEM               | (cont) |                 |

| 155-0087-00              | Legend Generator                  | Х      | 20 DIP a        |

| 155-0088-00              | Legend Generator                  | Х      | 20 DIP a        |

| 155-0104-00              | Legend Generator                  | Х      | 20 DIP a        |

| 155-0105-00              | Legend Generator                  | Х      | 20 DIP a        |

| 155-0110-00              | Legend Generator                  | S      | 20 DIP a        |

| 155-0135-00              | Legend Generator                  | Х      | 20 DIP a        |

| 155-0171-00              | 4 Decade Counter and Memory       | S      | 16 MINIPAC a    |

| 155-0198-00              | Knob Readout Counter              | х      | 40 DIP a        |

|                          | READOUT SYSTEM                    |        |                 |

| 155-0004-01              | Beta Computer                     | х      | 16 DIP a        |

| 155-0005-00              | Beta Computer                     | х      | 16 DIP a        |

| 155-0006-00              | Beta Computer                     | х      | 16 DIP a        |

| 155-0007-01              | Readout I                         | Х      | 16 DIP a        |

| 155-0008-01              | Readout II                        | Х      | 16 DIP a        |

| 155-0114-00              | Seven Segment Character Generator | S      | 16 DIP a        |

| 155-0119-00              | Five Digit BCD Counter            | Х      | 40 DIP a        |

|                          | HORIZONTAL SYSTEM                 | И      |                 |

| 155-0028-00              | Miller Integrator & Dly Pickoff   | С      | 10 Lead TO-5 a  |

| 155-0028-01              | Miller Integrator & Dly Pickoff   | С      | 10 Lead TO-5 a  |

| 155-0048-01              | Trigger & Sweep                   | P      | 16 MINIPAC 5-21 |

| 155-0049-02              | Sweep Control                     | Р      | 20 DIP 5-27     |

| 155-0055-00              | Trigger & Sweep                   | Р      | 16 DIP 5-35     |

| 155-0056-00              | Sweep Control                     | С      | 16 DIP a        |

| 155-0109-01              | Trigger Circuit                   | Р      | 16 DIP 5-61     |

| 155-0121-00              | Trigger Subsystem                 | Х      | 16 DIP a        |

| 155-0122-00              | Sweep Control                     | Р      | 16 DIP 5-75     |

| 155-0123-00              | Sweep & Pickoff                   | Р      | 16 DIP 5-81     |

| 155-0124-00              | Horizontal Preamplifier           | Р      | 16 DIP 5-87     |

| 155-0126-00              | Trig Amp, Source Select           | Р      | 20 DIP a        |

| 155-0151-00              | Trigger Generator                 | х      | 20 DIP a        |

| 155-0160-00              | Trigger Amplifier, Source Select  | С      | 16 MINIPAC a    |

| 155-0196-00              | Trigger Circuit                   | Р      | 20 DIP 5-125    |

| 155-0216-00              | Amplifier                         | S      | 16 DIP a        |

| 155-0217-00              | Amplifier                         | Р      | 16 DIP 5-137    |

| 155-0241-00              | Horizontal Amplifier              | С      | Power Pkg a     |

| 203-0196-90              | Horizontal Clamp                  | C      | a               |

| 203-0213-90              | 600 MHz Trigger                   | P      | 6-43            |

| 203-0214-90              | Sweep DAC & Logic                 | Р      | 6-53            |

| 203-0229-90              | 300 MHz Trigger Amplifier         | Р      | 6-73            |

| 203-0231-90              | Sweep Integrator                  | Р      | 6-81            |

|                          |                                   |        |                 |

#### **NEW DESIGN CODE**

$\begin{array}{l} \mathsf{P} = \mathsf{Preferred} \\ \mathsf{X} = \mathsf{Suitable} \\ \mathsf{X} = \mathsf{Do} \ \mathsf{Not} \ \mathsf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

anot included in this catalog.

### INDEX BY FUNCTION (cont)

| Part Number    |                                        |        |              |       |

|----------------|----------------------------------------|--------|--------------|-------|

| Packaged Parts |                                        | New    | Package      | Page  |

| or Die         | Description                            | Design | Style        | No.   |

|                | AD/DA CIRCUITS                         |        |              |       |

| 155-0038-01    | D/A Converter                          | S      | 16 DIP       | а     |

| 155-0038-02    | D/A Converter                          | Р      | 16 DIP       | 5-17  |

| 155-0185-00    | 4 Decade DVM                           | S      | 20 DIP CER . | а     |

| 203-0155-91    | 4 Bit Flash A/D Converter              | Р      |              | 6-17  |

| 203-0175-90    | Dual High Speed Comparator             | С      |              | а     |

| 203-0177-90    | 5 Bit DAC                              | Р      |              | 6-23  |

|                | VERTICAL AMPLIFIER                     | s      |              |       |

| 155-0050-01    | Vertical Amplifier                     | S      | 20 DIP       | а     |

| 155-0059-00    | Gain Trim Amplifier                    | S      | 12 Lead TO-8 |       |

| 155-0061-00    | F <sub>t</sub> Doubler Amplifier       | S      | 16 DIP       | а     |

| 155-0078-10    | Diff/Var/Inv Amplifier                 | P      | 16 MINIPAC   | 5-53  |

| 155-0187-00    | Ft Doubler Amplifier                   | S      | 12 Lead TO-8 | а     |

| 155-0207-00    | Output Amplifier                       | x      | 24 DIP       | а     |

| 155-0218-00    | Output Amplifier                       | Р      | 20 DIP       | 5-141 |

| 155-0273-00    | Diff/Var/Inv Amplifier                 | P      | 14 DIP       |       |

| 155-0274-00    | Diff/Var/Inv Amplifier                 | P      | 14 DIP       |       |

| 203-0080-90    | Vertical Output Amplifier              | S      |              |       |

| 203-0084-00    | Differential/Variable/Invert Amplifier | P      |              | _     |

| 203-0089-91    | Vertical Output Amplifier              | P      |              |       |

| 203-0122-90    | 1 GHz Trigger                          | C      |              | а     |

| 203-0126-90    | F <sub>t</sub> Doubler                 | S      |              |       |

| 203-0130-90    | 100 MHz Vertical Preamp                | Ċ      |              |       |

| 203-0178-90    | 1 GHz Vertical Amplifier               | С      |              | а     |

| 203-0198-90    | Clamp & Sensor                         | С      |              | а     |

| 203-0199-90    | 1 GHz Input Amplifier                  | С      |              | а     |

| 203-0210-90    | Vertical Preamp                        | С      |              | а     |

| 203-0211-90    | Channel Switch                         | Р      |              | 6-29  |

| 203-0212-90    | Vertical Output Amplifier              | Р      |              | 6-33  |

|                | TV and CRT CONTROL CIR                 | CUITS  |              |       |

| 155-0051-00    | Z-Axis & HV Regulator                  | S      | 20 DIP       | а     |

| 155-0144-00    | Sync Stripper                          | P ·    | 16 DIP       | 5-93  |

| 155-0152-01    | CRT Geometry Correction                | Р      | 16 DIP       | 5-103 |

| 155-0154-00    | Display Multiplexer                    | Р      | 20 DIP       | 5-111 |

| 155-0188-00    | TV Sync Generator                      | Р      | 40 DIP       | 5-117 |

| 203-0216-90    | Z Axis Autofocus                       | Р      |              |       |

| 203-0227-90    | Z Axis Driver                          | Р      |              |       |

|                | PROBE CIRCUITS                         | •      |              |       |

| 155-0076-00    | Input Protection & Probe Logic         | С      | 16 MINIPAC   | а     |

| 155-0215-00    | Logic Analysis Input                   | P      | 16 DIP       | 5-131 |

| 206-0186-09    | Transistor Temperature Probe           | x      | Special      | a     |

| 206-0248-00    | Platinum Temperature Probe Tip         | P      | Special      | 5-193 |

| 203-0096-90    | Logic Probe                            | ×      |              | a     |

|                | -                                      |        |              |       |

**NEW DESIGN CODE**

P = PreferredX = Suitable

....

•

\* • \*

X = Do Not Use

$\mathbf{C} = \mathbf{Call}$  Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

anot included in this catalog.

### **INDEX BY FUNCTION (cont)**

| Part Number<br>Packaged Parts<br>or Die | Description           | New<br>Design | Package Pag<br>Style No | - |

|-----------------------------------------|-----------------------|---------------|-------------------------|---|

|                                         | DISCRETES             |               |                         |   |

| 151-0659-00                             | NPN Power Transistor  | С             | ТО-39 а                 | ı |

| 151-1139-00                             | Dual FET              | С             | Special a               |   |

| 152-0442-00                             | Schottky Diode        | х             | Special a               |   |

| 152-0442-01                             | Schottky Diode Pair   | х             | Special a               | , |

| 152-0446-00                             | Schottky Diode Pair   | Х             | Special a               | 1 |

| 152-0446-01                             | Schottky Diode Single | Х             | Special a               | 1 |

| 152-0646-00                             | Schottky Diode Pair   | С             | Micro T a               | 1 |

| 152-0646-02                             | Schottky Diode Pair   | С             | Micro T a               | ı |

| 203-0032-90                             | Schottky Diode        | С             | a                       | 1 |

| 203-0075-90                             | NPN Transistor        | С             | a                       |   |

| 203-0206-90                             | NPN Transistor        | С             | a                       |   |

| 203-0264-90                             | Schottky Diode        | С             | a                       | , |

| 203-0269-90                             | EBS Target Diodes     | С             | a                       | I |

|                                         |                       |               |                         |   |

**NEW DESIGN CODE**

$\begin{array}{l} \mathsf{P} = \mathsf{Preferred} \\ \mathsf{X} = \mathsf{Suitable} \\ \mathsf{X} = \mathsf{Do} \ \mathsf{Not} \ \mathsf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

not included in this catalog.

**\$**,

### **INDEX BY PART NUMBER**

| Part Number<br>PACKAGED PARTS | Description                 |     | New<br>Design      | Page<br>No. |

|-------------------------------|-----------------------------|-----|--------------------|-------------|

| 131-1393-00                   | Programmed Connector        | х   |                    | a           |

| 131-1394-00                   | Programmed Connector        | X   |                    | а           |

| 131-1395-00                   | Programmed Connector        | X   |                    | а           |

| 131-1396-00                   | Programmed Connector        | X   |                    | а           |

| 131-1659-00                   | Programmed Connector        | x   |                    | а           |

| 131-1660-00                   | Programmed Connector        | X   |                    | а           |

| 151-0659-00                   | NPN Power Transistor        | ĉ   |                    | а           |

| 151-1139-00                   | Dual FET                    | ċ   |                    | а           |

| 152-0442-00                   | Schottky Diode Pair         | x   |                    | а           |

| 152-0442-01                   | Schottky Diode Pair         | X   |                    | а           |

| 152-0446-00                   | Schottky Díode Pair         | _   |                    | а           |

| 152-0446-01                   | Schottky Diode Pair         |     |                    | а           |

| 152-0646-00                   | Schottky Diode Pair         | C   |                    | а           |

| 152-0646-02                   | Schottky Diode Pair         | č   |                    | а           |

| 152-0004-01                   | 576 Readout System          | x   |                    | а           |

| 155-0005-00                   | 576 Readout System          | X   |                    | а           |

| 155-0006-01                   | 576 Readout System          | X   |                    | а           |

| 155-0007-01                   | 576 Readout System          | X   |                    | а           |

| 155-0008-01                   | 576 Readout System          | X   |                    | а           |

| 155-0009-00                   | Horizontal Lockout Logic    | S   |                    | а           |

| 155-0010-00                   | Chop Divider, Blanking      | S   |                    | а           |

| 155-0011-00                   | Clock, Chop Blanking        | Š   |                    | а           |

| 155-0012-00                   | Z Axis Signal Conditioning  | P   |                    | 5-1         |

| 155-0013-00                   | Horizontal, Chop Alt Binary | S   |                    | a           |

| 155-0014-01                   | A/D Converter               | Š   |                    | а           |

| 155-0015-01                   | Data Switch                 | S   |                    | a           |

| 155-0017-00                   | Decade Counter              | č   |                    | а           |

| 155-0018-00                   | Zero Logic                  | č   |                    | а           |

| 155-0019-00                   | Decade Counter              | s   |                    | а           |

| 155-0020-00                   | Output Assembler            | ŝ   |                    | а           |

| 155-0021-01                   | Scan Osc. Logic Timing Gen. | S   |                    | а           |

| 155-0022-00                   | 2 Input Channel Switch      | P   |                    | 5-7         |

| 155-0022-01                   | 2 Input Channel Switch      | S   |                    | а           |

| 155-0023-00                   | Character Generator         | S   |                    | а           |

| 155-0024-00                   | Character Generator         | S   |                    | а           |

| 155-0025-00                   | Character Generator         | S   |                    | а           |

| 155-0026-00                   | Character Generator         | S   |                    | а           |

| 155-0027-00                   | Character Generator         | S   |                    | а           |

| 155-0028-00                   | Miller Integrator           | С   |                    | а           |

| 155-0028-01                   | Miller Integrator           | . C |                    | а           |

| 155-0031-01                   | Quad Timing Unit            | X   |                    | a           |

| 155-0035-00                   | Quad Op. Amp.               | Р   |                    | 5-11        |

| 155-0038-01                   | 5-bit Precision D/A         | S   |                    | а           |

| 155-0038-02                   | 5-bit Precision D/A         | Р   | <b></b> <i>.</i> . | 5-17        |

| 155-0047-00                   | Dual Output Amplifier       | S   |                    | а           |

| 155-0048-01                   | 5 MHz Trigger and Sweep     | Р   |                    | 5-21        |

| 155-0049-02                   | Sweep Control               | Р   |                    | 5-27        |

| 155-0050-01                   | Vertical Preamp             | S   |                    | 8           |

| 155-0051-00                   | Z Axis, HV Regulator        | S   |                    | a           |

| 155-0055-00                   | 5 MHz Trigger and Sweep     | Р   |                    | 5-35        |

|                               | -                           |     |                    |             |

#### NEW DESIGN CODE

P = Preferred X = SuitableX = Do Not Use

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

anot included in this catalog.

E

### **INDEX BY PART NUMBER (cont)**

| Part Number<br>PACKAGED PARTS | Description                                            | New<br>Desigr | Page<br>No.  |

|-------------------------------|--------------------------------------------------------|---------------|--------------|

|                               |                                                        |               |              |

| 155-0056-00                   | Sweep Control                                          | С             |              |

| 155-0057-00                   | Dual Op. Amp, Current Source                           | Ρ             |              |

| 155-0059-00                   | Gain Trim Amplifier                                    | S             |              |

| 155-0061-00                   | F <sub>t</sub> Doubler Amplifier                       | S             |              |

| 155-0067-02                   | DC to DC Inverter Regulator                            | Ρ             |              |

| 155-0076-00                   | Input Protection                                       | С             |              |

| 155-0078-10                   | Differential/Variable/Invert Amp                       | Ρ             |              |

| 155-0083-00                   | Dual Op Amp, Current Source                            | S             |              |

| 155-0086-00                   | Legend Generator                                       | Χ             |              |

| 155-0087-01                   | Legend Generator                                       | Χ             |              |

| 155-0088-00                   | Legend Generator                                       | Χ             | <sup>a</sup> |

| 155-0091-00                   | 250 MHz Channel Switch                                 | S             |              |

| 155-0104-00                   | Legend Generator                                       | Χ             | a            |

| 155-0105-00                   | Legend Generator                                       | Χ             | а            |

| 155-0106-00                   | Normalizing Circuit                                    | Χ             | <sup>a</sup> |

| 155-0109-01                   | 350 MHz Trigger                                        | Ρ             | 5-61         |

| 155-0110-00                   | Legend Generator                                       | S             | a            |

| 155-0111-01                   | LED Array                                              | Χ             | а            |

| 155-0112-01                   | Photo Transistor Array                                 | Χ             |              |

| 155-0114-00                   | 7-segment Character Generator                          | S             | а            |

| 155-0116-00                   | Quad Op. Amps.                                         | Ρ             | 5-69         |

| 155-0119-00                   | 5-digit BCD Counter                                    | Χ             |              |

| 155-0121-00                   | 50 MHz Trigger                                         | Χ             | а            |

| 155-0122-00                   | Sweep Control                                          | Ρ             |              |

| 155-0123-00                   | 50 ns Sweep & Delay Pickoff                            | Ρ             |              |

| 155-0124-00                   | 5 ns Horizontal Preamp                                 | Ρ             |              |

| 155-0126-00                   | Trigger Amp/Source Select                              | Ρ             |              |

| 155-0135-00                   | Legend Generator                                       | X             |              |

| 155-0144-00                   | TV Sync Stripper                                       | Ρ             |              |

| 155-0145-00                   | Controlled Risetime Amplifier                          | Ρ             |              |

| 155-0151-00                   | 100 MHz Trigger                                        | X             |              |

| 155-0152-01                   | Magnetic Deflected CRT Geometry                        | Χ             |              |

| 133-0132-01                   | Correction                                             | Р             | 5-103        |

| 155-0154-00                   | 3 Input Multiplexer                                    | Ρ             |              |

| 155-0157-00                   |                                                        | X             |              |

|                               | Vertical Digital Storage                               | X             |              |

| 155-0158-00                   | Horizontal Digital Storage<br>Trigger Source/Amplifier | C             |              |

| 155-0160-00<br>155-0171-00    |                                                        | S             | •••          |

|                               | 4 Decade Counter Memory                                |               |              |

| 155-0185-00                   | 4 Decade DVM                                           | S<br>S        |              |

| 155-0187-00                   | F <sub>t</sub> Doubler                                 |               | •••          |

| 155-0188-00                   | TV Sync Generator                                      | Ρ             |              |

| 155-0196-00                   | 100 MHz Trigger                                        | Ρ             |              |

| 155-0198-00                   | Knob Readout Counter                                   | X             |              |

| 155-0199-00                   | Vertical Control                                       | Χ             | •••          |

| 155-0205-00                   | F <sub>t</sub> Doubler                                 | Χ             | • • •        |

| 155-0207-00                   | Vertical Output                                        | X             |              |

| 155-0215-00                   | Logic Analyzer Input                                   | Ρ             |              |

| 155-0216-00                   | Amplifier                                              | S             |              |

| 155-0217-00                   | Amplifier                                              | Ρ             |              |

| 155-0218-00                   | Vertical Output                                        | Ρ             |              |

| 155-0241-01                   | Horizontal Amplifier                                   | С             |              |

| 155-0244-00                   | Scope Logic Interface                                  | Ρ             |              |

| 155-0247-00                   | Tape Controller                                        | Ρ             | 5-163        |

|                               |                                                        |               |              |

#### **NEW DESIGN CODE**

$\begin{array}{l} {\sf P} = {\sf Preferred} \\ {\sf X} = {\sf Suitable} \\ {\sf X} = {\sf Do} \; {\sf Not} \; {\sf Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die not included in this catalog.

### INDEX BY PART NUMBER (cont)

| Part Number<br>PACKAGED PARTS | Description                            |   | New<br>Design | Page<br>No. |

|-------------------------------|----------------------------------------|---|---------------|-------------|

| 155-0253-00                   | Schmitt Trigger                        | Р |               | 5-171       |

| 155-0273-00                   | Differential/Variable/Invert Amplifier | P |               | 5-175       |

| 155-0274-00                   | Differential/Variable/Invert Amplifier | P |               | 5-181       |

| 155-0283-00                   | Video Multiplier                       | P |               | 5-187       |

| DIE                           |                                        | · |               | 0.01        |

| 203-0032-90                   | Schottky Diode                         | с |               | а           |

| 203-0075-90                   | NPN Transistor                         | č |               | а           |

| 203-0080-90                   | Vertical Output Amplifier              | Š |               | а           |

| 203-0084-90                   | Differential/Variable/Invert Amplifier | P |               | 6-1         |

| 203-0089-91                   | Vertical Output Amplifier              | P |               | 6-7         |

| 203-0096-90                   | Logic Probe                            | x |               | a -         |

| 203-0122-90                   | 1 GHz Trigger                          | ĉ |               | а           |

| 203-0126-90                   |                                        | ŝ |               | а           |

| 203-0130-90                   | 100 MHz Vertical Preamp                | č |               | а           |

| 203-0155-91                   | 4-bit Flash A/D Converter              | P |               | 6-17        |

| 203-0175-90                   | Dual Comparator                        | Ċ |               | a           |

| 203-0177-90                   | 5-bit D/A Converter                    | P |               | 6-23        |

| 203-0178-90,91,92             | 1 GHz Vertical Amplifier               | Ċ |               | a           |

| 203-0196-90                   | Horizontal Clamp                       | č |               | а           |

| 203-0197-90                   | Horizontal Output                      | č |               | а           |

| 203-0198-90                   | Clamp & Sensor                         | Č |               | а           |

| 203-0199-90                   | 1 GHz Input Amplifier                  | č |               | а           |

| 203-0206-90                   | NPN Transistor                         | Č |               | a           |

| 203-0210-90                   | 300 MHz Vertical Preamp                | Ċ |               | а           |

| 203-0211-90                   | 300 MHz Channel Switch                 | Р |               | 6-29        |

| 203-0212-90                   | 300 MHz Vertical Output                | Р |               | 6-33        |

| 203-0213-90                   | 300 MHz Trigger                        | Р |               | 6-43        |

| 203-0214-90                   | Sweep DAC & Logic                      | Р |               | 6-53        |

| 203-0216-90                   | Z Axis, Autofocus Amplifier            | Р |               | 6-61        |

| 203-0227-90                   | Z Axis Driver                          | Р |               | 6-67        |

| 203-0229-90                   | 300 MHz Trigger                        | Р |               | 6-73        |

| 203-0231-90                   | Sweep Integrator                       | P |               | 6-81        |

| 203-0264-90                   | Schottky Diode                         | С |               | а           |

| 203-0265-90                   | Schottky Diode                         | С |               | а           |

| 203-0266-90                   | Schottky Diode                         | С |               | а           |

| 203-0268-90                   | PNP Transistor                         | Х |               | а           |

| 203-0269-90                   | EBS Target Diodes                      | С |               | а           |

| 203-0270-90                   | NPN Transistor                         | С |               | а           |

| 203-0271-90                   | NPN Transistor                         | С |               | а           |

| 203-0276-90                   | 50 Resistor                            | Х |               | а           |

| 203-0290-00                   | Schottky Diode                         | Х |               | а           |

| 206-0186-09                   | Transistor Temperature Probe           | Х |               | а           |

| 206-0248-00                   | Platinum Temperature Probe             | P |               | 5-193       |

#### **NEW DESIGN CODE**

$\begin{array}{l} \mathsf{P} = \mathsf{Preferred} \\ \mathsf{X} = \mathsf{Suitable} \\ \mathsf{X} = \mathsf{Do} \ \mathsf{Not} \ \mathsf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

#### M Number vs. Package Part Number

Packaged Part No./Die No.

|             | ·                                                    |

|-------------|------------------------------------------------------|

| M01A        | 155-0009-00                                          |

| M04         | 155-0010-00                                          |

| M12B        | 155-0011-00                                          |

| M15B        | 155-0012-00                                          |

| M18H        | 155-0028-00/01                                       |

| M19F        | 155-0014-01                                          |

|             |                                                      |

| M20J        | 155-0015-01                                          |

| M22         | 155-0013-00                                          |

| M25E        | 155-0017-00                                          |

| M26D        | 155-0018-00                                          |

| M27B        | 155-0019-00                                          |

| M28C        | 155-0020-00                                          |

| M29B        | 155-0021-01                                          |

| D32A        | 152-0646-00                                          |

| M33B        | 155-0004-01                                          |

| M34C        | 155-0005-00                                          |

| M35B        | 155-0006-01                                          |

| M36K        | 155-0022-00/01                                       |

| M38C        | 155-0007-01                                          |

| M39C        | 155-0008-01                                          |

| M42D        | 155-0056-00                                          |

| M45D        | 155-0038-01/02                                       |

| M402<br>M47 | 155-0031-01/                                         |

|             | 155-0047-00                                          |

|             | 155-0048-00, 155-0055-00                             |

| M52G        | -                                                    |

| M55E        | 155-0035-00, 155-0116-00<br>155-0216-00, 155-0217-00 |

| M65         | 155-0050-01                                          |

|             |                                                      |

| M68         | 155-0051-00                                          |

| M77A        | 155-0059-00                                          |

| M79H        | 155-0049-02                                          |

| M80F        | 203-0080-90                                          |

| M83         | 155-0061-00                                          |

| M84F        | 155-0078-10, 155-0274-00                             |

| M89A        | 203-0089-91                                          |

| M91E        | 155-0067-02                                          |

| M94B        | 155-0076-00                                          |

| M95A        | 155-0091-00                                          |

| M96F        | 203-0096-90                                          |

| M101B       | 155-0106-00                                          |

| M105        | 155-0083-00                                          |

| M112A       | 155-0198-00                                          |

| D113C       | 155-0112-01                                          |

| M115A       | 155-0199-00                                          |

| M119        | 155-0110-00                                          |

| M120D       | 155-0109-01                                          |

| M121D       | 155-0126-00                                          |

| M122C       | 203-0122-90                                          |

| M123A       | 155-0119-00                                          |

| M124A       | 155-0144-00                                          |

|             |                                                      |

**NEW DESIGN CODE**

P = Preferred

X = SuitableX = Do Not Use

155-XXXX = Packaged Parts 203-XXXX = Die

Γ

#### M Number vs. Package Part Number (cont)

|                | Packaged Part No./Die No. (cont) |

|----------------|----------------------------------|

|                |                                  |

| M126           | 203-0126-90                      |

| M127D          | 155-0114-00                      |

| M130           | 203-0130-90                      |

| M131A          | 155-0121-00                      |

| M132A          | 155-0122-00                      |

| M133A          | 155-0123-00                      |

| M136D          | 155-0160-00                      |

| M138           | 155-0124-00                      |

| M150A          | 155-0171-00                      |

| M151A          | 155-0145-00                      |

| M152D          | 155-0152-01                      |

| M154           | 155-0154-00                      |

| M155B          | 203-0155-91                      |

| M156           | 155-0288-00                      |

| M159           | 155-0151-00                      |

| M160A          | 155-0023-00                      |

| M161A          | 155-0024-00                      |

| M162A          | 155-0025-00                      |

| M163A          | 155-0026-00                      |

| M164A          | 155-0027-00                      |

| M165           | 155-0086-00                      |

| M166           | 155-0087-00                      |

| M167           | 155-0088-00                      |

| M169           | 155-0104-00                      |

| M170           | 155-0105-00                      |

| M171           | 155-0135-00                      |

| M175B          | 203-0175-90                      |

| M177A          | 203-0177-90                      |

| M178A          | 203-0178-90, 91, 92              |

| M180D          | 155-0157-00                      |

| M181D          | 155-0158-00                      |

| M187A          | 155-0185-00                      |

| M188A          | 155-0196-00                      |

| M192C          | 155-0188-00                      |

| M196A          | 203-0196-90                      |

| M197A          | 203-0197-90                      |

| M198A          | 203-0198-90                      |

| M199A          | 203-0199-90                      |

| D206A          | 203-0206-90                      |

| M207           | 155-0187-00                      |

| M208           | 155-0205-00                      |

| M210C          | 203-0210-90                      |

| M211C          | 203-0211-90                      |

| M212C          | 203-0212-90                      |

| M213C          | 203-0213-90                      |

| M214C<br>M215E | 203-0214-90<br>155-0241-01       |

|                |                                  |

| M216C          | 203-0216-90                      |

| M217G          | 155-0244-00                      |

| M218A          | 155-0215-00                      |

**NEW DESIGN CODE**

$\begin{array}{l} \mathsf{P} = \mathsf{Preferred} \\ \mathsf{X} = \mathsf{Suitable} \\ \mathsf{X} = \mathsf{Do} \ \mathsf{Not} \ \mathsf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

#### M Number vs. Package Part Number (cont)

|       | Packaged Part No./Die No. (cont) |

|-------|----------------------------------|

| M222B | 155-0218-00                      |

| M223B | 155-0247-00                      |

| M227C | 203-0227-90                      |

| M228B | 155-0279-00, 155-0283-00         |

| M229C | 203-0229-90                      |

| M231B | 203-0231-90                      |

| M232B | 155-0277-00                      |

| M234B | 155-0253-00                      |

| M240  | 203-0240-90                      |

| M241B | 155-0280-00                      |

| M274B | 203-0274-90                      |

| M289A | 155-0273-00                      |

| M297A | 203-0297-90                      |

| M307B | 203-0307-90                      |

| M312A | 155-0282-00                      |

NEW DESIGN CODE

$\begin{array}{l} \mathsf{P} \ = \ \mathsf{Preferred} \\ \mathsf{X} \ = \ \mathsf{Suitable} \\ \mathsf{X} \ = \ \mathsf{Do} \ \mathsf{Not} \ \mathsf{Use} \end{array}$

C = Call Application Engineering before using

155-XXXX = Packaged Parts 203-XXXX = Die

# NEW DESIGN INFORMATION

| SECTION 2 | NEW DESIGN INFORMATION                     | Page<br>No. |

|-----------|--------------------------------------------|-------------|

|           | Preferred for New Designs                  | 2-1         |

|           | Suitable for New Designs                   |             |

|           | Do Not Use for New Designs                 |             |

|           | Call Applications Engineering Before Using |             |

|                  |                                               | Page  |

|------------------|-----------------------------------------------|-------|

| Preferred for Ne | ew Designs—Cost Effective or State-of-the-Art | No.   |

| Packaged Parts   | i                                             |       |

| 155-0012-00      | Z axis signal conditioner                     | 5-1   |

| 155-0022-00      | 2 input channel switch Ins Rt                 | 5-7   |

| 155-0035-00      | Quad Op Amps, 80 MHz gain bandwidth           | 5-11  |

| 155-0038-02      | 5-bit precision D/A                           | 5-17  |

| 155-0048-01      | 5 MHz trigger and 1 V/µs sweep                | 5-21  |

| 155-0049-02      | Sweep control                                 | 5-27  |

| 155-0055-00      | 5 MHz trigger and 1 V/µs sweep                |       |

| 155-0057-00      | Dual Op Amp, current source                   |       |

| 155-0067-02      | DC to DC controller                           | 5-47  |

| 155-0078-10      | Differential/variable/invert amplifier        |       |

| 155-0109-01      | 350 MHz trigger                               | 5-61  |

| 155-0116-00      | Quad Op Amps, 80 MHz gain bandwidth           |       |

| 155-0122-00      | Sweep control                                 |       |

| 155-0123-00      | 50 ns sweep and delay pickoff                 |       |

| 155-0124-00      | 5 ns/div horizontal preamplifier              | 5-87  |

| 155-0126-00      | Trigger Amplifier/Source Select               |       |

| 155-0144-00      | TV sync stripper                              | 5-93  |

| 155-0145-00      | Controlled risetime amplifier                 |       |

| 155-0152-01      | Magnetic deflected CRT geometry correction    |       |

| 155-0154-00      | 3-input multiplexer                           |       |

| 155-0188-00      | TV sync generator                             | 5-117 |

| 155-0196-00      | 100 MHz trigger                               |       |

| 155-0215-00      | Logic analyzer input                          |       |

| 155-0217-00      | Amplifier                                     | 5-137 |

| 155-0218-00      | 100 MHz vertical output                       |       |

| 155-0244-00      | Scope logic interface                         |       |

| 155-0247-00      | Tape controller                               |       |

| 155-0253-00      | Schmitt trigger                               |       |

| 155-0273-00      | Differential/variable/invert amplifier        |       |

| 155-0274-00      | Differential/variable/invert amplifier        |       |

| 155-0283-00      | Video multiplier                              |       |

| 206-0248-00      | Platinum temperature probe tip                | 5-193 |

| Die              |                                               |       |

| 203-0084-90      | Differential/variable/invert amplifier        | 6-1   |

| 203-0089-91      | Vertical output amplifier                     |       |

| 203-0155-91      | 4-bit 80 MHz clock flash A/D converter        |       |

| 203-0177-90      | 5-bit DAC                                     |       |

| 203-0211-90      | Channel switch                                |       |

| 203-0212-90      | Vertical output                               |       |

| 203-0213-90      | 600 MHz trigger                               |       |

| 203-0214-90      | Sweep DAC & logic                             |       |

| 203-0216-90      | Z-axis, autofocus amplifier                   |       |

| 203-0227-90      | Z-axis driver                                 |       |

| 000 0000 00      | 200 Mile trigger emplifier                    | 6 72  |

2

anot included in this catalog.

203-0229-90 203-0231-90

. . .

:

And and the set of and the set of a set of the set

2-1

#### Suitable for New Designs-Older Still Useful Parts

#### **Packaged Parts**

| 203-0080-90 | Vertical Output Amplifier |

|-------------|---------------------------|

| 203-0126-90 | F <sub>t</sub> Doubler    |

Do Not Use for New Designs—Obsolete Designs, Replaced by Newer Designs, or No Longer a Process in Production

#### **Packaged Parts**

, ,

;

.

.

•

| 101 1000 00                | Dragonary and Osmanatan                |

|----------------------------|----------------------------------------|

| 131-1393-00<br>131-1394-00 | Programmed Connector                   |

|                            | Programmed Connector                   |

| 131-1395-00                | Programmed Connector                   |

| 131-1396-00                | Programmed Connector                   |

| 131-1659-00                | Programmed Connector                   |

| 131-1660-00                | Programmed Connector                   |

| 152-0314-00                | Schottky Diode                         |

| 152-0442-00                | Schottky Diode                         |

| 152-0442-01                | Schottky Diode Pair                    |

| 152-0446-00                | Schottky Diode Pair                    |

| 152-0446-01                | Schottky Diode Single                  |

| 155-0004-01                | 576 Readout System                     |

| 155-0005-00                | 576 Readout System                     |

| 155-0006-01                | 576 Readout System                     |

| 155-0007-01                | 576 Readout System                     |

| 155-0008-01                | 576 Readout System                     |

| 155-0031-01                | Quad Timing Unit                       |

| 155-0087-01                | Quad Timing Unit                       |

| 155-0088-00                | Legend Character                       |

| 155-0104-00                | Legend Character                       |

| 155-0105-00                | Legend Character                       |

| 155-0106-00                | Normalizing Circuit                    |

| 155-0111-01                | LED Array                              |

| 155-0112-01                | Photo Transistor Array                 |

| 155-0119-00                | 5-Digit BCD Counter                    |

| 155-0121-00                | 50 MHz Trigger                         |

| 155-0135-00                | Legend Character                       |

| 155-0151-00                | 100 MHz Trigger                        |

| *155-0157-00               | MOS Digital Storage Vertical Control   |

| *155-0158-00               | MOS Digital Storage Horizontal Control |

| *155-0198-00               | MOS Knob Readout Counter               |

| *155-0199-00               | MOS Vertical Control                   |

| 155-0205-00                | F <sub>t</sub> Doubler                 |

| *155-0207-00               | Vertical Output                        |

| 206-0186-06                | Transistor Temperature Probe           |

| 206-0286-11                | Transistor Temperature Probe           |

|                            | 1 2 2 2 2 2 2 2                        |

#### Die

| 203-0096-90 | Logic Probe     |

|-------------|-----------------|

| 203-0268-90 | PNP Transistor  |

| 203-0276-90 | 50 Ohm Resistor |

| 203-0290-90 | Schottky Diode  |

\*Limited supply-process capability does not exist.

#### Call Application Engineering Before Using

#### Packaged Parts

| 151-0659-00 | NPN Power Transistor     |

|-------------|--------------------------|

| 151-1139-00 | Dual FET                 |

| 152-0646-00 | Schottky Diode Pair      |

| 152-0646-02 | Schottky Diode Pair      |

| 155-0017-00 | Decade Counter           |

| 155-0018-00 | Zero Logic               |

| 155-0028-00 | Miller Integrator        |

| 155-0028-01 | Miller Integrator        |

| 155-0056-00 | Sweep Control            |

| 155-0076-00 | Input Protection         |

| 155-0160-00 | Trigger Source/Amplifier |

| 155-0241-00 | Horizontal Amplifier     |

| Die         |                          |

| 203-0032-90 | Schottky Diode                     |

|-------------|------------------------------------|

| 203-0075-90 | NPN Transistor                     |

| 203-0088-90 | Vertical Amplifier                 |

| 203-0122-90 | 1 GHz Trigger                      |

| 203-0130-90 | 100 MHz Vertical Preamp            |

| 203-0175-90 | Dual Comparator                    |

| 203-0178-90 | 1 GHz Vertical Amplifier           |

| 203-0196-90 | Horizontal Clamp                   |

| 203-0197-90 | Horizontal Output                  |

| 203-0198-90 | Clamp & Sensor                     |

| 203-0199-90 | 1 GHz Input Amplifier              |

| 203-0206-90 | NPN Transistor                     |

| 203-0210-90 | 300 1MHz Vertical Preamp           |

| 203-0264-90 | Schottky Diode                     |

| 203-0269-90 | EBS Target Diodes                  |

| 203-0270-90 | NPN 3 Watt 2 GHz Transistor        |

| 203-0271-90 | NPN 5 Watt 150 V .5 GHz Transistor |

| 203-0265-90 | Schottky Diode                     |

| 203-0266-90 | Schottky Diode                     |

|             |                                    |

### Q.A. PROGRAM

### ICM QUALITY

#### QUALITY POLICY

Integrated Circuits Manufacturing exists to provide quality products and services to our customers on time at reasonable cost. Quality is meeting all the requirements of the "specification". The standard of performance is complete conformance to the requirements for guaranteed customer satisfaction. Any change in requirements must be officially documented and reflect what we and our customers really need.

Our intent is that quality be built into each product during the design, development, and manufacturing stages of product life. Defect prevention, rather than "inspecting" quality in, is to be emphasized at all times at all organizational levels. Each individual is responsible for the quality of his/her work, and each manager is responsible for the quality of work performed under his/her direction. Correction of major plant and field problems will be given prompt attention and timely resolution.

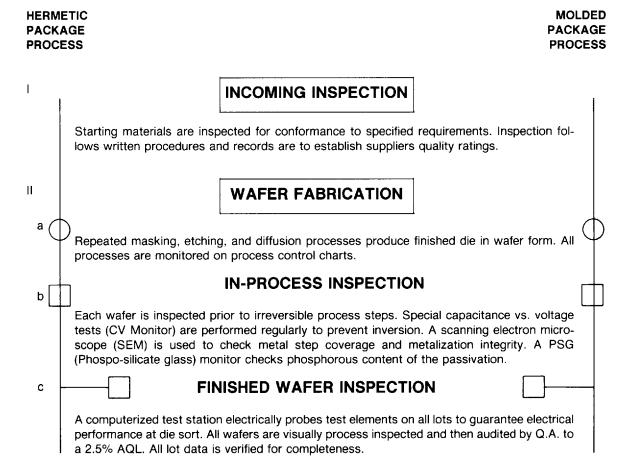

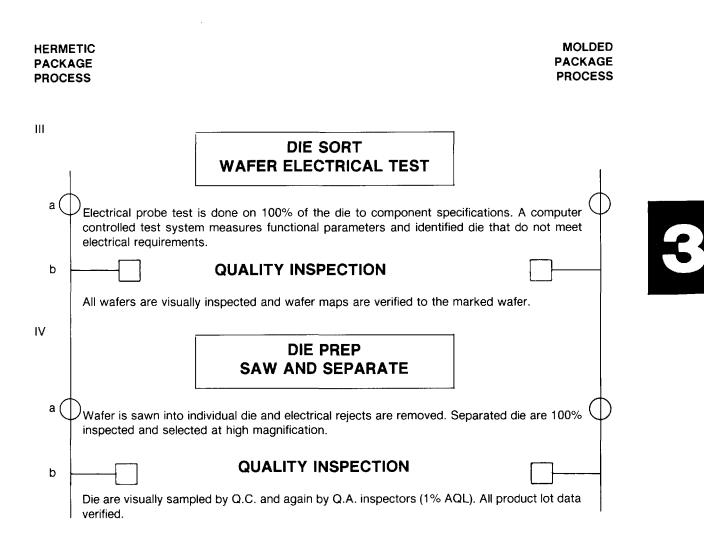

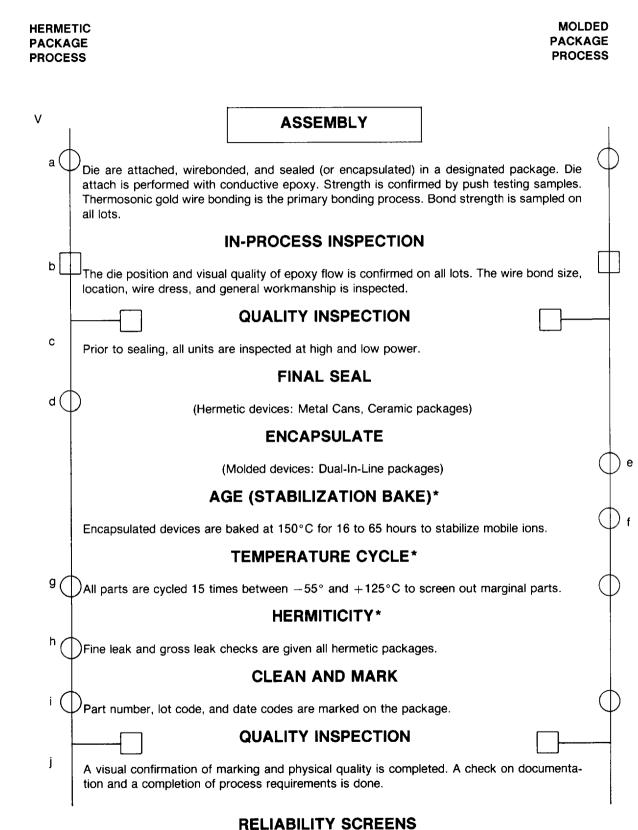

#### MANUFACTURING, SCREENING AND INSPECTION for INTEGRATED CIRCUITS

The following flow chart describes the major process steps and the key quality check points for producing hermetic and molded package I.C.'s. All operations are totally specified in product, process, test, and quality assurance specifications.

\* Reliability Screens

3-5

HERMETIC PACKAGE PROCESS MOLDED PACKAGE PROCESS

٧I

а

b

c(

FINAL TEST

100% of parts tested to requirements of component specifications: Includes static, dynamic, and functional tests specified temperatures.

#### QUALITY INSPECTION

Visual confirmation of marking and physical quality. Electrical confirmation of product identity by sample test to a 0.65% AQL. Confirmation of completion of all process steps and required documentation.

#### SHIP TO WAREHOUSE

Specialized reliability assurance screen tests, such as burn-in, can be developed for a specific application to insure a product's reliability. Initial discussions should be coordinated with an Applications Engineer. Quality and Reliability Engineers are also ready to support you and your application.

### RELIABILITY

#### RELIABILITY

The reliability of a circuit component is the probability of failure-free performance of a required function under stated conditions for a given period of time. It is possible to calculate the probability of successful operation to a specified confidence interval.

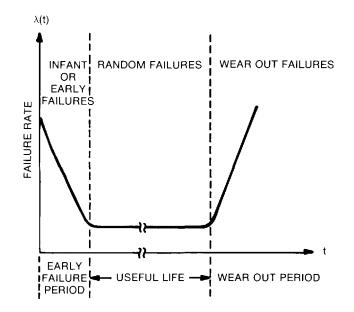

The typical failure rate behavior of a device is shown in the figure below:

4

**INFANT MORTALITY:** Early in the lifetime of a device there can be a relatively large number of failures, due to built-in weakness or defect. These early failures show a decreasing failure rate with respect to a relatively short time period.

**USEFUL LIFE:** During the middle period of the device lifetime fewer failures occur but it is necessary to know which failure mechanism is the principal determinant of the failure rate under the conditions of interest. In this region, sometimes called the "random failure region" of constant failure rate, the device characteristics are essentially constant and when failure occurs it is usually catastrophic.

**WEAR-OUT REGION:** As a device reaches the age at which wear-out failure mechanisms are activated it begins to deteriorate rapidly. The instantaneous failure rate increases monotonically and many failures occur. This failure region is called the "wear-out region" and is caused by material degradation, effect of electrical fields, and slow chemical reactions. Integrated circuits do not usually reach the wear-out region in normal operation. Exceptions occur when integrated circuits are exposed to ionizing radiation fields and when the hermeticity of integrated circuit packages is impaired by progressive corrosion. An "intrinsic" wear-out process leads to the ultimate failure of every device.

#### INTEGRATED CIRCUIT FAILURE MECHANISMS

The physical or chemical process that causes devices to fail is termed the *failure mechanism*. The cause of rejection of any failed device is termed the *failure mode*. Thus, electromigration is an example of a failure mechanism, which can lead to the failure mode of an open interconnection. A further example is given by excess charge near a silicon-oxide interface (failure mechanism) which causes drift of the parameters of a MOS transistor (failure mode).

Failure mechanisms for bipolar integrated circuits can be divided roughly into three groups, namely: (1) dierelated failures, such as oxide defects, metallization defects, and diffusion-related failures; (2) assemblyrelated problems such as die mount, wire bonds, or package failures; and (3) miscellaneous undetermined, or application-induced failures.

**DIFFUSION-RELATED FAILURES:** Nonuniform current-flow may occur within a device because of dopant diffusion-related causes. These may affect the base width, the emitter resistivity, the curvature of junctions, and other device parameters.

4

**OXIDE-RELATED FAILURES:** Contamination of oxide, during or after its growth, directly affects its dielectric properties, particularly its breakdown strength. Presence of surface charge,  $Q_{SS}$ , at or near an oxide-silicon interface can affect the turn-on voltage,  $V_{TH}$ , of a device and other parameters, such as dc gain, and leakage current. Oxide-charge values of large magnitude can cause surface inversion. Other surface-related failures arise because of ion migration in the thermally grown oxide and along its surface, dipole polarization effects or charge trapping effects.

**METALLIZATION-RELATED FAILURES:** The mass transport of metal atoms by momentum exchange with conducting electrons is called "electromigration". It occurs in metal lines at high current densities and elevated temperatures, and consists of the movement of metal atoms toward the positive end of the conductor, while voids move in the opposite direction. As a consequence, metal disappears from certain regions and ultimately an open-circuit occurs. The degradation of integrated circuits with aluminum metallization operating at high current densities and at elevated temperatures is described by the Arrhenius model. Electromigration occurs for many metals, including aluminum, gold, silver, copper, and platinum. The current density at which reliability problems occur with gold films is substantially higher than that for aluminum films. This has led to the use of gold in circuits requiring high current densities.

Another significant cause of metallization failure is the formation of microcracks, where the metallization passes over an oxide step. It occurs frequently where the oxide step is greater than 6000 Angstrom. Steeper steps lead to thinner metal deposits which have a greater probability of failure under high current stress. Microcracks are not usually detectable with optical microscopes, but may effectively be detected by scanning electron microscopes.

Metallization may also fail because of poor ohmic contacts with silicon, poor bondability to aluminum or gold wires, or poor adhesion to the silicon dioxide.

**DIE MOUNT FAILURES:** Die to leadframe attachment failures have been attributed to low strength adhesion caused by inadequate process control. Epoxy mounts may fail under temperature stress because the thermal coefficient of expansion of most epoxies exceeds the coefficients of expansion of both the semiconductor die and the leadframe to which it is mounted.

**WIRE BOND FAILURES:** Gold wire is bonded to the die metallization. Failure of gold wire bonds to aluminum-metallized die may be due to the formation of intermetallic compounds that lead to loss of strength and an increase of resistance.