# SAMPLING OSCILLOSCOPE CIRCUITS

BY John Mulvey

Significant Contributions by Al Zimmerman Joe Weber John Bookout

# **CIRCUIT CONCEPTS**

FIRST EDITION, FIRST PRINTING, MARCH 1970 062-1172-00 PRICE \$1.00

> © TEKTRONIX, INC.: 1970 BEAVERTON, OREGON 97005 ALL RIGHTS RESERVED

⊗

### CONTENTS

#### PREFACE

| 1 | INTRODUCTION TO SAMPLING PRINCIPLES 2                                 |

|---|-----------------------------------------------------------------------|

| 2 | BASIC CIRCUIT FUNCTIONS AND RELATIONSHIPS 5                           |

| 3 | SAMPLING, AMPLIFYING AND HOLDING CIRCUITS 55                          |

| 4 | RAMP TRIGGERING AND RAMP DELAY CIRCUITS 115                           |

| 5 | SEQUENTIAL MODE TIMING AND<br>STROBE DELAY CIRCUITS 157               |

| 6 | RANDOM MODE CIRCUITS 203                                              |

| 7 | DEFINITION OF TERMS 227                                               |

|   | SUBJECT INDEX 237                                                     |

|   | INSTRUMENT DIAGRAM INDEX 238                                          |

|   | INDEX TO 3T2 RANDOM MODE<br>CIRCUIT DESCRIPTIONS 239                  |

|   | INDEX TO SAMPLING, AMPLIFYING AND<br>HOLDING CIRCUIT DESCRIPTIONS 240 |

|   | INDEX TO TRIGGERING AND TIME BASE<br>CIRCUIT DESCRIPTIONS 242         |

|   | SAMPLING SCOPE VERTICAL CHANNEL<br>CALIBRATION 244                    |

|   | SAMPLING SCOPE TRIGGER AND<br>TIME BASE CALIBRATION 246               |

### PREFACE

This information is primarily for people who want to understand how sampling oscilloscopes work. It is particularly slanted toward instrumentation engineers, oscilloscope calibration men and owners and users who want best performance from their instruments.

Only key circuits and concepts unique to Tektronix sampling oscilloscopes are covered. Circuits common to sampling and conventional scopes are discussed in other books in this series. A list of those books will be found facing the inside back cover.

Probably the most imaginative sampling-circuit concepts are the ones that pertain to the manner in which the more basic circuits are related to each other. Understanding these broader *relatedness* concepts is normally tougher than perceiving ingenious circuit details. The best way we know to explain the relatedness concepts is by use of block diagrams and waveform time-relationship diagrams. Basic circuit functions are categorized, named and grouped into blocks showing their relationships. No one is expected to deduce the concepts from the diagrams alone. Each function is explained in detail in Chapter 2.

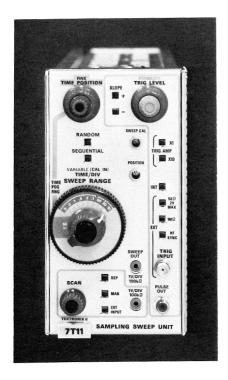

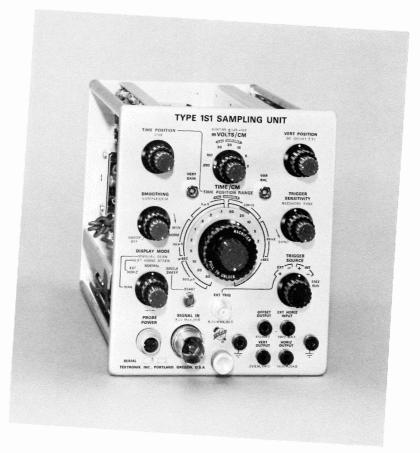

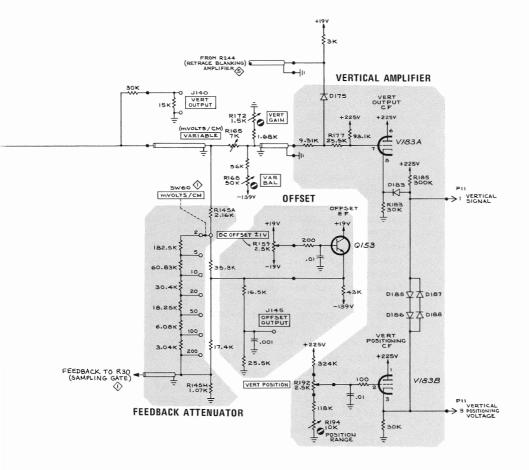

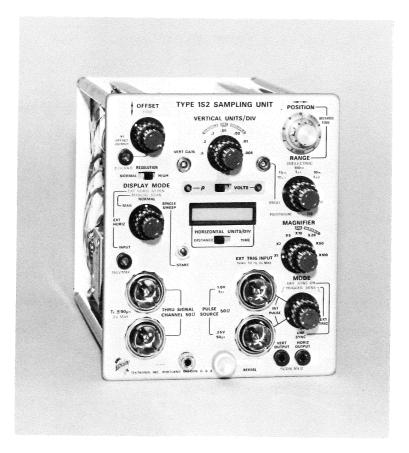

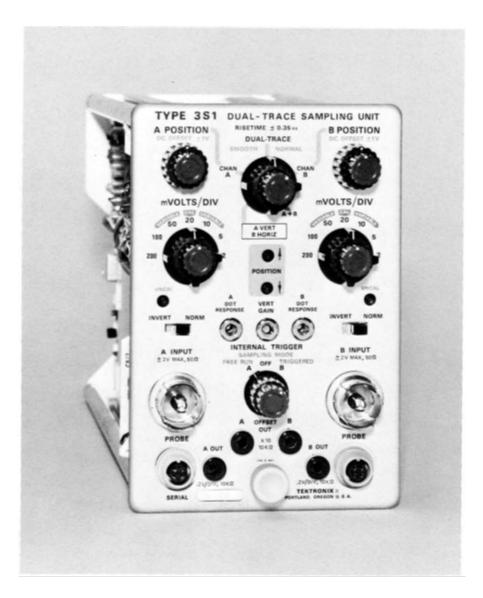

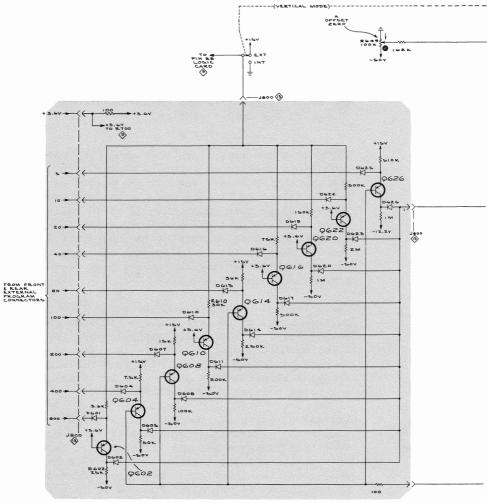

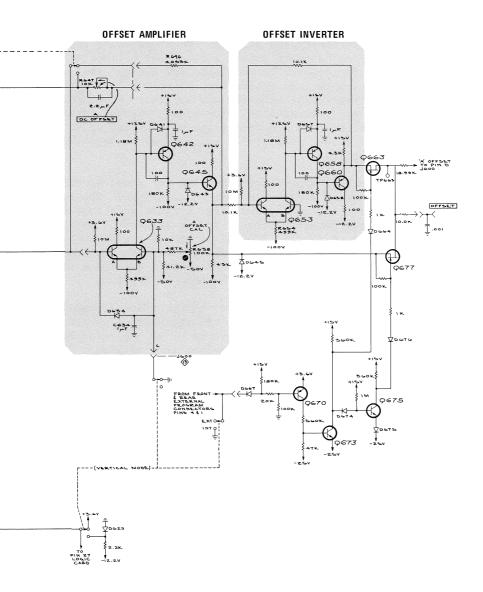

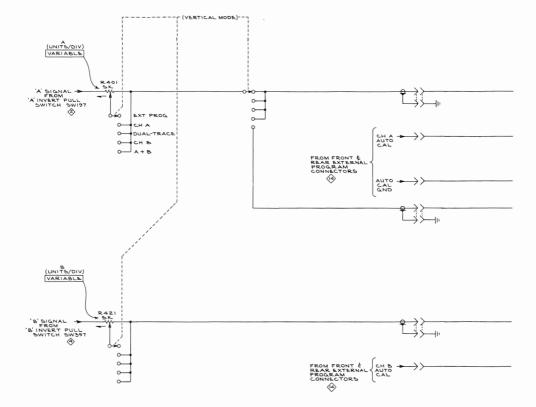

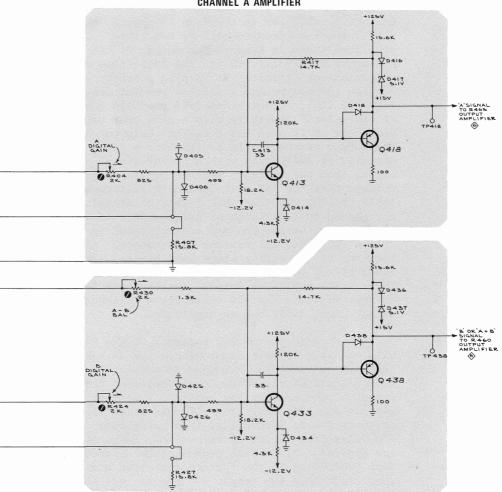

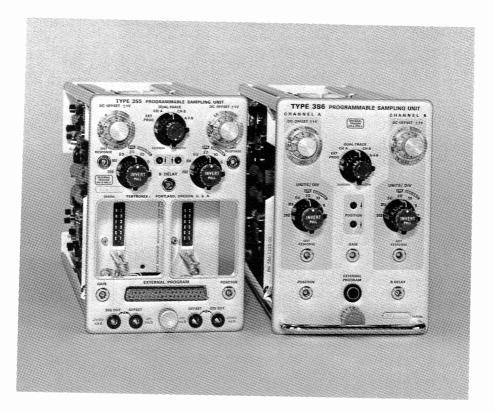

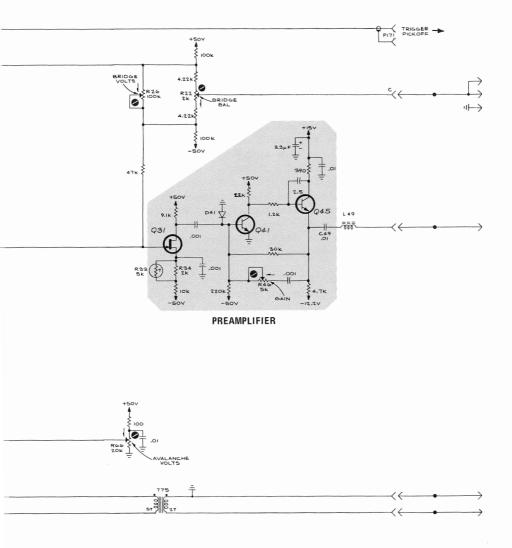

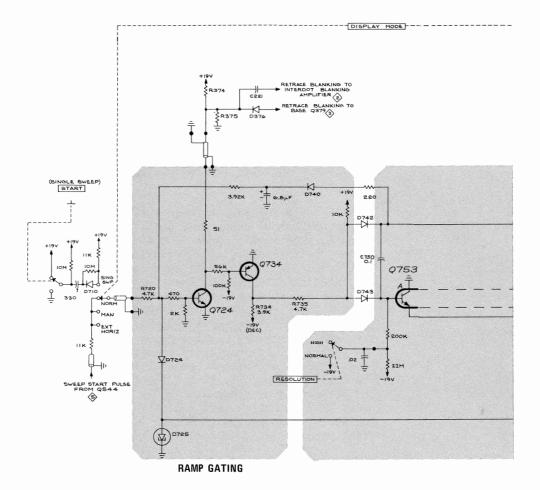

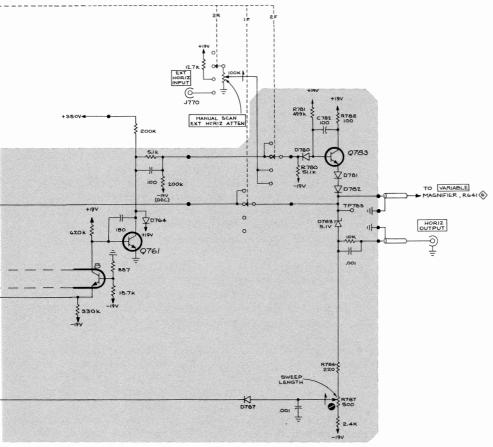

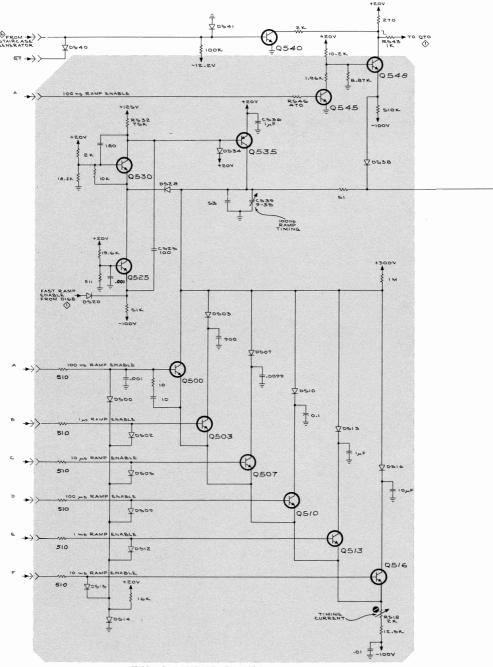

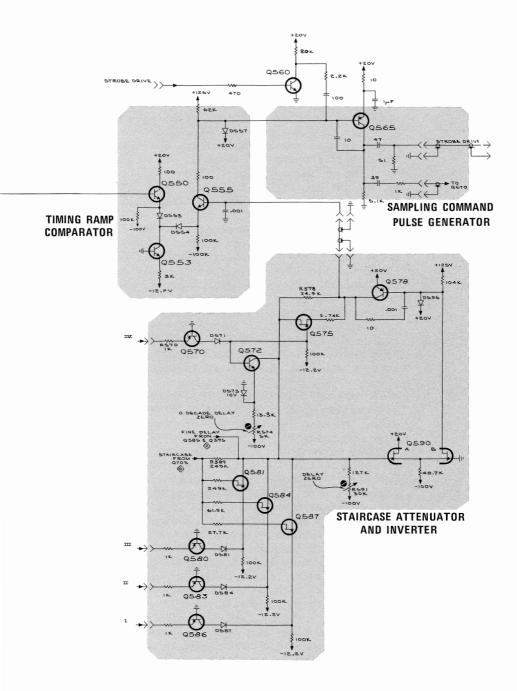

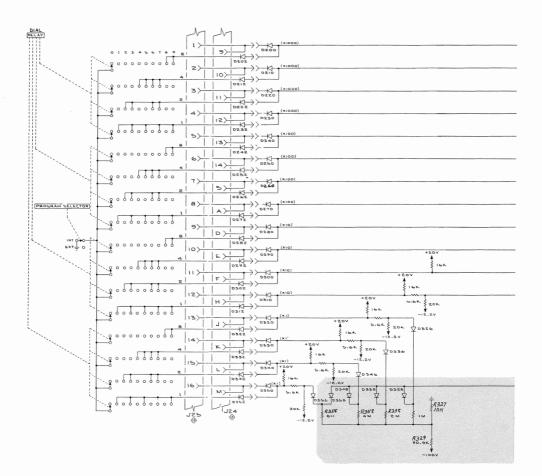

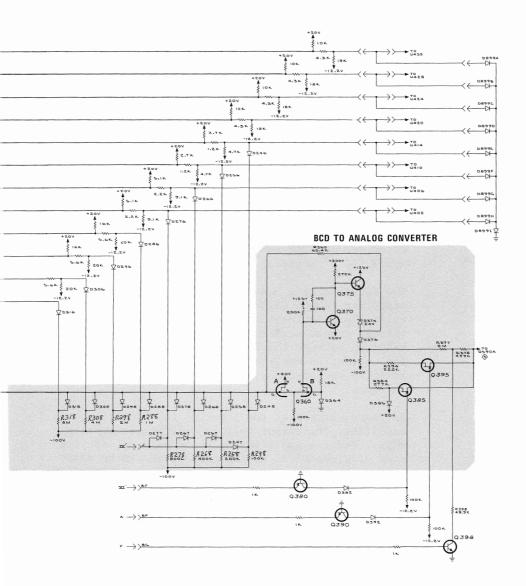

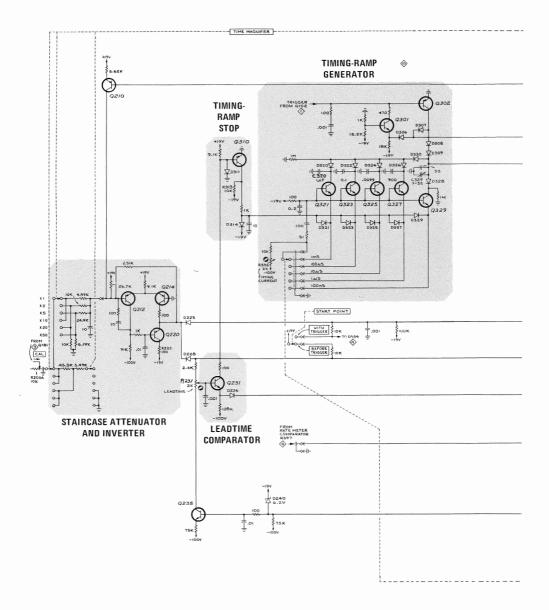

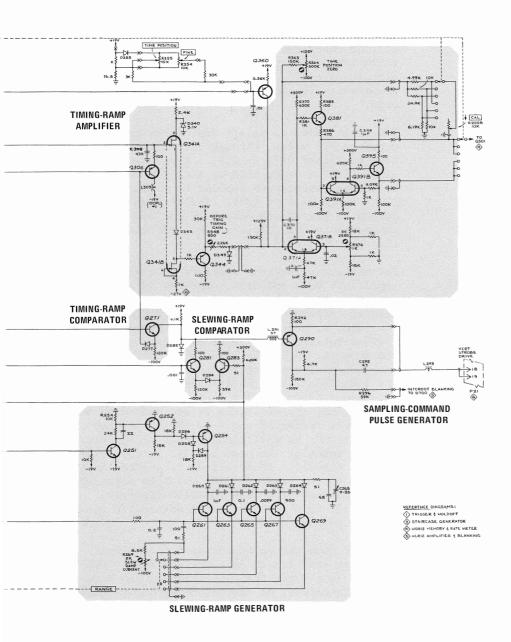

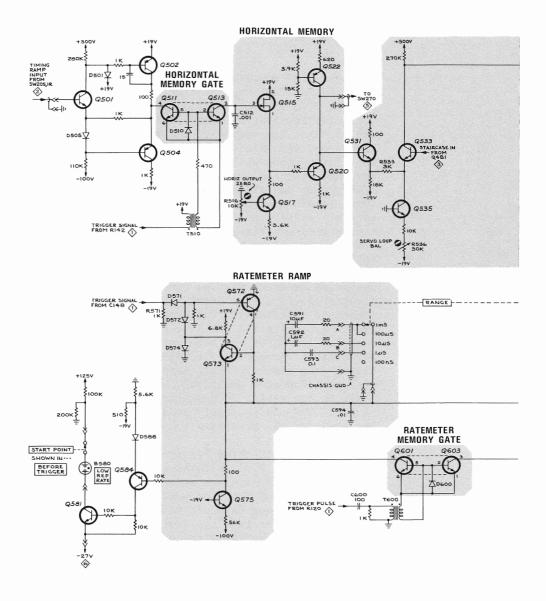

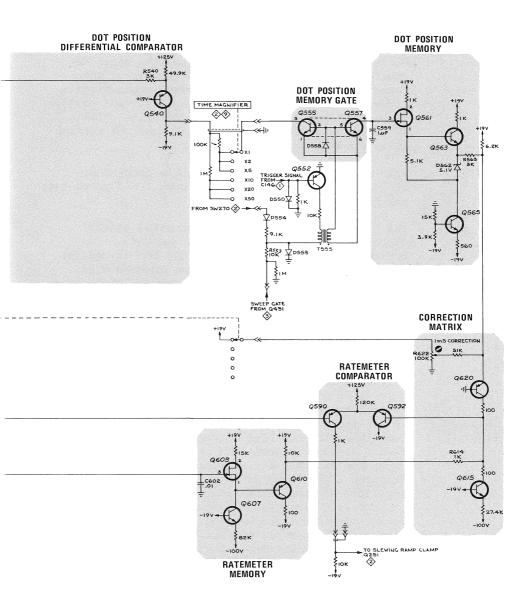

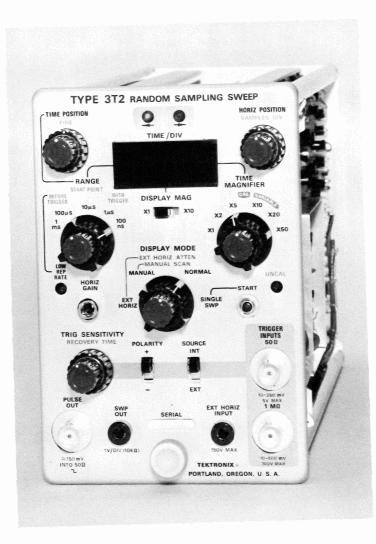

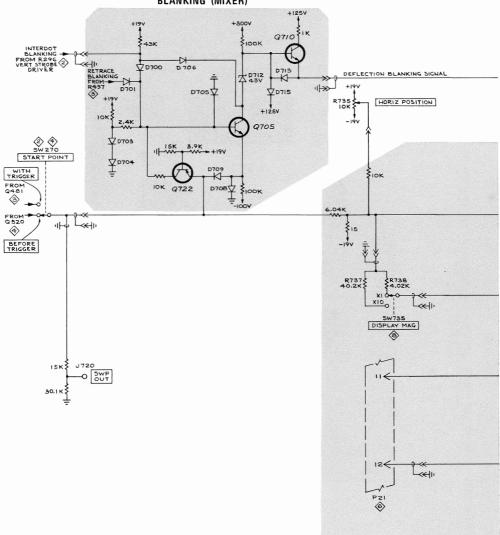

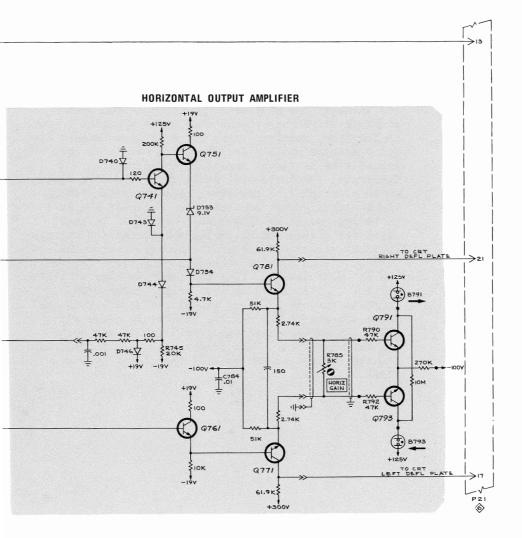

All the *circuits* discussed in Chapters 3, 4, 5 and 6 are good examples of the basic circuit functions described in Chapter 2. The circuit diagrams in this book are reproduced from actual diagrams that appear in the instruction manuals for various Tektronix sampling instruments in production in mid 1969. Thev do not include the 7S11 Sampler or 7T11 Sampling Time Base Unit announced in August 1969. Because the reproductions are greatly reduced in size, some details such as connector pin numbers and circuit symbol numbers are deleted for sake of clarity and simplicity. Sections of the diagrams have been shaded to correspond to the blocks in the block diagrams. We hope this helps you relate the details of how a circuit operates to its purpose for being there.

We have not extracted any section of a circuit diagram to place it closer to the text that describes that section even though we know it would make the job of switching your eyes between text and diagram easier. If you remember that the text always pertains to the closest diagram on an earlier page, relating the two will be simpler.

The diagrams were selected so that all of what might be called key sampling circuits (in mid 1969) could be described here. For sake of completeness, however, the circuits on each diagram that are not what might be called key circuits are also described. A list of circuits similar to the ones described appears as part of the index.

## INTRODUCTION TO SAMPLING PRINCIPLES

9

1

Sampling scopes have been commercially available since about 1959. Their primary advantage is their ability to respond to small fast-changing signal voltages better than conventional scopes.

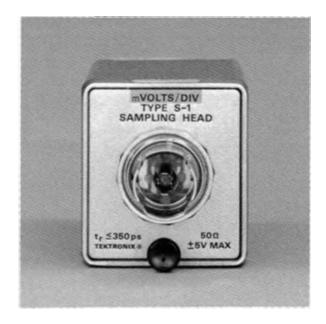

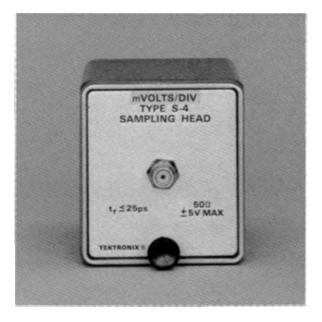

The most fundamental sampling principle is analogous to the principle of optical stroboscopes. A stroboscope generates very brief flashes of light which, when properly timed, can make rapidly moving things appear to be at rest or occurring in slow motion. Sampling scopes graphically depict fastchanging voltages as if the changes were occurring slowly. Instead of generating flashes of light however, sampling scopes generate very brief electrical pulses. These pulses allow us to "look" at a repetitive signal one point and one cycle at a time and depict the signal character graphically but slowly over a period of many cycles. Until recently, the brevity of the pulses determined the shortness of risetime. For example, pulses 350 ps in duration are used in sampling scopes having a risetime of 350 ps. This risetime is comparable to a bandwidth of 1 GHz -- one-billion cycles per second! These pulses are called strobe pulses because of their similarity in function to the flashes of light from a stroboscope.

Although the faster response of sampling scopes is their principle attraction, they have three other features that make them especially useful. First, the process of taking and storing samples of a repetitive signal is such that sampling scopes are almost completely free from display aberrations caused by overscanning the screen. Secondly, large, permanent, paper-chart recordings can be made of a displayed signal directly from X and Y coordinate output signals. And third, the process of sampling lends itself to digitizing time measurements directly, even extremely short intervals of time, and to making digital measurements of the voltage difference between two points on a very fast-changing signal. Sampling scopes were forerunners of digital-readout scopes.

The principle of sampling electrical signals was known before the turn of the century. In 1880 Joubert devised a way of sampling a power-generator waveform with a pen and ink recorder. This was well

useful

strobe

pulses

features

before the days of even simple oscilloscopes. In the 1950's when transistors became available, the work of J. G. McQueen, R. Sugarman, R. Carlson and others paved the way to practical commercial sampling oscilloscopes. Even the very first commercial sampling scopes had much shorter risetimes than any conventional scope which used a vertical-deflection amplifier.

The fundamental reason why sampling scopes can respond to faster-changing signal voltages than usina semiconductor conventional scopes is that with certain devices semiconductor devices we can generate much narrower pulses than we can amplify. With vacuum tubes this was not so.

> Besides generating narrow pulses we must cause them to occur at the right moments. Tektronix presently uses four methods of timing strobe pulses. All four result in a CRT display comprised of a series of dots -- one dot per sample. When the dots occur at a high repetition rate and are closely spaced they may give the appearance of a continuous trace.

Two of the names given to the timing methods are based on the appearance of a trace for that mode. The first and most common mode is called sequential sequential sampling. With sequential sampling the display is comprised of a very orderly series of equally spaced random dots resulting from equally spaced steps of the CRT sampling beam. The second mode is called random sampling. With random sampling successive dots may occur at what appears to be random horizontal positions while plotting the graph.

and

The other two timing methods are used in the mode real-time called real-time sampling. With real-time sampling sampling we do not attempt to depict fast changes in slow In fact, that system is not one of depicting motion. fast changes at all, but rather is a way of extending the use of sampling scopes to look at very slow voltage changes. With real-time sampling, unlike sequential sampling and random sampling, the horizontal time scale of the scope is equal to the actual time the beam takes to traverse horizontally the divisions on the screen.

With sequential sampling and random sampling, the time required to make one complete sweep (scan) of the beam across the screen is vastly longer than the time represented by the full horizontal scale. That tells us the time per division of the scale is much less than the horizontal beam velocity. With either of the modes, the vertical and horizontal (X and Y) coordinate relationships are precisely maintained to produce a coherent, graphic, scope display. How all these good things are made to happen will be the subject for the following pages!

## BASIC CIRCUIT FUNCTIONS AND RELATIONSHIPS

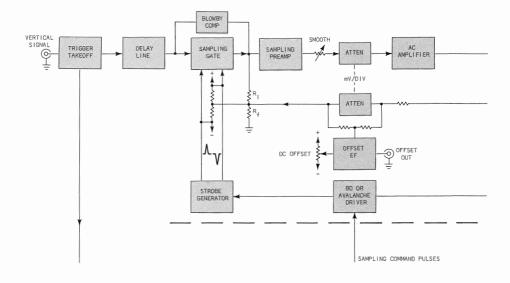

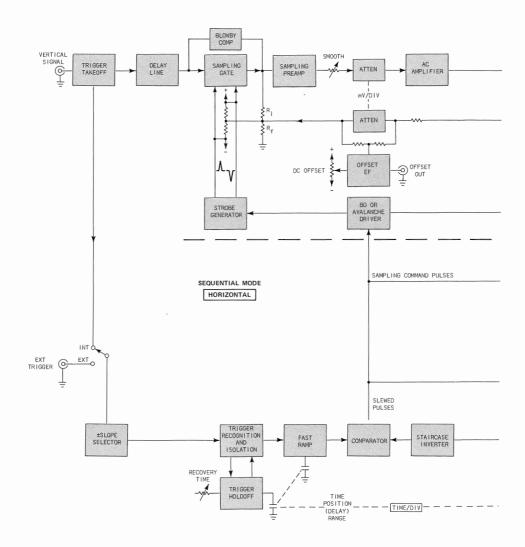

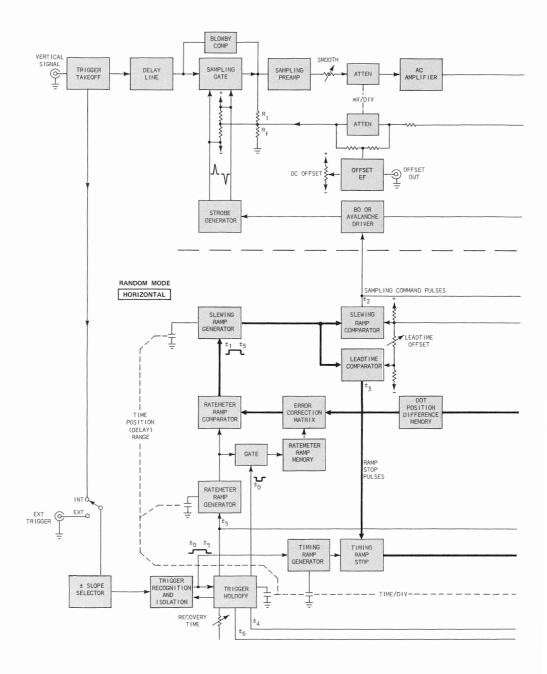

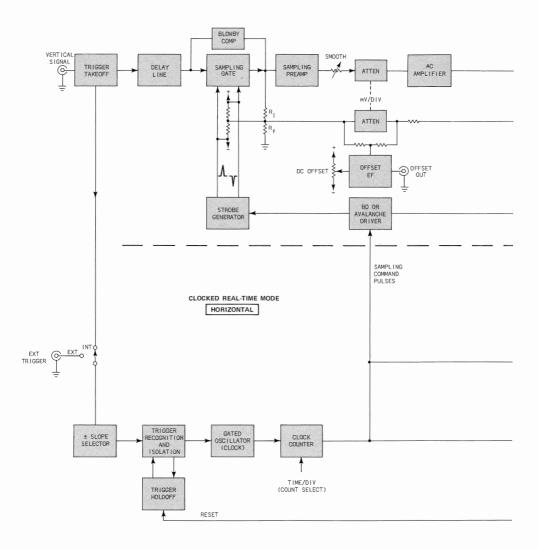

Fig. 2-1. Basic block diagram of vertical deflection section.

#### SAMPLING, AMPLIFYING, HOLDING, FEEDING BACK

The block diagram in Fig. 2-1 represents the function to be discussed.

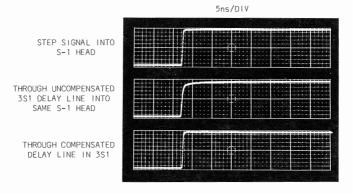

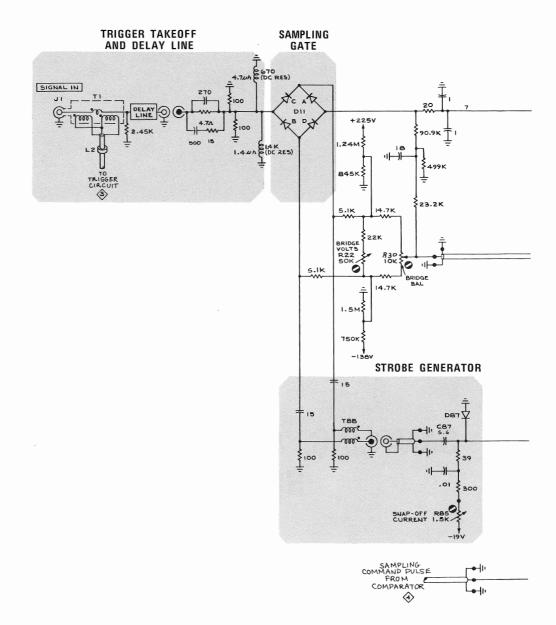

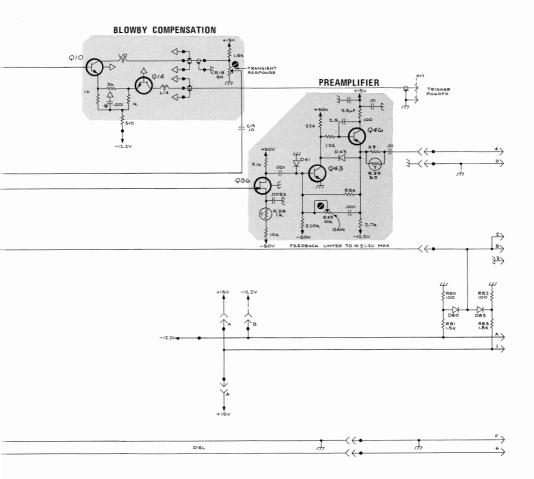

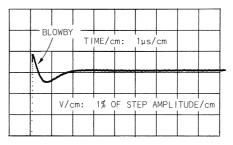

Notice that a delay line is shown between the trigger delay takeoff and the sampling gate. Sampling instruments having a shorter risetime than about 350 picoseconds line do not have delay lines. But delay lines are not always used, even when the risetime is 350 picoseconds or longer. This delay line is a specially constructed, 50-ohm coaxial cable about thirty to fifty feet long having a delay of about 45 to 75 ns. A delay line this long, having dimensions small enough so it can be wound up and placed inside of a sampling scope, will degrade the response to fast-step signals. In particular, the top corner of a rising-step signal (or the bottom corner of a falling-step signal) will be rounded. See Fig. 2-2. When we use such a delay line, therefore, we usually have a passive compensation circuit at the end of the delay line that provides a correction for the degradation of waveshape introduced by the delay line. The end of the delay line is terminated in this network.

sampling The sampling gate is connected at the end of the gate network and at this point blocks further passage of the input signal nearly all the time. The purpose of the sampling gate is to block the signal except during the very brief moments when the signal voltage is allowed to go through the gate and into the sampling preamplifier.

Fig. 2-2. Delay-line dribble-up. 70-ps step signal from Type 284 displayed on 561B (projected graticule).

Typically, Tektronix sampling instruments do not sample any signal more often than 100,000 times a second, regardless of the signal frequency. Trigger countdown is always to 100 kHz or less. Sampling 100,000 times a second, when the sampling gate is opened for only 350 picoseconds for each sample, provides a sampling duty factor of only about one part in 30,000.

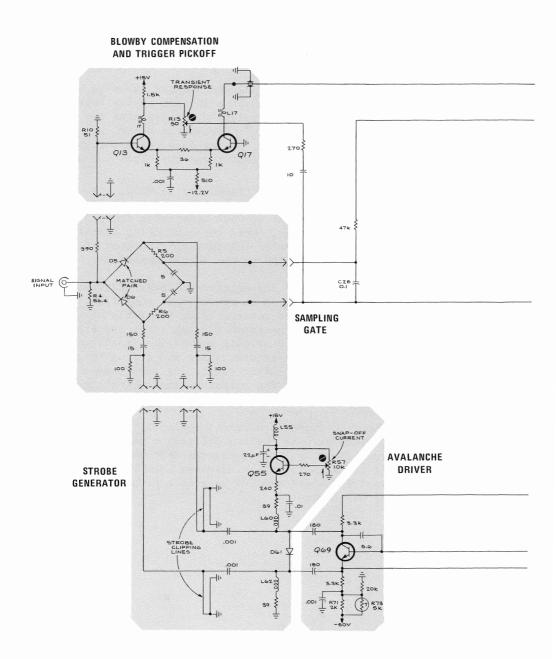

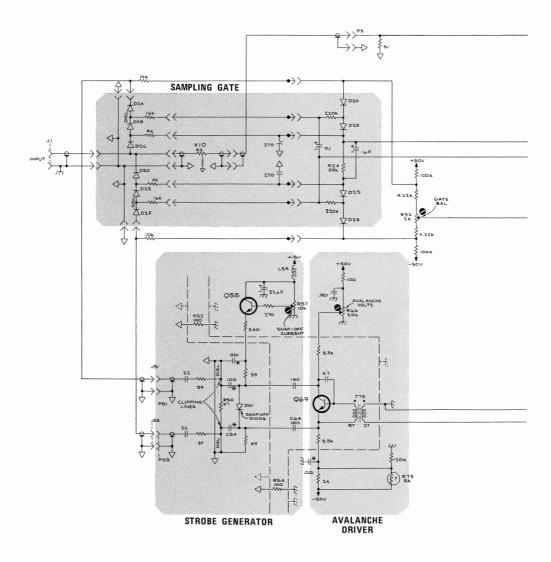

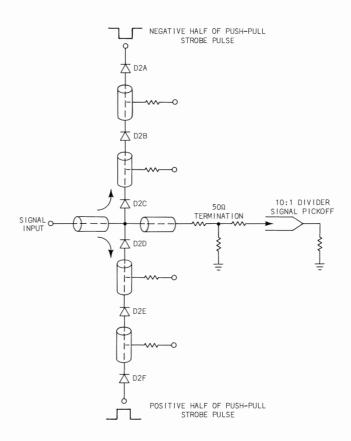

The sampling gate consists of two to six very fast low-storage diodes. These diodes are arranged to have a back-bias voltage applied across them at all times except when we wish the signal energy to pass through. The back-bias voltage is usually derived by tapping a couple of points in a resistive DC-voltage divider. In the block diagram shown, we can see that the two inputs to the bottom part of the sampling gate block have two different voltages applied; one negative and one positive with respect to ground. The center-tap voltage is normally within ±1 volt of ground. The back-bias voltage must be high enough to be greater than the peak amplitude of the signal being applied to the input of the sampling gate, or the signal itself will cause one or more of the diodes to conduct, passing the signal at the wrong moments. The sampling-gate diodes are only supposed to conduct at the moments when we want samples to be taken. The same two lines coming into the sampling gate that bring in the back-bias voltage also bring strobe pulses from the strobe-generator block.

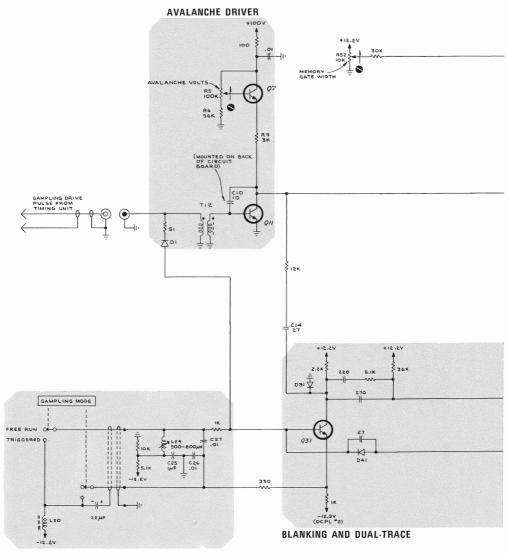

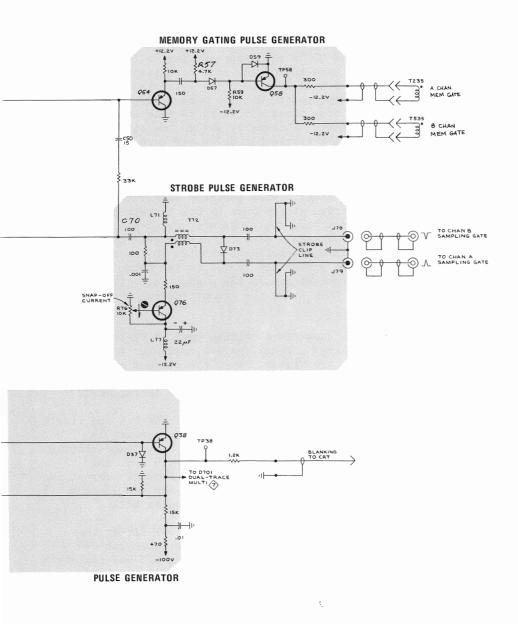

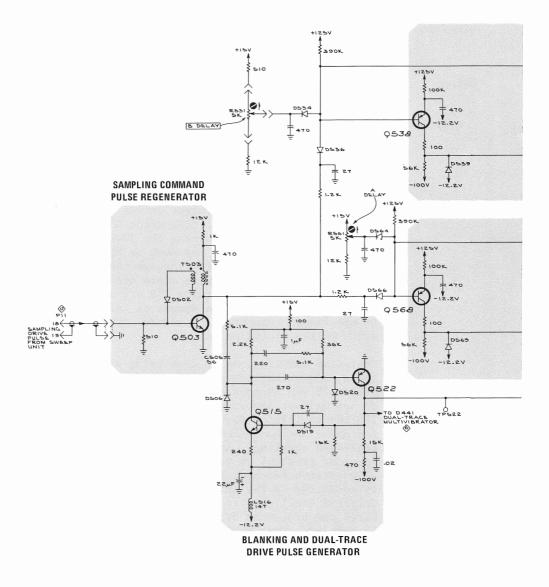

Strobe generators usually employ snap-off diodes (also called step-recovery diodes) to generate very narrow pulses. The pulses are invariably applied push-pull with the right polarity to overcome the back-bias on the sampling-gate diodes. In this block diagram the strobe generator is being driven by either a blocking oscillator or a transistor operated in the fast-switching avalanche mode. In turn this circuit is driven by the sampling-command pulses that originate in the horizontal-deflection section. Everytime a sampling-command pulse is generated, a pair of strobe pulses is delivered to the sampling gate. The strobe pulses admit the signal to the preamplifier but for only a very brief time. That time is normally equal to the duration of the strobe pulses themselves.

back-bias voltage

strobe generator sampling preamplifier Let's consider what happens just before and during the time when the sampling gate allows the signal to come through into the sampling preamplifier. A pair of strobe pulses are generated and applied to the sampling gate, overcoming the back-bias on the sampling-gate diodes and admitting the signal through the sampling gate into the sampling preamplifier. There is invariably a small amount of stray capacitance to ground at the input to the preamplifier, and this capacitance gets partially charged to the voltage which exists on the input side of the sampling gate. The capacitance would get fully charged if the strobe pulses were wider. When the sampling gate stops conducting, a small voltage will have been developed across this capacitance and will last for a relatively long time because it has a high-resistance path through which to discharge. The waveform at the input to the sampling preamplifier is a step signal having a transition time about equal to the risetime of the sampling scope.

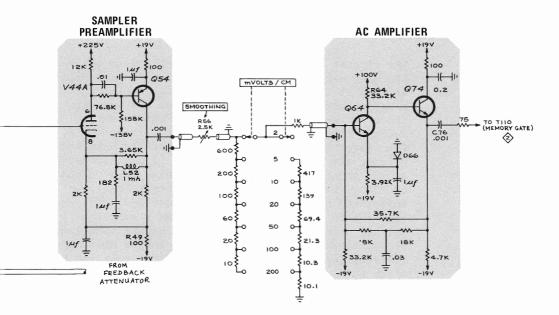

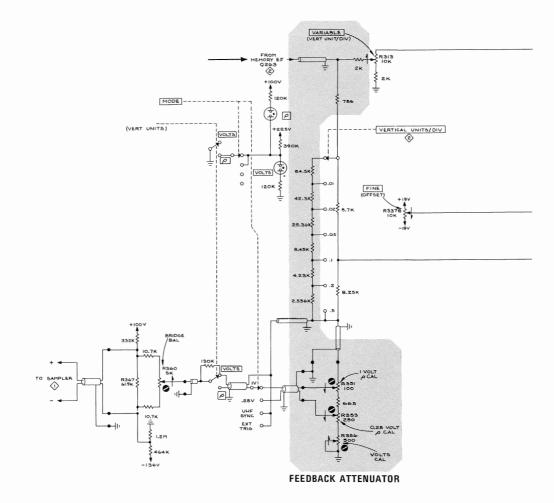

The resistor  $R_1$  shown in the path to ground at the input of the sampling preamplifier has a relatively high resistance compared to the input impedance of the sampling gate. When driven by the input signal, the stray input capacitance can charge or discharge rapidly compared to the time taken for discharge through resistor  $R_1$ . We may see that a voltage step has been applied to the sampling preamplifier which is captured as a charge on the input capacitance. The sampling preamplifier responds to this step as fast as it can and its output is applied through a couple of attenuators, one of which is called a smoothing control, amplified further through a stage usually called an AC-amplifier stage, and then is applied to a gate at the input to the memory.

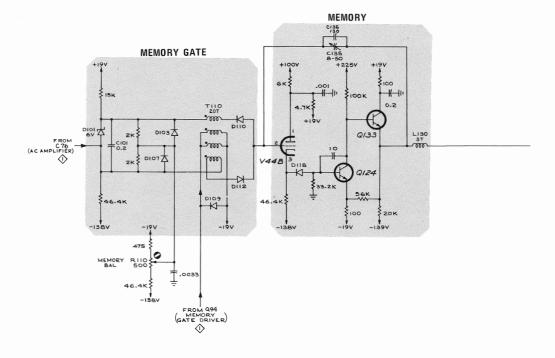

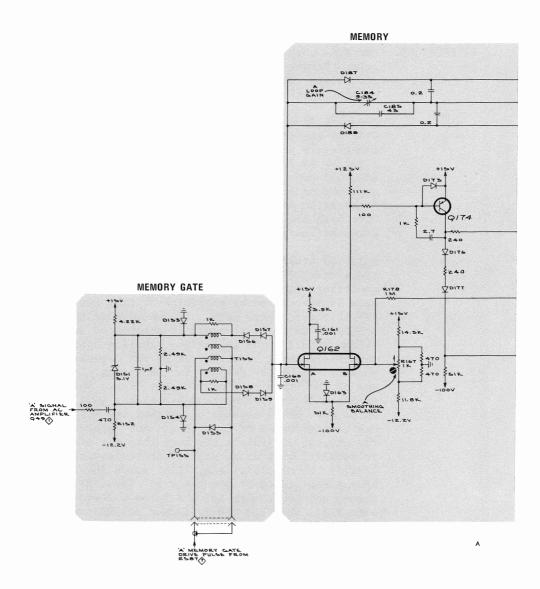

The memory gate is very similar in some respects to gate The sampling gate, but is operated for a much longer period of time. Typically, the memory gate will pass the amplified signal for about one-third *microsecond* each time there is a sampling-command pulse. Compared to a third of a nanosecond or less when the sampling gate is passing the input signal, we have approximately a 1000-to-1 ratio. Notice, however, that the memory gate and the sampling gate are both turned on by the sampling-command pulses that come from the horizontaldeflection section. Not evident in the block diagram is the fact that the memory-gating pulses, although starting simultaneously with the strobe pulses, are not turned off until much later. This tells us that a small step voltage, applied to the input of the sampling preamplifier, can be amplified for a large fraction of a microsecond while being applied through the memory gate to the memory, before the memory gate interrupts the amplified step-signal.

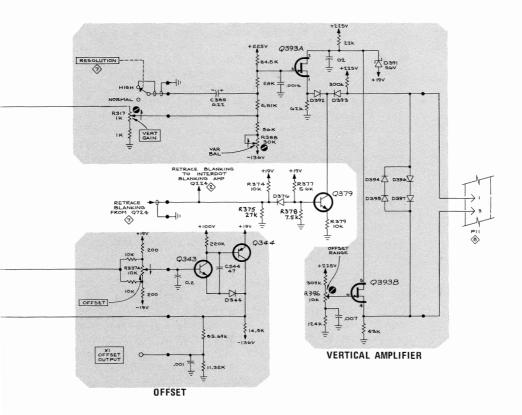

memory The memory is a DC-coupled inverting amplifier with the output fed back to the input through a memory capacitor. Whenever the memory gate is open and not allowing a signal to go through, the gate disconnects the input to the memory capacitor providing only a very high impedance to ground at the input side. That tells us that whatever voltage is stored in the memory capacitor can remain essentially constant until another sample is taken. The output voltage of the memory amplifier goes to the vertical amplifier, producing vertical deflection. Each change in voltage at the output of the memory is a step change, a step proportional in amplitude to a step at the input to the preamplifier.

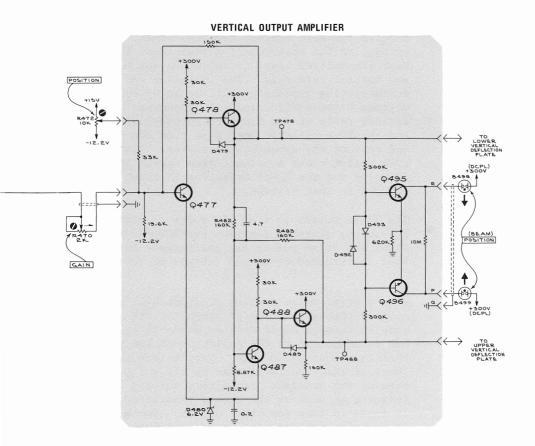

> The amplifier stages which follow the memory output are very similar to the amplifiers in conventional oscilloscopes. There is nothing very unique about these stages.

The output of the memory amplifier also goes back to the sampling-preamplifier input, through an attenuator. The attenuator circuit consists of the feedback attenuator resistor connected directly to the output of the memory, plus a selectable resistor connected to the first resistor, then to the resistor to ground,  $R_{f}$ . The amount of voltage which is developed across resistor  $R_{f}$  is the voltage which is applied to the sampling preamplifier from the memory output. The voltage at the memory output is, therefore, attenuated a certain amount before being reapplied back to the sampling-preamplifier input. The voltage existing across this resistor is partly determined by the DC-offset setting. For the time being we will consider the voltage across this resistor to be determined only by the output of the memory. That is, we will assume the DC-offset voltage is set to zero volts.

Nothing in the block diagram indicates what the polarity or phase of the memory-output voltage may be compared to the signal voltage sampled. It is important to know that a step in one direction at the sampling-preamplifier input invariably produces an amplified step in the same direction at the memory output. From this we can see that the feedback is always in phase with the input step. Nonetheless, the feedback from the memory output to the sampling-preamplifier input is part of a nullseeking servo loop. We call it a sampling loop. With each sample, the memory output repeatedly attempts to reduce the voltage existing between the input and the output of the sampling gate to zero. If the input voltage is the same each time it is sampled, the feedback matches it, reducing the difference and the size of the steps to practically zero.

The sampling loop is comprised of (1) the sampling gate, (2) all the amplifier and attenuator stages up to the output of the memory, and (3) the feedback path from the output of the memory to the input of the preamplifier. The input to the sampling gate is the input to the sampling loop. The percentage of signal voltage transferred across the sampling gate when the gate conducts is referred to as sampling efficiency. Sampling efficiency is primarily a function of strobe width, source impedance and preamplifier input capacitance. It is usually less than 25% for risetimes less than 350 picoseconds. If we have a signal level at the sampling-gate input which, at the moment the signal is first sampled, differs from the level at the output by one volt and we have a sampling efficiency of 25%, a 1/4-volt step will appear at the input to the samplingpreamplifier stage. The risetime of that step? Very nearly the same as the interval the gate was conducting.

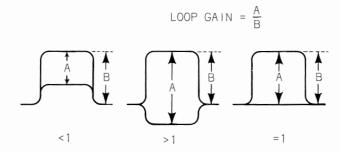

The amplification of the step signal through the sampling preamplifier, the AC amplifier, and the forward memory amplifier, comprises what we call forward gain. How much the signal at the output of a memory is qain attenuated before it is fed back and reapplied to the input of the sampling-preamplifier stage is called feedback feedback attenuation. The product of sampling attenuation efficiency, forward gain and feedback attenuation (with feedback attenuation expressed as gain) is samplingwhat we call sampling-loop gain. Sampling-loop gain loop gain should normally be close to unity (1).

sampling loop

sampling efficiency

12

Let's consider what happens when the right conditions prevail to give us a loop gain of 1. First of all, let us assume that the voltage of the signal when first sampled is 10 mV above ground. The voltage applied to the sampling-preamplifier input will therefore be 2.5 mV after the first strobe pulse causes the sampling gate to conduct. If we have a forward gain of 400, the memory output will be +1 volt (400 x 0.0025). If the output of the memory is attenuated by a factor of 100 before being reapplied to the sampling-preamplifier input, then +10 mV will be fed back to this input. Ten millivolts, remember, was the level of the signal at the moment when sampled. Under these conditions we will have unity loop gain, a loop gain of one. That is because a sampling efficiency of 0.25 multiplied by a forward gain of 400 multiplied by a feedback attenuation of 1/100 equals 1.

When loop gain is 1, the voltage fed back and applied to the sampling preamplifier between strobes will be precisely the same voltage as applied to the samplinggate input at the moment the signal was last sampled. This is usually the ideal set of circumstances.

DC offset Now let's consider how the DC-offset control works. The primary purpose of this control is to allow us to sample and display small voltage changes on top of large DC levels at high sensitivities. We can typically offset a DC level that is, in effect, as much as 500-divisions off-screen vertically. For example, we can offset an input level of +1 volt at a sensitivity of 2 mV/div, a ratio of 500 to 1. When we say we are offsetting an input level of +1 volt at 2 mV/div, it means we set things so that a zero-volt signal level would be about 500 divisions off-screen and a 1-volt level is near center screen. We can regard the internally applied voltage as bucking the externally applied voltage. But at first it will seem strange that both voltages will have the same polarity.

> When we internally apply a DC-offset voltage, we tend to develop that voltage across  $R_{\rm f}$  in the feedback path by applying a specific constant current through  $R_{\rm f}$ . When no signal is applied to be sampled, the voltage sampled is always zero volts. Let us assume no signal is applied. If we apply a DC-offset voltage of +1 volt across  $R_{\rm f}$ , that voltage will appear at the amplifier input across the input capacitance. Then, when we first sample the input voltage (zero volts),

the capacitor partially discharges and the step change is amplified, transferred to the memory, held and fed back. The size of the step will be the same as if zero volts had initially existed across the capacitor and a 1-volt signal had been applied. The direction of the step will be down, as if the applied signal was negative in polarity, because the 1-volt level will diminish when the sampling gate conducts. The resulting step-voltage output from the memory would therefore be negative in polarity and would be larger than 1 volt in amplitude because of forward gain. The actual amplitude would depend on the forward gain and on the sampling efficiency. But if we assume that we have a loop gain of 1, the fed back portion, the portion existing across Rf, should be equal to that which existed across the sampling gate when the sample was taken. In other words, the feedback tries to place minus 1 volt across the same resistor that we had deliberately placed plus 1 volt across with the DC-offset control. The net effect is that essentially zero volts will be developed across the resistor  $R_{f}$ . The output voltage from the memory will be the proper amount to divert practically all of the current, furnished by the DC-offset circuit, from flowing through  $R_{f}$ . Subsequent samples will essentially see zero volts across the sampling gate, resulting in no change to be amplified and no change in the trace position on screen. However, the trace will be down, corresponding to a negative level at the memory output. If sensitivity is high enough to place the zero-volt level off-screen, the trace will be off-screen.

The voltage fed back and applied to the preamplifier input from the memory output, after being attenuated, has to be applied through a relatively high-resistance When the gate conducts, the voltage applied to Ri. the sampling-gate input can charge the stray capacitance at the sampling-preamplifier input rapidly compared to the rate that the voltage fed back from the memory output charges the input capacitance. The time-constant of the feedback path to the sampling preamplifier (comprised primarily of  $R_i$  and the preamplifier input capacitance) has to be chosen short enough so any output voltage step from the memory can fully charge the input capacitance to the sampling preamplifier through the resistance before the next sample is taken. But, the time-constant should not be so short that the input capacitance will lose much of its charge while the voltage across it is

feedback path time constant being amplified, or so short that the net gain around the closed part of the loop makes the feedback regenerative. Because the maximum sampling rate is typically once every 10  $\mu$ s, or longer, and the time the memory gate is conducting is typically less than 1  $\mu$ s, there is at least 9  $\mu$ s for the memory output to charge the sampling-preamplifier input capacitance each time a sample is taken. At least one of the amplifier stages preceding the memory gate is AC-coupled and the coupling time constant is made relatively short. In this way, each time the memory gate conducts, only the voltage from the *new* sample influences the charge stored on the memory capacitor.

Notice that the mV/DIV switch adjusts two sets of attenuators, ganged on the same switch, simultaneously. One is the forward-gain attenuator and the other is the feedback attenuator. By having these two attenuators always controlled simultaneously with the same switch, it is possible to maintain unity samplingloop gain for all settings of the switch.

There are several purposes for feedback. A minor one is to minimize energy being fed out of the vertical input connector from the push-pull strobe pulses that turn the sampling gate on and off. The sampling gate is a balanced sampling gate, one which is designed to minimize strobe-signal energy being fed back to the signal source. But how much energy is fed out is partly determined by what the signal voltage is at the time it is sampled compared to the voltage at the electrical center of the sampling gate. If both sampling-gate input diodes are back-biased at equal amounts above and below the level of the input-signal voltage when the strobe pulses arrive, the least amount of strobe signal is fed out. Remember that the center-tap voltage of the back-bias across the sampling-gate diodes may be a repeatedly changing voltage. It changes to follow every sample of the signal and is the same voltage as is attenuated and reapplied to the sampling-preamplifier input from the memory output. When loop gain is one, the voltage at the center tap is always the same as the voltage level of the input signal during the last sample. Most of the time, particularly when using the sequential mode of sample timing, successive samples represent very small differences in signal voltage level. Therefore, strobe signal kickout is minimized by continually rebalancing the sampling gate to match the last sampled signal level.

minimizing strobe signal kickout in forw tempera each of reducing stabili vertical- loop te deflection that ar errors the ten was the To unde forward

A more important purpose of the feedback is to minimize the effects of changes in forward gain. Because the forward-gain amplifier consists of several stages, there can be a considerable change in forward gain due to component aging and temperature changes in the instrument, even though each of the stages may employ inverse feedback to stabilize the gain for that stage. The sampling loop tends to reduce errors in vertical deflection that are due to changes in forward gain. However, the tendency is not quite the same as if the feedback was the ordinary, degenerative, out-of-phase type. To understand how it does work, imagine that the forward gain has for some reason decreased by ten percent. Without feedback, the beam deflection would also decrease by ten percent and the instrument, of course, would be in error by that amount. With the feedback system, however, only a few dots in a sweep can be in error by as much as 10% if we use the sequential mode, and if sufficient dots are present in the display this error may be well under 1%. То see why this is true, imagine that we are sampling a step voltage and the first few samples have been of the baseline ahead of the step. Let's say that level is zero volts. If we also assume that the step is very abrupt compared to the time per division, and that there are no samples on the rise of the step, we have suddenly changed from sampling zero volts to sampling some positive voltage level. The first sample of the positive voltage level will cause a dot to be positioned on-screen 10% lower than it should have been. This means that the output voltage from the memory was 10% lower and the voltage fed back and reapplied to the sampling-preamplifier input was 90% of what it ideally should have been. The next sample of the same positive signal level finds the voltage at the sampling-preamplifier input 10% lower than it should have been. Had it been correct, there would have been no difference in the two levels. The remaining difference is treated as an input signal although it is actually only an error signal. The second sample of the same positive level produces a dot on the screen which goes 90% of the remaining distance, within 1% of the correct level. The first 10% error was corrected to within 1% of the correct value on the second try. By having a method of sampling which requires only that the difference between one sampled voltage and the next be processed, the difference may partly consist of errors in forward gain; and when it does, the error is minimized on subsequent samples. In the example we assumed we had

no dots on the rise. Had there been several dots on the rise of the step the dot position error would have been well under 10%. By minimizing errors in deflection in this way, we can deliberately reduce forward gain with the smoothing control, reducing random noise in the display. The smoothing control typically reduces sampling-loop gain by a factor of about 4 to 1 and this will reduce noise by about 3 to 1. The only corresponding requirement is that dot density be maintained at a high enough level to minimize dot-position errors.

A system which operates on the voltage difference offset from one sample to the next can inject an offset voltage i.e., one which makes the input operate very much the same as a differential amplifier. The offset feature on a sampling oscilloscope is one of its main attractions because the display is almost completely free from aberrations due to overscanning the screen. Also, the offset voltage can be monitored to a fairly high degree of precision when desired.

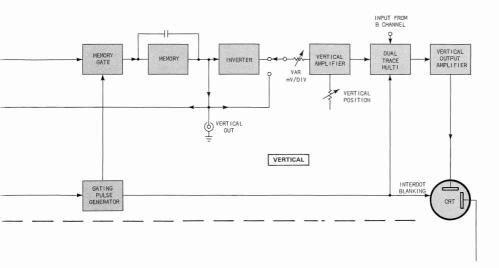

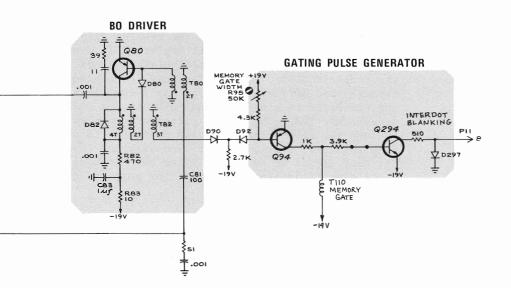

> Notice now, in the block diagram, the lines coming from the blocking oscillator or avalanche driver. One line goes to the gating-pulse generator. From there a line goes to the memory gate, another to the dual-trace multi, and still another to the cathoderay tube to produce what is called interdot blanking. The CRT beam is blanked for about one microsecond everytime a sample is taken, while the beam might be moving vertically. The purpose and effect is similar to transient blanking used in the chopped mode in conventional oscilloscopes. With this system the beam is turned on all the time except during the intervals when the dot is being changed from one position to the next and during retrace.

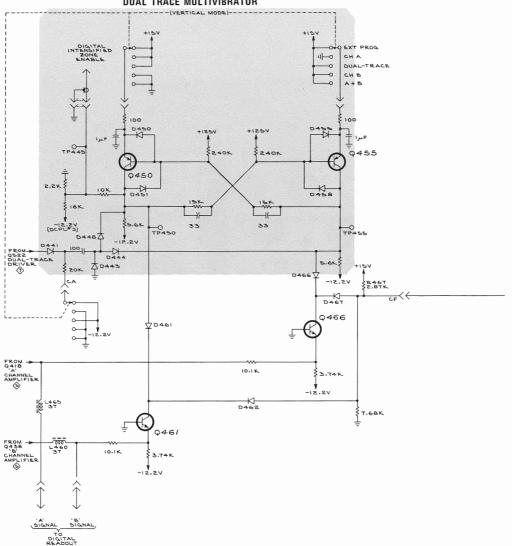

On sampling scopes having two input channels, instead of just a single channel as is shown in the block diagram, there are two sets of sampling-loop circuits and the output from each of the two memory amplifiers is fed to a dual-trace switching circuit ahead of the CRT vertical output amplifier. Dual-trace operation in a sampling scope is not the same as alternatetrace operation in a conventional scope. Instead the dual-trace mode is similar to the chopped mode which produces two traces in a conventional scope. Each sample of the two input signals is held in a separate memory. The output of each memory is displayed alternately on successive dots.

interdot blanking

dual-trace

In the basic block diagram (Fig. 2-1), the signal which produces interdot blanking is the same one which switches the two memory outputs of a twochannel sampling scope. This dual-trace multi does not have to be synchronized with the occurrence of each sample, but when it is synchronized the job of blanking the beam while moving it is simplified.

single sweep Whenever we produce a single sweep using a sampling scope, the number of dots displayed on-screen is equal to the number of signal cycles sampled during the sweep. In a sampling scope, single-sweep operation is not single-shot operation. We can display two traces in one sweep with an equal number of dots in each trace.

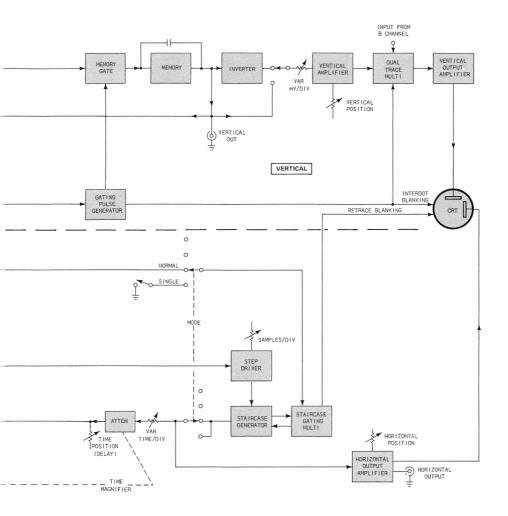

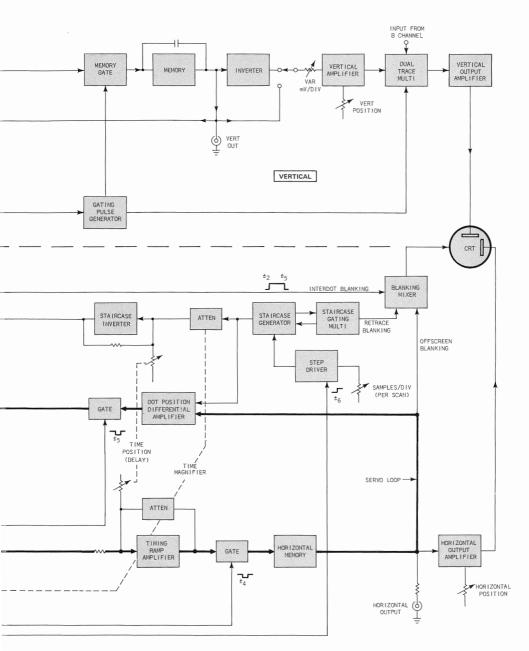

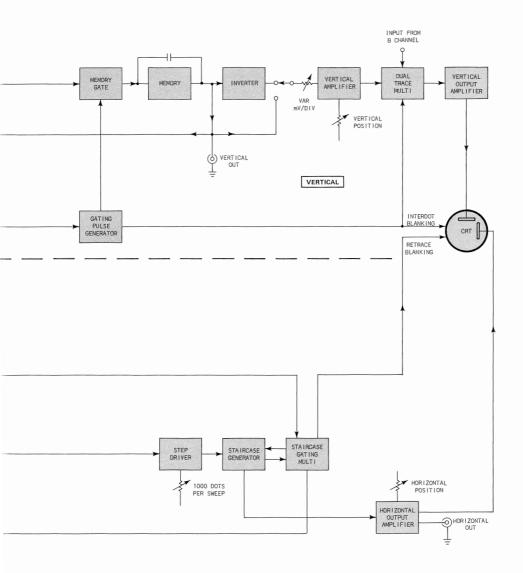

Fig. 2-3. Sequential-mode block diagram.

21

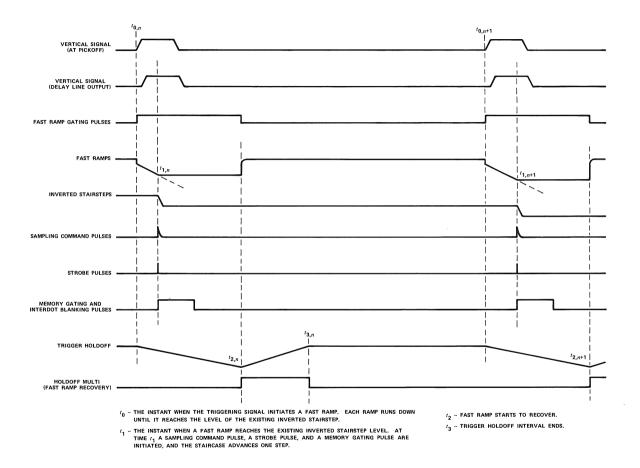

Fig. 2-4. Sequential-mode timing diagram.

#### SEQUENTIAL-MODE TIMING

fast ramp

timing ramp

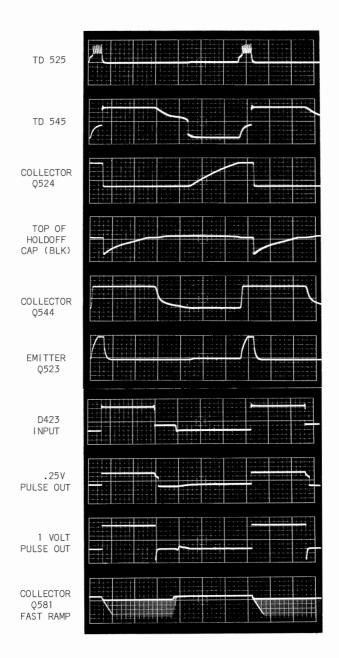

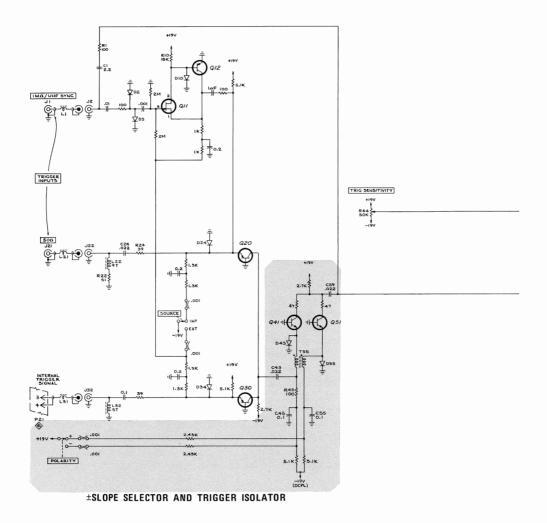

This is a discussion of the function of the horizontal section of a sampling oscilloscope operating in the sequential mode, using Fig. 2-3. Fig. 2-4 shows time relationships.

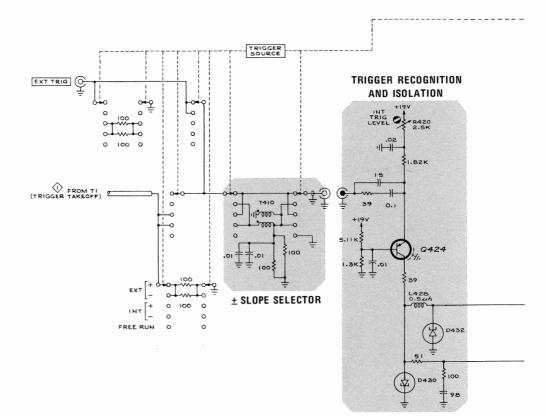

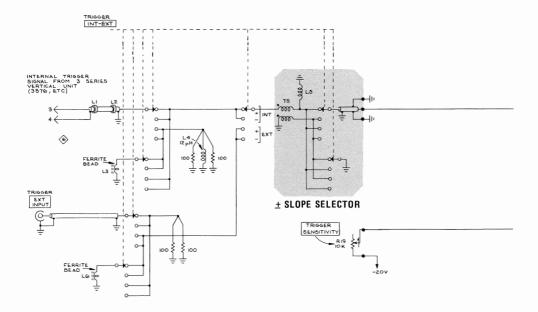

Notice that, similar to conventional scopes. we must have a triggering signal in order to make a triggering coherent display. The block diagram shows a portion of the vertical-input-signal energy diverted and delivered to the trigger-recognition block by way of the trigger slope-selection block. A suitable triggering signal from a different source might have been applied via the EXT trigger input.

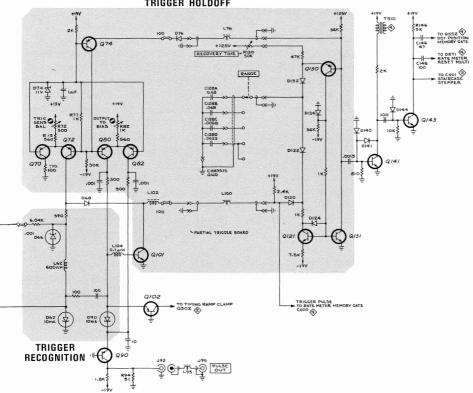

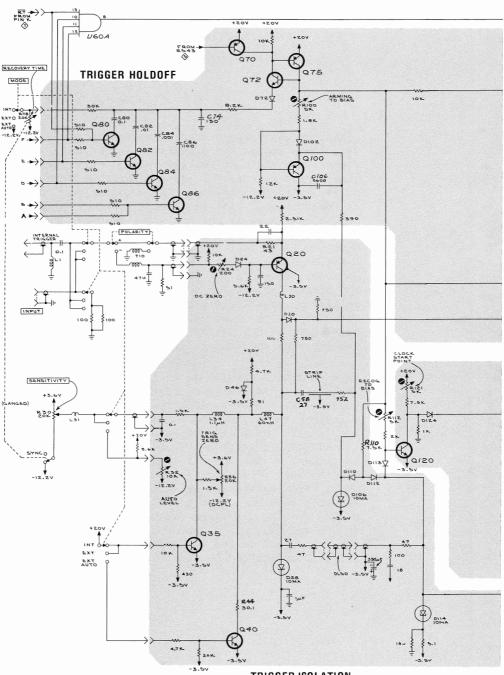

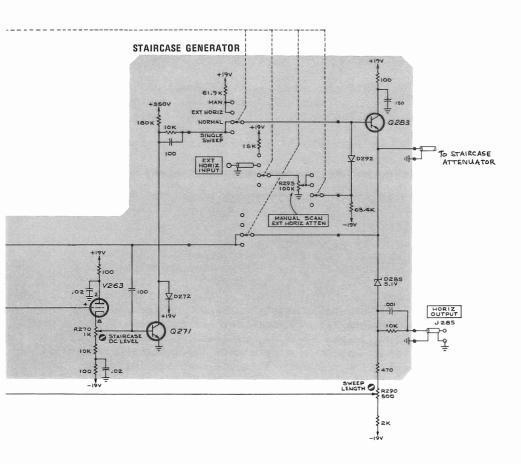

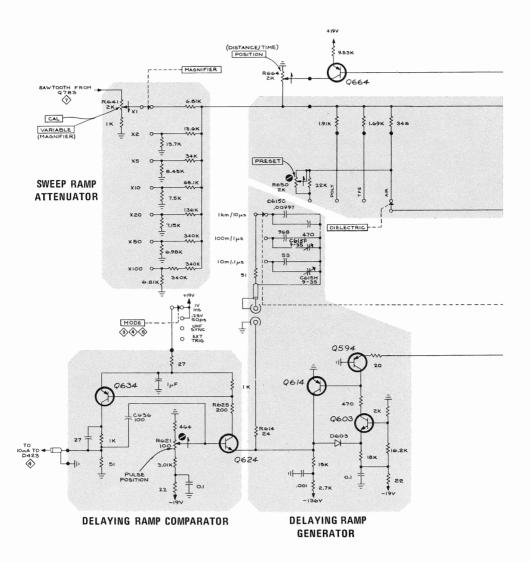

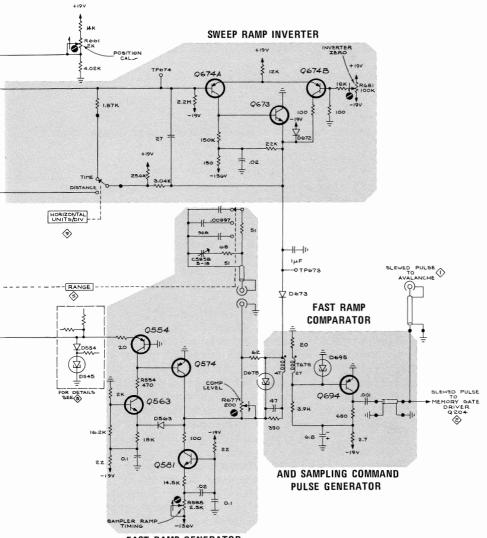

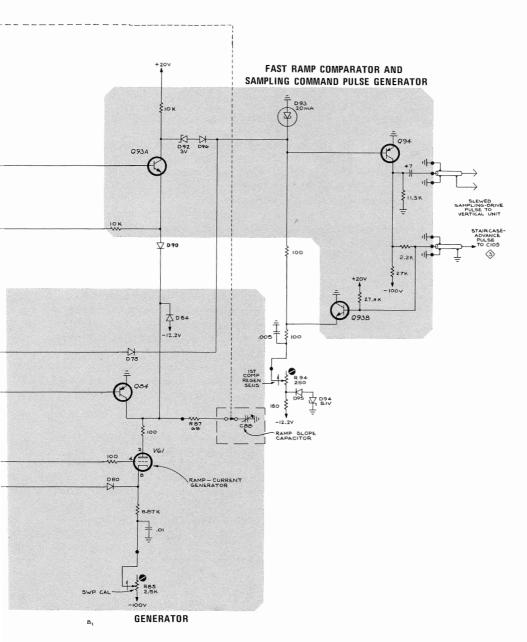

The function of the trigger-recognition circuit is, as the name implies, one of responding to a suitable triggering signal. The response generates a fast step-signal that initiates a ramp. This ramp can be called a fast ramp, timing ramp or slewing ramp. Ιt is very similar in some respects to the sweep ramp in a conventional oscilloscope. One radical slewing ramp difference is that the slewing ramp causes no deflection. It is not applied, directly or after being amplified, to the horizontal-deflection plates. Nevertheless, this slewing ramp is one of several primary factors in a sequential-sampling time-base circuit which determine the horizontal time per division. If we steepen the slope of the fast ramp, and change nothing else, we reduce the time per division of the scale. Any nonlinearities in the slewing-ramp voltage produces a nonlinear time scale. The time-per-division on sampling scopes can be much less than on wideband conventional scopes. In wideband conventional scopes we use the fastest ramps we know how to produce, so it may be puzzling how in sampling scopes we can possibly depend on the slope of a ramp to determine the time per division. In sampling scopes, do we actually generate steeper, faster ramps than in conventional scopes? The answer is no; we don't need to. And the reason is that the ramps do not have to be very high in amplitude. In fact, to achieve less time per division on a sampling scope we only need to use *less* of a given ramp. How we accomplish this will be explained in detail later. The process is analogous to sampling a section of the timing ramps and amplifying those samples to produce horizontal deflection.

In the sequential mode, even though the horizontal position of each dot is not determined by a sample of a timing ramp, each sample does correspond to a different point on a timing ramp. In the random mode, as we will see later, the timing ramps are sampled, amplified and stored.

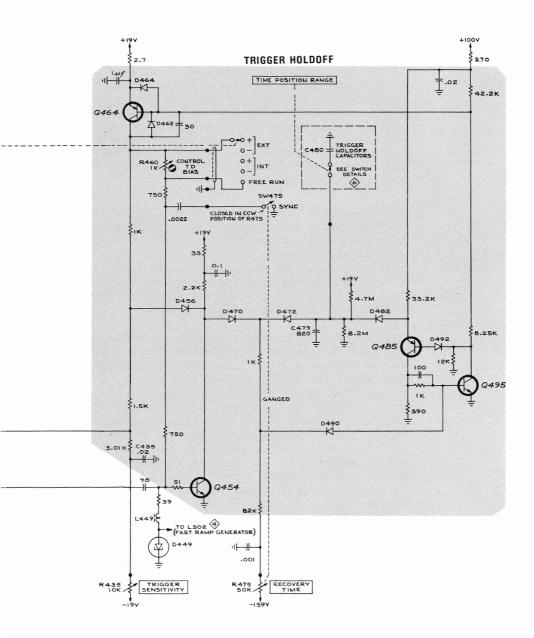

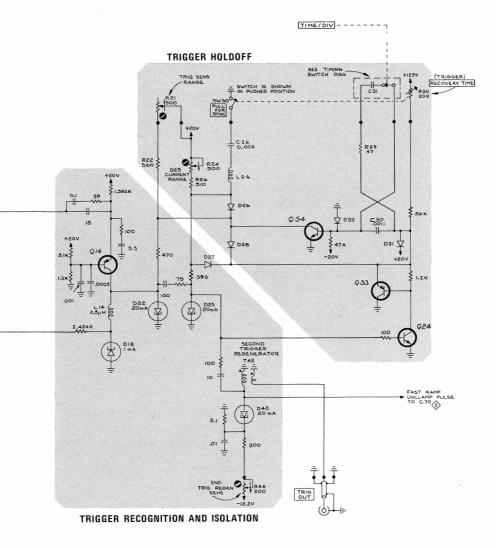

The trigger-holdoff block, just below the trigger trigger holdoff recognition block in the diagram, represents a function which is very much the same as found in a conventional oscilloscope. That is, its purpose is to prevent the premature initiation of a new ramp excursion before the full recovery of the last one. By holding off the triggering signal or, in other words, recognizing only every cycle of the triggering signal that you can utilize, each fast ramp has an opportunity to fully recover and be ready to start again before a new one can possibly be triggered.

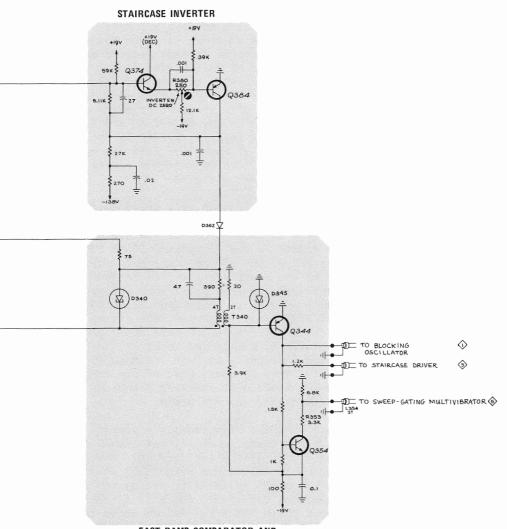

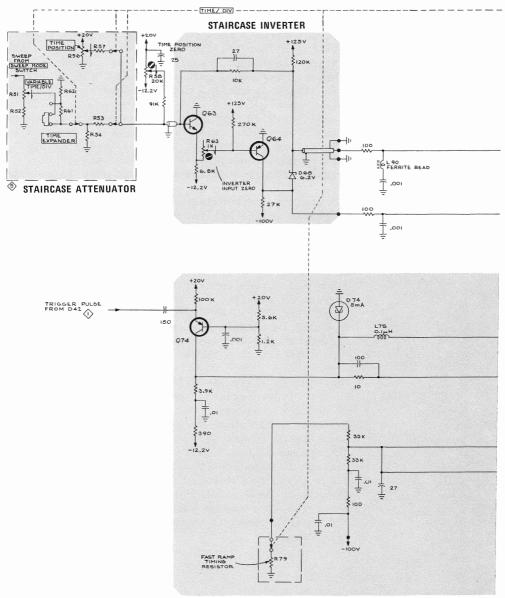

Whenever you change the time per division of the scale with a knob on the front panel, you may change one or a combination of four things. One of them is the capacitance of the fast-ramp generator. That capacitor determines the slope of a fast ramp. Another is the capacitance of the holdoff capacitor which, with the Recovery Time control, determines how far a given high-frequency triggering signal will be counted down. The third is the Display Magnifier, a gain-control switch for the horizontal amplifier. The fourth is an attenuator resistor which, as you can see, is inserted between the output of the staircase generator and the staircase inverter. Changing this attenuator provides what is called time magnification magnification, as contrasted with display magnification.

> The output of the staircase inverter feeds to one side of the comparator block. The other side of the comparator receives the fast ramp. Whenever a fast ramp reaches the level of an attenuated and inverted voltage, corresponding to a particular step in the staircase generator, a "slewed pulse" is produced which goes to a variety of places. The reason these pulses are called slewed pulses is that normally each successive pulse that emerges from the fast-ramp comparator is slightly later than the previous one with respect to any given point in a cycle of the signal. This slewing (or sliding) correctly implies

24

time +

slewed

pulses

that each successive pulse out of the fast-ramp comparator is delayed one increment more than the former one with respect to the beginning of each fast ramp (a point in each recognized cycle of the triggering signal). A more general term for slewed pulses is sampling-command pulses.

In a sampling scope display each dot on the screen represents a single sample of the vertical-inputsignal voltage. In the sequential mode of timing samples, each successive dot on the screen is laid down from left to right in a very orderly fashion. Each new sample of the vertical signal should be a point in the signal cycle which is slightly later than the point sampled in the previous cycle. All points of interest on an input signal are sampled, in the sequential mode, by having each successive sample of each successive cycle occur slightly later in the cycle than the previous sample.

Perhaps we are now ready to see why fast ramps are also called timing ramps and sometimes slewing ramps. They have two primary functions. One function is to help determine what the time-per-division of the horizontal scale shall be. That function is the timing function. The other is to produce a series of increasingly delayed sampling-command pulses that allow us to sample all portions of the signal of interest when enough cycles have occurred. That function is the slewing function.

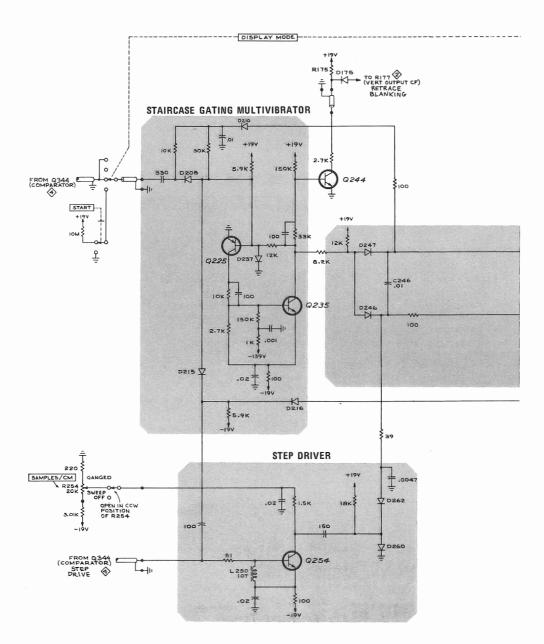

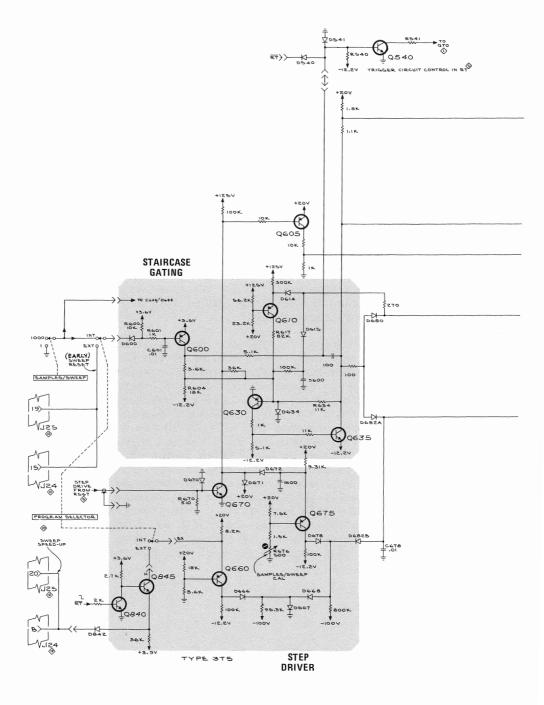

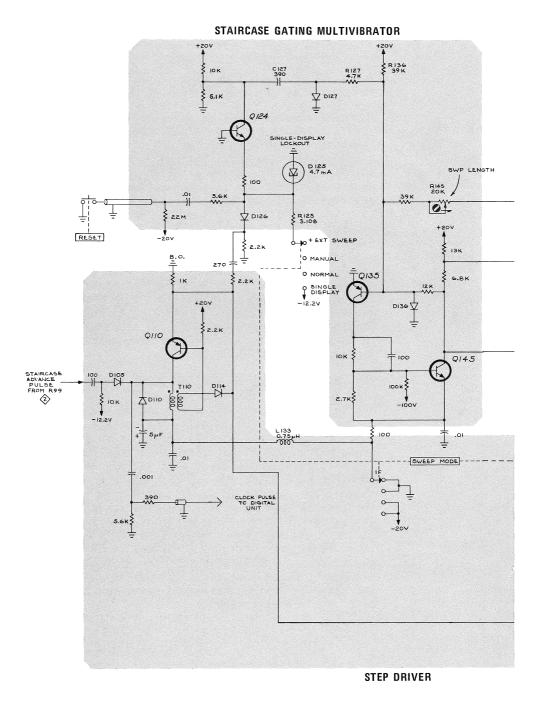

As you can see by the block diagram, there are two places where the slewed pulses are delivered inside the horizontal-deflection portion of the diagram. One place is to the staircase-gating multi; the other is to the step driver. The staircase-gating multi has two functions. One of them is to initiate a staircase and another is to stop the staircase after it has reached sufficient amplitude and allow it to recover.

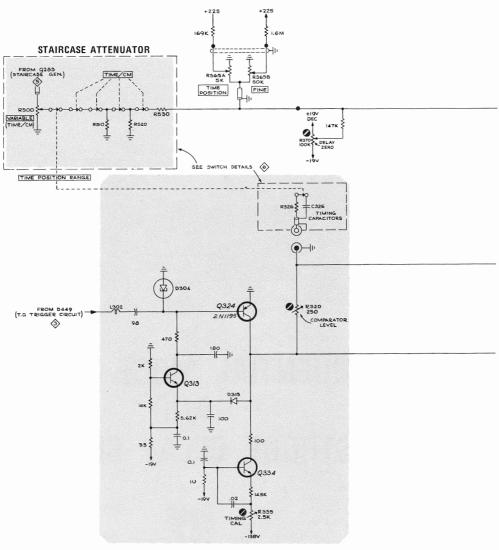

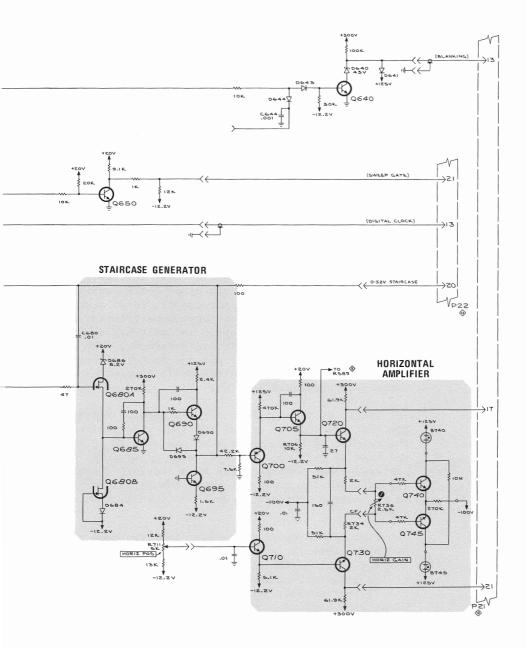

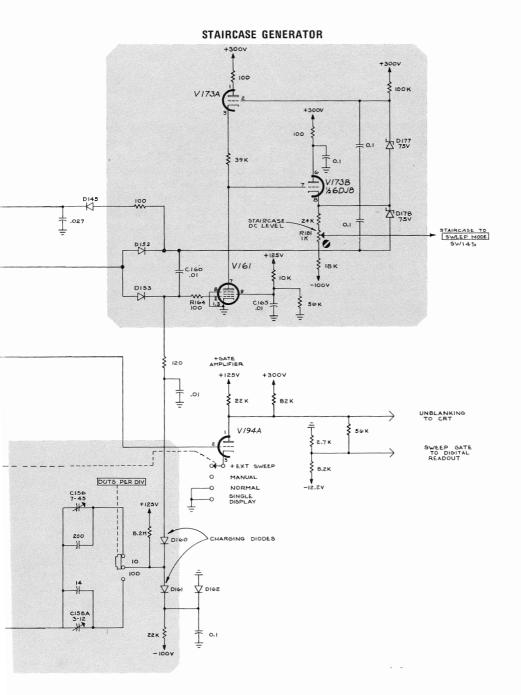

staircase The staircase generator also has two functions. One generator of them is to produce the horizontal deflection when applied to the horizontal output amplifier. The other is to produce sets of advancing reference voltage levels, which, after being attenuated and inverted, are applied to one input of the comparator.

samplingcommand pulses

staircase-

gating multi The staircase generator generates a positive staircase. That staircase is applied to the horizontal output amplifier, and produces horizontal deflection, one dot at a time. After the staircase is attenuated and inverted, it is negative-going and of less amplitude than originally. The staircase inverter is needed because the stairstep levels should advance in the same direction as the ramps, which are negative-going.

Imagine the two inputs to the comparator: On the left-hand side is a series of negative ramp voltages; on the right-hand side is a negative staircase, a cyclic set of advancing reference levels. A new staircase level is generated each time a ramp voltage crosses the existing staircase level. Refer to Fig. 2-4. You may see that the instant when each fast-ramp crosses a new staircase level will be slightly later than the last, when compared to any given point in the sampled signal. That is because every staircase level coming into the comparator is slightly lower than the former one, and each fast ramp has to reach that level by travelling further. There is precisely one step in the staircase each time there is a fast ramp, because the slewed pulses which come out of the comparator are the same pulses which drive the step driver and cause the staircase generator to advance one step. Every time the staircase generator advances one step, an inverted step of proportional size is applied to the righthand side of the comparator and becomes the new reference level which the subsequent fast ramp must cross to produce the next slewed pulse.

After enough steps have been generated so that the staircase staircase amplitude reaches a predetermined voltage, reset the voltage necessary to produce full-scale horizontal deflection, the staircase-gating multivibrator turns off the generator, allows it to recover and be readied for a new staircase. Any fast ramps which are generated during the time when the staircase generator is recovering will also cause slewed pulses to be produced and samples of the signal taken, but these samples will not be shown on-screen because the staircase-gating multivibrator blanks the CRT during the retrace period. The retrace period is the time when the staircase generator is recovering and getting ready to generate another staircase.

ramp versus staircase in comparator dots per division

time per

division

Let's consider that we have a 50-volt staircase which has a thousand steps, resulting in a thousand dots across the ten-division screen. This is 100 dots per division. Let us also assume that the ramp voltage goes from zero to ten volts negative. If we were to attenuate the staircase generator by a factor of ten the output of the staircase inverter would be a smaller staircase that went from zero to five volts negative. The 0 to -5 volt excursion of the inverted staircase would be only one-half of the 0 to -10 volt amplitude of the ramp. Also, in that 0 to 5 volts there would be 1000 separate discrete levels applied to the comparator during the time when the staircase generator was running up. That is to say, each discrete level of the inverted staircase would only differ from the next by one-thousandth of five volts, or five millivolts. Now if the slope of the 10-volt ramp were such that it took 100 nanoseconds to go from 0 volts to 10 volts, we may see that any 5-volt segment of the 10-volt ramp will occur during 50 ns. If we assume that the first dot laid down on the screen corresponds to a time when a fast ramp crossed a minus 1-volt level coming from the staircase inverter and the last dot on screen corresponds to the time when a fast ramp crossed a minus 6-volt level coming from the staircase inverter, you may see that in terms of one fast ramp only, the time between the first dot on screen and the last on screen corresponds to 50 ns. Now it is true that 1000 fast ramps had to occur before we would get 1000 dots on the screen, but in terms of just the increments of delay of each successive slewed pulse from first to last, we would have 1000 increments totaling 50 ns. This would tell us that the time per division of a ten-division horizontal scale would be 5 ns.

If we remember that there are 100 dots for every division, then we can figure that the time represented by the distance between each successive dot is 1/100th of 5 ns, or 50 ps. Now the time represented by the distance between dots at this point is not very significant, but it is interesting to note that the 50 ps represented by the distance between dots corresponds to the real time it takes for a fast ramp to change 5 mV. In other words, the time it takes a ramp of that slope to move 5 mV is 50 ps. The 5 mV figure, remember, was the difference in staircase level from one step to the next at the input to the comparator. If the sweep were comprised of less than 1000 dots, then the time represented by the distance between dots would be greater than 50 ps, but the time represented by one centimeter on the scale would remain unchanged at 5 ns.

As mentioned earlier, one of the things which determines the time per division of the horizontal scale is the amount of attenuation between the staircase generator and the staircase inverter. Ιf we were to attenuate the staircase by a factor of 100, instead of by a factor of 10 such as we chose in the example in the last paragraph, then the difference in level between each successive step out of the staircase inverter would be only 1/10th of 5 mV, or 500  $\mu$ V. Then the time it takes one fast ramp to go between one level and the next would be 1/10th of what it was formerly. The full 10-division scale, instead of corresponding to 5 volts of the fast ramp, would now correspond to only 1/10th of that or 0.5 volts. In this case the time-scale would be 0.5 ns/div instead of 5 ns/div and the 10-division scale would be 5 ns. Simply by attenuating the staircase fed into the comparator, we can make a given ramp produce a time-scale that represents less time per division. However, carefully notice that the staircase which goes to the horizontal amplifier is not attenuated. It always remains adequate to produce full-scale deflection. Had it been attenuated by the same factor (10X) there would have been only one division of deflection instead of ten and no change in the time represented by that division.

time/div independent of dots/div

It is important to mention again that in the sequential mode, whether we have a 1000-dot sweep or a sweep with some other number of dots, the time per division of the scale does not change. (However, the time it takes the beam to move one division will change.) The reason the time scale doesn't change is that when the staircase steps are large and produce a correspondingly large horizontal separation between dots, they also produce a proportional change at the comparator input. For example, if instead of having a 1000-step staircase, we changed the samples per division at the step driver so that we had a 500-step staircase, then each level fed to the comparator after being inverted by the staircase inverter would not be 5 mV, as we chose originally, but 10 mV. The

time represented by the distance between dots then would be 100 ps instead of 50 ps, but because there are only 50 dots per division now, instead of 100 dots per division, we still would have 5 ns per division.

time position

Notice the time position control inserted between the staircase inverter and the attenuator leading into it. The time position control on a sampling scope is the same sort of thing as a sweep delay control in a conventional scope, except that the rotation of the dial clockwise produces a movement of the display to the right, the opposite direction from what we're used to for a delay control, but the direction you might expect. Time position seems to be an obvious term if you imagine the CRT screen as a sort of port or window through which a portion of the graphic history of a changing voltage may be viewed. What the time position control does in the circuits is to apply an offsetting DC current at the input of the staircase inverter, so that the output level of the entire inverted staircase may be varied. Typically, the time position control allows us to move the level of the inverted staircase by up to half of the voltage of a full excursion of the fast ramp. In the example we said the fast ramp had a 10-volt excursion, and we said the attenuated and inverted staircase had a 5-volt excursion. If, using the time position control, we can make the first staircase step at the output of the staircase inverter be anywhere from 0 to -5 volts, the last step would end somewhere between 5 and 10 volts. By this means we utilize the fast ramp to produce delay, as well as perform its other functions. Whenever we have the time position control rotated fully clockwise, we have minimum delay and the display on the screen moves to the right as far as possible. In the other extreme, if the time position control was rotated fully counterclockwise, delay would be a maximum and the display on screen would move as far to the left as possible. Under the latter conditions, the staircase would start at -5 volts and move down to -10 volts. You may see then that each fast ramp must move at least 5 volts in order to reach a voltage level fed into the comparator from the staircase inverter. The first dot on-screen would then correspond to a delay equal to 5 volts on the fast ramp, or 50 ns of delay.

This completes a description of the fundamental concepts of the conventional sequential mode of sampling. The method of relating all the horizontal positions of the beam to corresponding points on a fast ramp is unique to this mode. And the technique of delaying the strobe pulses by discrete timeincrements which are related jointly to the slope of the fast ramp and the position of the beam is also unique to this mode. The 7T11 Time Base unit has some variations, however.

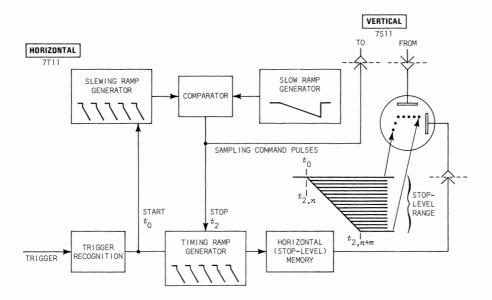

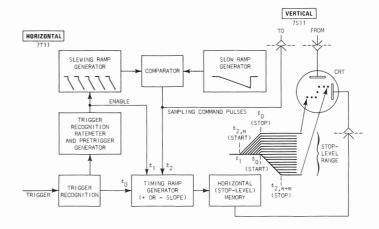

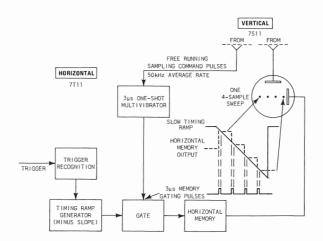

#### 7T11 SEQUENTIAL-MODE PRINCIPLES

Refer to the simplified block diagram on the opposite page.

Each time the input triggering signal is recognized, both a slewing ramp and a timing ramp are initiated simultaneously. Each slewing ramp runs down until, as it crosses the ramp level that exists at the output of the slow ramp generator, it generates a sampling-command pulse. Each sampling-command pulse stops the run-down of the timing ramp and causes the vertical input signal to be sampled. The stopped level of each timing ramp is transferred to a horizontal memory and causes horizontal deflection proportional to the stopped level.

Unlike the more conventional method of sequential sampling, the horizontal position of each dot is not predetermined by a staircase generator. If a sampling-command pulse is generated a little earlier or later than it ideally should occur, because of inherent noise in the comparator, the timing ramp will be stopped early or late by the same amount, reducing time jitter in the displayed signal. The horizontal spacing between successive dots may change, therefore, and corresponding dots in successive sweeps may not precisely overlap.

Fig. 2-5. 7T11 sequential mode (simplified).

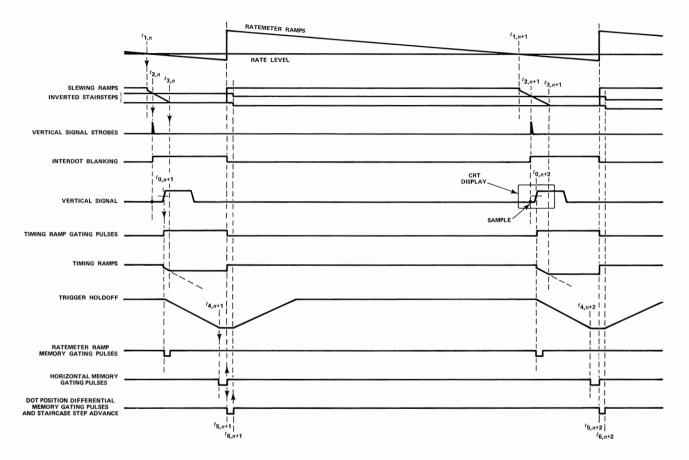

Fig. 2-6. Random-mode block diagram.

Fig. 2-7. Random-mode timing diagram.

## RANDOM-MODE TIMING

Random sampling is one of the basic modes of strobe timing used in sampling oscilloscopes. A good understanding of the sequential mode discussed earlier in this chapter is required for this discussion. The two strobe timing methods for the real-time mode are discussed in the last part of this chapter.

random dot sequence The random mode is not simply a mode for sampling a signal which occurs at a random rate and producing a coherent graphic display from such samples. The sequential mode actually handles signals of that character better than the random mode. The use of the word random pertains to what appears to be an absence of order in the sequence in which dots occur on the screen, and to the fact that the sampling command pulses do not have to be precisely synchronized with the signal being sampled. The timing ramps *are* still triggered in precise synchronism with the signal cycles, however.

When the sampling command pulses are not precisely synchronized with the signal cycles, each sample will produce a dot which may occur on the screen either to the left or to the right of the previous sample, without effecting the coherence of the display. The dots laid down on the screen, therefore, appear to be at random compared to the sequential mode. The degree of randomness is a function of signal-cycle jitter and jitter of other kinds. No deliberate attempt is made to sample in a random fashion. Because the dots are not laid down from left to right across the screen in a completely orderly sequence does not mean that each dot cannot be in its correct position. Plotting any graph, point by point, can be done just as well by jumping around at random as when done in a more orderly manner as long as each dot is plotted at the *correct* X and Y coordinate position.

The *advantage* of the random mode of sampling does not pertain to randomness of any kind in any way. The advantage of random sampling is that it is a way of or pretrigger sampling and viewing sections of a signal ahead of need the trigger-recognition point (usually on the leading edge of a pulse) without the use of vertical signal delay lines or an externally-applied pretrigger signal. When we use sweep delay in a conventional oscilloscope to view portions of a signal ahead of the trigger-recognition point, we sometimes may accomplish the same sort of thing. When we do, we depend first of all on the fact that the signal is recurrent. Whenever a signal is recurrent we can trigger a delay generator with one occurrence of a signal cycle, and with the delay generator cause a subsequent trigger pulse to be generated ahead of the next occurrence of the signal cycle, the one to be viewed. When we do this, we are essentially generating our own pretrigger signals and this is basically the same process we use in the random sampling mode. But there are two big differences in the analogy. First of all, in a sampling oscilloscope operated in the random mode, we use a system of automatically metering the signal cycle repetition rate so as to produce delayed triggers which occur at the same rate or a submultiple of the same rate. But the main difference is that time-jitter, due to either scope delay-jitter or signal-cycle jitter, does not show up as a blurred display. Instead, such jitter merely affects the degree to which successive dots appear to occur in random positions. We trade what would be a jittery, blurred, incoherent display for one which is coherent by allowing the jitter to manifest itself in the randomness of dot positions. This process is not the same as using a delayed trigger merely to arm the trigger recognition circuits. That process still relies on the use of a vertical signal delay line to view sections ahead of the trigger recognition point.

timing ramp is sampled

delayed

triggers

jitter

The underlying principle of trading delay jitter for randomness of the point-by-point plot is that both the vertical signal *and* a triggered linear timing ramp corresponding to a sweep are sampled each time a dot is displayed on the screen. Because each timing ramp is triggered by the same point in each cycle of the signal which is sampled, the proper X and Y coordinates for each dot are available at the output of the vertical memory and the horizontal memory. In the sequential mode no ramp is sampled, only the vertical signal is sampled.

Refer to the double-page block diagram, Fig. 2-6. Notice that in the random mode two kinds of samplingcommand pulses are generated. One goes to the vertical-deflection section of the scope to cause the vertical signal to be sampled, and one stays in the horizontal-deflection section to cause the timing ramps to be sampled. The ramp-stop pulses cause the timing ramps to be sampled. In the random mode, two separate and distinct sampling processes go on continually; one for the vertical signal and one for the timing ramps. The sampling-command pulses for the timing ramps are called ramp-stop pulses. Samples of the timing ramps are amplified and stored in the horizontal memory. From there they are amplified and produce horizontal deflection in very much the same way as the output from the vertical memory produces vertical deflection.

In the sequential mode of operation, you may recall, the fast ramps perform two functions. One, the timing function, is to help determine the time per division of the horizontal scale and the other, the slewing function, is to produce various increments of strobe delay so that all portions of the signal to be sampled will be sampled and displayed. In the random sampling mode these two functions still must be performed. One is performed by fast ramps from one fast-ramp generator and the other is performed by fast ramps from a second fast-ramp generator. Both ramps have precisely the same slope and have the same repetition rate but start at different moments. One of these fast ramps is called the timing ramp and the other is called the slewing ramp.

Now the main purpose of the random sampling mode, remember, is to reduce the need for a vertical signal delay line when no pretrigger signal is available. To do this it is necessary to generate our own pretriggers. However, unlike the usual pretrigger, the ones that we *generate* in the random mode do not have to occur precisely the same amount of time ahead of the section of the signal to be displayed each time they occur. That is because there are *two* related but separate triggered functions in sampling scopes but only *one* in a conventional scope. In a

two fast-ramp generators conventional scope we only need to trigger a sweep ramp. In a sampling scope we must not only trigger a timing ramp but we must also trigger the strobe pulses that sample the signal to be displayed. In the random mode we trigger the timing ramps in the usual way and with the internally generated presignal triggers cause the strobe pulses to be generated. But the strobe pulses are not triggered directly by the presignal triggers but are triggered after being increasingly delayed (slewed) with reference to the presignal triggers.

In both the sequential mode and the random mode the instant when the timing ramp triggering signal is recognized defines the trigger-recognition point  $(t_0)$  on the vertical signal. Whether the timing ramp triggering signal is a portion of the vertical input signal or an externally applied triggering signal is immaterial. In the random mode an externally applied triggering signal may be used that lags the leading edge of the signal to be displayed. In that case the trigger recognition point would be later than the leading edge but points ahead of the leading edge could still be sampled and displayed.

Let's look at the block diagram (Fig. 2-6) and note some similarities between the random mode of operation and the sequential mode. First of all notice that, as with the sequential mode of operation, only two signal lines go between the vertical and the horizontal sections of the block diagram. The one at the far left is the signal line which carries the trigger-pickoff signal from the vertical-signal input to the trigger-recognition block at the bottom lefthand corner of the diagram. Going from the horizontal section to the vertical section are the sampling command pulses from the slewing-ramp comparator. In the bottom left-hand corner of the diagram we see the trigger-recognition block and the trigger-holdoff block, both of which are common to the sequential mode of operation. The primary signal out of the trigger-recognition block is the step signal which initiates the timing ramp in the timingramp generator. This also is common with the sequential mode of operation, except the timing ramp is called either a fast ramp or a slewing ramp. As mentioned earlier, the slewing function is performed by a slewing ramp. It has the same slope as the

timing ramp. The slewing-ramp generator block is in the upper left-hand side of the horizontal section of the block diagram. The slewing ramp drives the slewing-ramp comparator in the same way that the fast ramp drives the fast-ramp comparator in the sequential mode diagram. The voltage levels against which the slewing ramps are compared are negative levels which arrive from the output of the staircase inverter. The staircase inverter is driven by a positive-going staircase, which is first attenuated before being applied to the staircase inverter.

One big difference in the random mode of operation is that the staircase generator does not produce any horizontal deflection. The sole purpose of the staircase generator is to help the slewing ramps produce sampling-command pulses and ramp-stop pulses that sample all portions of the vertical signal and timing ramps.

The staircase-gating multi and the step-driver have functions similar to that of the sequential mode.

Six of the blocks in the horizontal section of this block diagram have functions which are involved with nothing except generating presignal triggers. The names of the six blocks are: Ratemeter ramp generator, ratemeter ramp memory, ratemeter ramp comparator, error correction matrix, dot position difference memory and dot position differential amplifier. A discussion of the functions represented by those blocks will be postponed while we give our first attention to the other blocks.

We said that the slewing ramps, in the upper lefthand corner, drive the slewing-ramp comparator to produce sampling-command pulses for the vertical section. Notice, also, that the slewing-ramp generator drives another kind of comparator called the leadtime comparator. The stepped reference voltage levels for both of these comparators are the inverted staircase levels that correspond to the staircase steps after being attenuated. The output of the staircase inverter is a negative-going staircase. Notice that the negative-going staircase, before being applied to the leadtime comparator, is offset further negative by the voltage drop across the resistor labeled leadtime offset. In an actual circuit a constant current flows through that resistor producing a constant voltage drop.

leadtime comparator

The slewing ramps, the same as the fast ramps in the sequential mode, are negative-going ramps. But unlike the sequential mode, two pulses are produced every time a slewing ramp occurs instead of just one pulse. The first emerges from the slewing-ramp comparator. The second emerges from the leadtime comparator. The sampling-command pulses which come from the slewing-ramp comparator always cause the vertical input signal to be sampled and that is always sooner than the ramp-stop pulse samples the timing ramps. A pulse edge from the leadtime comparator stops the timing ramp at whatever voltage the ramp had reached at the moment the pulse edge occurs, and that level remains constant until the timing-ramp gating pulse ends and the ramp starts to recover. This manner of stopping the timing ramp and causing it to remain at the level at which it stopped is the process of sampling the timing-ramp signal. The stopped amplitude of each timing ramp is a good sample of the amplitude that existed at the moment the stop-pulse arrived from the leadtime comparator. Do not misunderstand the function of the leadtime comparator. Leadtime is the amount of time ahead of the trigger-recognition point that we may sample and display the vertical signal. The pulses which emerge from the leadtime comparator always follow the pulses which emerge from the slewing-ramp comparator. However, the difference between the instant when each sampling-command pulse is generated and the subsequent instant when each timing-ramp-stop pulse is generated determines the determination leadtime. Adjustment of the Leadtime Offset control, an internal adjustment, determines the difference in the reference voltage levels that are applied to the two comparators from the staircase inverter. The difference in level determines the difference in time between the generation of a sampling-command pulse and the generation of a ramp-stop pulse, and this determines the leadtime.

Each stopped timing ramp is amplified and inverted by the timing-ramp amplifier and applied to a horizontal horizontal memory. The output of the horizontal dot memory, after being amplified by the horizontal-output position amplifier, determines the horizontal position of any dot on the screen. Under ideal circumstances the dots which are laid down on the screen simulate the

samplingcommand pulse

timing-rampstop pulse

leadtime

appearance of the sequential mode, where they are laid down from left to right in equal steps from the output of the staircase generator. But the horizontal position of any dot is not *controlled* by the staircase generator. Instead it is controlled by the voltage at the output of the horizontal memory.

time-perdivision controls The time per division for the horizontal scale for the random mode is controlled from the front panel by three controls. One of them determines the slope of the timing ramp, one determines how much amplification we use ahead of the horizontal memory and one controls the gain of the horizontal amplifier. The TIME MAGNIFIER controls the amount of amplification, TIME POSITION RANGE control determines the slope of the timing ramp, and a control called DISPLAY MAG determines the gain of the horizontal amplifier.

The horizontal deflection system for the random mode of operation is very similar in many respects to the conventional oscilloscope sweep generator and sweep magnifier. It is not at all like the sequential-mode deflection system. In a conventional scope the fastest sweep is generally achieved by the process of amplifying a small portion of the fastest sweep ramp. Almost exactly the same sort of thing occurs in the random sampling mode, except that by sampling the timing ramp before amplifying it we may amplify it with amplifiers having a low bandwidth and thereby easily achieve less time per division for the horizontal scale. In the 3T2, for example, the time magnifier can magnify the fastest timing ramp 50 times, and the fastest timing ramp without magnification is 10 ns per division. How short the time per division might be is limited only by what practical use might be made of extremely short time-scales and how much display time-jitter you are willing to tolerate. Light travels one centimeter in 33 ps in air and it is common for the shortest time per division to be equivalent to a 20 ps per centimeter rate or faster.

As long as the vertical signal and the timing ramps are locked together, simultaneously sampling those two signals should result in two samples that bear the correct X and Y coordinate relationship to each other, regardless of when the samples are taken.

short time-scales

This is when the samples are taken simultaneously. What if they are not taken simultaneously but one sample is taken before the other? Even then it doesn't matter so long as the time between each pair of samples remains unchanging. See Fig. 2-7. When a sample of the vertical signal precedes a sample of the timing-ramp signal by the same amount every time the two signals are sampled, the display will be just as correct and coherent as if the pairs of samples always occurred simultaneously. The difference will be that a sample of the signal taken prior to the trigger-recognition point on the vertical signal may be displayed. Samples taken after the triggerrecognition point may also be part of the display. This difference is in our favor and what makes random sampling useful. How much time the vertical signal may be sampled ahead of the trigger-recognition point and still be correctly displayed, will be the time between the instant when the vertical signal is sampled and the instant when the timing-ramp signal This selectable but fixed interval of is sampled. time is leadtime. In the 3T2 the leadtime is equal to six-tenths of the selected time position range and amounts to at least six divisions of the ten-division scale except for the 100 ns range.

Let us now consider in detail the functions of the six blocks which are involved with the generation of pretriggers. First of all, notice the lines in Fig. 2-6, identified by  $t_0$ ,  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$ ,  $t_5$  and  $t_6$ . These lines all deliver pulses. The pulse *edges* that we are concerned with occur at instants in time identified as  $t_0$ ,  $t_1$ , etc. In every normal sampling cycle the order of the occurrence of the instants  $t_1$ through  $t_6$  is the same. However, the triggerrecognition point  $t_0$  may occur either before or after time  $t_1$  in any normal cycle. Even though this is so, all pulses actually depend on the generation of trigger-recognition pulses at time  $t_0$ . That is because a pulse edge at time  $t_0$  in one cycle initiates events which always cause a delayed pulse to be generated at time  $t_1$  in the next cycle. See Fig. 2-7.

leadtime

Time  $t_0$  is the trigger-recognition point, the master time-reference point in each sampling cycle. The sequence of events initiated at  $t_0$  set the stage for each subsequent sampling cycle. The pulse edge at time  $t_0$  causes a timing ramp to be initiated, and causes the existing ratemeter-ramp level to be gated into the ratemeter-ramp memory.

Time  $t_1$  occurs when the ratemeter ramp crosses a level introduced to the ratemeter-ramp comparator from the error-correction matrix. The pulse edge at time  $t_1$  causes a slewing ramp to be initiated. Ideally, time  $t_1$  is a stable pretrigger point which occurs well ahead of time  $t_0$  in *that* sampling cycle. In the first sampling cycle no event occurs at  $t_1$ ,  $t_2$  or  $t_3$ .

Time  $t_2$  occurs when a slewing ramp crosses the level introduced to the slewing-ramp comparator from the staircase inverter. The pulse edge at time  $t_2$  is a vertical-signal sampling command and, essentially, is the instant the vertical signal is strobed and sampled.

Time  $t_3$  occurs when a slewing ramp crosses the lower negative offset level which rides on the output from the staircase inverter. It occurs at a fixed time interval following  $t_2$ . The pulse edge at time  $t_3$  is a timing-ramp sampling command that stops the timing ramp in its run down and holds that level as a sample until amplified and stored in the horizontal memory.

Time  $t_4$  occurs at the end of the first part of the holdoff cycle. The pulse beginning at time  $t_4$  and ending at time  $t_5$  gates the amplified, stopped level of the timing ramp into the horizontal memory.

Time  $t_5$  occurs shortly after time  $t_4$  at the middle of the holdoff cycle. The pulse edge at time  $t_5$ resets the timing-ramp generator, the slewing-ramp generator and the ratemeter-ramp generator (which starts over again automatically). The pulse beginning at time  $t_5$  and ending at time  $t_6$  gates into the dot-position difference memory whatever voltage may be applied at that moment from the dot-position differential amplifier. Time  $t_6$  occurs a moment later than  $t_5$  during the last part of the holdoff cycle. The pulse edge at time  $t_6$  causes the staircase generator to advance one step.

ratemeter ramp

Let's look at the ratemeter-ramp generator block (Fig. 2-6). The ratemeter ramp is a relatively slow ramp. It has an excursion which may last 1000 times as long as the time position range and is selected with the same control. Whenever a ratemeter ramp is initiated, as with the generation of a pulse edge at time  $t_5$  from the trigger-holdoff block, the ramp starts a slow rundown. It runs down until the next similar pulse edge at time  $t_5$  emerges from the trigger-holdoff block. At that moment the ratemeter ramp reverts and starts over again at the same slope. The ratemeter-ramp amplitude, therefore, is a function of the time between occurrences of successive pulse edges at time  $t_5$ . In other words, the ramp amplitude is a function of the trigger-recognition rate. Remember, this rate may not be the same as that of the triggering signal if the triggering signal is a high-frequency signal and trigger countdown is occurring.

The ratemeter ramp goes two places, to the ratemeterramp comparator and to the ratemeter-ramp memory. The ratemeter-ramp amplitude at time  $t_0$  is stored in the ratemeter-ramp memory. At time  $t_5$  in every cycle the ratemeter ramp resets and starts down again. The ramp amplitude stored in memory will be an unchanging DC level if the trigger-recognition rate is a very constant frequency. If the frequency decreases, the ramp amplitude increases and the rate level increases in the negative direction. The level out of the ratemeter-ramp memory is mixed with another level in the error-correction matrix and the combination is fed over as a reference level for the ratemeter-ramp comparator.

Let's consider for a moment that the level fed out of the error-correction matrix to the ratemeter-ramp comparator is slightly higher by a fixed amount than the level out of the ratemeter-ramp memory. Such a condition is normal and typical because of the other servo-loop input to the error-correction matrix. When a down-going ratemeter ramp, which is fed into the ratemeter-ramp comparator, reaches this level the leading edge of an output pulse will emerge which initiates a slewing ramp in the slewing-ramp generator. Because the reference level at the input to the ratemeter-ramp comparator was slightly higher than the level out of the ratemeter-ramp memory, the negative-going ratemeter ramp will cross this level sooner than if it ran all the way down to the level that is at the output of the ratemeter-ramp memory. Because the level at the output of the ratemeterramp memory is the level of the ratemeter ramp when last sampled at time  $t_0$ , the pulse which emerges from the ratemeter-ramp comparator will normally occur ahead of each new time  $t_0$ . That pulse is our pretrigger pulse. The pretrigger pulses occur at time  $t_1$  and start the slewing ramps. Remember the pulses generated at time  $t_1$  occur as a result of events in the previous cycle, and in that way can occur prior to time  $t_0$  in any given cycle.

As a slewing ramp runs down it first produces an output pulse at the slewing-ramp comparator, then produces an output pulse at the leadtime comparator. The first pulse causes the vertical signal to be sampled, the second pulse causes the timing ramp to be sampled. With these two samples we have enough information to correctly position one dot on-screen, both vertically and horizontally.

Now if the slewing-ramp comparator and the leadtime comparator did not have changing reference levels fed into them from the staircase inverter, each of the pairs of pulses produced by each slewing ramp crossing the two levels might sample the signal and a timing ramp at nearly the same point each cycle. This condition isn't desirable because we need to sample the vertical signal at all points of interest in order to display all points of interest. So we must have a slewing function. This slewing function follows the same pattern as occurs in the sequential mode of operation. That is, we generate a series of staircase levels which are applied to the slewingramp comparator and these changing reference levels, which step once with every sample, cause us to slew

pretrigger pulse

slewing

across the entire signal and sample all portions of it after enough slewing ramps have occurred. We try, therefore, to sample the vertical signal in exactly the same manner as though we were sampling it in the sequential mode, except we start to slew from a point ahead of the trigger-recognition point.

To help simulate that process, the level out of the staircase generator at any moment, which corresponds in one sense to a particular spot on the horizontal scale, is applied as one input to the dot-position differential amplifier. The other input to the dot-position differential amplifier is the output of the horizontal memory. If a particular sample was placed on the screen at the same horizontal position as the staircase generator would have placed it had we been sampling in the sequential mode, there would be no difference in the voltage from the staircase generator compared to the output voltage from the horizontal memory. If there is no difference in dot position, then there will be no error signal to store in the dot-position difference memory and no error signal level added to or subtracted from the level corresponding to the stored ratemeter-ramp amplitude applied to one input of the error-correction matrix.

Typically, the horizontal position of any one dot may differ radically from the position that dot would have if it had been placed there by the staircase generator. If the position of a dot is further to the right on the screen than it ideally should be, then there will be one polarity of voltage applied to the dot-position difference memory. Ιf the dot is further to the left than it ideally should be, then there will be the opposite voltage applied determination to the dot-position-difference memory. The polarity and the magnitude of the voltage which comes out of the dot-position-difference memory has a direct influence on the DC level which comes out of the error-correction matrix and is applied as a reference level at one input to the ratemeter-ramp A change in the DC level of this comparator. reference input will cause the pretrigger signal to occur earlier or later than it formerly did to minimize the error and repeatedly sample the signal most of the time over the particular region to be displayed on screen. The process is one of

error signal

horizontal dotposition

continually metering and correcting for errors in the estimation of the trigger-recognition rate so as to produce pretriggers at the same rate, and at times  $(t_1)$ , which are consistently early by a nearly constant amount compared to the trigger-recognition point  $(t_0)$ .

blanking