# Digital Concepts

| Α | В | X |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| I | 0 | 0 |

| l |   | ı |

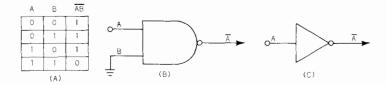

$$X = \overline{\overline{A}} \overline{B} = AB$$

| A | В  | Y |

|---|----|---|

| 0 | 0  | 0 |

| 0 | I  | ١ |

| ı | 0  | 1 |

| 1 | .1 | 1 |

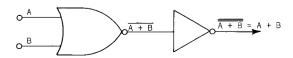

$$Y = \overline{\overline{A}}\overline{\overline{B}} = A+B$$

## OTHER BOOKS IN THIS SERIES:

Circuit Concepts

Power Supply Circuits 062-0888-01

Oscilloscope Cathode-Ray Tubes 062-0852-01

Storage Cathode-Ray Tubes and Circuits 062-0861-01

Television Waveform Processing Circuits 062-0955-00

Digital Concepts 062-1030-00

Spectrum Analyzer Circuits 062-1055-00

Oscilloscope Trigger Circuits 062-1056-00

Sweep Generator Circuits 062-1098-00

Measurement Concepts

Information Display Concepts 062-1005-00

Semiconductor Devices 062-1009-00

Television System Measurements 062-1064-00

Spectrum Analyzer Measurements 062-1070-00

Engine Analysis 062-1074-00

# DIGITAL CONCEPTS

BY LEONARD W. BELL

Significant Contributions

by

JOHN W. SHEPPARD

FIRST EDITION SECOND PRINTING JUNE 1969 062-1030-00 PRICE \$1.00

TEKTRONIX, INC.; 1968 BEAVERTON, OREGON ALL RIGHTS RESERVED

# CONTENTS

| 1 | INTRODUCTION 1                                        |    |

|---|-------------------------------------------------------|----|

| 2 | THE BINARY NUMBER SYSTEM 3                            |    |

| 3 | BOOLEAN ALGEBRA 15                                    |    |

| 4 | NAND GATE, NOR GATE, AND FLIPFLOP                     | 31 |

| 5 | IMPLEMENTING LOGIC FUNCTIONS 47                       |    |

| 6 | IMPLEMENTING LOGIC CIRCUITS USING INTEGRATED CIRCUITS | 71 |

| 7 | COUNTING CIRCUITS 91                                  |    |

| 8 | COUNTER READOUT CIRCUITS 107                          |    |

|   | INDEX 125                                             |    |

#### **FORWARD**

This the first edition of the Tektronix Digital Concepts book uses Negative True Logic when explaining circuits throughout the book. This is due to the fact that most digital instruments designed at Tektronix prior to the publication of this book have had their circuits and logic diagrams explained in terms of Negative True Logic.

This is not meant to imply that Tektronix has standardized on Negative True Logic. There are times when Positive True Logic may be the more natural form to use.

The content of the book is as valid for explaining the concept of one system as for the other.

#### INTRODUCTION

Automated or programmed devices using integrated logic circuits (IC) become more common daily. engineer or technician whose background lies largely with conventional or analog-type circuitry can have difficulty understanding digital diagrams filled with odd-shaped symbols. Most people with an electronics background are trained to use schematic diagrams which require consideration of each individual component and its contribution toward the operation of the circuit. In logic circuitry as implemented today, our point of interest is shifted upward an order of magnitude. Rather than considering each individual bit and piece, entire circuits are supplied in individual packages. It is not necessary to know the exact circuit configuration of the particular device because the device is encapsulated. Consider the Fairchild 914 NAND gate. Within the capsule are six transistors and numerous associated resistors. The only access we have to these transistors and resistors is through the eight pins. Therefore signal-tracing the circuitry within the IC (or chip as it is often called) is impossible. is necessary to understand the relationship between the input and output signals, but no more. cannot repair the 914 we can only replace it as a unit. This is universally true of presently available integrated circuitry.

This Digital Concepts book will help the beginner to approach digital instruments from the standpoint of circuit blocks rather than individual components. We begin by reviewing the concepts of the decimal and binary number systems. We next study the rules of Boolean algebra and its application to the field of digital logic circuitry. We then present the application of the algebra to the design, simplification, and understanding of these circuits.

To the designer, applications of Boolean algebra involve the basic design and simplification of a particular series of functions. He begins with a series of statements of what a circuit is to perform and implements these statements in a logic circuit. Determining a first approximation of the circuit, the designer next applies the principles of Boolean algebra to simplify. After simplification the resulting Boolean equations are translated again into circuitry. Frequently the second design is simpler and therefore less expensive.

The user of the completed instrument has other concerns. For him the circuits are already designed. His major problem is to interpret instrument operation from the diagrams supplied. He is required to understand the sometimes complicated interconnecting of the various IC's to determine the scheme of operation. This is particularly necessary in troubleshooting the complete instrument. digital instruments available today were designed using the principles of Boolean algebra, diagrams supplied use logic symbols. To realize what the symbols mean and gain a finer appreciation for digital techniques, the technician must also be familiar with the basic principles of Boolean algebra. the technician's standpoint, however, the methods of simplifying a device are of secondary importance.

This book concentrates on the interpretation of existing designs, although some of the principles that enter into completing the design are mentioned. Having considered basic principles of Boolean algebra and the basic symbology, we next procede to more complex designs. Finally, selected circuits taken from existing Tektronix digital instruments are analyzed. The book does not explain the overall operation of such instruments, but concentrates on those areas which are common, such as counters and registers.

A thorough study of the book should accelerate the student's understanding of digital instruments.

#### THE BINARY NUMBER SYSTEM

Digital instruments such as the digital voltmeter, the frequency counter, and the analog-to-digital converter may be broken down into hundreds (or thousands) of switching devices. A switch has two stable conditions, "on" and "off." When examining devices containing many switches, the decimal system is unhandy. Since the switch is a two-state device, a counting or numbering system based upon the value two is convenient. Such a numbering system is called the binary number system. Although unfamiliar to the average person, the binary number system is logical and easily learned.

binary number system

decimal number system

In the decimal number system ten symbols are used: 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. A person counting paper clips, for example, and writing down the count, writes 0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

For the tenth clip he has run out of symbols, therefore, he starts again with 0 and places a 1 to the left of the zero indicating that the count has reached 10 one time. The next count is 11, indicating 1 ten + 1 one = 11. When the count reaches twenty, note that the right-hand column begins with 0 again but this time a 2 is written to the left of 0. This indicates that the count has gone to ten a total of two times. The symbol 63 indicates 6 tens + 3 ones. Note that at the count 99, we have again exhausted the symbols so we repeat the change which occurred at ten and write 100 indicating 1 hundred + 0 tens + 0 ones.

Note that the change points are even powers of ten which are indicated  $10^1 = 10$ ;  $10^2 = 100$ ;  $10^3 = 1,000$ ;  $10^4 = 10,000$ , etc. In a written number such as 10,349 we can determine the various powers of 10 which the number represents by the position of the written numbers, as  $1 \times 10^4 + 0 \times 10^3 + 3 \times 10^2 + 4 \times 10^1 + 9 \times 10^0$ .

In the binary numbering system only two symbols are used. Although the symbols are completely arbitrary we use the first two symbols of the Arabic numbering system in order to avoid having to memorize new To see how binary counting works let us again assume a person is to count paper clips and is to write the running total in binary form. He begins by writing 0 indicating that he has not counted yet. He counts the first clip and writes 1. He now has on his paper 0, 1. When he counts the second clip what does he do? In the binary system there are only two symbols, therefore, he resorts to the same method used in the decimal system, he writes a 0 and places a 1 to the left indicating he has counted to two 1 time. At the count of three he writes 11 indicating 1 two + 1 one = three. At the count of four he is again out of symbols so he writes 100 indicating 1 four + 0 twos + 0 ones. At the count of five he writes 101 indicating 1 four + 0 twos + 1 one and so he continues until at the count of seven he writes 111. Again he has used all symbols in all columns so he writes 1000, indicating 1 eight + 0 fours + 0 twos + 0 ones. Look at Fig. 2-1, which shows the binary count along with the same count in decimal form.

Note that the position notation idea is valid for a number in binary form, except that each position is based upon a power of two. For example,  $20_{10}$  is  $10100_2$  (the subscripts are used to indicate the radix being used. The radix of a numbering system is simply the number of symbols that it uses.)

$10100_2$  = 1 sixteen + 0 eights + 1 four + 0 twos + 0 ones which could also be written:  $10100_2$  = 1 x  $2^4$  + 0 x  $2^3$  + 1 x  $2^2$  + 0 x  $2^1$  + 0 x  $2^0$ . (any number to the zero power equals 1)

binary-todecimal conversion In the study of digital circuits it will be necessary sometimes to be able to convert a binary form number to decimal form. With the aid of a power-of-two chart this can be accomplished very easily.

Consider the number 1101. This can be read using the position value of each symbol as  $1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$ . Referring to the table in Fig. 2-1:

13<sub>10</sub> is the number in decimal form.

| DECIMAL | BINARY |

|---------|--------|

| 0       | 0      |

| 1       | 1      |

| 2       | 10     |

| 3       | 11     |

| 4       | 100    |

| 5       | 101    |

| 6       | 110    |

| 7       | 111    |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

| 16      | 10000  |

| 17      | 10001  |

| 18      | 10010  |

| 19      | 10011  |

| 20      | 10100  |

| 21      | 10101  |

| 22      | 10110  |

| 23      | 10111  |

| 24      | 11000  |

| 25      | 11001  |

| 26      | 11010  |

| 27      | 11011  |

| 28      | 11100  |

| 29      | 11101  |

| 30      | 11110  |

| 31      | 11111  |

| 32      | 100000 |

Fig. 2-1. Comparison of binary and decimal numbers.

Comparing the same number in binary and decimal forms shows that the binary form is cumbersome in that it takes many more digits to express a number. Refer back to Fig. 2-1, and notice that  $32_{10}$  takes 6 digits in binary form. Why then do digital instruments use the binary system? Electronic devices and decimal counting are not very compatible. Although circuits can be built to use base-10 values, the circuitry is quite complex and involves the use of ten different voltage levels.

Since active electronic devices can operate as switche two-voltage-level circuits are easily made. In addition these devices can be made to switch at rates of millions per second. It is simplicity and speed which makes the use of the binary system practical in electronics.

The operation or programming of digital instruments often requires that very long binary numbers be used. For convenience, certain terms are used to identify parts of these numbers. The term bit is used to identify a binary digit. (Bit is derived from BInary digit.) The term character is a group of bits. The term word refers to the total number of bits required by a particular instrument.

For example, the Tektronix Type 240 Program Control Unit is designed to process a binary number which is 192 bits long. The complete number is called a word and the Type 240 is said to use a 192-bit word. Because of the extreme length of the word, for convenience it is divided into groups of 4 bits. Each 4-bit group is called a character. Hence the Type 240 is also said to use a 48-character word.

Digital instruments use data and instructions in binary form. Humans, however, use decimal numbers and alphabetic letters. Therefore, various codes have been designed to facilitate communication with digital devices. These codes are formed by taking groups of bits and assigning each unique combination a particular letter, symbol or decimal number. There are many codes in existence, only a few of which will be considered here.

Some binary codes use a number weighting scheme. The simplest code called pure binary uses the exact position value of each binary digit as the weight

bit

word

character

binary codes

| DECIMAL | BCD  |

|---------|------|

| 0       | 0000 |

| 1       | 0001 |

| 2       | 0010 |

| 3       | 0011 |

| 4       | 0100 |

| 5       | 0101 |

| 6       | 0110 |

| 7       | 0111 |

| 8       | 1000 |

| 9       | 1001 |

Fig. 2-2. 8, 4, 2, 1 BCD code.

value. For example, the number  $15_{10}$  is written in binary as 1111. This number is read as  $1 \times 8 + 1 \times 4 + 1 \times 2 + 1 \times 1 = 15$ . Pure binary (also called hexadecimal) is said to have an 8, 4, 2, 1 weight. Many other weight schemes are used. Examples include 7, 4, 2, 1; 4, 2, 2', 1 and 6, 3, 2, 1, 0 (5 bits).

Other codes are unweighted which means that the decimal equivalent of the binary number is determined only by an arbitrarily assigned value. An example of this type is the Excess-3 code.

binarycoded decimal The simplest code to understand is the binary-coded decimal, which is abbreviated BCD. The BCD code uses four binary bits per character and a weight scheme of 8, 4, 2, 1. Each character has the decimal value that the four bits represent. The code is shown in Fig. 2-2. Note that the decimal equivalent is simply the binary number expressed in decimal form.

A 4-bit number can have values from zero to fifteen. Ordinarily, however, in the BCD code only enough combinations are used to express all 10 decimal symbols. In order to express decimal numbers greater than 9, a separate four-bit group is used for each number. For example:  $82_{10}$  is 1000 0010 in BCD,  $370_{10}$  is 0011 0111 0000,  $591_{10}$  is 0101 1001 0001.

Note that the BCD system requires many bits to express a decimal number.

To return to the Tektronix Type 240 Program Control Unit, recall that the 192-bit word is divided into 4-bit characters. Each 4-bit character is further simplified by giving each character its decimal value in a specific case. Since each 4-bit character in this situation may contain any of the sixteen possible combinations of bits, a character in the Type 240 may have a value in excess of nine. Fig. 2-3 shows all possible values.

| DECIMAL | CHARACTER |

|---------|-----------|

| 0       | 0000      |

| 1       | 0001      |

| 2       | 0010      |

| 3       | 0011      |

| 4       | 0100      |

| 5       | 0101      |

| 6       | 0110      |

| 7       | 0111      |

| 8       | 1000      |

| 9       | 1001      |

| 10      | 1010      |

| 11      | 1011      |

| 12      | 1100      |

| 13      | 1101      |

| 14      | 1110      |

| 15      | 1111      |

Fig. 2-3. Pure binary 8, 4, 2, 1.

| DECIMAL | 8,4,2,1 CODE | 4,2,2',1 CODE | EXCESS-3 CODE |

|---------|--------------|---------------|---------------|

| 0       | 0000         | 0000          | 0011          |

| 1       | 0001         | 0001          | 0100          |

| 2       | 0010         | 0010          | 0101          |

| 3       | 0011         | 0011          | 0110          |

| 4       | 0100         | 1000          | 0111          |

| 5       | 0101         | 0111          | 1000          |

| 6       | 0110         | 1100          | 1001          |

| 7       | 0111         | 1101          | 1010          |

| 8       | 1000         | 1110          | 1011          |

| 9       | 1001         | 1111          | 1100          |

Fig. 2-4. Comparison of some BCD codes.

This coding is similar to BCD but includes combinations which are forbidden in the BCD system. To reduce confusion, care should be taken not to call the Type 240 character system "BCD." It should instead be called pure binary 8, 4, 2, 1.

4,2,2',1 code Excess-3 code

Other common codes are shown in Fig. 2-4; the 8, 4, 2, 1 BCD code is included for comparison. The 4, 2, 2', 1 code is used in the Tektronix Type 6R1A. The Excess-3 code is formed by adding binary 3 to the BCD number. For example,  $0_{10}$  in BCD is 0000; by adding  $3_2$  the sum is 0000 + 0011 = 0011. Each Excess-3 number is formed by the same process. The Excess-3 code has some advantages over BCD when performing arithmetic subtraction in computers. 1

<sup>&</sup>lt;sup>1</sup>T.C. Bartee, *Digital Computer Fundamentals*, (New York: McGraw-Hill, 1966), pp 56-7.

ASCII Code

In computers designed for business data processing it is necessary to work with alphabetic characters as well as decimal numeric characters. alphanumeric code must contain more than 4 bits since 26 letters plus 10 digits must be encoded. means that at least 6 bits must be used since 5 bits contain only 32 unique combinations. A six-bit code has often been used. In the past each manufacturer has selected or created codes to suit his particular devices. In an attempt to standardize, the American Standards Association approved a new 7-bit code in 1964. This code is known as ASCII (American Standard Code for Information Interchange). (For verbal communication the letters are phoneticized az-key.) Fig. 2-5 shows the entire code. Seven bits are used so that punctuation marks, symbols, plus telephone and teletype abbreviations can be included.

Examine the column headed by "011." The ten decimal digits are listed in order. The chart is decoded by using the four digits shown on the left and adding the three digits at the head of the column. Examples: 4 = 011 0100 and 7 = 011 0111. The last four binary digits express the decimal number in 8, 4, 2, 1 BCD code. Because of this, the ASCII code is compatible with instruments designed to use the 8, 4, 2, 1 BCD code. The Type 240 Program Control Unit can be addressed by the ASCII code.

| Stane |  |  |

|-------|--|--|

|       |  |  |

| b7      |         | Ξ                   | =              |    | =     | 000 | 001 | 010  | 01, | 100 | 101 | 1 0 | 1,  |

|---------|---------|---------------------|----------------|----|-------|-----|-----|------|-----|-----|-----|-----|-----|

| B 1 1 5 | Ь4<br>1 | Ь <sub>3</sub><br>і | b <sub>2</sub> | b) | ROW I | 0   | 1   | 2    | 3   | 4   | 5   | 6   | 7   |

|         | 0       | 0                   | 0              | 0  | 0     | NUL | DLE | SP   | 0   |     | Р   | ,   | Р   |

|         | 0       | 0                   | 0              | 1  | 1     | SOH | DC1 |      | 1   | Α   | Q   | a   | q   |

|         | 0       | 0                   | 1              | 0  | 2     | STX | DC2 |      | 2   | В   | R   | ь   | r   |

|         | 0       | 0                   | 1              | 1  | 3     | ETX | DC3 | #    | 3   | С   | S   | С   | s   |

|         | 0       | 1                   | 0              | 0  | 4     | EOT | DC4 | _ \$ | 4   | _ D | T   | ď   | 1   |

|         | 0       | 1                   | 0              | 1  | 5     | ENQ | NAK | %    | 5   | E   | U   | e   | U   |

|         | 0       | 1                   | 1              | 0  | 6     | ACK | SYN | _ &  | 6   | F   | ٧   | f   | ٧   |

|         | 0       | 1                   | 1              | 1  | 7     | 8EL | ETB |      | 7   | G   | ₩   | g   | w   |

|         | 1       | 0                   | 0              | 0  | 8     | BS  | CAN | (    | 8   | Н   | Х   | h   | х   |

|         | 1       | 0                   | 0              | 1  | 9     | HT  | EM  | )    | 9   | - 1 | Y   | i   | у   |

|         | 1       | 0                   | 1              | 0  | 10    | LF  | SUB | *    | . : | J   | Z   | j   | z   |

|         | 1       | 0                   | 1              | 1  | 11    | VT  | ESC |      | ;   | К   | ]   | k   | - ( |

|         | 1       | 1                   | 0              | 0  | 12    | FF  | FS  | _ ,  | <   | L   | 1   | 1   | - 1 |

|         | 1       | 1                   | 0              | 1  | 13    | CR  | GS  |      | -   | М   |     | m   | }   |

|         | 1       | 1                   | 1              | 0  | 14    | SO  | RS  | _ ·  | >   | N   | ^   | n   | ~   |

|         | 1       | 1                   | 1              | 1  | 15    | SI  | US  | /    | ?   | 0   |     | 0   | DEL |

## Legend

| €   | ontrol Characters                              | Graphic Characters |        |                                                         |  |

|-----|------------------------------------------------|--------------------|--------|---------------------------------------------------------|--|

| NUL | Null                                           | Column/Row         | Symbol | Name                                                    |  |

| Юн  | Start of Heading (CC)                          | 2/0                | SP     | Space (Normally Non-Printing)                           |  |

| STX | Start of Text (CC)                             | 2/1                | :      | Exclamation Point                                       |  |

| ETX | End of Text (CC)                               | 2/2                | 4      | Quotation Marks (Diaeresis )                            |  |

| EOT | End of Transmission (CC)                       | 2/3                | #      | Number Sign                                             |  |

| ENQ | Enquiry (CC)                                   | 2/4                | 8      | Dollar Sign                                             |  |

| ACK | Acknowledge (CC)                               | 2/5                | %      | Percent                                                 |  |

| ΒΈL | Bell (audible or attention signal)             | 2/6                | č.     | Ampersand                                               |  |

| BS  | Backspace (FE)                                 | 2/7                | ,      | Apostrophe (Closing Single Quotation Mark; Acute Accent |  |

| нт  | Horizontal Tabulation (punched card skip) (FE) | 2/8                | (      | Opening Parenthesis                                     |  |

| F   | Line Feed (FE)                                 | 2/9                | )      | Closing Parenthesis                                     |  |

| νT  | Vertical Tabulation (FE)                       | 2/10               | *      | Asterisk                                                |  |

| FF  | Form Feed (FE)                                 | 2/11               | +      | Plus                                                    |  |

| CR  | Carriage Return (FE)                           | 2/12               |        | Comma (Cedilla )                                        |  |

| 50  | Shift Out                                      | 2/13               | -      | Hyphen (Minus)                                          |  |

| 51  | Shift In                                       | 2/14               |        | Period (Decimal Point)                                  |  |

| DLE | Data Link Escape (CC)                          | 2/15               | 1      | Slant                                                   |  |

|     | Device Control 1                               | 3/10               | :      | Colon                                                   |  |

|     | Device Control 2                               | 3/11               |        | Semicolon                                               |  |

|     | Device Control 3                               | 3/12               | <      | Less Than                                               |  |

|     | Device Control 4 (Stop)                        | 3/13               | =      | Equals                                                  |  |

|     | Negative Acknowledge (CC)                      | 3/14               | >      | Greater Than                                            |  |

|     | Synchronous Idle (CC)                          | 3/15               | ?      | Question Mark                                           |  |

| ETB | End of Transmission Block (CC)                 | 4/0                | @      | Commercial At                                           |  |

|     | Cancel                                         | 5/11               | 1      | Opening Bracket                                         |  |

| EM  | End of Medium                                  | 5/12               | \      | Reverse Slant                                           |  |

| SUB | Substitute                                     | 5/13               | 1      | Closing Bracket                                         |  |

| ESC | Escape                                         | 5/14               | ^      | Circumflex                                              |  |

| FS  | File Separator (IS)                            | 5/15               | _      | Underline                                               |  |

| GS  | Group Separator (IS)                           | 6/0                |        | Grave Accent (Opening Single Quotation Mark)            |  |

| RS  | Record Separator (IS)                          | 7/11               | 1      | Opening Brace                                           |  |

| us  | Unit Separator (IS)                            | 7/12               | 1      | Vertical Line                                           |  |

| DEL | Delete                                         | 7/13               | 1      | Closing Brace                                           |  |

|     | Defect.                                        | 7/14               | ~      | Overline (Tilde ; General Accent )                      |  |

Fig. 2-5. USA Standard Code for Information Interchange.

octal system Another common numbering system used within the digital area is the octal system. The octal system is based on the number 8. Eight digits are used, 0, 1, 2, 3, 4, 5, 6, and 7. The rules are basically the same as for binary or decimal except that position is based upon powers of 8. Fig. 2-6 shows decimal and octal equivalents.

Note that the octal system requires more digits than the decimal system to express a number but not nearly as many as the binary system. The octal system converts readily to binary because the basis of the octal system 8 is also an even power of two, i.e.,  $8 = 2^3$ .

Caution must be used in verbally naming numbers expressed in octal and other numbering systems. For example,  $10_8$  is *not* pronounced ten because  $10_8$  = 8 and should be called "eight" verbally.

The octal numbering system is used by several digital-equipment manufacturers as a means of expressing binary numbers by using fewer symbols. This system could be called "octal-coded binary." For example, the Digital Equipment Corporation makes the PDP-8 family of computers. These computers operate with a 12-bit word. A word might be 110 011 001 111. To reproduce this word would of course require writing 12 digits. By arranging the word bits in groups of three bits each, and converting each group to its equivalent in octal code, the same number can be written using 4 octal digits. The process is shown in Fig. 2-7.

Thus the 12-bit word 110 011 001 111 can be written  $6317_8$ . This system is convenient because a group of 3 bits can have only 8 possible values. With practice the numbers from  $000_2$  to  $111_2$  can be memorized and the binary-to-octal conversion can be performed mentally.

This is primarily used as a shorthand method of writing binary numbers. A computer program might consist of several hundred 12-bit words, each one of which must be recorded. Think how much writing can be saved by using the octal-coded binary method of condensing the binary word! Seldom will the octal numbering system be used for arithmetic operation; it is the positional notation which is of value here.

| DECIMAL | OCTAL |

|---------|-------|

| 0       | 0     |

| 1       | 1     |

| 2       | 2     |

| 3       | 3     |

| 4       | 4     |

| 5       | 5     |

| 6       | 6     |

| 7       | 7     |

| 8       | 10    |

| 9       | 11    |

| 10      | 12    |

| 11      | 13    |

| 12      | 14    |

| 13      | 15    |

| 14      | 16    |

| 15      | 17    |

| 16      | 20    |

| 17      | 21    |

| 18      | 22    |

| •       |       |

| •       |       |

|         |       |

| 64      | 100   |

| 65      | 101   |

|         |       |

|         | • .   |

|         |       |

Fig. 2-6. Octal numbering system.

| OCTAL  | 6   | 3   | 1   | 7   |

|--------|-----|-----|-----|-----|

| BINARY | 110 | 011 | 001 | 111 |

Fig. 2-7. Octal-to-binary conversion.

# BOOLEAN ALGEBRA

The engineer's understanding of digital circuits and digital instruments requires an understanding of a different form of algebra from the algebra taught in high school. Although unfamiliar to many, this algebra is logical and easily understood. Boolean algebra, universally used by digital instrument designers, differs from conventional algebra in that it uses the binary numbering system. Boolean algebra contains methods which are specially adaptable to digital circuitry and makes the design of such circuitry much easier. Conventional algebra is best for everyday use, but in the digital area, it may needlessly complicate circuit design.

There is a twofold advantage in using Boolean algebra in the digital field. First, Boolean algebra permits the engineer to design a circuit or instrument in a logical manner. Secondly, it allows another engineer or technician to easily understand and follow the operation of the device.

two-valued logic Boolean algebra has been called the algebra of two-valued logic. An English mathematician, George Boole, published a work in 1854 titled, An Investigation of the Laws of Thought. This book contains one of the earliest attempts to discuss logic in a mathematical sense using special notation similar to mathematical symbols.

Boolean algebra remained almost forgotten until 1938 when Claude Shannon, a research assistant at MIT, published a thesis titled, "A Symbolic Analysis of Relay and Switching Circuits." The paper presented a method for representing switching circuitry by a set of mathematical expressions analogous to the expressions of Boolean algebra. The techniques developed in Shannon's paper have been improved until today they are used in all parts of digital circuit design. The economy of reducing circuitry to mathematical expressions and simplifying by mathematical operations permits the design of even the most complex modern computers.

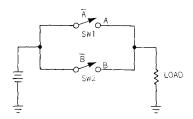

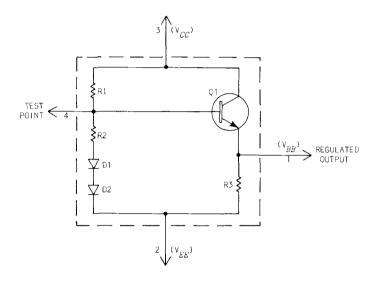

Fig. 3-1.

Boolean algebra is a method of manipulating deductive logic. It recognizes only two possible values for a statement. A statement is either entirely true or entirely false. There are no halfway conditions. A statement which is not true must therefore be false. These premises allow the algebra to be used to represent the conditions found in electrical switching circuitry. Consider the switch of Fig. 3-1. switch is either open or closed. It has no other possible conditions. By applying the basic premise of Boolean algebra we can define the closed switch as a "true" condition and the open switch as a "false" condition. The switch, when not open, must be closed. If not closed it is open. This parallels the Boolean logic. The closed condition could be called the false state and the open condition a true state, without ambiguity. By defining the conditions of a two-state device in Boolean terms, the symbology of the algebra becomes usable. Note the switch of Fig. 3-1 can also itself represent various electronic elements such as transistors, diodes, and vacuum tubes operated in switched modes.

symbology

Boolean algebra has numerous theorems; however, only a few need be examined here. Letters are used to represent quantities. Letters close to the beginning of the alphabet are used to represent variable values and letters close to the end of the alphabet represent unknown quantities.

NOT

Consider the circuit of Fig. 3-2. We represent the condition of switch SWI by the letter A if the switch is closed and by  $\bar{\rm A}$  if the switch is open. The bar over A indicates the "false" state of the switch where false indicates the open condition. An expression with the bar is read aloud by saying for  $\bar{\rm A}$ , "not A." It follows therefore, that the expression A indicates, by the absence of the bar, that the switch is in a closed or true state. Throughout Boolean algebra this convention is followed.

Fig. 3-2.

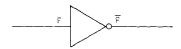

inverter

The not symbol is used to represent a very common circuit function which is the inverter. A signal can be inverted by a transformer, amplifier, or by various other means. Assume a two-valued signal is assigned the letter F. If the signal is inverted by a circuit the value of F must also be inverted. Symbolically  $\overline{F}$  is placed at the output. The symbol for an inverter presently used by Tektronix on logic diagrams is shown in Fig. 3-3.

Considering again Fig. 3-2, we can represent the condition of switch SW2 with the letter B. Further, we can describe the presence or absence of voltage across the load by the letters T (true) or F (false). Thus, T means voltage is present and F means voltage is not present. A Boolean algebra equation may now be written which describes all possible combinations of the switches SW1 and SW2 and whether or not voltage appears across the load. The equation is A + B = X, where X represents a voltage across the load.

Fig. 3-3. Inverter symbol.

| Α   | В | X |  |  |

|-----|---|---|--|--|

| 0   | 0 | 0 |  |  |

| 0   | 1 | 1 |  |  |

| 1   | 0 | 1 |  |  |

| 1   | 1 | 1 |  |  |

| (B) |   |   |  |  |

Fig. 3-4. OR function truth tables.

0R

Reading aloud the reader should state, "A OR B equals X." The symbol "+" is read as "OR" in Boolean algebra, not as "plus." Literally, the equation states, "If either A OR B (or both) is true, then X is true." To properly examine this equation requires the use of a table listing all possible combinations of A and B. Such a table is easily constructed. See Fig. 3-4A.

truth table This table shows that there are four possible combinations for the variables A and B. It follows that in a different equation with three variables there would be eight combinations, and with four variables sixteen combinations, i.e., the number of combinations for 2-valued variables is  $2^n$ , where n is the number of different variables. Note that X is true for all conditions of A and B except where A and B are both false (switches SWl and SW2 open). The truth table is easier to construct and interpret by using the binary number symbols 1 and 0, as in Fig. 3-4B. In this table wherever a variable is true a 1 is placed, wherever a variable is false, a 0 is placed.

The above discussion describes a Boolean OR function. For the purpose of simplifying diagrams wherever a circuit appears which could perform an OR function, the schematic may be replaced by the OR-gate symbol. The presently used symbol is shown in Fig. 3-5A. Three variables are shown. The distinctive shape means the OR function. Fig. 3-5B shows the Boolean equation for the OR gate.

One of the many possible circuits which operates as an OR gate is shown in Fig. 3-5C. To realize how this circuit functions, let us define two voltage levels. A voltage level of +10 V is defined as a logical 0 in this circuit. A ground level (0 V) is a logical 1.

Fig. 3-5. OR functions.

The absolute voltage level assigned to logical 1 is negative with respect to the voltage level assigned to logical zero. This is an example of negative logic. The exact voltage levels could be any values desired, but if the more negative of the two represents 1 then the logic is negative.

The reverse case is possible and often used. If, for example, +10 V was logical 1 and zero volts logical 0 the circuit would be termed a "positive logic" circuit. Note, however, that the circuit of Fig. 3-5C is not a positive logic OR gate. Study of the circuit shows that if A or B or C were at 0 V then the output Y would also be at 0 V, and therefore logically true (1) as defined above.

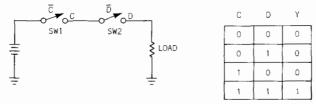

Another important Boolean algebra function is called the AND function. Fig. 3-6 illustrates a circuit which will help one understand the concept of the AND function.

Note that unless switch SW1 and SW2 are closed, no voltage is delivered to the load. If we assign symbols, letting C stand for switch SW1, D stand for switch SW2, and Y stand for presence of output across the load, then a Boolean equation for the circuit may be written  $C \cdot D = Y$ . Note the use of the symbol which means "multiply by" in conventional algebra. In Boolean the " $\cdot$ " means "AND."

Fig. 3-6. AND function.

(B)

negative logic

AND

The equation is read aloud as "if C is true AND D is true, then Y is true." Often an expression omits the dot entirely but its presence is understood; for example, BEFGH would mean B AND E AND F AND G AND H.

Fig. 3-6B illustrates the truth table for the circuit of Fig. 3-6A. Note that the only time the output is true is when the inputs are all true.

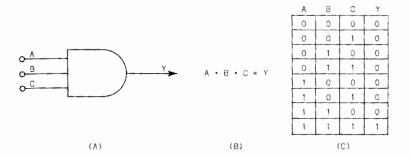

Fig. 3-7A shows the symbol for an AND gate as found on logic diagrams. Fig. 3-7B shows the equation for the gate and Fig. 3-7C shows the truth table for the example. Note again that Y is true only when A and B and C are all true.

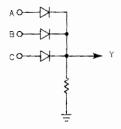

An example of a circuit which displays the AND function is shown in Fig. 3-8. This is an AND gate for negative logic. If any one of the inputs A, B, or C is false (at +10 V), output Y will be false. Only if A·B·C are true (0 V) will Y be true.

Fig. 3-5C and 3-8 are examples of OR and AND gates. There are numerous other ways of building circuits and devices to perform these functions. The principle methods will be treated in a later chapter.

positive logic As an experiment let us re-examine the circuit of Fig. 3-8, but this time with positive logic. We define +10 V as the true level and 0 V as the false level. If +10 V is now the true level then Y will be at +10 V if A or B or C (or any combination of A, B, C) is at 10 V. The truth table inverts the values of Fig. 3-7C.

Constructing a new truth table as in Fig. 3-9, it is apparent the circuit is now an OR gate. Thus, a negative logic AND gate is a positive logic OR gate. At this time, examine Fig. 3-5C and you will find that the circuit is a positive logic AND gate. Thus, depending on the logic chosen for a particular device, the gates are dual in nature. Notice that once the logic levels are chosen this duality vanishes.

Fig. 3-7. Three-variable AND function.

Fig. 3-8. AND gate.

| Α | В | С | Y |

|---|---|---|---|

| 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | i | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 0 |

Fig. 3-9. OR-function truth table.

| A + A = A                                                    | 3.1  |

|--------------------------------------------------------------|------|

| A • A = A                                                    | 3.2  |

| A + 1 = 1                                                    | 3.3  |

| A • 1 = A                                                    | 3.4  |

| A + O = A                                                    | 3.5  |

| A • 0 = 0                                                    | 3.6  |

| $A + \overline{A} = 1$                                       | 3.7  |

| $A \cdot \overline{A} = 0$                                   | 3.8  |

| $\overline{\overline{A}} = A$                                | 3.9  |

| A + AB = A                                                   | 3.10 |

| A (A + B) = A                                                | 3.11 |

| $\overline{A + B} = \overline{A} \overline{B}$               | 3.12 |

| $\overline{AB} = \overline{A} + \overline{B}$                | 3.13 |

| $A(\overline{A} + B) = AB$                                   | 3.14 |

| $A + \widehat{AB} = A + B$                                   | 3.15 |

| $\overline{A} + AB = \overline{A} + B$                       | 3.16 |

| $\overline{A} + A\overline{B} = \overline{A} + \overline{B}$ | 3.17 |

Table 3-1. Useful Boolean algebra theorems.

Boolean algebra is the tool which enables the engineer to reduce circuitry to mathematical equations and then to simplify these equations. Having studied some of the Boolean algebra functions and examined the circuit implementation of these functions, we next consider some of the theorems and postulates of Boolean algebra. Some of these postulates are exactly the same as in ordinary algebra. Some, however, are exclusive to Boolean algebra. Table 3-1 shows a list of some useful Boolean algebra theorems. Some of the theorems can be seen to be true by inspection, some however, require proof. We shall prove several of the theorems.

Boolean theorems

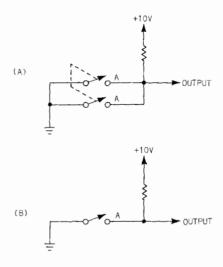

The proof may be accomplished by several different methods. One method uses the truth table, another proves the theorem in mathematical form by applying previously proven algebraic theorems to simplify the mathematical equations. A third method implements the Boolean function in an actual circuit and is simplified by inspection. We shall give examples of all of these methods. Fig. 3-10A shows a circuit which implements Theorem 3.1: A OR A = A. Since the quantity A is to be OR'd with itself, A is represented as a ganged switch. Whenever the switch is closed, we can assume A is true, whenever the switch is open, we can assume it is false. The extra contact on the switch is redundant.

Fig. 3-10.

Therefore, the expression and the circuit could be simplified to a single switch labeled A as in Fig. 3-10B.

Theorem 3.10 will be proven by the use of a truth table. See Fig. 3-11. Since the theorem involves two variables, A and B, the figure lists all four combinations of values that A and B can assume. The values for the term AB are shown in Fig. 3-11B. In Fig. 3-11C we combine the values of A OR'd with the quantity of A AND B. In Fig. 3-11D we find the value of the expression A OR the quantity A AND B is exactly the same as the value of A alone. Therefore, when an expression of the form A + (A·B) appears in an equation, it can be replaced solely by the quantity A.

Theorem 3.11 is proved mathematically:

| A (A + B) | = | A | Theorem 3.11 |

|-----------|---|---|--------------|

| AA + AB   | = | A | Multiply     |

| A + AB    | = | A | By 3.2       |

| A         | = | A | By 3.10      |

DeMorgan's theorems The proof of the rest of the theorems is left as an exercise for the reader. Pay special attention to theorems 3.12 and 3.13 which are known as DeMorgan's theorems. These theorems form the basis for NAND and NOR operations described in Chapter 4.

The engineer may be presented with digital circuit problems in several different forms. One, he may be given a series of logical statements which may be translated into actual circuitry. Two, he may desire to implement a truth table by actual circuitry. Three, he may be given a logic diagram representing a Boolean algebra function and, four, he may be presented with the expression in mathematical terms. In all cases he should be aware of the methods by which one form can be changed to any other. As an example, supposing the problem is to implement the following logical statement. "A room with two doors is to have a central light installed with switches accessible to each door, either one of which can turn the light either on or off." Let the letter A represent the switch by one door, and the B represent the switch by the other door. Let the letter L stand for the lamp. We first construct the truth table. See Fig. 3-12. Although the choice is entirely arbitrary we assume that when a switch is closed it has a logical value of 1 and when opened it has the logical value of 0.

Fig. 3-12. Exclusive-OR truth table.

When A is zero and B is zero the lamp will be off -we assign this condition a logical value of zero.

In order for either switch to control the lamp, if

A or B changes states, the lamp must go on. Therefore,

when A is zero and B is one L must have the value of

one and when A is one and B is zero, L must also have

a value of one. Finally, when A and B are both one

the lamp must be off. The next problem is to write

a Boolean algebra expression for the truth table.

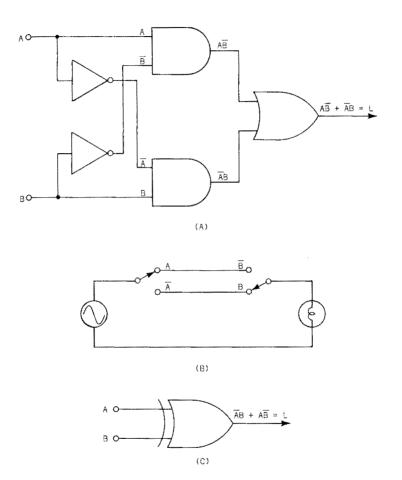

L is to be one for two possible conditions; when A is zero and B is one and also when A is one and B is zero. When two quantities are AND'd together, they must be both equal to one for the result to be one. (Theorem 3.2). In this case we indicate A as zero, however, its complement  $\overline{A}$  would have a value of one when A is zero. Therefore, we write:  $\overline{AB}$ . Similarly we write  $\overline{AB}$ . L is 1 for either one OR the other combination. The complete equation is  $\overline{AB} + \overline{AB} = L$ .

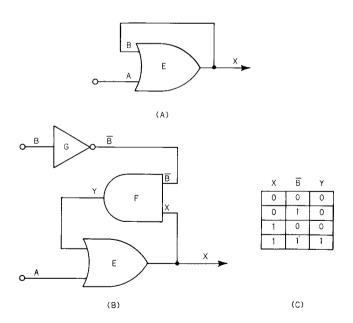

Inspection of the equation shows that it cannot be simplified using any of the theorems in Table 3-1. Next, we implement the equation in a logic diagram. Wherever two terms are ANDed together we use the symbol for an AND gate; wherever the two terms are OR'd together, we use the symbol for an OR gate. The complete diagram is shown in Fig. 3-13A. Inverters are used to generate the negated values of any one of the variables when it is required.

In Fig. 3-13B we show the final circuit which uses switches to implement the logic functions. By the use of single-pole double-throw switches we generate both the true and negated value for a particular variable.

Re-examining Fig. 3-13A, note that L is true if either A or B is true, but not when both are true. This particular combination is so useful that it has been given a special name and a special symbol. The implementing circuit is called an "Exclusive OR" gate. The symbol is shown in Fig. 3-13C which diagrams the lamp problem using the Exclusive OR. The problem could be diagrammed as in Fig. 3-13A or 3-13C; however, the latter diagram is the more convenient.

Fig. 3-13. Exclusive-OR operations.

Fig. 3-14. Simplification of complex logic diagrams.

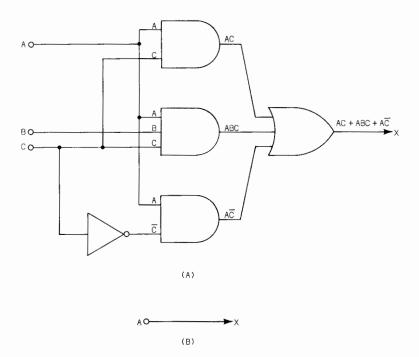

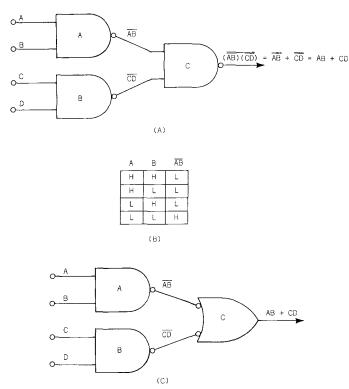

Fig. 3-14A shows another type of problem that may be encountered. The engineer is presented with an accomplished logic diagram. His task is to reduce this diagram to its Boolean algebraic equivalent. By starting at the input and carefully labeling each line, noting also where negation or inversion has taken place, the function may be completely derived from the diagram. The final equation is shown at the output. Examining the equation shows that the equation can be simplified as follows:

AC + ABC +

$$\overline{AC}$$

= X

$$A(C + \overline{C}) + ABC = X \quad \text{Factoring and rearranging terms.}$$

$$A(1) + ABC = X \quad \text{By 3.7}$$

$$A + ABC = X \quad \text{By 3.4}$$

$$A = X \quad \text{By 3.10}$$

The simplified equation shows that the function reduces to a straight-wire connection (Fig. 3-14B) from A to X eliminating all other gates and connections.

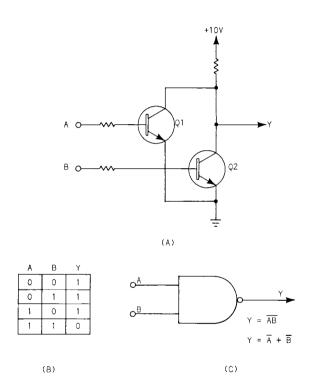

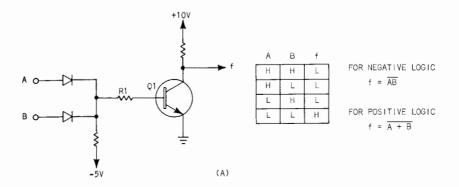

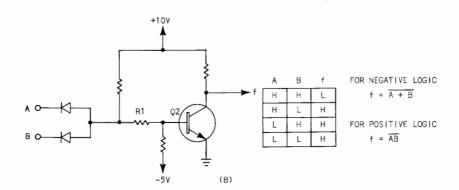

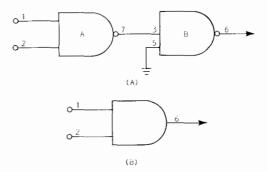

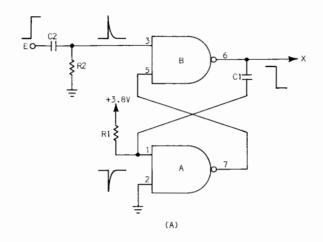

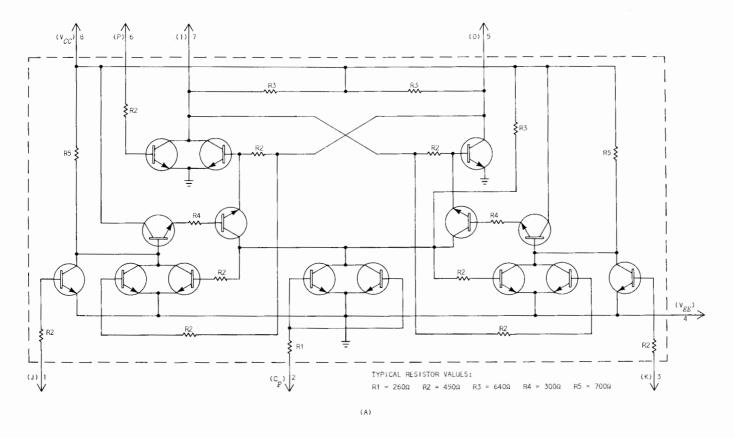

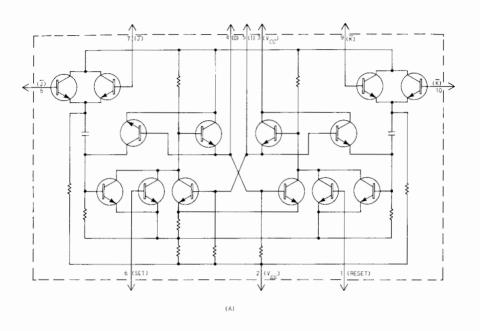

Fig. 4-1. NAND functions.

4

## NAND GATE, NOR GATE, AND FLIPFLOP

When the design engineer tries to implement a Boolean algebra function he may use any common switching device, including the transistor and vacuum tube. When operated in common-emitter mode, the transistor acts as an inverter. Thus, when a transistor is used to implement a logic function; the output of the transistor, if taken at the collector, represents the inversion of the input operation. This means that when constructing an AND gate using a transistor, often the output represents the inversion of an AND gate.

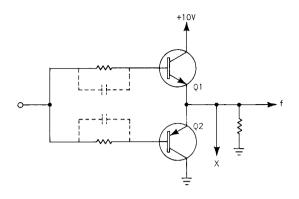

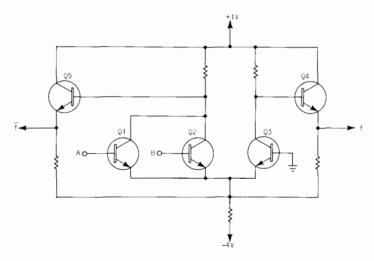

In Fig. 4-1A we show a two-input digital gate, consisting of two NPN transistors Q1 and Q2. In a negative logic system, when inputs A and B are true they are 0 V. In this condition both transistors are off. If they are both off, the output level is +10 V, the false level. Examination of the truth table for an AND gate shows that the output is 0 or false for any combination of inputs A and B except when both are true. Referring to Fig. 4-1A again, if both transistors are off, which occurs only when A and B are true, Y is false. For all other conditions, one or the other or both of the transistors is on because its base is at the false or positive level. With either transistor on, Y is equal to 0 V, the true level. The Y column is the inverse of an AND gate output.

NAND

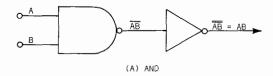

This type of gate is known as a negated AND gate which is shortened to NAND gate. The symbol for a NAND gate appears in Fig. 4-1C. The basic shape of the gate identifies it as an AND function. The circle at the output of the gate means that the signal is logically *inverted* at the point where the circle appears. The Boolean algebra expression for the NAND GATE is written as  $Y = \overline{AB}$ . By DeMorgan's theorem (3.13) this expression can also be written as  $Y = \overline{A} + \overline{B}$ . Note that in one form of the equation, the AND function is indicated, in the other form of the equation the OR function is indicated.

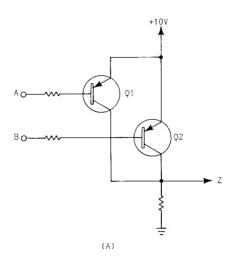

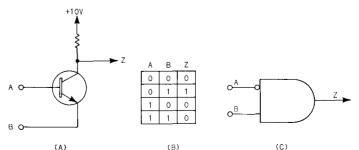

Fig. 4-2. NOR functions.

Fig. 4-2A shows a digital logic circuit using two PNP transistors. In negative logic system when inputs A or B are made true, the base of the appropriate transistor is pulled negative with respect to the emitter which turns the transistor on. A truth table for this gate is shown in Fig. 4-2B. Output Z is true only when both transistors are not conducting. Both transistors are off only when A and B are both false. This result is equivalent to taking the output of an OR gate and negating it. The circuit is therefore referred to as a negated OR gate or NOR gate. The symbol for a NOR gate is shown in Fig. 4-2C. The basic shape of the gate indicates an OR function.

The presence of a circle at the output indicates logic inversion at that point. An equation for a NOR gate is Z =  $\overline{A+B}$ . By DeMorgan's Theorem (3.12) this expression is also equivalent to Z =  $\overline{A}$   $\overline{B}$ . Thus, in the NOR gate as in the NAND gate both OR and AND functions can be implemented. Neither the NAND gate nor the NOR gate are restricted to two input configurations. NAND or NOR gate IC's are available with up to five inputs.

The question is frequently asked as to why most commercially available digital integrated-circuit gates are of the NAND or NOR variety. The answer is found by applying DeMorgan's theorem to NAND and NOR functions. As mentioned previously DeMorgan's theorem shows that in either the NOR or the NAND gate, both AND and OR functions are indicated.

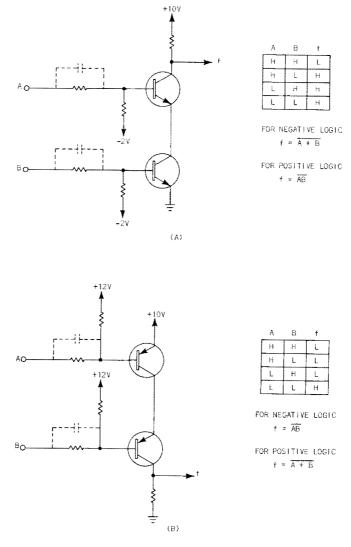

NAND or NOR as AND or OR

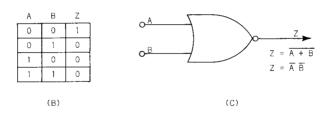

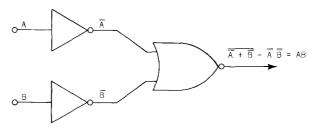

A manufacturer producing integrated-circuit chips can manufacture a single type of gate, either NAND or NOR type, thus simplifying his own inventory and production problems. The user of this single type of gate can implement any kind of indicated operation AND/OR strictly by the use of NAND or NOR gates. To illustrate this principle let us re-examine Theorem 3.12 which reads:  $\overline{A} + \overline{B} = \overline{A} \ \overline{B}$ . See Fig. 4-3. The output of the gate is  $\overline{A} + \overline{B}$  which equals  $\overline{A} \ \overline{B}$ . By applying Theorem 3.9,  $\overline{A} \ \overline{B} = AB$ . By inverting logic levels before the NOR gate, the result is equivalent to an AND function.

Fig. 4-3. Implementing the AND function with NOR gates.

Fig. 4-4. The NOR gate as an inverter.

An important question is: Can the NOR gate function as an inverter? Examining the truth table for a NOR gate Fig. 4-4A, if input B is held permanently false, when A is O the output is 1 and when A is 1 the output is O. This method of operating a NOR gate would invert whatever signal is connected to input A. Input B is easily held false in a negative logic system by connection to the positive supply. A NOR gate operated as an inverter, Fig. 4-4B, could also be symbolized by the symbol in Fig. 4-4C, i.e., an inverter or NOT circuit. It is of little consequence in a logic diagram exactly how the inverter function is implemented. Many diagrams would use the inverter symbol. The AND function of Fig. 4-3 could therefore be implemented by using three NOR gates.

If the OR function is to be implemented using NOR gates, the designer may proceed as in Fig. 4-5.  $\overline{A+B}$  inverted becomes A+B; thus inversion of the AND function, or the OR function, can be implemented using nothing more than NOR gates.

Theorem 3.13 reads  $\overline{AB} = \overline{A} + \overline{B}$ . Using the A NAND B relationship any of the desired functions can be implemented. Examine the truth table for a NAND gate as shown in Fig. 4-6A. If the B input is held permanently true (Fig. 4-6B) then the A input is inverted. The NAND gate may be used as an inverter and may be symbolized as in Fig. 4-6C.

Fig. 4-5. Implementing the OR function with NOR gates.

Fig. 4-6. Inverting with a NAND gate.

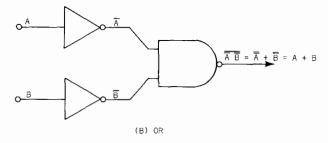

Fig. 4-7A illustrates the implementation of an AND function using only NAND gates. Fig. 4-7B shows the implementation of an OR function using only NAND gates. A and B are first inverted and then NANDed together giving the result,  $\overline{\overline{A}\ B}$ . By DeMorgan's theorem this is equivalent to A + B.

Most integrated circuit chips presently manufactured are NAND gates when used in a negative logic system. Very many NAND gates appear in Tektronix digital instruments. The student should be familiar with the implementation of logic functions using NAND gates.

Fig. 4-7. Implementing with NAND gate.

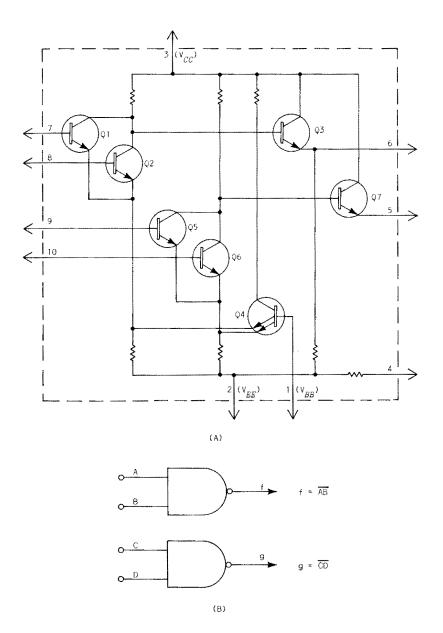

Fig. 4-8. Complex NAND circuits.

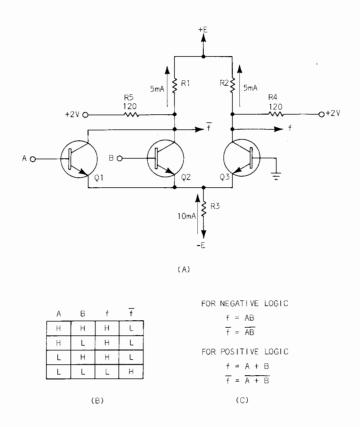

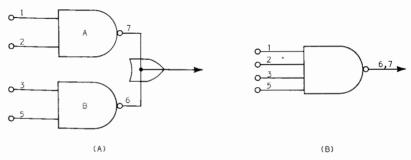

NAND as inverted input OR Sometimes a NAND gate is shown as an inverted input OR gate. See Fig. 4-8A. The truth table for a NAND gate indicates that with A and B both true a false output results. The same applies to gate B. Here we have a situation in which true inputs give a false output. Gate C responds to the false output levels of gates A and B. Re-examine the truth table for a NAND gate replacing true and false with the negative logic voltage levels (Fig. 4-8B), we find when any NAND gate input is high the output is low. Only if both inputs are low is the output high. Using positive logic instead of negative logic we could say that this gate acts as a positive logic NOR gate. certain schematics, as in Fig. 4-8C, the symbol for Gate C is replaced by an inverted input OR symbol. A NAND B and C NAND D are inverted before being OR'd. The final result is A AND B OR C AND D. Fig. 4-8A also gives this result if we apply DeMorgan's theorem to the output. The difference is only in the symbology used. The actual logic operation is the same.

The configuration in Fig. 4-8 appears several times in the Tektronix Type 230 and Type 240 instruments. When using NAND gates or NOR gates a system of mixed logic actually occurs within the diagram. inputs for a NAND gate give a false output. operation can be called an inversion in logic values. Thus, many observers say that after passing through a NAND gate (if the input is in a negative logic assignment) the output has a positive logic assignment. In the case of Fig. 4-8, the system inputs are in a negative logic environment. They are inverted once by the first two NAND gates and inverted again by (negative logic NAND or positive logic NOR) gate C. The output level emerges in a negative logic environment. This is the case for many Tektronix digital instrument circuits. The actual logic assignments are fixed in Tektronix diagrams.

Fig. 4-9A illustrates a transistor whose input terminals are the emitter and the base. In this case, input A must be high and input B must be low for the transistor to be on. The inputs required have opposite levels. The truth table for such a gate in a negative logic environment is shown in Fig. 4-9B. The output is zero (or false) except when A is zero and B is one. The logic symbol for such a gate is shown in Fig. 4-9C. The equation for such a gate is  $Z = \overline{AB}$ . Occasionally we use such a gate where it is desired to hold one input false and disable the entire gate. Here, if input B is held false, the output at A has no control over the gate. In this sense, then, input B is termed an inhibiting input and the gate is often called an "inhibitor." At Tektronix we consider this type of gate a special form of AND or NAND gate with mixedlogic inputs. Examples of this gate appear in both Type 230 and Type 240 instruments.

inhibitor

Fig. 4-9. An inhibited gate.

The logic operations discussed to this point are essentially single action in nature. A set of logic signals is applied to a set of logic decision devices which proceed to generate a single result. Many digital systems require nothing more. Others, perhaps the majority, require a series of such operations in sequence. To provide a sequential action, a device is required which has a memory. One which will remember the results of a logic operation for later use. A counting circuit is an example. When counting from one to ten the counter must remember how many units have already been counted. At the fourth count, to realize that this is the fourth count, the counting circuits must remember that three prior counts have been made.

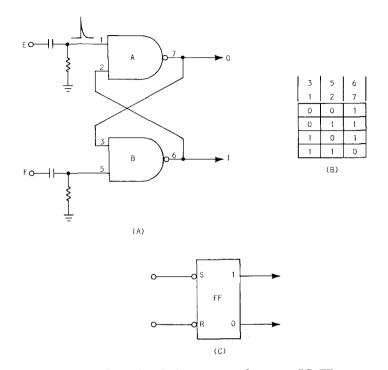

Fig. 4-10. Evolving a flipflop.

A simple way of obtaining a memory device uses an OR See Fig. 4-10A. OR gate E has a connection from its output back to one of the inputs. that X initially equals zero. If X is zero then A must be zero. If A is now made equal to one, then X must equal one. If X equals one, input B receives the one and regardless of whether A returns to zero the output remains at one. The circuit as shown is impractical because there is no way of forcing X back to the zero state. The gate can be forced back to zero if some means is provided for breaking the feedback path. See Fig. 4-10B. Here the feedback path contains AND gate F. The AND gate F has inputs B and X and output Y. A truth table for gate F is shown in Fig. 4-10C. Examining the table Y equals X if  $\overline{B}$  is one. If  $\overline{B}$  is zero, however, the output is zero. By making  $\overline{B}$  equal to zero we force the OR gate E back to zero if A is zero at that time. The logic equation for this circuit would be  $Y = \overline{B} \cdot X$ . Looking at the overall circuit a one input at A forces the output X to one. A one at B, inverted by gate G, forces the output to zero.

The above is an electronic equivalent to a toggle switch. Flip the switch one way to on, flip the switch the other way to off. Similarly make B equal to one and X flips to zero; make A equal to one and X flips to one. This leads to the definition for a binary memory unit. Such a binary unit has two control inputs. A true level at one input forces the output of the device to one. The other input having a true input forces the output to the opposite state.

The circuit of Fig. 4-10B is bistable. If input A

goes to one, X goes to one. If input B goes to one, X goes to zero. This action is similar to an FF (flipflop). An FF can be implemented by using vacuum

tubes, transistors, tunnel diodes, magnetic cores or any other two-state active device.

flipflop

Fig. 4-11. T flipflop.

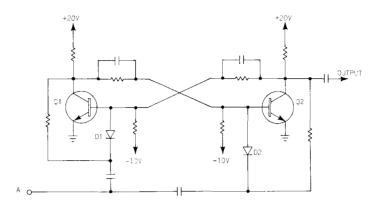

A commonly encountered type of FF using transistors is shown in Fig. 4-11. A trigger pulse introduced at A is differentiated and then conducted via diode D1 and D2 to Q1 and Q2 bases. D1 and D2 polarize the pulse so that only the negative edge of the pulse appears at the bases. The NPN transistors are turned off by a negative edge. Any time a trigger pulse is coupled into input A the flipflop will change state. Since this action is analogous to toggle-switch action, the circuit is called a toggle flipflop (T FF). The T FF has a major shortcoming. The state of the FF after a trigger is applied cannot be accurately known unless the present state is known.

toggle flipflop (T FF)

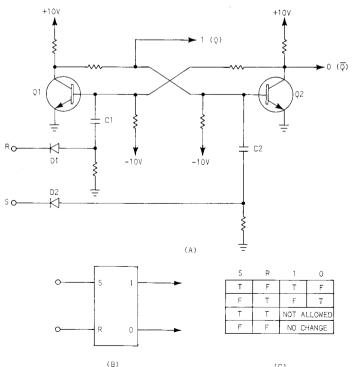

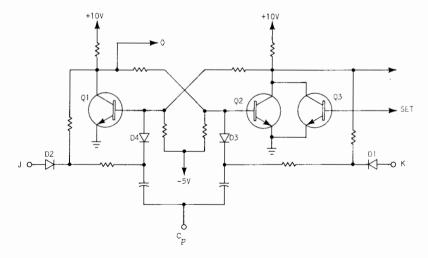

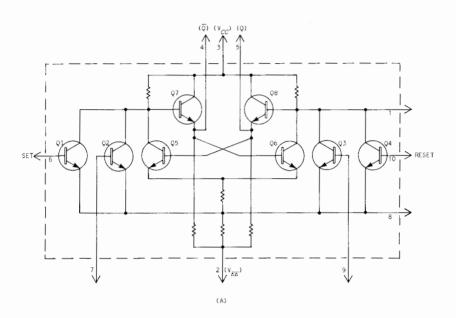

set-reset flipflop (RS FF) Another common FF is the "Set-Reset" (RS FF). A representative transistor RS FF is shown in Fig. 4-12A. This is similar to the T FF except that there are two input terminals. This circuit is predictable for three of four input conditions.

The inputs labeled R and S are called the Reset and Set inputs, respectively. Two rules for RS flipflops are "Set to one" and Reset to zero." Set to one means an input signal (negative step here) to the Set terminal switches the circuit to a known condition called the *One state*. Reset to zero means that an input signal (negative step) to the Reset input switches the flipflop to the opposite condition called the *Zero state*. It remains to define the output states of the circuit. As an example, consider Fig. 4-12A. A negative edge to the S input couples through D2 and C2 to turn Q2 off. The collector of Q2 goes false and turns on Q1. The collector of Q1 goes

true. This output is therefore the one output. Thus, a Set input signal places the flipflop in the one state. A negative edge to the R input switches the 1 output to zero.

The collector of Q2 always logically complements the 1 output and is called the 0 output. In Fig. 4-12B we show the logic diagram symbol for an RS flipflop. A box symbol shows two inputs on the left, two outputs on the right. Tektronix diagrams always show the Set input opposite the 1 output. The Reset appears opposite the O output. The rule that an input to R causes the 1 output to go to 0 could also be stated R causes the O output to go to 1. The RS flipflop truth table (Fig. 4-12C) shows that all input conditions are covered except when S and R inputs receive simultaneous negative edges. The next state of the FF cannot be predicted and is ambiguous. Since this is true, for the RS flipflop simultaneous R and S inputs are commonly called "not allowed" or "forbidden" combinations. The RS flipflop is used in logic situations which do not include the possiblility of simultaneous Set and Reset inputs.

Eig 1 12 The DC flinflen

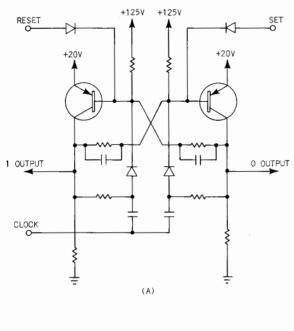

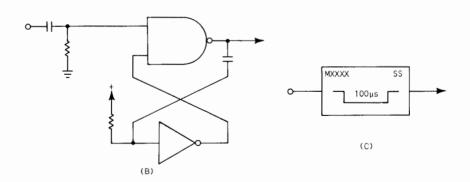

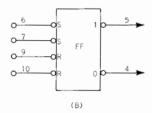

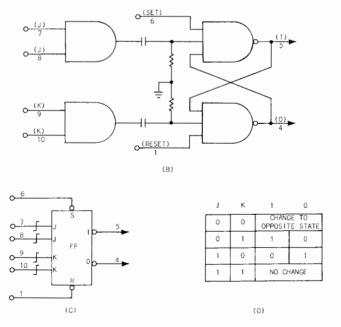

The circuit of Fig. 4-13A combines the features of the toggle and RS FF's. This particular circuit using PNP transistors responds to positive signals at all inputs. The Clock input responds only to positive-edge signals.

A logic symbol (drawn for negative logic) appears in Fig. 4-13B. The small circles at S and R inputs indicate logic inversion at that point. This should be interpreted to mean that a false level is inverted to become a true level within the box. The 1 and 0 outputs also have circles. From a negative-logic viewpoint these are  $\overline{1}$  and  $\overline{0}$  outputs. A  $\overline{\text{Set}}$  signal (the bar indicates that the set input is the high level) switches the FF to a  $\overline{1}$  condition. See the truth table of Fig. 4-13C.

The symbol at the  $C_p$  (Clock pulse) input indicates that this input responds to a positive edge signal only.

clocked RS FF The clocked RS FF is used in counting circuits. In such circuits the FF operates in a clocked mode for a period of time. Afterwards the FF must be returned to a known condition using either R or S input.

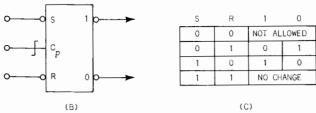

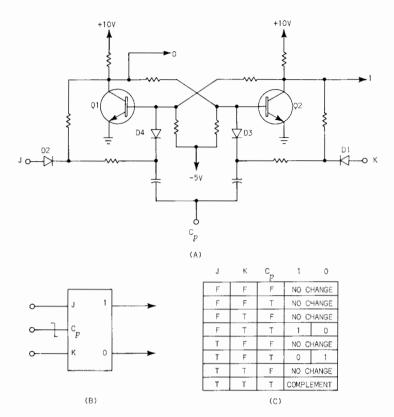

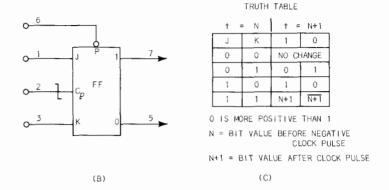

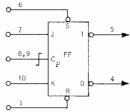

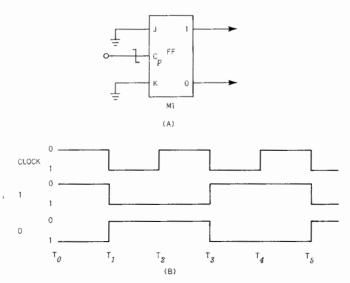

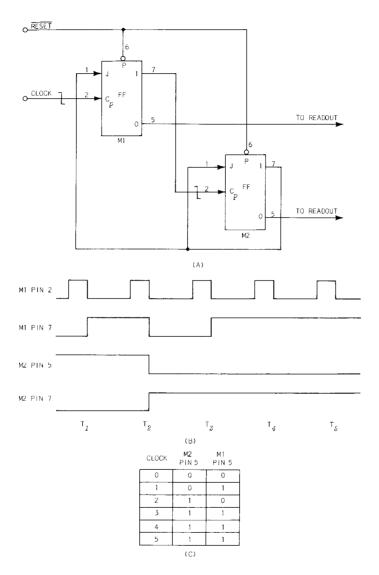

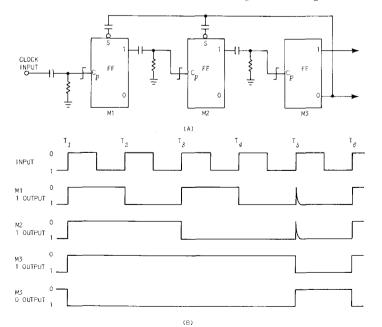

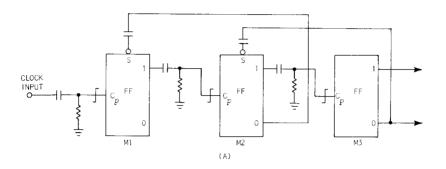

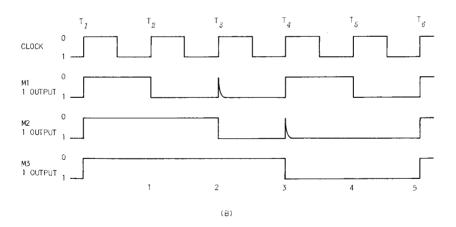

clocked JK FF The JK FF has no ambiguous states. When a one is applied to the J, the flipflop is switched to the one state. With a one at K the flipflop is switched to the zero state. If ones are applied to both J and K the FF switches to its complement state. Many JK flipflops are supplied with two or more J inputs and two or more K inputs. Frequently one J and one K input are connected together and called the clock input. This input is usually labeled  $\mathbf{C}_p$  on Tektronix logic diagrams.

Fig. 4-13. The clocked RS FF.

Fig. 4-14. Clocked JK FF.

Fig. 4-15. Clocked JK FF with Set input.

Fig. 4-14A shows a JK flipflop using discrete components. The circuit is similar to that for the T FF. Diodes D1 and D2 provide a way of inhibiting  $\mathbf{C}_p$  input signals. For example a positive level applied to the J input causes D2 to conduct. The positive level coupled through D2 holds D4 off. D4 when off, blocks a negative edge signal to Q1 base. Q1 cannot be turned off. The  $\mathbf{C}_p$  signal can pass through D3 turning Q2 off (if not already off).

A positive voltage at K couples through D1 to D3. D3 inhibits a  $\mathbf{C}_p$  signal to Q2. This inhibiting action can be viewed as a way of steering the flipflop to a desired condition. If both J and K are held false the flipflop will hold its present condition when a clock input occurs.

One mode of operation puts J and K at one. negative logic assignment used at Tektronix the inputs are at 0 V. J and K are electrically disconnected from D3 and D4, the trigger gates. The operation is now the same as for the T FF. The state of the flipflop changes for each negative edge into the  $C_n$ input. For this circuit, just pulling J false or K false will not change the state of the flipflop. false J or K inputs have no effect until a clock is applied to  $C_{\mathcal{D}}$ . This is typical of all clocked JK flipflops. The reader may determine the operation of the flipflop by referring to the truth table of Fig. 4-14C. The logic symbol for a JK flipflop appears in Fig. 4-14B. The JK flipflop has no ambiguous states. The designer can always control the output state of the flipflop regardless of the combination of input signals. For this reason the JK flipflop is used more frequently than any other type.

In certain circuits the designer requires an additional input which overrides the J, K, and clock inputs. The circuit of Fig. 4-14A may have an extra transistor connected as shown in parallel with Q2. See Fig. 4-15. The base of Q3 would be called a set input. By putting a false level on Q3 the 1 output goes true regardless of any other inputs to the circuit.

set input

## IMPLEMENTING LOGIC FUNCTIONS

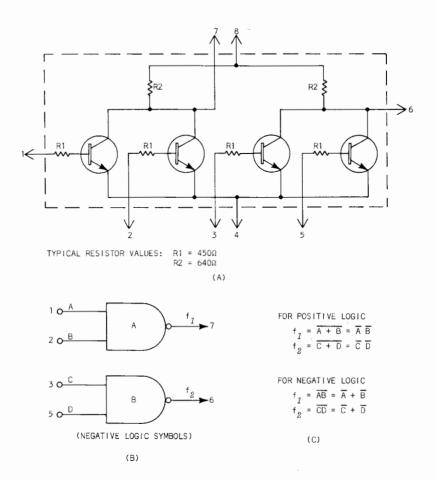

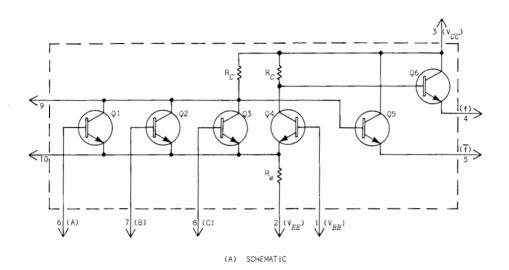

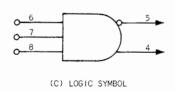

Logic functions can be implemented by the use of any component which can act as a switch. This includes mechanical switches, relays, diodes, transistors, vacuum tubes, field-effect transistors; indeed any active device which can turn on and off. methods of using the switching devices to implement logic functions are given special names. The name is usually a series of letters taken from the first letter of the first words which name each type of logic circuit. Thus we have such names as DL which stands for Diode Logic, RTL standing for Resistor-Transistor Logic, DTL for Diode-Transistor Logic, TTL for logic systems using Transistor-coupled to Transistor Logic circuits and CML for Current-Mode Logic. Within the digital circuit industry, other initials are commonly used. These, however, are primarily utilized for commercial purposes and are normally found to be modifications of the previously named types of logic systems.

Knowledge of the exact type of logic circuit used is often of minor importance to the user of the completed device. However, this knowledge is very important to the device designer because the families of logic circuits possess various advantages and disadvantages which recommend one over the other. Also, to troubleshoot or circuit trace an existing instrument, a knowledge of the shortcomings of the types of logic circuits becomes important.

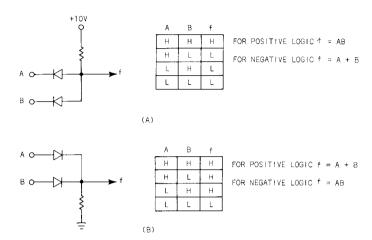

The semiconductor diode is a two-terminal, nonlinear switching device. It is binary in nature because when forward biased it has low forward resistance, and when reverse biased, it has high reverse resistance. Semiconductor diodes used to perform logic functions were among the first devices utilized in digital circuits, principally because they are small, inexpensive, fast switching and operate at low power levels. The diode, however, is a nonamplifying device, and circuits which employ diodes are usually limited to single logic functions.

diode logic

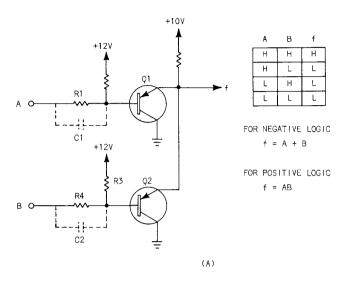

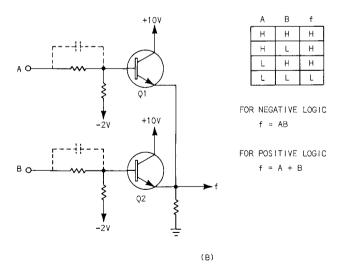

Fig. 5-1. Diode logic gates.

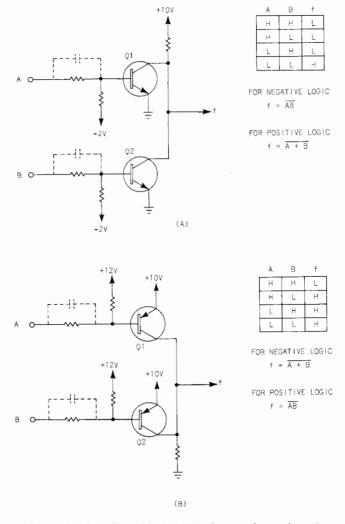

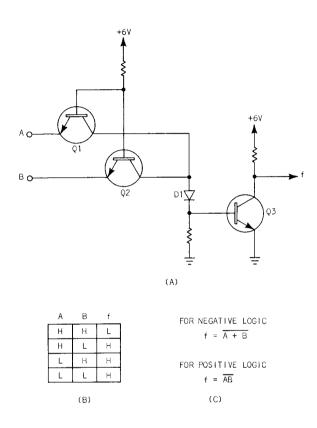

Practical circuits utilizing diode logic circuits often include active transistors or other amplifying devices to offset diode losses. Two basic diode logic circuits are shown in Fig. 5-1. Fig. 5-1A shows a diode circuit and a voltage-level truth table. This circuit operates as an AND gate in a positive-logic system, and an OR gate for a negative-logic system. Fig. 5-1B, on the other hand, is a positive-logic OR gate and a negative logic AND gate. Since these are universal circuits it is important to realize that the same circuit in one instrument could be an AND gate and could equally well be an OR gate in a different instrument.

In either of the circuits of Fig. 5-1, assuming that silicon semiconductor diodes are utilized, approximately 0.6 volts is lost between the input and the output signal levels. If an attempt is made to cascade several diode-logic circuits, it is usually found that enough voltage is lost to render the circuit almost unusable. In early instruments which used this type of logic circuit, an amplifying transistor or vacuum tube was often inserted to replenish circuit losses.

When operated in high-speed logic systems, the diode logic circuit has several shortcomings. One problem is the fact that when a diode is forward biased and an attempt is made to turn it off, it takes an interval of time before the stored charge is fully

diode losses fan out

swept out of the diode junction. This limits switching speed for the diode. In addition, the diode logic circuit suffers from poor "fan-out" capabilities. Fan out is a term which refers to the number of other logic-device input circuits that a particular logic output circuit may be capable of driving.

The diode logic circuit has poor fan-out capabilities because the diode has low forward resistance and provides little isolation between input and output. The source impedance of the circuit can cause excessive voltage losses. If high-speed logic functions are to be performed, the ability of a diode circuit to charge a capacitive input is limited by the finite forward resistance.

The biggest advantages of diode logic circuits are small size and low cost. Because of these advantages, which often outweigh the disadvantages, frequent use is made of diode logic circuits.

resistortransistor logic Resistor-transistor logic circuits use the transistor as an active element. The transistor has several advantages. It provides both voltage and current gain which gives it excellent noise immunity and excellent fan out. The transistor is normally operated as a switching device; that is, it operates between a cutoff condition and a saturated condition. When cut off the transistor has high reverse resistance and when saturated has low forward resistance. Thus it is a good binary element.

cutoff

saturation

time delay

On the other hand, transistors operated into saturation may suffer from several forms of time delay. When turned on, the transistor takes an interval of time before the carrier condition is fully established. A saturated transistor requires a certain amount of turn-off time because of the minority-carrier storage time of the forward-biased collector-to-base junction. This limits the usefulness of the RTL circuit in high-speed logic applications.

commonemitter mode RTL circuits use transistors in the common-emitter amplifier mode. Because of the bipolar nature of transistors, circuits utilize both NPN and PNP devices.

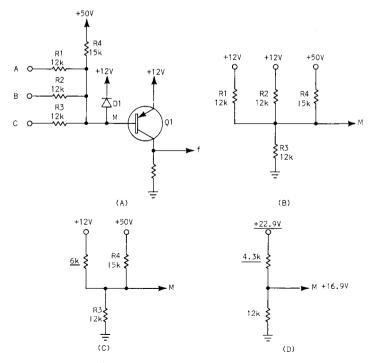

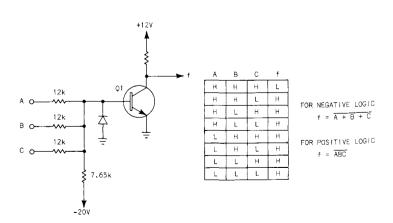

A representative RTL circuit using a PNP transistor is shown in Fig. 5-2. This is a three-input NAND gate. The three inputs, A, B and C, are each coupled to the base of Q1 by a 12-k resistor. The logic levels for this particular circuit are 0 V = 1, 12 V = 0. Unless A and B and C are all true, the base of Q1 is not negative with respect to its emitter and Q1 remains off. Only with A and B and C at zero volts, can Q1 be on, and the output be false. This is characteristic of a NAND gate.

The major point of interest in this circuit is the voltage level at node M in Fig. 5-2A. To confirm the truth of the previous statements, let us examine the possible conditions for the gate. First we consider the C input true, the other two inputs false. This is the voltage condition shown in Fig. 5-2B. We apply Thevenin's theorem to the two-resistor branch consisting of R1 and R2 which gives the result shown in Fig. 5-2C. Again applying Thevenin's theorem gives the circuit of Fig. 5-2D. R3 in series with the equivalent 4.3 k $\Omega$  puts node M at +20.7 volts. This assures that Q1 is off.

Fig. 5-2. An RTL circuit using a PNP transistor.

If Ql were to be a silicon planar PNP transistor, it would be necessary to add a clamp-diode Dl at node M to prevent Ql from going into emitter-base breakdown. This diode would clamp node M at approximately +12.7 volts. Without the diode, node M would be at +16.9 volts.

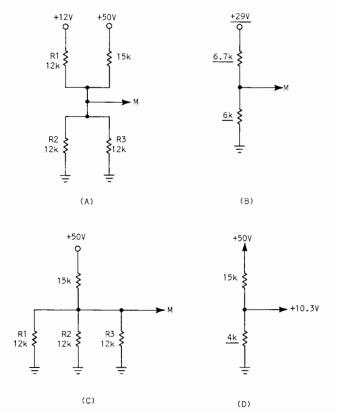

If we consider two inputs (B and C) true we have the circuit of Fig. 5-3A. This Thevenizes to the simplified circuit in Fig. 5-3B. The resistor ratio places node M at approximately +13.8 volts. This level assures that Q1 is off.

Finally, considering the case where all three inputs are true, we have the circuit of Fig. 5-3C. This simplifies to the circuit of Fig. 5-3D placing node M at approximately +10.3 volts. Q1 is turned on with +10.3 volts at the base.

Fig. 5-3.

If Ql were to draw excessive emitter-base current a resistor could be added between node M and the base of the transistor to limit that current. Fig. 5-4 illustrates a similar circuit which performs as a negative-logic NOR gate. Here an NPN transistor is used. Ql is cut off unless all inputs are false. Study of the voltage-level truth table shows that this is a negative-logic NOR gate. The reader may solve the resistive divider for all possible input combinations using the methods for Fig. 5-3 to convince himself that the circuit operates as stated.

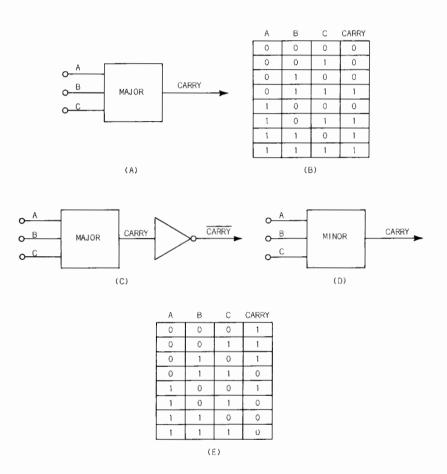

majority logic Fig. 5-5A shows the symbol of a three-input circuit which performs a majority logic operation. Unlike ordinary Boolean algebra circuits, a majority circuit responds to the majority of its inputs. A truth table for such a function of a three-input majority logic gate is shown in Fig. 5-5B. The output of the gate is 0 unless two or more of the inputs (a majority) are 1, in which case, the output is 1.

minority logic One of the simplest methods of implementing this function uses RTL with an inverting transistor. The majority output is thus inverted. See Fig. 5-5C. A majority inverted becomes a minority. The output (carry) agrees with the minority of A, B, and C input levels. This composite gate is represented by the symbol of 5-5D. The truth table for the minority gate is shown in Fig. 5-5E.

Fig. 5-4. An RTL circuit using an NPN transistor.

Fig. 5-5. Majority/minority functions.

| Α   | В | С | М |

|-----|---|---|---|

| 0   | 0 | 0 | 1 |

| 0   | 0 | 1 | 1 |

| 0   | 1 | 0 | 1 |

| 0   | 1 | 1 | 0 |

| 1   | 0 | 0 | 1 |

| 1   | 0 | 1 | 0 |

| 1   | 1 | 0 | 0 |

| 1   | 1 | 1 | 0 |

| (B) |   |   |   |

Fig. 5-6. A minority circuit.

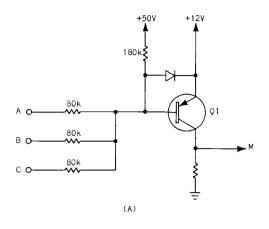

A circuit which performs a minority function appears in Fig. 5-6A. The circuitry appears to be the same as that of a three-input NAND gate. The resistive components are chosen so that Q1 remains off unless at least two of the inputs are true. A truth table for the gate is shown in Fig. 5-6B. The gate uses logic levels of 0 = +12 V and 1 = 0 V. The reader may solve the circuit and prove the truth table.

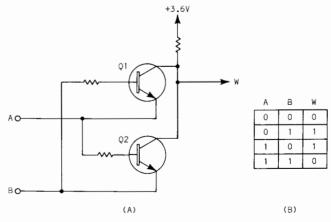

Exclusive-OR gate The Exclusive-OR gate (also called an anticoincidence gate) delivers a true output if the input states are not identical. The output of the gate is false if the inputs are identical. A typical discrete-component transistor Exclusive-OR gate is shown in Fig. 5-7A. Transistors Ql and Q2 are connected together in the form of a RTL logic circuit. Input A is connected to the emitter of Ql and the base of Q2. Input B is connected to the base of Q1 and the emitter of Q2. If inputs A and B are at the same level, both transistors have zero-biased emitter-base junctions and neither transistor is on. Only if the inputs are at opposite logic levels can one or the other of the transistors be on. A truth table for the device is shown in Fig. 5-7B.

diodetransistor logic The major disadvantage of the RTL circuit is slow operation due to saturation. In addition, given a fixed logic assignment and restricted to a single type of transistor (NPN or PNP), there is no way to obtain both NAND and NOR operations. Thus certain logic expressions cannot be implemented efficiently. Both disadvantages are avoided by combining the diode logic circuit with the transistor.

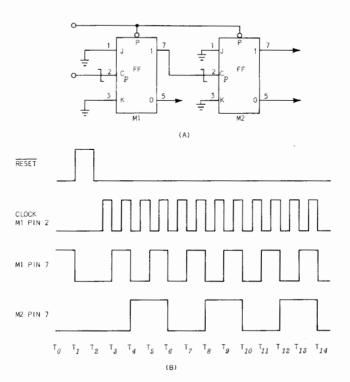

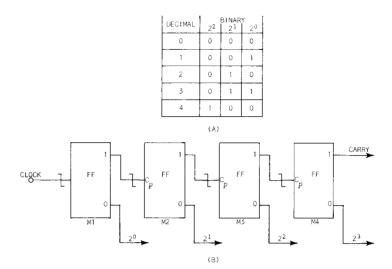

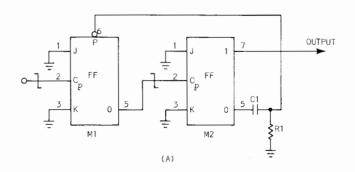

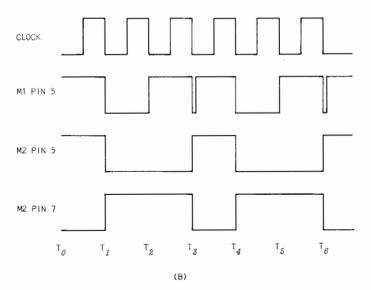

Fig. 5-7. Exclusive OR gate.