# Vertical Amplifier Circuits

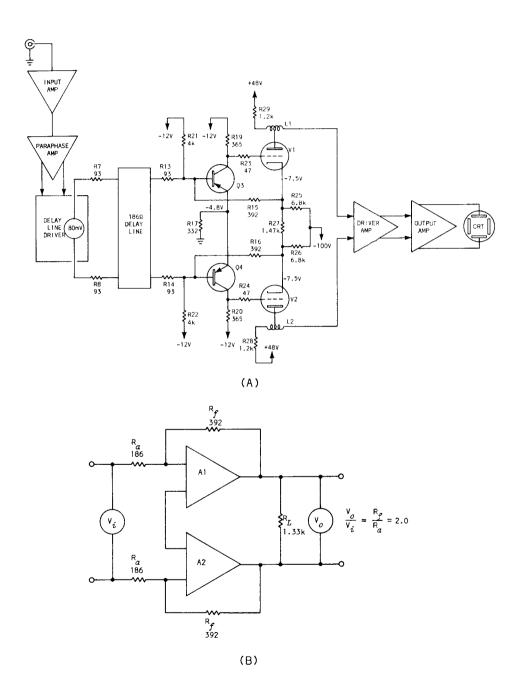

# OSCILLOSCOPE VERTICAL AMPLIFIERS

BY BOB ORWILER

CIRCUIT CONCEPTS

FIRST EDITION, FIRST PRINTING, DECEMBER 1969 062-1145-00 PRICE \$1.00

## **CONTENTS**

|   | INTRODUCTION 1                                |    |

|---|-----------------------------------------------|----|

| 1 | VERTICAL AMPLIFIERS 5                         |    |

| 2 | INPUT CIRCUITS AND COMPENSATED ATTENUATORS 39 |    |

| 3 | FOLLOWERS 59                                  |    |

| 4 | TRANSMISSION LINES 173                        |    |

| 5 | SINGLE-ENDED AMPLIFIERS 193                   |    |

| 6 | DIFFERENTIAL AMPLIFIER FAMILY 28              | 53 |

| 7 | FEDBACK AMPLIFIERS 393                        |    |

|   | INDEX 459                                     |    |

### INTRODUCTION

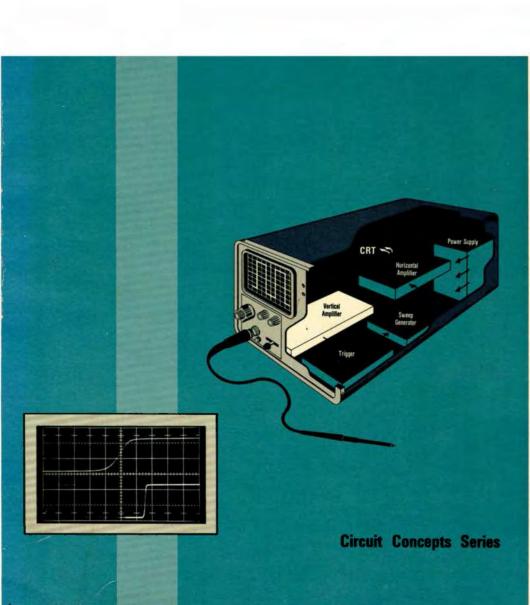

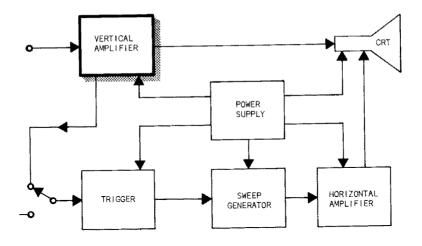

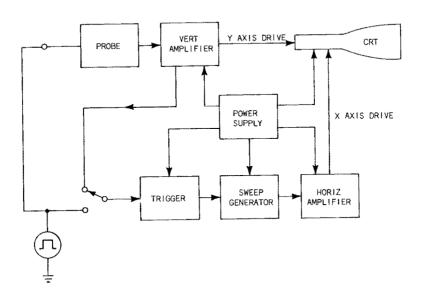

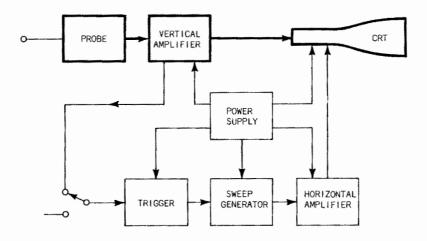

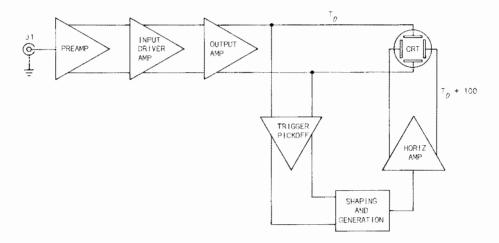

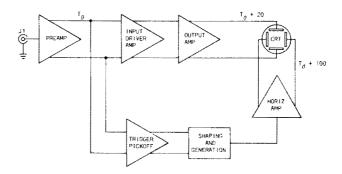

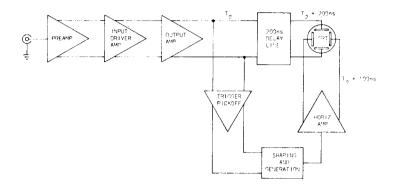

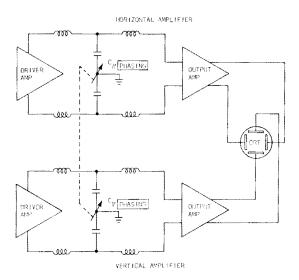

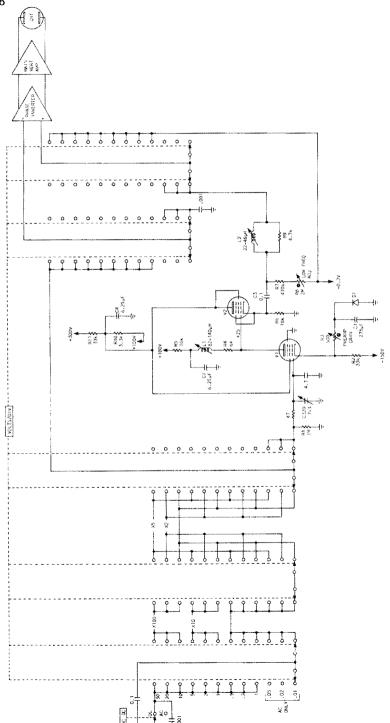

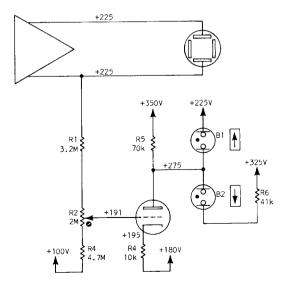

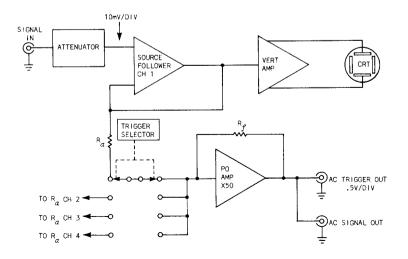

In a study of conventional oscilloscopes, the various circuits of the instrument fall into general groupings: the power supply, cathode-ray tube, trigger circuit, sweep generator, horizontal amplifier and the vertical amplifier.

Each performs an important function. Combinations of individual contributions determine instrument performance.

power supply

The power supply converts some form of available power (depending on the type and location of the instrument) to DC operating potentials for all the active circuits of the oscilloscope. Regulation holds most of these potentials to narrow tolerances, guaranteeing precise circuit performance. A power supply might also contain filament power for vacuum—tube circuits, overload protection and facilities for adapting the instrument to various local power conditions.

cathode-ray tube The cathode-ray tube (CRT) displays light on a two-dimensional phosphor screen. It conveys intelligence in the form of alphanumerics, picture images or graphs. Graphical presentations offer an analytical approach: Actual measurements taken with a graticule along the "X" and "Y" screen axis.

The CRT electron gun is sealed inside an envelope. A vacuum minimizes collisions between free gas particles and the electron beam. High-voltage power supplies create controllable electrostatic fields which accelerate free electrons from the heated cathode to form an electron beam. The beam of electrons then transit an electron lens which converges or focuses the beam on a phosphor screen. When the high-velocity electrons collide with phosphor atoms at the focal point, photons of light emit towards the viewer.

Varying the electrostatic fields between a set of "X" and "Y" deflection plates positions the light source on the screen. Thus the electron beam creates a display anywhere within the viewing screen area. Since electrons have an extremely small mass, they can be deflected or scanned over the entire screen area millions of times per second. This permits the viewer to observe changing phenomena in real time.

The CRT must not unduly load either the vertical or horizontal amplifier nor require a greater dynamic-deflection range of voltage than the amplifiers can supply. In practice, the CRT and deflection amplifiers are designed together for maximum performance and efficiency.

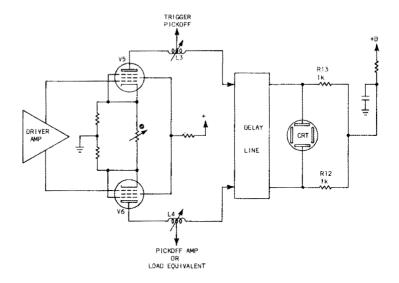

trigger circuit Input signals take a wide variety of shapes and amplitudes, many unsuitable as sweep-initiating triggers. For this reason a trigger circuit converts these signals to pulses of uniform amplitude and shape. This trigger circuit makes it possible to start the sweep with a pulse that has a constant size, eliminating variations of the sweep-circuit operation caused by changing input signals. The operator now uses either slope of the waveform to start the sweep, selects any voltage level on the rising or falling slope of the waveform, and, in some instances, eliminates selected frequencies of the input signal with ease and repeatability.

sweep generator The sweep generator produces a sawtooth waveform for processing by the horizontal amplifier which then deflects the CRT beam. The sweep generator produces a sawtooth waveform, with the proper rate-of-rise, amplitude and linearity, suitable as a time-measuring reference.

horizontal amplifier

Primarily, the horizontal amplifier converts the time-base ramp, developed in the sweep generator, to deflection voltage for the horizontal CRT deflection plates. The resulting trace is the reference for Y-T displays (voltage plotted as a function of time). In those instruments offering X-Y capabilities (where both X and Y inputs are dependent variables) the horizontal amplifier reacts to the external (X) input as a linear amplifier. It exhibits a frequency response comparable to that of the vertical amplifier. Additionally, the horizontal amplifier provides DC-level and amplifier gain controls which permit positioning of the horizontal trace and sweep magnification (expansion) The latter facility extends respectively. instrument sweep speed without imposing additional sweep-rate requirements on the sweep generator.

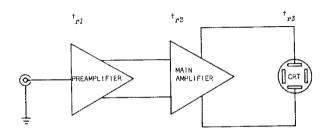

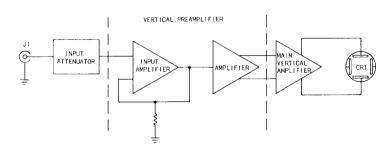

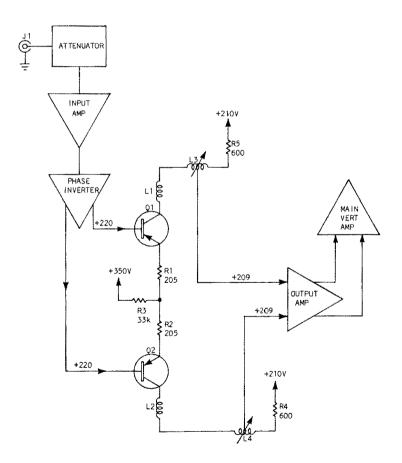

vertical amplifier The vertical amplifier determines the useful bandwidth and gain of the instrument. Vertical amplifiers take three general forms: a fixed vertical, a complete vertical in a plug-in form or a fixed main vertical amplifier preceded by a plug-in preamplifier. Selection of plug-ins allows a range of characteristics. An additional type of instrument takes the drive directly to the CRT plates without passing through any type of amplifier.

The general-purpose oscilloscope provides a faithful display of an input voltage. For meaningful results, displayed waveforms contain few aberrations and these but a few percent of the total waveform amplitude.

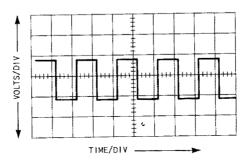

Fig. 1-1. Oscilloscope display.

Fig. 1-2. Basic oscilloscope block diagram.

#### VERTICAL AMPLIFIERS

Vertical amplifiers meet requirements briefly summarized below:

- Buffer the signal source (probe) and the CRT.

- Provide various modes of operation such as: direct or AC coupling, multiple trace, and, perhaps, selectable differential modes.

- Finally, the amplifier faithfully reproduces voltage waveforms within specified risetime-bandwidth-amplitude limits.

Why these items are important and how they are accomplished by Tektronix is what this book is about.

graticule

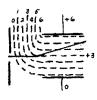

An oscilloscope graphically displays signals of interest, as shown in Fig. 1-1. Here periodic rectangular pulses appear superimposed on a grid called the graticule. Equal divisions divide the graticule X and Y axes. Fig. 1-1 shows ten major horizontal (X) divisions and six major vertical (Y) divisions. Small markings along the center lines describe minor division dimensions at 20% of a major division.

The horizontal base is calibrated in units of time per division; the vertical in units of voltage per division. For example, if each vertical increment is 0.5 volts and horizontal is 0.5 milliseconds per division, then Fig. 1-1 depicts a 1-volt pulse train with pulses recurring each millisecond.

Accurate information from both horizontal and vertical circuits creates faithful reproductions of the input waveforms. To accomplish this an oscilloscope generally requires the basic blocks shown in Fig. 1-2.

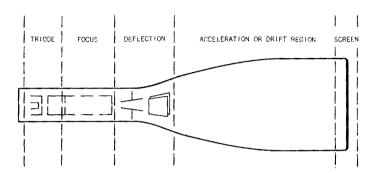

Fig. 1-3. CRT sections.

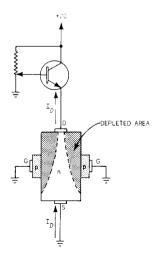

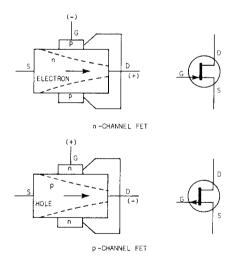

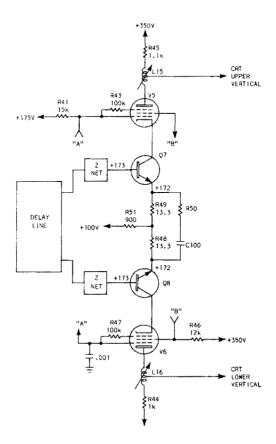

CRT

Cathode-ray tubes present a reactive load to deflection amplifiers. CRT construction and applied voltages cause a beam of the electrons, emitted by the CRT cathode, to form. The beam forms during electron travel from cathode to phosphor-coated faceplate. Energy contained in this concentrated mass of electrons striking the faceplate or screen is partially converted to light. Deflecting the beam vertically (Y) and horizontally (X) graphically reproduces waveforms. Deflection may be either electrostatic or electromagnetic. Since very few oscilloscopes use magnetic deflection, this book covers electrostatic deflection only.

Two pairs of plates mounted at right angles, as shown in Fig. 1-3, deflect the beam when energized. Leads from each plate penetrate the CRT envelope for connection to external excitation sources. The beam in the CRT shown passes first between the vertical deflection plates, then the horizontal.

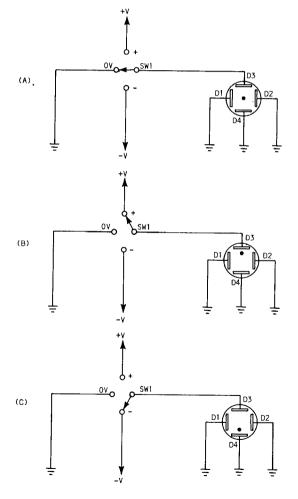

A CRT and power supply alone function as a crude oscilloscope. Fig. 1-4 shows such an arrangement.

norizontal plates connect to D1-D2 and vertical plates to D3-D4. D1, D2 and D4 connect to a common voltage, shown as ground. D3 connects to a signal source represented by the three-position switch. Applying zero volts to D3 centers the beam. Throwing the switch to +V attracts the beam toward D3. Repelling occurs with -V applied to D3.

Connecting either D1 or D2 to a signal source results in horizontal deflection.

A vertical deflection system like this one has one advantage -- simplicity. Unfortunately, there are disadvantages. Some are:

Low sensitivity.

Signal source loading.

Nonlinearity.

Fig. 1-4. A vertical system utilizing the CRT only.

deflection sensitivity One needs a means of measuring deflection. Assume a vertical scale inscribed on the CRT faceplate. Scale increments begin at the center extending three divisions up and three divisions down. One needs to know the deflection sensitivity to calibrate the scale; i.e., how many scale divisions each volt deflects the electron beam. If divisions were scaled one centimeter apart (a representative dimension) the ratio cm/V expresses deflection sensitivity. O.1 cm-per-volt represents a general deflection sensitivity. This restricts practical direct measurements to one volt minimum signal. Deflection sensitivity and screen diameter fix the maximum measurable level.

signal source isolated

Inserting a probe and an amplifier increases deflection sensitivity and isolates signal source The deflection plates appear as capacitive and CRT. circuit components. Connected directly this reactance might drastically change monitored circuit characteristics. The probe - vertical amplifier -CRT combination presents a high impedance to the circuit under test, allowing measurements to represent nominal circuit conditions. This vertical deflection system by including an amplifier implies voltage gain. Vertical amplifiers can increase deflection sensitivity. Further, the amplifiers contain calibrated step control of gain and attenuation extending input deflection sensitivity from, perhaps, 0.04 div/V to 100 div/V in several steps.

sensitivity improved

deflection factor Division-per-volt terminology usually requires calculation for meaningful observations. therefore, uses deflection factor to conveniently express sensitivity. Deflection factor is the inverse of deflection sensitivity and is listed as volts-per-division (V/div): The CRT was earlier assigned a deflection sensitivity of 0.1 div/V. This is a deflection factor of 10 V/div. Including an amplifier increased vertical-deflection sensitivity to 100 div/V -- in terms of deflection factor, 10 mV/div. Rather than say the input sensitivity is selectable in eight steps from 0.04 div/V to 100 div/V, one states the steps, in terms of deflection factor, as from 25 V/div to 10 mV/div. Each observed division of CRT deflection now reads directly.

linearity improved

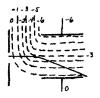

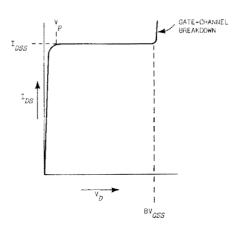

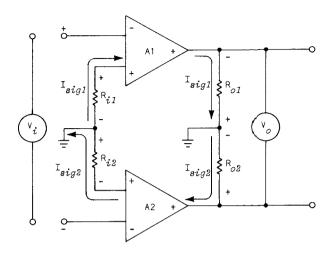

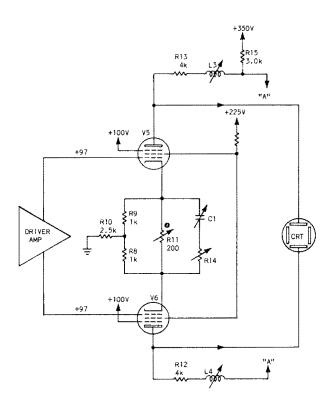

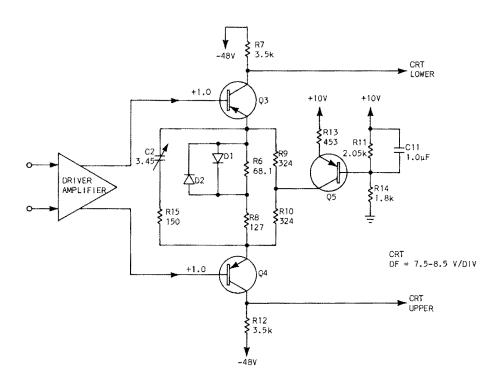

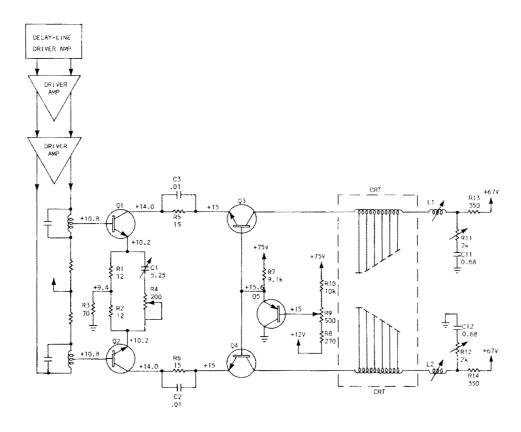

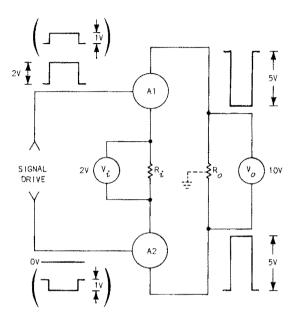

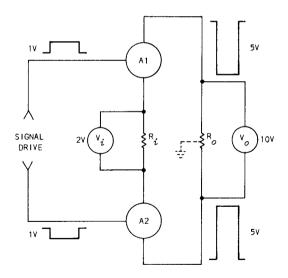

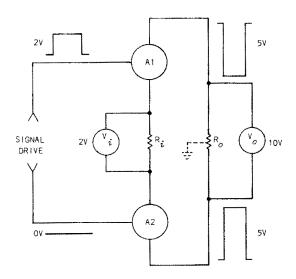

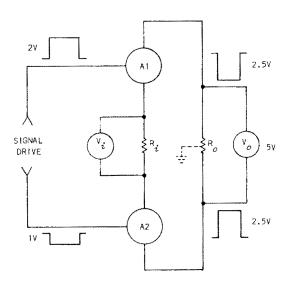

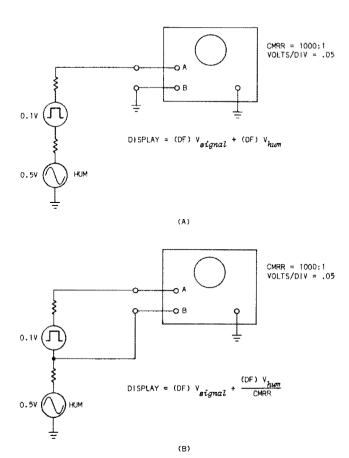

Almost all oscilloscopes use push-pull vertical and horizontal amplifiers. Push-pull CRT drive combats deflection nonlinearity. This is because single-ended drive develops a zero-volt equipotential surface near the grounded plate, while push-pull deflection centers the zero-volt equipotential surface between plates.

Consider a single-ended system with a positive signal voltage applied. An electron approaching the plates encounters positive equipotential surfaces; axial velocity therefore increases. Assume this results in two divisions of deflection above center.

Nonlinearity shows upon application of an equalamplitude opposite-polarity signal. An electron now decelerates as it approaches the deflection plates due to negative equipotential surfaces encountered. The beam then deflects further below center, perhaps by one division, than in the case above. Nonlinearity to this degree is unacceptable.

Push-pull voltages applied to both D1-D2 and D3-D4 eliminate nonlinearity of single-plate drive. Equal signal voltages of opposite polarity appear on the plates. Deflection voltage develops across the plates but the zero-volt equipotential surface remains centered between plates. An electron approaching the deflection plates encounters a surface approximating anode voltage. It then experiences neither acceleration nor deceleration. Deflection signals cause equal radial velocity either side of center.

Fig. 1-5. Linearity comparison.

Fig. 1-6. Locating the deflection-plate voltage gradient (not to scale).

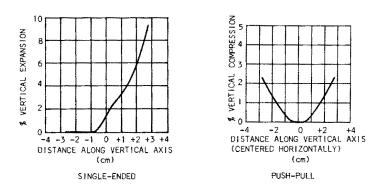

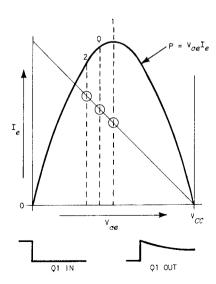

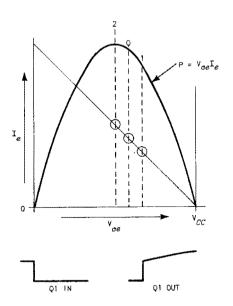

push-pull and singleended linearity contrasted Each type of CRT does exhibit characteristic nonlinearity. However, dramatic improvement results from push-pull drive. Compare the graphs of Fig. 1-5 to contrast the linearity between push-pull and single-ended deflection. These graphs are of the same tube type under nearly identical conditions. Even the linearity characteristics vary between drives. Push-pull suffers a low percentage of compression; single-ended creates unacceptable expansion.

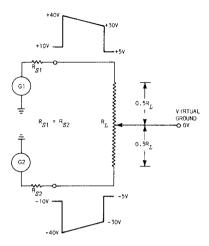

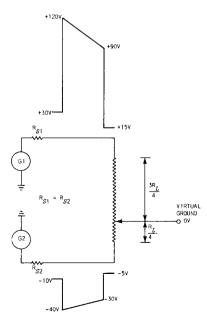

CRT design holds deflection-plate rest potential to specific limits. This calls for deflection amplifiers designed to operate around these levels.

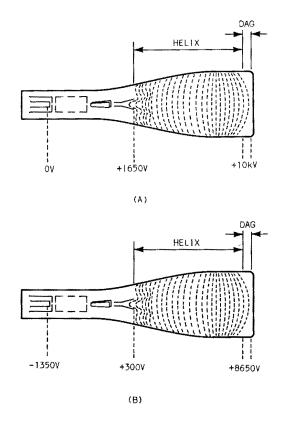

The voltage gradient between CRT cathode and aquadag (dag) creates the restrictive deflection-plate operating levels. Fig. 1-6A is a cut-away CRT which includes the equipotential surfaces in the postdeflection-acceleration (PDA) region. Gradients develop between the cathode and the low-voltage end of the helix. The deflection plates set in an area bisected by the 1600-to-1700-volt equipotential surface. To prevent severe distortion of surfaces in the PDA region, external deflection-plate leads should connect to a voltage source equal to the internal voltage environment -- in this case between 1600 and 1700 volts. Deflection amplifiers driving these deflection plates maintain quiescent deflection-plate voltage 1600 to 1700 volts above the CRT cathode.

Operating amplifiers above 1.5 kV is a bit unreasonable. This among other reasons, is why operating voltages are as shown in Fig. 1-6B. Operating with the cathode below ground reduces the positive operating level, required by the deflection plates, to a reasonable value.

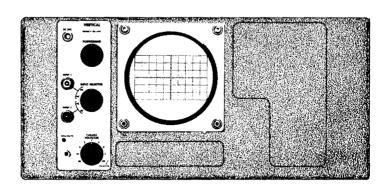

Fig. 1-7. Oscilloscope vertical controls.

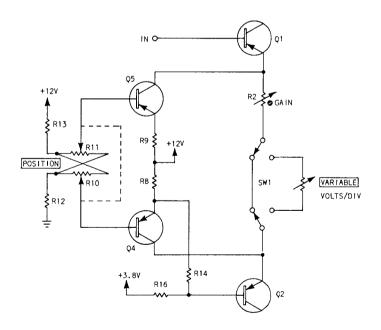

operating controls

Fig. 1-7 is a representative oscilloscope with all controls, other than vertical, blanked out. The instrument illustrated includes basic front-panel vertical-amplifier controls: Vertical POSITION, INPUT SELECTOR, VOLTS/CM selector and the VARIABLE control.

POSITIONIU &

Adjusting the vertical-POSITION control moves the CRT display up and down along Y axis. Centering the vertical POSITION and restricting the input to zero volts centers the vertical CRT display.

DEPUT SOURCEON

The INPUT SELECTOR allows the operator to choose either of two input connectors. It further extends his choice to a direct connection (DC) or capacitive coupling (AC) from input connector to vertical amplifier.

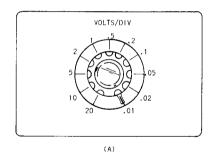

VOLTS/CM and VARIABLE mount on concentric shafts. The VOLTS/CM selector is shown as an input deflection-factor selector. One selects, in nine calibrated steps, input deflection factors between 0.05 V/cm and 20 V/cm. This is the deflection factor at the input connectors. The continuously adjustable VARIABLE provides between-step, uncalibrated, deflection-factor control: With the VOLTS/CM set to 1, the VARIABLE may set input deflection factor at any point between 1 V/cm and approximately 2 V/cm. This control slips into a detent at the extreme clockwise position allowing calibrated input deflection factor. Placing the VARIABLE in detent. one reads deflection factor as indicated by the VOLTS/CM selector. These controls and connectors are a part of circuits generally located in the vertical preamplifier.

vertical preamplifier

Subdividing vertical amplifiers into preamplifiers and main amplifiers helps simplify concept development. Two tests separate vertical preamplifiers and main vertical amplifiers: (1) Circuits which contain front-panel controls most commonly occur in preamplifiers, and (2) a vertical circuit into which a connector could be inserted to allow preamplifier plug-in capability is a main amplifier.

main vertical amplifier The main-vertical-amplifier tag evolved from main-frame vertical amplifier. The advent of plug-in capability required a vertical-amplifier separation—one portion removable and the other a permanent part of the oscilloscope main frame, thus the tag: main frame vertical. Common usage shortened the name by dropping "frame."

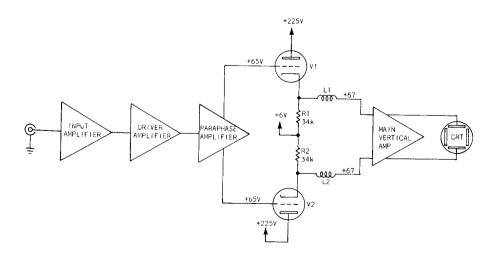

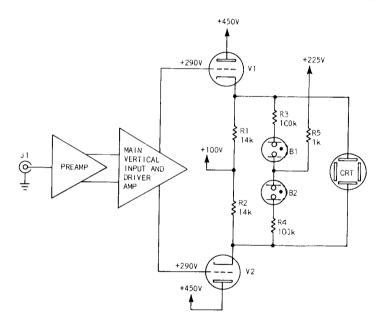

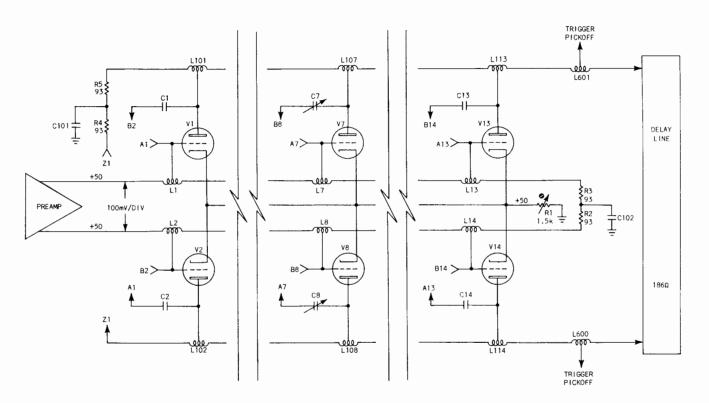

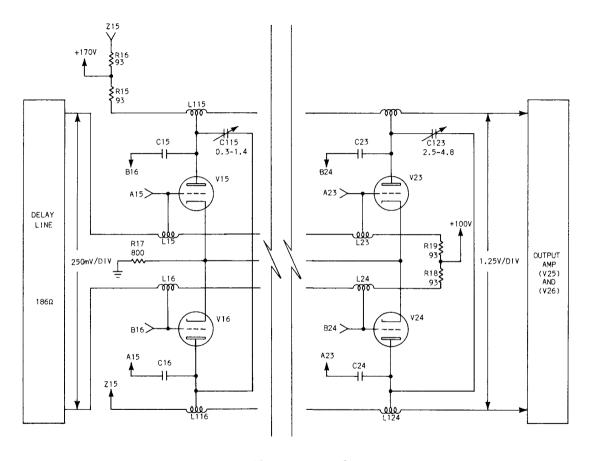

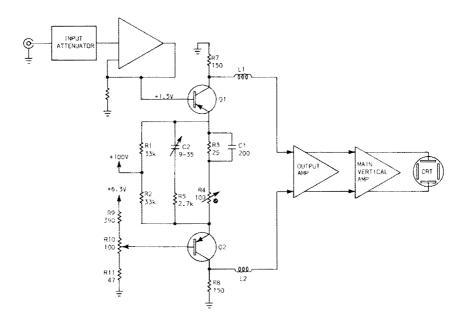

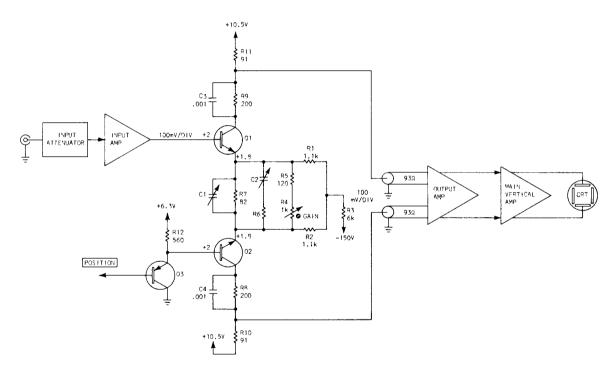

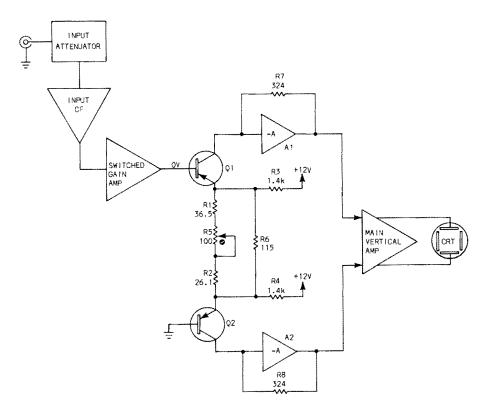

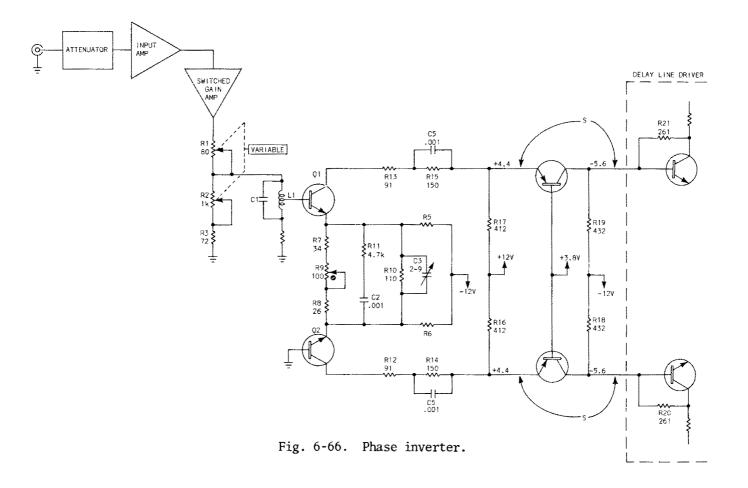

The vertical preamplifier acts upon signals appearing at the input connector. It then converts the signal to push-pull. Vertical preamps also provide gain as selected with the volts-per-division selector. Preamplifier gain is that necessary to provide a constant deflection factor at the preamplifier output. A push-pull signal of 100 millivolts-per-division is representative. The main vertical amplifier then is a push-pull amplifier of fixed gain. Amplification is as needed to match the constant input deflection factor to that of the CRT. An internal gain calibration frequently constitutes a part of the main vertical amplifier.

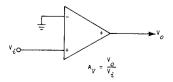

gain

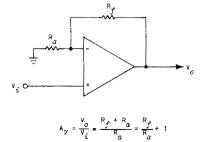

$$A_{v} = \frac{V_{o}}{V_{in}}$$

$A_{v} = \frac{DF_{o}}{DF_{in}}$

Gain in this book refers to voltage gain. Since oscilloscope vertical amplifiers are basically voltage-actuated devices, gain in terms other than voltage has little direct meaning. A simple expression, output voltage divided by input voltage, defines voltage gain. Substitute deflection factors for voltages in the gain ratio to determine required amplifier gain. As an example, assume the CRT deflection factor is 20 V/div and the VOLTS/DIV selector sets at 1 V/div. Ratio  $\frac{20 \text{ V/div}}{1 \text{ V/div}}$  expresses the required vertical-amplifier gain. Overall vertical-amplifier gain may be unity, less than unity or greater than unity.

One seldom refers to gain directly when describing the characteristics of a vertical amplifier. He does describe input deflection factor such as: the VOLTS/DIV selector of Fig. 1-7 allows selection of input deflection factors between 0.05 VOLTS/DIV and 20 VOLTS/DIV or, as used earlier, as an expression of amplifier sensitivity. This partially describes the limits or capabilities of the instrument.

bandwidth

Bandwidth expands oscilloscope descriptions. Bandwidth, applied to a specific vertical amplifier, defines the frequency limits of calibrated input deflection factors. That is, a one-volt input signal, to a vertical amplifier set at one volt-perdivision input deflection factor, deflects the CRT one division only if the signal frequency is within the capabilities of the vertical amplifier. Oscilloscope bandwidth specifications express frequency capabilities of the vertical amplifiers.

One type of Tektronix instrument is advertised as a DC-to-10 MHz oscilloscope. In the same advertisement, under vertical characteristic summary: bandwidth DC-coupled, DC to 10 MHz. AC-coupled, 2 Hz to 10 MHz. This specification should have the same meaning to everyone.

However, an oscilloscope vertical amplifier must also be capable of faithfully reproducing complex waveshapes, and this requires good transient response characteristics. Stated another way, we need to have a linear phase-versus-frequency response.

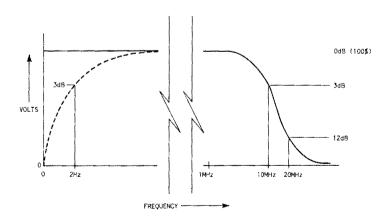

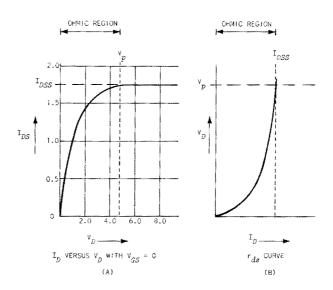

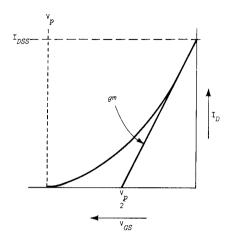

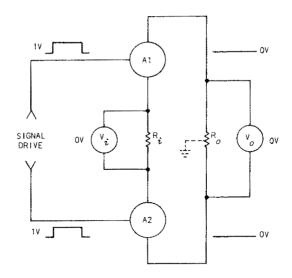

bandwidth plot Fig. 1-8 graphically shows the described bandwidth. One constructs a graph of this type by applying, to the vertical amplifier input, signals of varying frequency but constant amplitude. He then plots displayed amplitude versus input frequency. The solid line of Fig. 1-8 represents a bandwidth of DC-to-10 MHz. Displayed signal voltage remains essentially the same between 0 Hz (DC) and 1 MHz.

upperfrequency limit Refer to this as 0-dB attenuation. As the input frequency increases (input voltage held constant) the displayed signal amplitude decreases, reaching 70.7% of zero-hertz (DC) voltage at 10 MHz. Refer to this point as 3-dB attenuation. The upper-and lower-frequency 3-dB-down points define bandwidth. No lower-frequency 3-dB point appears

Fig. 1-8. Bandwidth curve.

Fig. 1-9. Expanded frequency curve.

on the solid line graph. This is characteristic of direct-coupled instruments. Thus, one frequently refers only to the upper-frequency limitation: "This is a ten-megahertz scope."

lowerfrequency limit A precise description of an AC-coupled instrument must include the lower-frequency 3-dB point. The dotted line on Fig. 1-8 follows the slope of low-frequency response. 3-dB attenuation occurs at 2 Hz. Midfrequency and high frequency remain as for direct-coupling. 2 Hz is a low frequency and the majority of general-purpose oscilloscopes must respond to DC. Therefore, the upper 3-dB-down frequency ( $F_{\mathcal{C}}$ ) receives greatest attention.

The bandwidth curve of Fig. 1-8 has neither square corners, nor does it actually achieve a flat top. Beginning at the lower (2 Hz) 3-dB point, the curve ascends from 70% of maximum to exceed 99% at 20 Hz. Response continues to ascend until reaching maximum, then descends again dropping to 99.5% at 1 MHz.

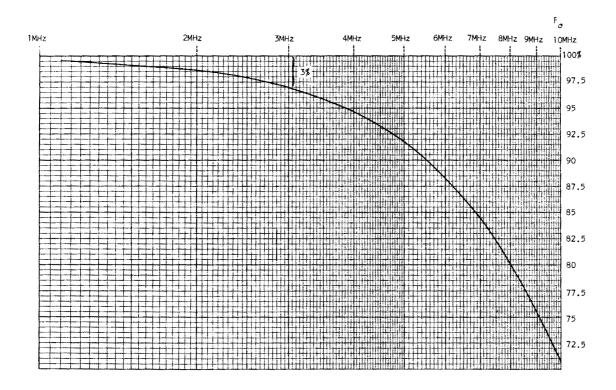

measurement errors Fig. 1-9 expands the upper frequency portion of the curve between 1 MHz and 10 MHz. This curve indicates that one experiences voltage display errors of discrete frequencies above 1 MHz: 0.5% at 1 MHz, 1.5% at 2 MHz, 5.5% at 4 MHz, 12% at 6 MHz, 20% at 8 MHz and 30% at 10 MHz ( $F_c$ ). This is why some use the "thumb rule of 5:" That the scope bandwidth should exceed the highest frequency to be measured by five. The error at 20% of cutoff ( $F_c$ ) is less than 2%. If one were satisfied with a 3% display error he could economize by using a scope whose  $F_c$  exceeded maximum measurement needs by 3.

Incidentally, the curve of Fig. 1-9 applies to most oscilloscopes. One need only apply F to the upper 3-dB point of his instrument and assign percentage values to the listed frequencies: 8 MHz is 80% of F, 6 MHz is 60% of F. . . . and 1 MHz is 10% of F. Using the chart to correct for display errors gives an accurate amplitude measurement of sinewayes.

One might wonder why he pays for frequency response he is not using. Why not provide him with a scope with a flat response between frequencies which then drops abruptly to zero? This would give him accurate displays within the specified frequencies and reject all frequencies above and below these limits. Actually he uses all of the bandwidth he buys. The proposed abrupt response considers only frequency not time delay or phase shift. Phase relationships come into play during reproduction of nonsinusoidal waveforms. Even persons concentrating exclusively on frequency domain areas seldom, if ever, encounter a pure sinewave. An aberration of interest or a circuit distortion, such as clipping, creates complex waveforms. Accurate display of these waveforms depends upon vertical-amplifier phase-gain characteristics.

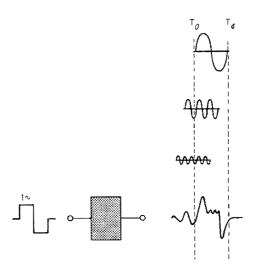

squarewave evaluation One method of performance evaluation applies periodic rectangular waveshapes (squarewaves) to the vertical-amplifier input. This allows one to demonstrate frequency and phase response of a vertical system.

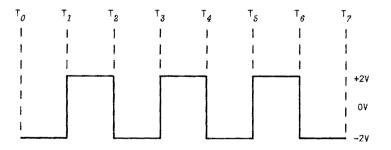

transient voltage Fig. 1-10 shows three cycles of a periodic rectangular wave. There are two theoretical methods of constructing a squarewave: the transient-voltage and sinewave method. In terms of transient-voltage method, the voltage of Fig. 1-10 remains set from  $T_0$  to  $T_1$  at -2 volts; changes abruptly at  $T_1$  to +2 volts; remains at +2 volts until  $T_2$  suddenly changes to -2 volts; the level remains at -2 volts until  $T_3$ , and so on.

Fig. 1-10. Squarewaves.

Fig. 1-11. The addition of successively higherorder harmonics to a fundamental sinewave to produce a close approximation of a squarewave.

frequency components

PLUS

PLUS

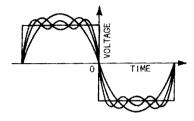

The sinewave method follows the assumption that a squarewave contains a number of frequencies. Fig. 1-11 shows the reproduction of a symmetrical squarewave. It shows three frequency summations superimposed on an "ideal" squarewave. First the fundamental sinewave establishes the basic rate. Next the third harmonic algebraically adds to the fundamental. Finally, the fifth harmonic adds to the waveform resulting from the first and third. This waveform only begins to resemble a squarewave. The corners are rounded and the top is not flat. Each additional harmonic sharpens the corners and flattens the top.

These harmonics bear both proper phase and amplitude relationship. As the fundamental frequency begins in a positive direction, all harmonics must also ascend. And at the completion of one fundamental cycle, as the fundamental intercepts zero amplitude from the negative, so must all harmonics. The fundamental completed 360°; the 3rd harmonic, 1080°; the 5th, 1800°; and so on through the odd-order harmonics.

Amplitude relationships must also be maintained. The 3rd harmonic is 1/3 of fundamental amplitude, the 5th is 1/5 and so on . . . .

A squarewave allows one to evaluate vertical amplifiers. For example, assume a "perfect" squarewave input appears on the CRT with rounded corners. Fourier analysis predicts higher harmonics sharpen the corners, therefore, the vertical amplifier suffers high-frequency attenuation.

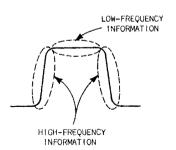

waveform contains frequency information Fig. 1-12 locates frequency information on one pulse. Notice that both the corners and vertical pulse excursions contain high-frequency information. Notice also the rounded pulse corners and vertical slopes. Properly extending an amplifier's frequency response preserves pulse corners, vertical slopes and "flat" tops.

time domain

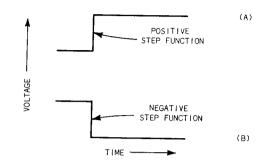

step function Time-domain studies are concerned with the transit time from one voltage level to another. When discussing time-domain methods one encounters the term step function. This waveform results when a voltage "steps" from one level to another. Fig. 1-13 illustrates the two forms of the step function. In Fig. 1-13A the voltage sets at a level then abruptly changes to and remains at a more positive level. Fig. 1-13B illustrates a transit to a more negative voltage. Both figures imply a single change in voltage.

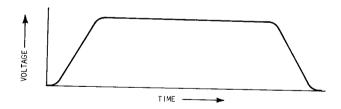

pulses as step functions Repetitive signals are generally more practical than single events. Thus, one finds periodic rectangular pulses used as step functions. Fig. 1-14 shows such a pulse. To consider pulses as step functions, pulse duration must be long compared to voltage level transit time.

Fig. 1-12. A summary of the low- and high-frequency information found in a squarewave.

Fig. 1-13. Positive-going and negative-going step functions.

Fig. 1-14. Positive and negative step functions.

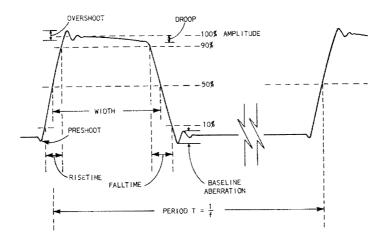

Fig. 1-15. Pulse shape.

How well vertical amplifiers reproduce ideal step functions is a measure of performance. Step functions of Fig. 1-14 are ideal, voltage transition occurs in zero time. Applying the "ideal" step to a vertical amplifier results in a display having rounded corners and a slope to voltage excursions. Fig. 1-15 shows such a response.

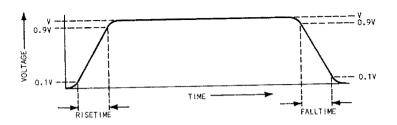

risetime

The term *risetime* refers to voltage-level transition time. Risetime applies to either positive or negative step response. However, a displayed negative excursion is popularly termed *falltime*.

falltime

One measures risetime along a portion of the slope only. Initial and final portions of an excursion make close measurement arbitrary, at best. Risetime refers to only the middle 80% of a step function. Fig. 1-16 illustrates proper oscilloscope risetime measurement. This figure indicates risetime as the transit time between 10% of maximum voltage and 90% of maximum voltage.

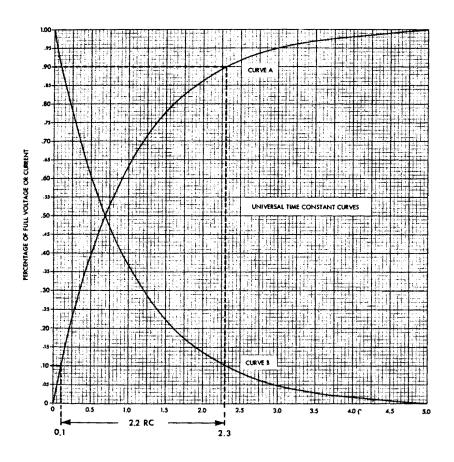

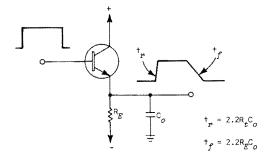

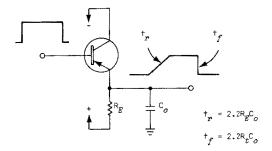

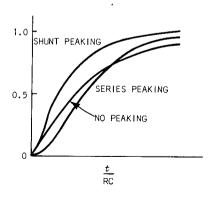

2.2 RC

Applying a step function to an RC network results in risetime dependent upon network time constant. The leading edge follows an RC curve, such as shown in Fig. 1-17. Risetime resolves to 2.2 RC: 10% of maximum occurs in 0.1 RC and 90% in 2.3 RC, the difference is 2.2 RC.

Risetime  $(t_r) = 2.2 \text{ RC}$ .

Fig. 1-16. Pulse measurement.

Fig. 1-17.

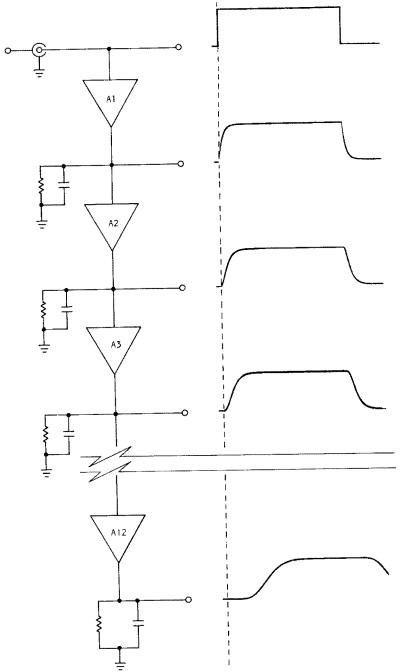

Fig. 1-18. Cascaded RC amplifier response to an ideal step.

A solitary RC circuit response is fairly easy to visualize. But, how does a cascade of RC amplifiers react to an approximation of the ideal step?

Ultimate risetime occurs later, rises slower and assumes a new shape. Fig. 1-18 shows these effects. Consider each amplifier increment:

- Input -- The amplifier input step has zero risetime, both 10% and 90% points occur at  $T_{ij}$ .

- Al -- Output risetime follows the curve of a universal time constant. Risetime increases and a small delay occurs.

The step reaches 10% at 0.1 RC ascending to 90% 2.2 RC later. This is the input to A2.

- A2 -- A2 receives an input with a varying change-of-voltage-per-unit-time. The output, developing across an RC network, ascends to 10% at a different slope rate. A small curve develops.

A greater time also lapses between 10% and 90%.

- A3 -- The 10% point here occurs still later and risetime (tp) again increases. At this output the curve between minimum amplitude and 10% begins to resemble the curve between 90% and maximum amplitude. This condition continues with each stage contributing an increase in time delay and risetime. And with each stage the upper and lower step halves approach mirror-image shapes. After an infinite number of stages the step in fact assumes a mirror-image shape.

- Al2 -- Here there is a considerable delay between T<sub>O</sub> and the 10% point.

Risetime has noticeably increased and response appears to be symmetrical about the 50% point.

The curve between minimum and 10% approximates the curve between 90% and maximum. This approximates a gaussian step response.

Fig. 1-19. Step response.

Fig. 1-20. System risetime results from individual amplifier risetimes:  $t_r^2 = t_{r1}^2 + t_{r2}^2 + t_{r3}^2$

Fig. 1-19 compares a gaussian and an RC step response of equal risetime. The RC step rises abruptly, at an almost linear rate, from zero to 10%. Rate of rise then changes, requiring as much time from 90% to 99% as from zero to 90%.

On the other hand, gaussian responses rise from zero to 10% more slowly, assuming an almost linear slope between 10% and 90%, then ascend the last 10% in a curve equal to the first 10%.

Oscilloscope vertical-amplifier step response, except for a few specialized types, falls between the RC and the gaussian. Gaussian responses receive more detailed treatment later. For now, realize that a true gaussian amplifier is impossible. Vertical amplifiers do, however, very closely approach a gaussian response.

When an ideal step function passes through amplifiers in cascade, each amplifier contributes to risetime deterioration in a predictable manner. Fig. 1-18 showed this pictorially but failed in indicating predictability. Refer to Fig. 1-20 and assume the following conditions: An ideal step-function applied to a vertical input passes through two cascaded amplifiers and is displayed on a CRT. One predicts displayed risetime by applying the formula:

$$t_r = \sqrt{t_{r1}^2 + t_{r2}^2 + t_{r3}^2}$$

where:

t<sub>p1</sub> = risetime of the preamplifier

operating alone.

$t_{n2}$  = risetime of the main amplifier alone.

$t_{n3} = CRT \text{ risetime.}$

For example, assign values:

$t_{r1} = 3$  microseconds

$t_{r2} = 4 \text{ microseconds}$

$t_{m3} = 10$  nanoseconds

$$t_r^2 = (3 \times 10^{-6})^2 + (4 \times 10^{-6})^2 + (10 \times 10^{-9})^2$$

$\approx (9 + 16)10^{-12}$

$t_r = \sqrt{25 \times 10^{-12}} = 5 \times 10^{-6}$  seconds

Displayed risetime resulting from an ideal step function is about 5.0 microseconds.

vertical

risetime

must be

less than

test device

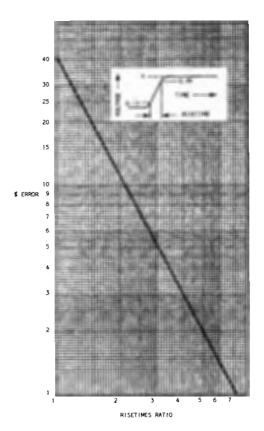

One now might ask, how can an oscilloscope user measure risetime? To do so the oscilloscope vertical amplifier must have a risetime much less than the device being measured. Suppose one wishes to display a given waveform. He also requires the displayed waveform to be within 2% of the input waveform. Fig. 1-21 indicates oscilloscope performance for the required result. For example, 2% (Y axis) intercepts the graph slope at the ratio of 5 (X axis). This tells an operator that to observe a 50-nanosecond risetime waveform, with 2% accuracy, his oscilloscope must have 10-nanoseconds risetime or less.

Fig. 1-21 was calculated from the square root of the sum of the squares equation. A modification of this formula allows one to determine true risetime of a circuit under test:

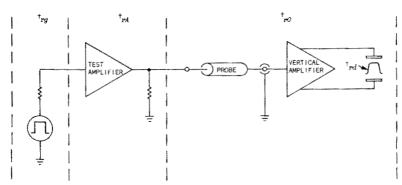

$$t_{rA}^2 = t_{rg}^2 - t_{rd}^2 - t_{rO}^2$$

where:

$t_{nA}$  = Amplifier risetime (amplifier under test).

$t_{nd}$  = Displayed risetime.

$t_{rg}$  = Risetime of the squarewave generator (or other source).

$t_{nO}$  = Oscilloscope vertical-amplifier risetime.

Using these calculations one moves from "ideal" restrictions to reality. Fig. 1-22 shows a possible condition. A squarewave generator develops the step function with risetime,  $t_{rg}$ . The amplifier under test increases risetime as does the vertical-amplifier system. All devices contribute to risetime displayed,  $t_{rd}$ . Thus an operator must know the risetime of the step-function source and his oscilloscope from the probe tip. He then substitutes the known and measured values into the formula for true risetime of the amplifier under test.

Fig. 1-21. Percent error in risetime measurement (Y axis) plotted against ratio of input waveform risetime to oscilloscope risetime (X axis).

Fig. 1-22. Factors determining actual risetime of a circuit under test.

е

s

One note of caution about oscilloscope risetime. One Tektronix oscilloscope type, specified at 7 ns, actually meets a performance of 6 ns or better when it leaves the factory. On the other hand, instrument risetime can be considerably degraded without user awareness. Whether due to conservative specifications or eroded performance, the calculations may be in error. Measure your instrument performance.

risetimebandwidth product Vertical amplifiers have so far been considered from two standpoints, risetime and bandwidth. A definite relationship exists between risetime and bandwidth. This is expressed as a constant, K, equal to the risetime-bandwidth product:  $t_P \cdot bw = K$ . K = 0.35 in the case of RC amplifiers. K results from a combination of the risetime formula and the -3 dB frequency formula:

$$t_{n} = 2.2 RC$$

and

$$F_C = \frac{1}{2\pi RC}$$

or  $RC = \frac{1}{2\pi F_C}$

substituting,

$$t_p = 2.2 \left(\frac{1}{2\pi F_c}\right) = \frac{2.2}{2\pi F_c} = \frac{0.35}{F_c}$$

$$t_{n}F_{c} = 0.35$$

If one considers  $\mathbf{F}_c$  as bandwidth then:

$$t_{p} \cdot bw = 0.35$$

gaussian circuits The above derivations apply only to an amplifier whose bandwidth is RC limited. Cascading a number of such amplifiers or proper compensation in a single-stage amplifier results in an essentially gaussian response. In this case the risetime-bandwidth product also partially describes the amplifier.

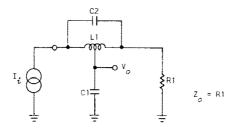

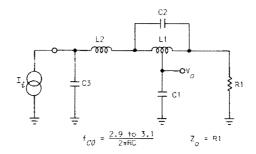

A true gaussian response resolves to  $t_r \cdot bw = 0.32$ . Because of several factors oscilloscope amplifiers don't meet the requirement for true gaussian response. "Gaussian" circuits are thus essentially gaussian. Empirical products, arrived at through years of research, define these "gaussian" circuits. For a gaussian response,  $t_r \cdot bw = 0.35$  to 0.45. Higher products indicate least risetime. However, overshoot

accompanies the risetime reduction. A product of 0.45 results in about 5% overshoot and when  $t_p \cdot bw = 0.35$  there is little, if any, overshoot in the step response. Tektronix usually establishes the product at K = 0.35, sacrificing risetime for minimum overshoot.

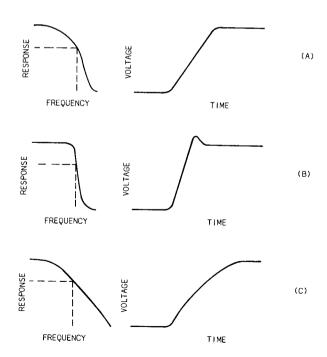

Fig. 1-23 compares relative bandwidth rolloff to step response. The bandwidth rolloff of Fig. 1-23A approximates gaussian. Step response, symmetrical about the 50% point, exhibits fastest rise without overshoot.

overshoot

s

Overshoot appears in Fig. 1-23B. In this figure upper frequency response falls off too steeply to be gaussian. Step response rises above then returns to 100% voltage level. This is called overshoot. Frequently associated with overshoot, a damped

Fig. 1-23. Bandwidth versus frequency.

e.

t

oscillation may appear along the top of the wave. A few percent overshoot can represent an acceptable level when optimizing a system for least risetime.

slow rise

In Fig. 1-23C, the frequency-response curve falls off too slowly. The corresponding step response takes undue transit time.

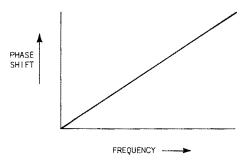

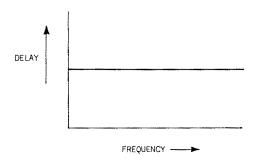

phase shift linear The gaussian rolloff expresses step-function response because of frequency-phase relationships. A circuit must impose two related phase characteristics for optimum step response: A linear shift with frequency or all frequencies equally delayed. Reactive components which attenuate also affect a phase shift. Impedances with gaussian attenuation shift phases linearly with frequency.

Fig. 1-24. Phase shift linear with frequency.

Fig. 1-25. Delay constant with frequency.

group delay Fig. 1-24 shows phase shift-frequency relationship necessary for gaussian response. For optimum step response all frequency components must be equally delayed (Fig. 1-25). In other words, the frequency components of a pulse transiting a gaussian network experience phase shift increasing linearly with frequency. Also, all pulse-forming frequencies arrive at the termination simultaneously.

Now that a vocabulary has been established, a much more compact statement will summarize the amplifier description. Completely describing a linear amplifier by means of steady-state sinewave testing requires two plots:

- 1. Amplitude versus frequency, and,

- 2. Phase versus frequency.

Theoretically, given the amplitude and phase characteristics, one can calculate step response.

The most common input for amplifier testing is the step signal. This describes a linear amplifier by means of the time response to any input signal. Complete step response contains all of the information that amplitude and phase plots contain.

Theoretically, given a complete step response one can calculate the amplitude and phase characteristic. The tool used to deduce one information set from the other is the Fourier transform. Frequency response (amplitude and phase versus frequency) is the Fourier transform of an impulse response. The impulse response is basically the time derivative of the step response.

The step response of an amplifier with abrupt upper-frequency rolloff contains both preshoot and overshoot. Fig. 1-26A.

Nonlinearity of the phase characteristic adds distortion. Fig. 1-26B shows three types of phase characteristics. These are plotted in terms of phase and delay:

- a. Ideal,

- b. Insufficient delay of high frequencies,

- Peaks, or excessive delay at high frequencies.

Fig. 1-26C approximates the step response resulting from nonideal phase characteristics.

Fig. 1-26. Frequency response -- step-response interdependence.

These interrelationships can also be demonstrated by shifting and attenuating the harmonic content of a squarewave.

Fig. 1-27 shows three of many frequency components contained in a squarewave. The fundamental completes one cycle between  $T_0$  and  $T_4$ ; during the same interval the 3rd harmonic completes three cycles; the 5th completes five and so on through all odd harmonics. This relationship must be maintained for squarewave reproduction. Should the fundamental be shifted 90° ( $T_2$ ) the third harmonic must shift 270° and the 5th 450°.  $3 \times 90 = 270$ ,  $5 \times 90 = 450$ . Further, to maintain this phase relationship all frequency components must be delayed equally: If the fundamental is delayed  $5 \mu s$ , then all harmonics must also be delayed  $5 \mu s$ .

Fig. 1-27. Equal group delay.

Fig. 1-28. Unequal group delay.

Fig. 1-29. Pulse nomenclature.

unequa l group delay Fig. 1-28 represents the results of unequal delay. High frequencies transit the network faster than low frequencies. High-frequency energy appears to arrive at the output before  $T_{\mathcal{O}}$ . A distorted output waveform results. In this figure the output waveform was approximated using only a few odd harmonics to show aberrations preceding the main output pulse.

These requirements for linear phase shift or flat delay apply to all waveshape reproduction.

risetime

Apply the nomenclature covered to the simulated display of Fig. 1-29. Risetime measurements occur along the leading edge of the pulse, falltime at the trailing edge. The terms risetime and falltime become ambiguous on an inverted pulse. Therefore, risetime is always measured along the leading edge. Pulse width and pulse-recurrence time are both

falltime

pulse width

aberrations

baseline

shift

preshoot

overshoot

droop

This illustration includes fast and slow deviations.

Fast deviations appear as baseline and top

measured at the 50% amplitude points.

aberrations. Droop (tilt) indicates slow deviations. In this case the vertical amplifier apparently imposes unequal frequency delay: High frequencies

transit faster than low, creating preshoot.

Overshoot also results since unequal group delay makes linear phase shift impossible. Droop is also an unequal group delay indicator. Droop shows

excessive low-frequency delay. The baseline ringing, like overshoot, occurs during nonlinear

phase shift/frequency relationships.

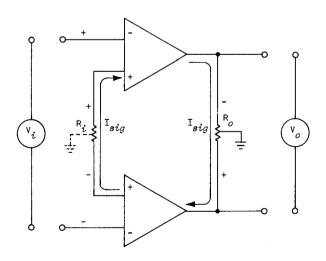

Fig. 2-1. Vertical amplifier.

## INPUT CIRCUITS AND COMPENSATED ATTENUATORS

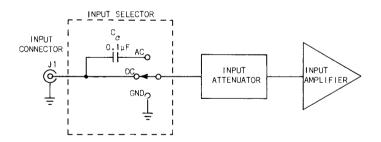

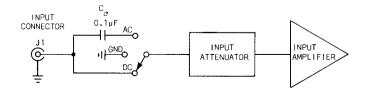

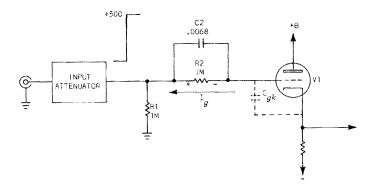

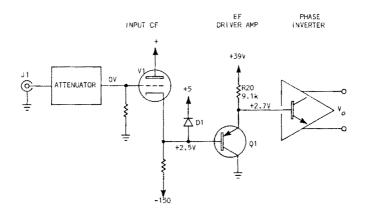

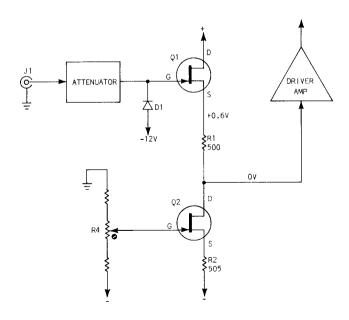

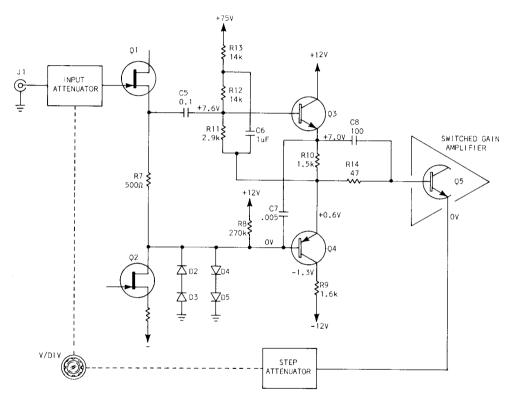

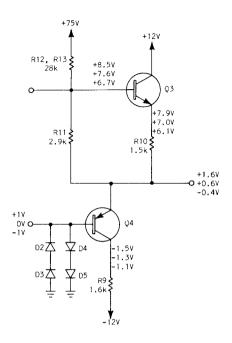

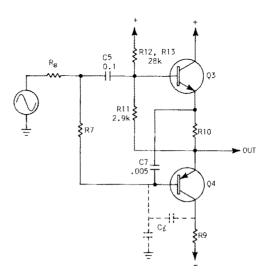

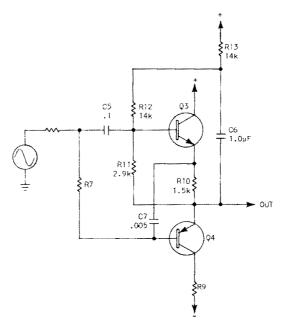

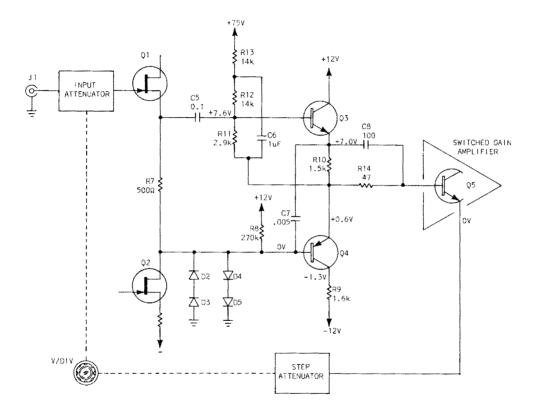

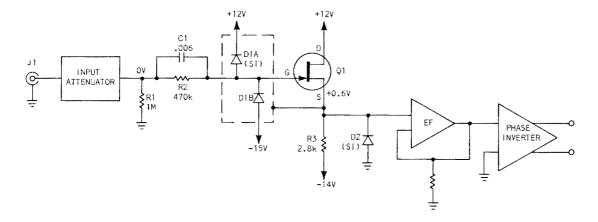

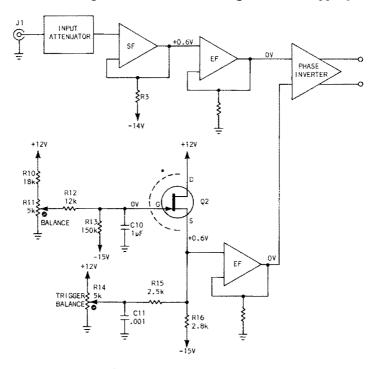

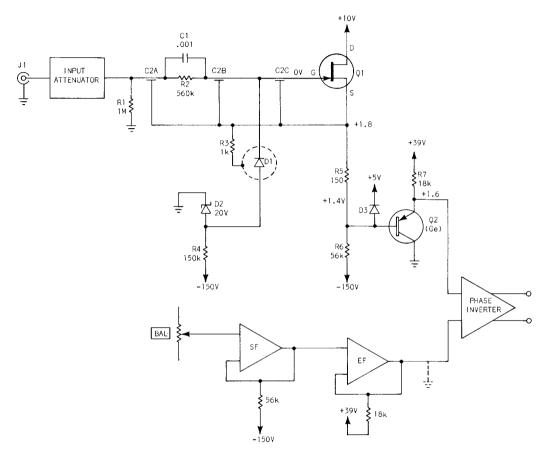

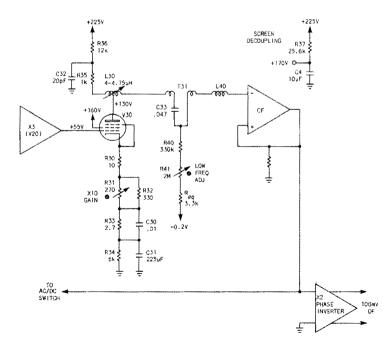

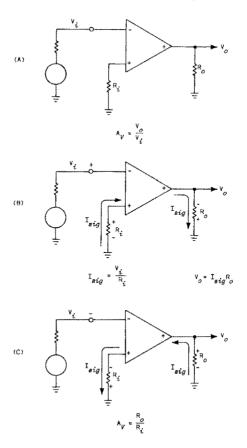

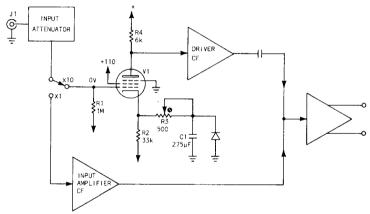

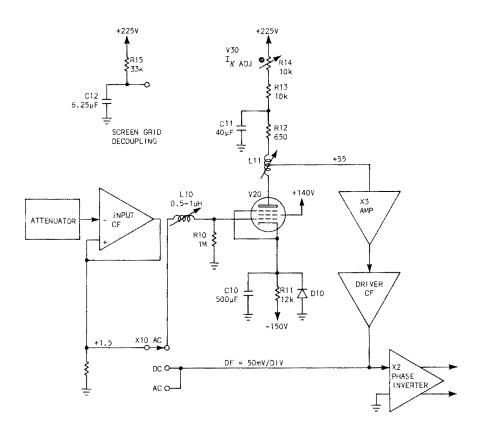

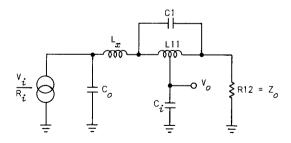

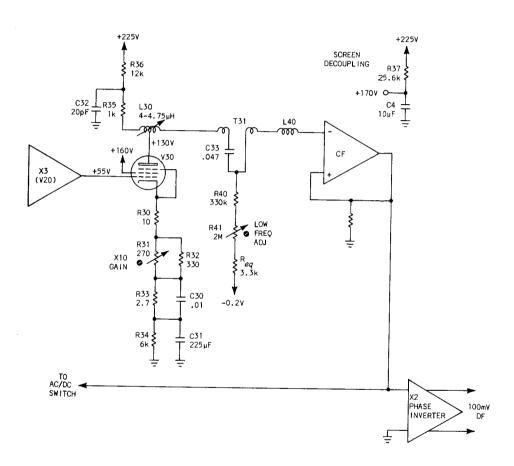

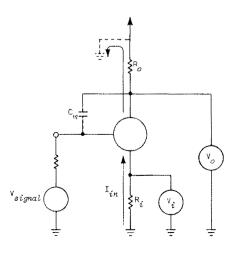

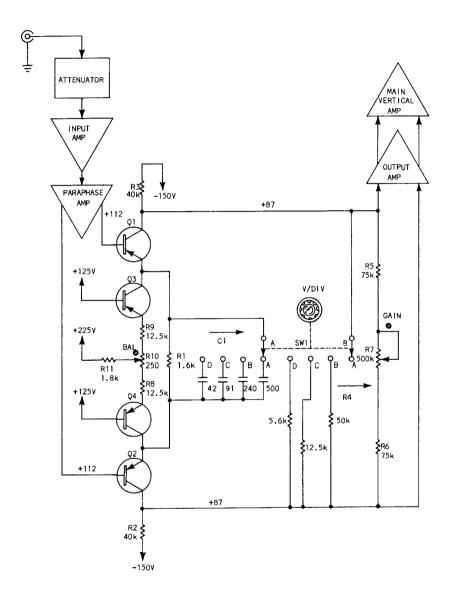

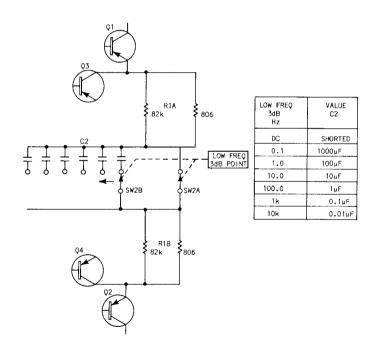

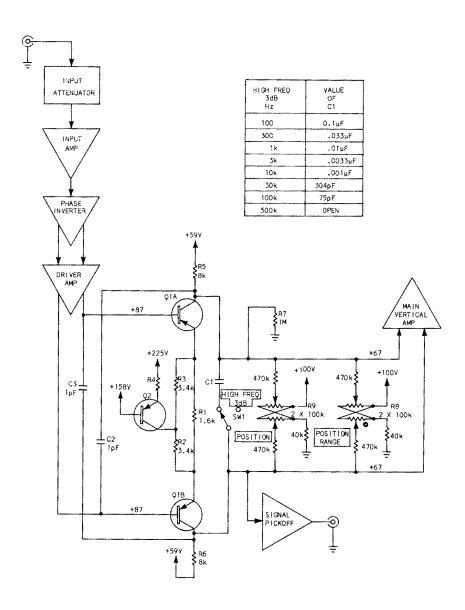

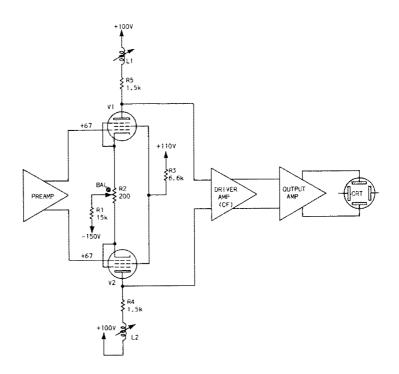

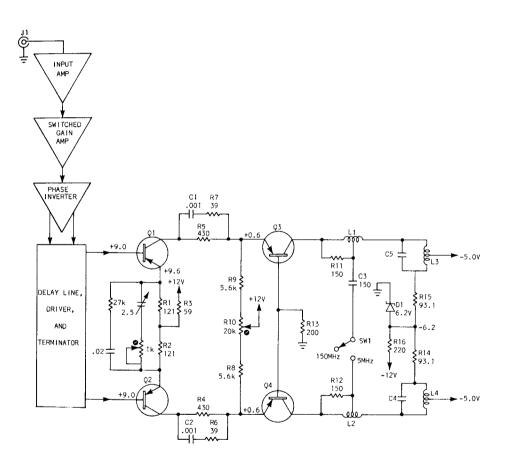

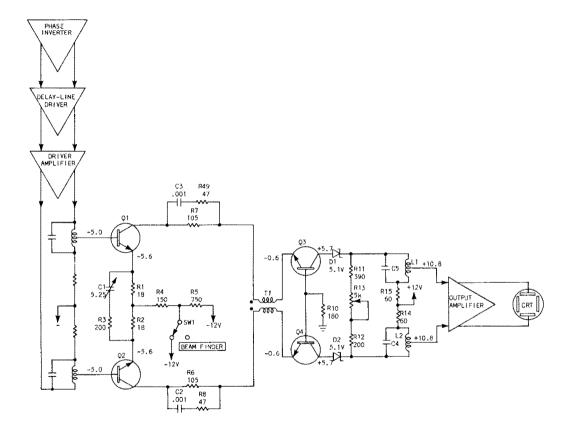

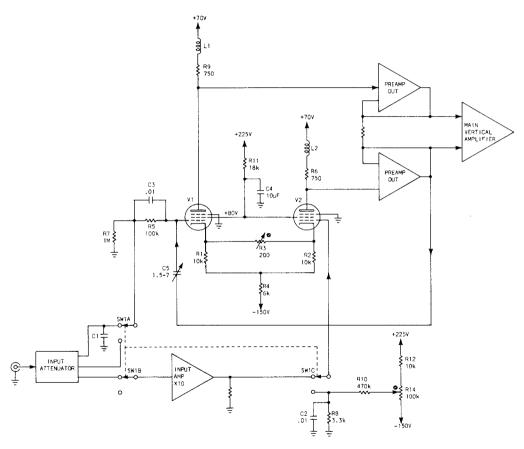

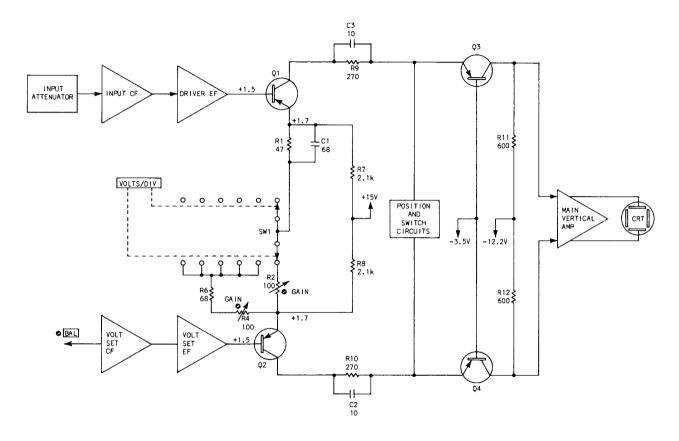

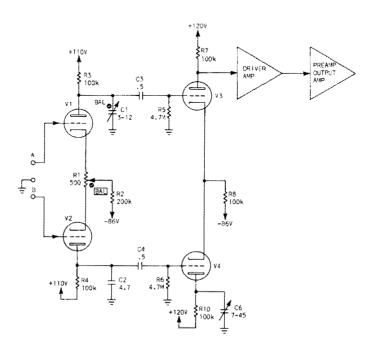

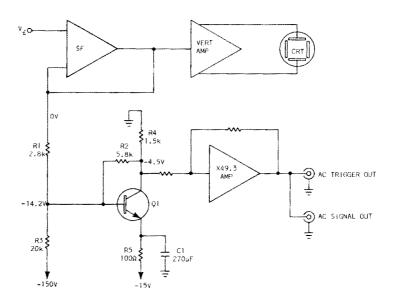

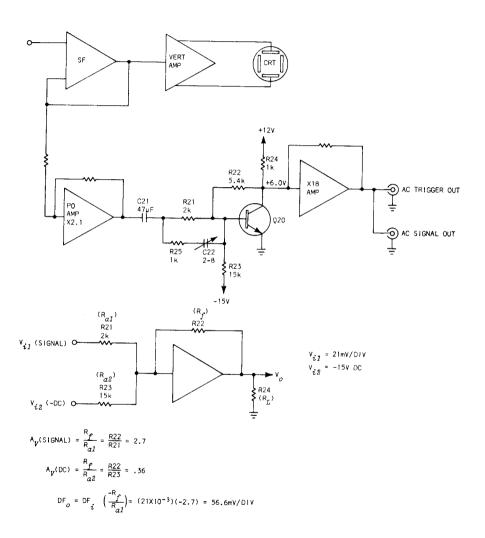

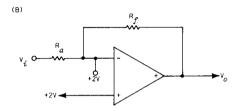

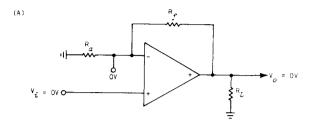

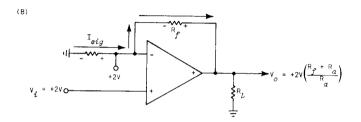

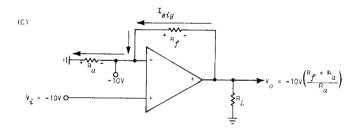

The first vertical circuits to affect an input signal are the input selector and input attenuator. Fig. 2-2 shows an input selector, attenuator and input amplifier block.

The INPUT SELECTOR determines lower-frequency bandwidth. Placing the input selector to AC capacitively couples signals, appearing at input connector J1, to the input attenuator. Switching to GND opens J1 and grounds the attenuator input. DC, the position shown, directly connects the attenuator to J1.

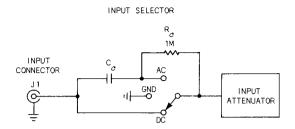

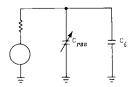

switching logic Fig. 2-3 shows improved switching logic. As an operator switches from DC to AC he grounds the input attenuator temporarily. This action discharges

Fig. 2-2. Input-selector switching.

Fig. 2-3. Improved input-selector switching.

input attenuator capacitance, reducing the quantity of  $C_{\mathcal{O}}$  charge current which must flow through the attenuator networks.

input charge current Some consider the input circuit charge current negligible -- not so! There have been instances of switch contact destruction. Consider the effects of the following sequence: An oscilloscope user checks or sets the level of the -150 volt supply. The input selector is set to DC. He then decides to measure ripple content of the +150 volt supply. To do this he removes the probe from the -150 volt supply, switches to AC and connects the probe to the +150 supply.

${\rm C}_{\mathcal{C}}$  in Fig. 2-2 initially charges toward 300 volts. The input attenuator contains -150 volts charge and +150 appears at input connector Jl.

In Fig. 2-3, charge current is reduced by half. When the input selector moves from DC to AC it contacts GND, removing stored charge in the input attenuator.  $C_{\alpha}$  charges to the applied voltage.

The user certainly can reduce charge current by placing the input selector to GND between measurements. The circuit in Fig. 2-3 removes this memory burden.

${\rm C}_{\mathcal C}$  charge current flows through the attenuator in both cases. The vertical amplifier reacts during charge time as though a signal were applied. At best, this causes a measurement delay while the display follows the changing input charge signal. Further,  ${\rm C}_{\mathcal C}$  could have retained an additive charge from some previous measurement. This is because  ${\rm C}_{\mathcal C}$  is an open circuit in input selector positions other than AC. Adding a resistor to the circuit in Fig. 2-3 from the AC contact to the attenuator would close the loop in any input selector position.

Fig. 2-4 includes resistance  $R_{\mathcal{C}}$  which closes the  $C_{\mathcal{C}}$  charge path.  $C_{\mathcal{C}}$  charges to the input voltage through  $R_{\mathcal{C}}$  with DC or GND selected. Selecting AC shorts  $R_{\mathcal{C}}$  to prevent unnecessary attenuation of input signals. This accomplishes two purposes: First, it reduces the charge current through the attenuator and the switch contacts; second,  $C_{\mathcal{C}}$  cannot contain an unknown captive charge.

Fig. 2-4. Providing  $C_c$  an additional charge path.

Fig. 2-5. Input circuit of a vertical system.

fixed input RC Oscilloscopes have a fixed input RC. The attenuator changes the input deflection factor (volts per division) but not the input RC. Maintaining a constant RC eliminates probe recompensation with attenuation changes.

probe

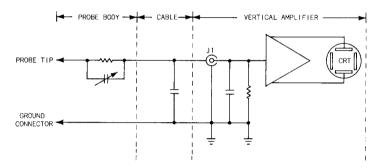

One must couple the signal of interest to the vertical-amplifier input. Simple test leads work for some low-frequency applications. Generally, use of an oscilloscope probe results in greater convenience and accuracy. Assume the probe is connected to J1 of Fig. 2-4 and the selector switch positioned to DC.

Fig. 2-5 represents circuit equivalents of the probe and vertical-amplifier input. The probe body consists of a resistor shunted by a variable capacitor. A single capacitor represents distributed cable capacitance. An RC network appears to the right of Jl. This parallel circuit is the fixed-input time constant of the vertical amplifier.

$V_{in}$

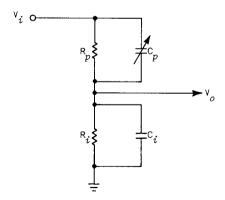

Lumping fixed cable and vertical-amplifier input capacitance evolves the circuit of Fig. 2-6. In this figure  $V_{in}$  represents the signal of interest;  $V_O$  the vertical-amplifier signal;  $R_D$ , probe resistance;  $C_D$ , probe capacitance;  $R_i$ , vertical-amplifier input resistance;  $C_i$ , vertical-amplifier input and cable capacitance.

Fig. 2-6 is a compensated voltage divider as long as time constant  $R_{\mathcal{C}}C_{\mathcal{C}}$  equals time constant  $R_{\mathcal{C}}C_{\mathcal{C}}$ .  $C_{\mathcal{C}}$  and  $C_{\mathcal{C}}$  form a capacitive divider creating voltage division across the capacitors equal to the division

attenuation ratio across  $\mathbf{R}_p$  and  $\mathbf{R}_i$ . Ratio  $\frac{\mathbf{R}_p + \mathbf{R}_i}{\mathbf{R}_i}$  defines basic DC attenuation.  $\mathbf{C}_p$  and  $\mathbf{C}_i$  form a capacitive divider of the same ratio so that the resultant time constants equal,  $\mathbf{R}_p\mathbf{C}_p = \mathbf{R}_i\mathbf{C}_i$ .

compensation

An adjustable  $\mathbf{C}_p$  allows one to adjust the probe time constant to match a specific vertical-amplifier-input time constant. This probe compensation must take place each time one connects the probe to an oscilloscope since input capacitance varies between instruments. Examples of input-time-constant specifications are listed below:

1 MΩ x 15 pF 1 MΩ x 20 pF 1 MΩ x 24 pF 1 MΩ x 33 pF 1 MΩ x 47 pF.

The listing shows a wide variation of input RC between different type oscilloscopes. Oscilloscopes of one type also vary, but to a much lesser degree. For a specific vertical amplifier one need compensate the probe once only. An input attenuator must be designed and calibrated to meet this criteria.

Compensated voltage dividers create a number of misunderstandings. Therefore, one needs to imbed the concepts of compensated voltage dividers in his mind. Fig. 2-6, the equivalent probe-scope input

circuit, contains the basic compensated voltagedivider components. And probe compensation offers an oscilloscope user a vehicle for demonstrating the effects of voltage-divider compensation.

Some say that a compensated voltage divider presents a constant impedance. No! Impedance ratio remains constant, but total impedance changes with frequency. Compensating a voltage divider sets up an impedance ratio independent of frequency.

Input voltage  $(V_{in})$ , Fig. 2-6, develops across an impedance  $(Z_T)$  which changes with frequency. The impedance of the probe  $(Z_p)$  and of the input  $(Z_i)$  also changes but when compensated, the ratio remains constant. This occurs when the RC time of one network matches the RC time of the other network:  $R_pC_p = R_iC_i$ .

If  $R_p = 9$  M $\Omega$ ,  $R_i = 1$  M $\Omega$ ,  $C_p = 2.2$  pF and  $C_i = 20$  pF, then  $R_p C_p = R_i C_i$ .

Fig. 2-6. Equivalent input circuit of a vertical system.

Fig. 2-7. Effects of probe compensation.

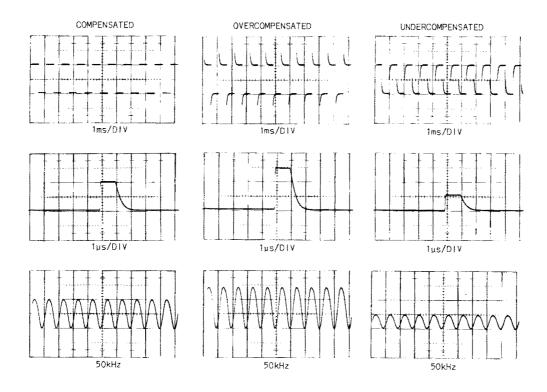

correctly compensate

Fig. 2-7 demonstrates the effects of probe compensation. To compensate his probe one connects to a squarewave source, such as the calibrator output on most oscilloscopes. These pulses may be much slower than the vertical amplifier system. Compensate the probe by adjusting for fastest risetime without overshoot. Accurate measurements are now possible whether they be pulses or high-frequency sinewaves — within the instrument risetime—bandwidth limits.

overcompensated Overcompensation shows as overshoot in the calibrator waveform. Both narrow pulses and discrete high frequencies appear larger than life.

undercompensated Rounded calibrator waveforms indicate undercompensation. Narrow pulses and high-frequency sinewaves suffer excessive attenuation.

Notice that neither the sinewaves nor narrow pulses change shape. This is one of the dangers. Overall waveshape does not necessarily indicate proper probe compensation.

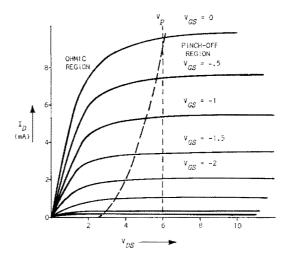

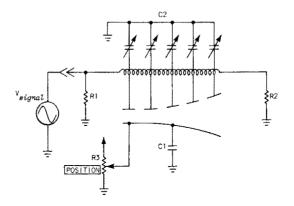

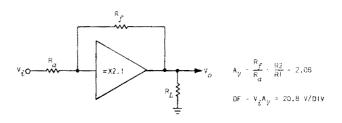

The probe offered a logical circuit point to describe compensated voltage dividers. Mentally disconnect the probe and consider input attenuators alone. The input attenuator consists of selected voltage dividers controlled at the front panel by the VOLTS/DIVISION selector. The VOLTS/DIVISION selector is calibrated in terms of deflection factor at the input connector. To expand the discussion of input attenuator functions, assume the following vertical-amplifier conditions:

- 1. 33 pF x 1 M $\Omega$  specifies the fixed time constant at the input connector.

- 2. DC selected by the INPUT SELECTOR.

- 10 millivolts per division is the basic input deflection factor.

- 4. The VOLTS/DIVISION selector steps in a 1-2-5 sequence; 0.01, 0.02, 0.05, 0.1, 0.2, 0.5, 1, 2, 5, 10 and 20 V/div.

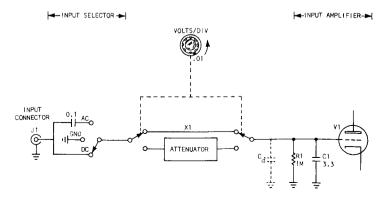

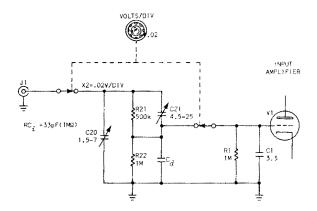

X1

X2

distributed capacitance

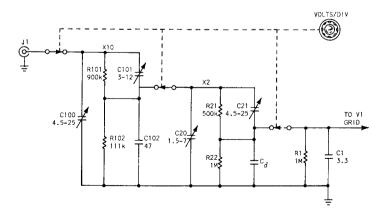

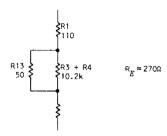

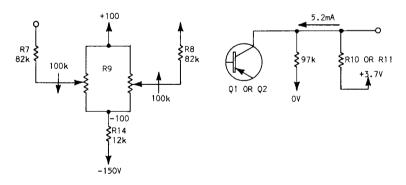

The above assumptions relate to Fig. 2-8. To the right of the attenuator block is the grid RC of input amplifier, V1. R1 and C1 remain in the circuit at all times. They always form a part of the attenuator network. All network switching, however, takes place in the attenuator block. Placing the VOLTS/DIV selector to 0.01 switches the attenuator to X1. Selecting X1 attenuation directly connects the top of R1 to the input. Distributed capacitance ( $C_d$ ) forms an appreciable portion of the input RC, and specified at the input: 1 M $\Omega$  must shunt 33 pF. R1 meets the resistive requirement, but C1 contributes only 3.3 pF.  $C_d$  then must appear as 31.7 pF:

$RC_i = 1 \text{ M}\Omega \times 33 \text{ pF}; R1 = 1 \text{ M}\Omega; C1 = 3.3 \text{ pF}; 33.0 - 3.3 = 29.7 \text{ pF}.$

Consider distributed capacitance a component in all vertical-amplifier input circuits.

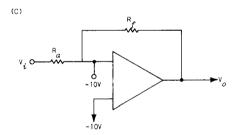

Selecting 0.02 VOLTS/DIV switches the attenuator to X2 voltage attenuation. Fig. 2-9 shows the X2 attenuator schematic. Signal voltage applied to J1 appears at the top of C20, R21 and C21. 50% of the input voltage develops at the grid of V1.

Basic attenuation consists of R21, R22 and R1. 500 k, total resistance of parallel network R22-R1, matches the resistance of R21. Resistance, thus voltage, division is equal. 1 M $\Omega$  appears from J1 to ground.

Fig. 2-8. X1 input attenuation.

Fig. 2-9. X2 input-voltage division.

voltage divider compensation Cl and parallel distributed capacitance ( ${\rm C}_d$ ) shunt the lower divider leg. One adjusts C21, across R21, to match the upper leg RC to the lower leg RC.

input compensation Input RC = 33 pF x 1 M $\Omega$ . Switching to X2 maintained input resistance but altered capacitance. C20 shunts this network providing adjustment for 33-pF total input capacitance. Although C $_d$  changed due to stray capacitance at the input lead, the input C altered mainly from the series effect of C21 with C $_d$  and C1:

$$C_i = \frac{C21(C_d + C1)}{C21 + C_d + C1}.$$

C20 shunting the attenuator thus raises total input shunt capacitance to the standardized value:  $C_2 + C20 = 33 \text{ pF}.$

Moving the VOLTS/DIV selector through its range step-selects additional attenuator networks of appropriate ratios. All of the attenuator networks use the same concept: Simple RC voltage dividers which maintain a set ratio to one another and present to the input a resistance of 1  $M\Omega$  and a capacitance of 33 pF.

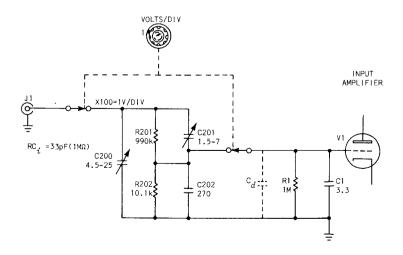

X100

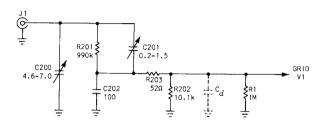

Fig. 2-10 contains circuitry resulting from a VOLTS/DIV selection of 1.0. The operator switched in the X100 attenuator. The basic divider consists of: R202, paralleled by R1, in series with R201. C202,  $\mathbf{C}_d$  and C1 shunt the lower resistive leg forming a capacitive voltage divider with C201. Adjusting C201 compensates the voltage divider. Adjusting C200 matches total input capacitance to other attenuator positions.

component quality Input attenuator parts must be of high quality. They are not only close tolerance resistive or capacitive values, but also must contribute small and predictable amounts of alien components. Resistors contain capacitance or inductance or both. Capacitors also contain resistance or inductance or both. These components should be as pure as possible for use in the input attenuator. Quantity production requires physical repeatability and predictability which usually calls for purity compromises. Therefore, capacitors add L and R, and resistors add L and C.

Interconnecting and component leads are inductors. Long leads or those with a bend impose more inductance than short straight leads. Leads also contribute capacitance, dependent upon conductor spacing.

Fig. 2-10. X100 input-voltage division.

Capacitance develops between switch terminals and contacts, between circuit-board strips and so on. Any connection, in fact, is a potential capacitor. The relatively slow effect is hook. Hook is a small dip, of short duration, on the flat top of a displayed step, immediately following the leading edge. The capacitance variation that causes hook usually results from dielectric alterations during transit time. Dielectrics involved can be attenuator capacitors, active device input capacitance, terminal stand-off insulation, or that of a circuit board. Terminals or circuit boards are the most common offenders. This dielectric modification occurs during the step-transit time. Following pulse or step transition, the dielectric returns to normal, creating a discharge current with a time constant much slower than the input-step risetime. The discharge current develops a voltage across the output, which subtracts from the input level. Tektronix corrects for hook at the attenuator by component selection, circuit layout and circuitboard construction.

hook correction

Selected components, careful layout and quality assembly reduces stray reactances to a practical tolerance for instruments of medium risetime. As a rule-of-thumb, which will have several exceptions, assume instruments with risetimes of 10 ns or longer contain simple attenuators as shown in Figs. 2-9 and 2-10. Verticals in the 7-10 ns range may contain input attenuators as in Figs. 2-9 and 2-10, or the attenuators may reflect the techniques of the "faster" instruments.

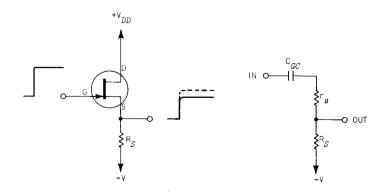

stray components "Fast" instruments react to stray components of sometimes obscure origins, such as the paint on components. Vertical amplifiers capable of reproducing steps of 7 ns or less have extra parts which counter component-induced distortion. This distortion takes two forms: Rolloff, due to changing input capacitance, and overshoot (ringing), caused by adding inductance.

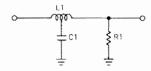

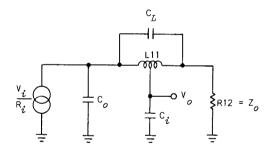

Varying input capacitance is the input amplifier's response to a fast step. This "negative-input-resistance characteristic" receives treatment in the next chapter. At the input attenuator the change takes the form of additional capacitive current. Series-peaking networks provide one solution.

Fig. 2-11. X2 attenuator with series peaking.

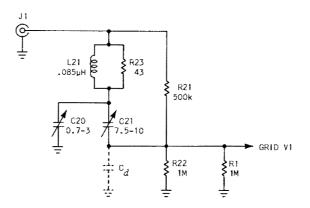

series peaking Fig. 2-11 shows series-peaking network L21 and R23 added to a X2 attenuator. This circuit is taken from a preamplifier with an overall risetime of about 2 ns. L21 and R23 maintain a delicate balance between signal and regenerative currents.

Input voltages which change levels in a few nanoseconds demand maximum capacitive current from the attenuator. The grid of VI also draws additional capacitive current. However, during signal transit, L21 presents maximum opposition to signal-current flow. R23 then establishes total attenuator signal-current flow. If R23 signal-current reduction equals the current drawn by VI, the attenuator achieves a voltage division of 2. This only results from delicate part selection and placement. Components involved are L21, R23, C20, C21, Cd and the capacitive change in the VI grid circuit. Should the components be improperly proportioned the input either rings or degrades risetime.

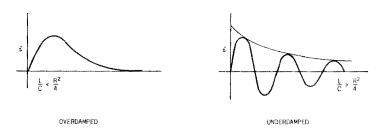

Precise RLC responses are very complex. For this reason only basic ideas explain peaking-network action here. R23 shunts the peaking coil. For explanatory purposes a small resistor shunting the coil has the same effect as a large series resistor. A series RLC circuit responds to a step function in one of two basic ways: It develops a

overdamped

underdamped

pulse of current, or it rings. Overdamped response (a current pulse) occurs when the L-to-C ratio is small and the series resistance is correspondingly large. Underdamped response (ringing) results from a large L-to-C ratio and a small series resistance. Curves of Fig. 2-12 show circuit current relative to L, C and R values.

Since damping is the same, a small resistance shunts L21 rather than a large series component. Keeping R23 small negates effects on all but the "fast" signals.

The overdamped response current only occurs in attenuator reactances. 1  $M\Omega$  resistance shunts the reactive leg, so when the reactive current drops to zero, total signal current flows through the 1  $M\Omega$  resistance.

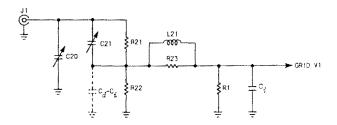

In the case of Fig. 2-13, L21 and R23 separate  $C_i$  from  $C_d$  during signal transitions.  $C_i$  consists of quiescent input capacitance modified by V1 negative

Fig. 2-12. Comparison of overdamped and underdamped response.

Fig. 2-13. Alternate location of X2-attenuator series peaking.

input characteristics and, possibly, circuit-board dielectric loss. L21 and R23 probably do not retain the values listed in Fig. 2-11. L and R values must combine with circuit capacitance to form an underdamped response.

RLC appear as part of the input attenuator only when the changing capacitance is an appreciable percentage of the capacitive divider. Increasing attenuation reduces the need for peaking. This is because component capacitance shunting the grid line becomes larger. The preamplifier from which Fig. 2-11 was taken has an RLC network in the X2, X5, X10, X20 and X50 voltage dividers. The X100, X200 and X500 have none, neither of course does the X1.

high-value dividers Fig. 2-14, the X100 divider, includes no LR network. Two capacitances, C200 and C202 are much larger values than counterparts, C20 and C $_d$ , in the X2 attenuator. The smaller value of C201 makes this necessary. Series capacitance C201 establishes total divider capacitance. Therefore, C200 must be large enough to set the input RC equal to the X1 RC at J1. C202 added to C $_d$  should approximately compensate the divider at the midrange setting of C201: R1C1 = R2C2.

Changing capacitance at the grid line, or due to C201 dielectric deviations, represents too small a percentage of the total capacitance to consider a peaking network necessary.

ringing

R203 loads the circuit to damp oscillations. This ringing results from stray inductances, inherently a part of the capacitors, resistors and attenuator wiring. R203 adds but 1/2% error to the voltage divider.

eliminating input networks Eliminating attenuator components reduces production costs and stray reactances. There are two major techniques used to eliminate networks: Stacking and amplifier-gain switching.

stacking

Stacking reduces only production cost. Stacking input attenuators reduces the total number of parts required for a given range of input deflection factors. The representative VOLTS/DIV selector (shown in Fig. 2-15A) and information so far presented, leads one to believe each switch position

is a separate attenuator circuit. This 11-position selector indicates 10 RC voltage dividers. (X1 is not considered a voltage divider.) There are not necessarily 10 networks. Five networks, eliminating a number of parts but adding a slightly more complex switching system, provide the same result as 10.

Fig. 2-14. The X100 attenuator of a "fast" preamplifier.

| VOLTS/DIV | NETWORK   | STACKED WITH |

|-----------|-----------|--------------|

| 0.01      |           |              |

| 0.02      | (÷) X2    |              |

| 0.05      | (÷) X5    |              |

| 0.1       | (÷) X10   |              |

| 0.2       | (÷) X10   | (±) X2       |

| 0.5       | (÷) X10   | (†) X5       |

| 1.0       | (÷) X100  |              |

| 2.0       | (÷) X100  | (÷) X2       |

| 5.0       | (÷) X100  | (‡) X5       |

| 10.0      | (÷) X1000 |              |

| 20.0      | (÷) X1000 | (÷) X2       |

(B)

Fig. 2-15. Stacked-attenuator switching logic.

stacking program Stacking cascades, by switch selection, voltage dividers to multiply attenuation ratios. Fig. 2-15B lists a stacking program. The first column lists selected input deflection factors; the second, primary attenuators selected; and the last column, the selected cascaded attenuator. For input deflection factors 0.01 VOLTS/DIV through 0.1 VOLTS/DIV only primary attenuators appear. Selections 0.2 VOLTS/DIV through 20 VOLTS/DIV utilize X2 and X5 attenuators in cascade; of this group 1 VOLTS/DIV and 10 VOLTS/DIV utilize primary attenuator selections alone.

÷ and X

interchangeable

Symbols  $(\div)$  and (X) both appear in Fig. 2-15B. These symbols are interchangeable and either may appear on a schematic diagram. Read X2 as an attenuation of 2; and  $\div$ 2 as a voltage division of 2.

Compare Fig. 2-15B and Fig. 2-16. Fig. 2-16 illustrates a stacked X20 or  $\div 20$  input attenuator. Fig. 2-15B indicates attenuation results from selection of 0.2-VOLTS/DIV input deflection factor. Each attenuator network presents 1-M $\Omega$  input impedance. Therefore, connecting the X2 network across R102 shunts the same as R102 connected to the grid of V1. R1 does parallel R22. Both X10 and X2 attenuators then load as though connected in the circuit alone. Proper voltage division occurs:

- 200 millivolts at J1 develop 20 millivolts at junction R101-R102.

- 20 millivolts across the X2 attenuator develop 10 millivolts at the grid of V1.

Stated in terms of deflection factor:

- 1. 200 millivolts/division at Jl.

- 20 millivolts/division input to the X2 attenuator.

- 3. 10 millivolts/division at the grid of V1.

Selecting 0.5 VOLTS/DIV substitutes a X5 attenuator. Input voltages now receive an attenuation of 50. Concepts remain the same for all stacked configurations.

compensation

One compensates these dividers in switch positions that place single networks in the circuit. From Fig. 2-15B, these positions of the VOLTS/DIV selector would be: 0.02, 0.05, 0.1, 1.0 and 10. Selecting stacked positions creates the need for compromise adjustment. Unfortunately, stacking limits minimum input capacitance. The electromechanical effects of each stack adds capacitance.

Fig. 2-16. X20 or ÷20 stacked attenuator.

Fig. 2-17. Preamplifier switching logic.

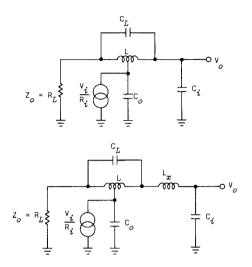

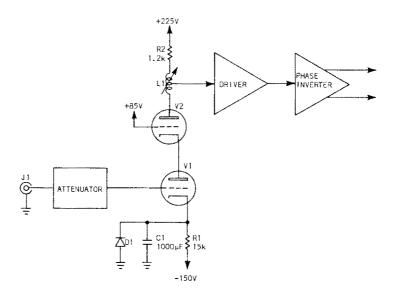

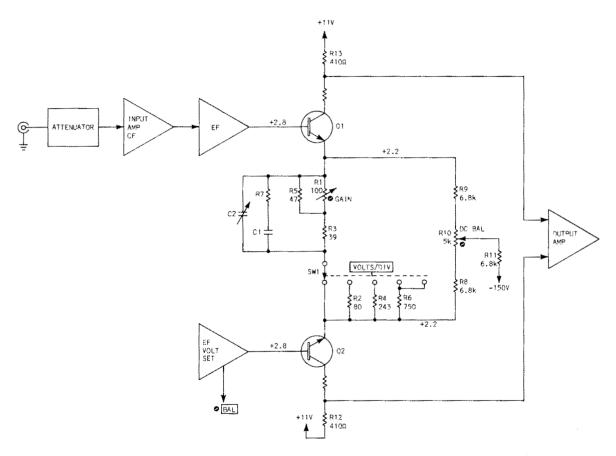

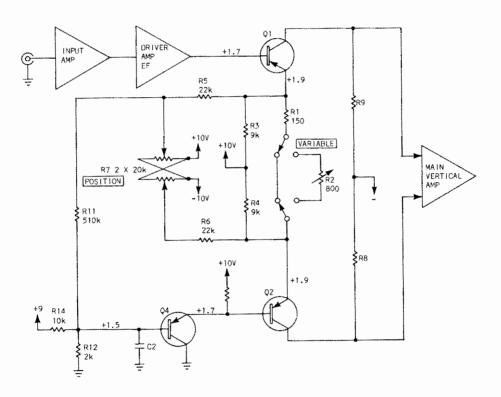

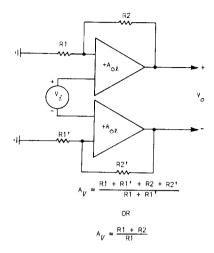

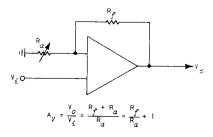

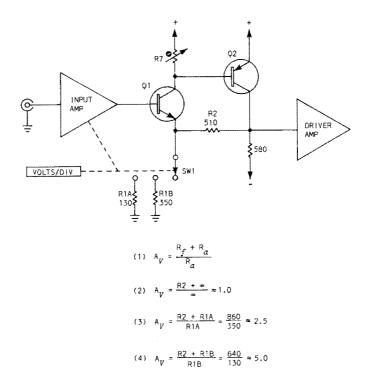

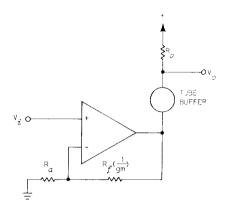

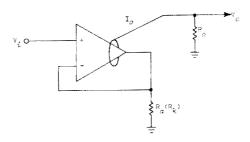

gain switching

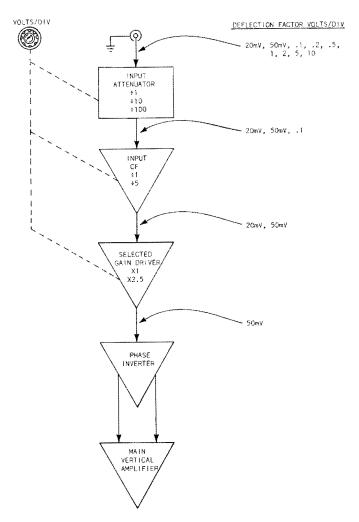

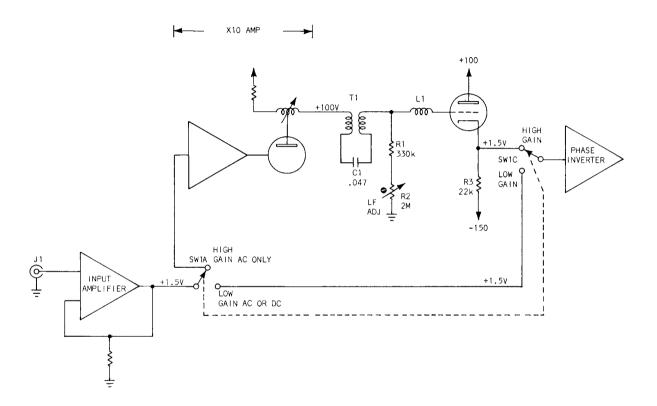

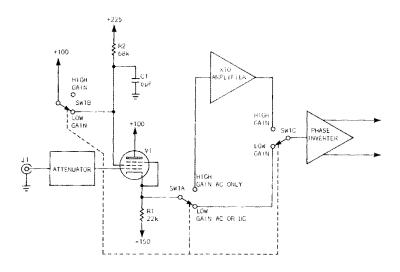

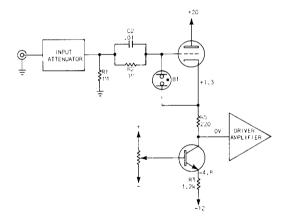

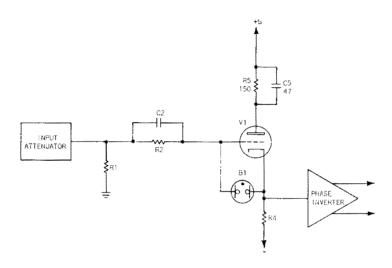

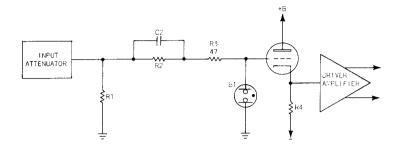

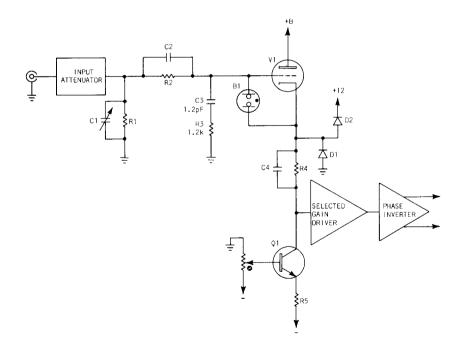

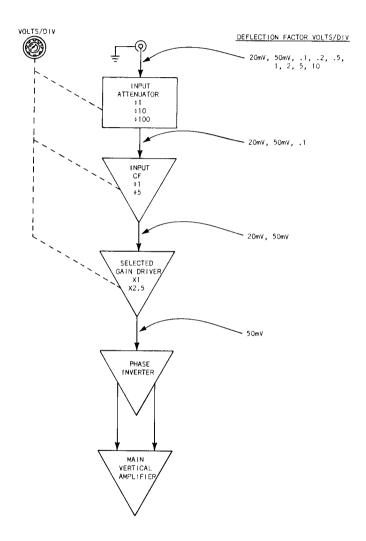

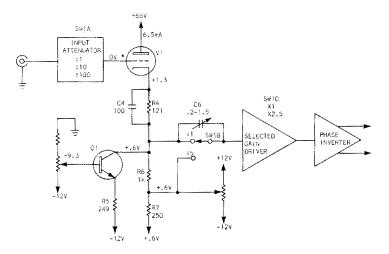

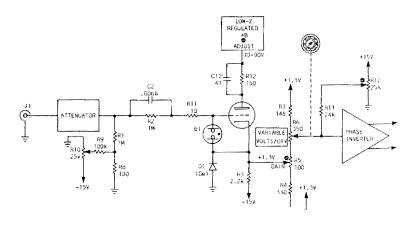

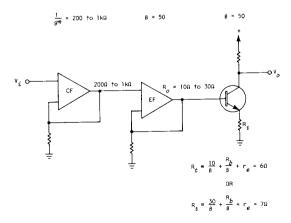

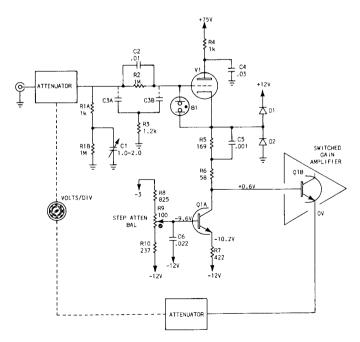

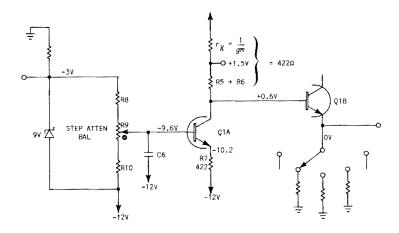

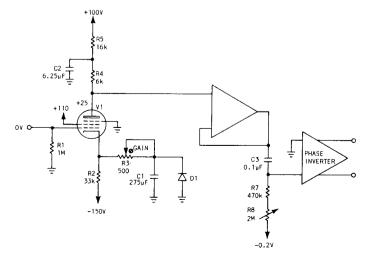

input attenuator Amplifier-gain switching, mechanically ganged to the input attenuator, provides the present solution for numerically reducing input attenuator networks. Fig. 2-17 shows in block form the switching logic necessary to drive a phase inverter at a constant deflection factor. Blocks labeled Input Attenuator, Input Cathode-Follower and Selected-Gain Driver mechanically gang to the VOLTS/DIV selector. Deflection factor at the input jack is from 20

input CF

selectedgain driver millivolts to IO volts per division, step-selected in a I-2-5 sequence. The three input dividers reduce the nine input deflection factors to three: 20 millivolts, 50 millivolts and 100 millivolts. Selecting cathode-follower gain of 1 or 1/5 gives sn input deflection factor to the selected-gain driver of 20 and 50 millivolts per division. The selected-gain driver can now have a constant output deflection factor.

Wafer switches contribute significantly to total capacitance, even to the simplest input attenuators. Stacking compounds the difficulty. Stray inductance increases due to wiring complexity as well as stray capacitance.

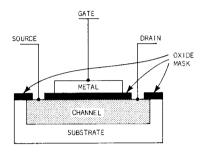

furret attenuator The device which reduces stray reactances the most is the seldom used turret attenuator. Fig. 2-18 is a photograph of one type of Tektronix turret attenuator. The body of the turret holds voltage-divider components. These parts need have very short leads thereby reducing inductance. Rotating the turret body moves voltage-divider parts and associated connectors to the single set of switch contacts. No method yet devised contributes as few reactances as the turret attenuator.

Fig. 2-18. Turret attenuator.

Turret attenuators at present just don't lend themselves to quantity production. For this reason only a few Tektronix instrument types contain turret attenuators.

Modern oscilloscopes have a constant input RC. The input attenuator consists of compensated voltage dividers. Deflection factors change in one of three basic methods:

- 1. Selecting one of a group of compensated voltage dividers.

- Program selecting stacked compensated voltage dividers.

- Amplifier-gain switching combined with one of the above techniques.

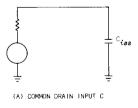

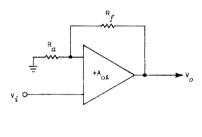

## **FOLLOWERS**

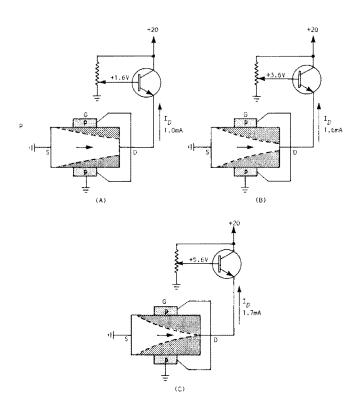

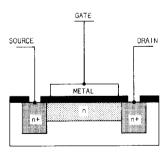

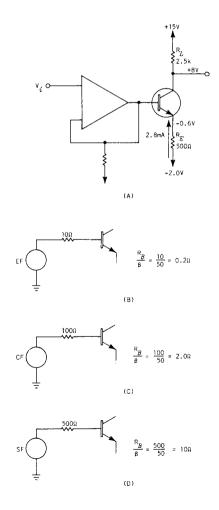

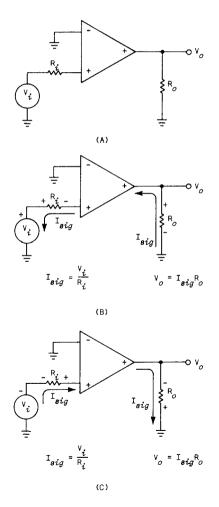

three basic configurations Followers consist of three basic circuit configurations: Cathode followers, source followers and emitter followers. Follower circuits might appear in any stage of oscilloscope circuitry. Basic follower characteristics justify such wide usage. Characteristics necessary to achieve uniform frequency response over a wide range of input frequencies and amplitudes are indigenous to followers:

- Low input capacitance (high input impedance).

- 2. Low output impedance.

- 3. Linear amplification.

- 4. Gain stability.

- 5. Can handle large input voltage swings.

Additionally, there are peculiar characteristics of followers that are made use of:

- Gain is less than one but can be made to approximate unity.

- 7. No signal inversion.

- 8. Quiescent level is easily set.

- Supply voltage fluctuations are greatly attenuated at the output.

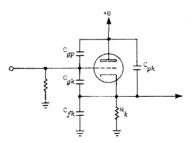

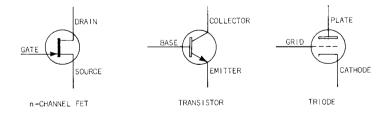

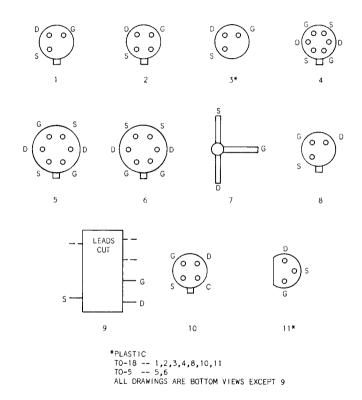

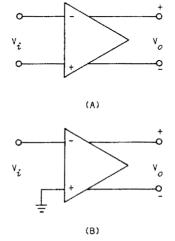

Fig. 3-1. Follower symbols.

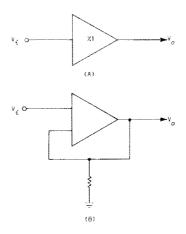

circuit symbols

CF, SF and EF abbreviations Circuit symbols, as shown in Fig. 3-1, apply to followers. (A) symbolizes a unity gain amplifier. However, one might interpret (A) to indicate phase inversion unless the initials CF, SF, or EF appear within the triangle. CF abbreviates cathode follower; SF, source follower; and EF, emitter follower. On the other hand, symbol (B) is exclusive to followers. This symbol indicates noninverted unity gain. Both symbols appear in block diagrams through this book.

low input capacitance

low output R

Any discussion of follower circuitry in wideband amplifiers utilizes the terms impedance transfer or isolation. These terms generally apply to all characteristics but specifically consider the first two: low input capacitance (another term for high input impedance) and low output resistance.

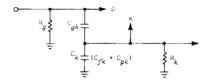

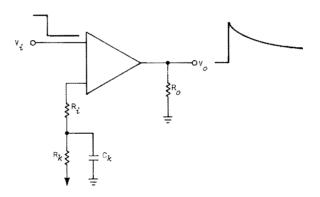

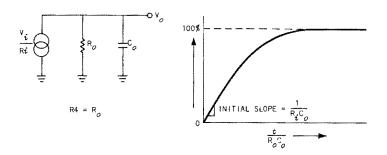

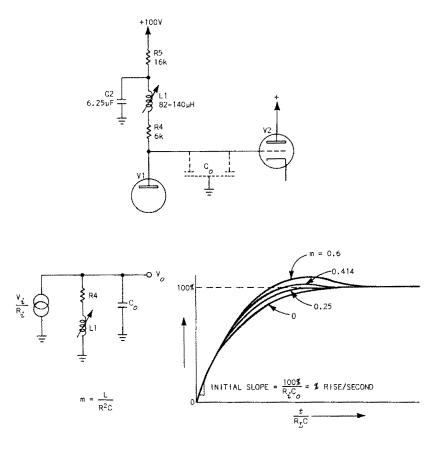

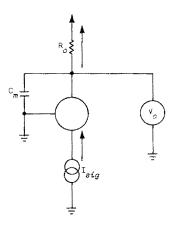

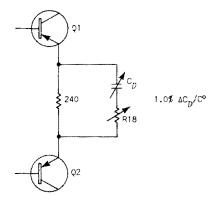

risetime improvement Fig. 3-2 illustrates the principle of placing a follower between a large resistive output and a large capacitive input to improve risetime. Risetime (bandpass) of an amplifier is a function of the product of resistance and capacitance. 2.2 RC defines circuit risetime. Follower amplifier A2 shunts the large output resistance of A1 with a small capacitance. A2 also presents to A3 a small  $\rm R_{\rm O}$  to shunt the large input capacitance of A3. The resultant risetime is less than connecting A1 directly to A3.

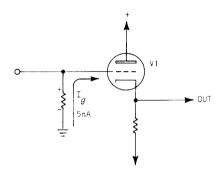

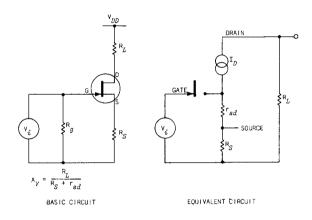

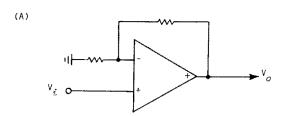

input amplifier Followers are not restricted to interstage isolation. They also function as output amplifiers or, as shown in Fig. 3-3, input amplifiers. The followers' high input impedance shunts the attenuator very little, allowing passive device values to set input impedance at Jl. Of the three basic follower configurations, cathode followers currently appear most frequently as input amplifiers.

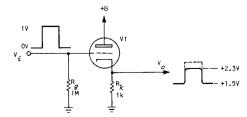

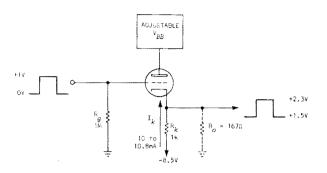

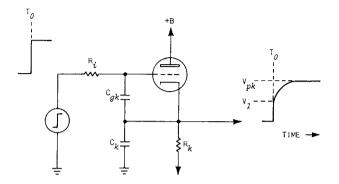

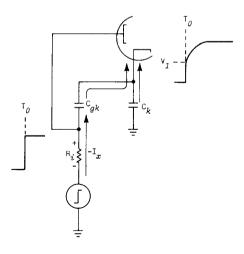

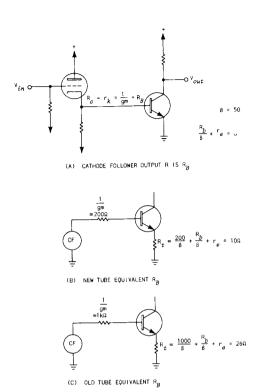

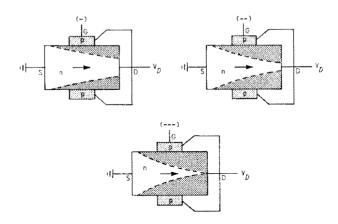

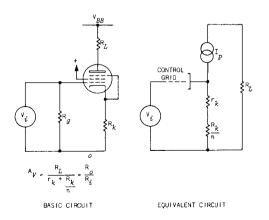

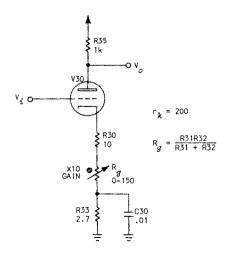

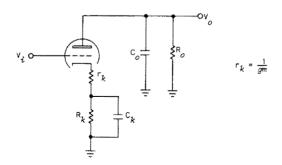

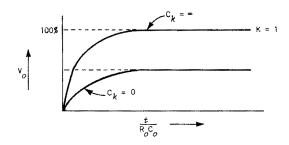

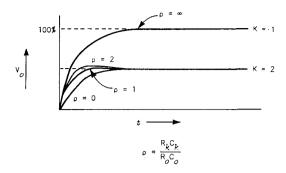

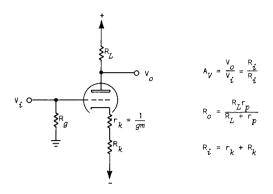

cathode follower Fig. 3-4 shows a cathode follower. In this figure, a pulse applied to the grid develops at the cathode with corners rounded and attenuated. Consider first the signal attenuation. Attenuation implies

Fig. 3-2. Isolation block diagram.

Fig. 3-3. Vertical-amplifier block diagram.

Fig. 3-4. Cathode follower.

Fig. 3-5. Equivalent CF circuit (1).

Fig. 3-6. Equivalent CF circuit (2).

voltage-divider action and that is just what happens. The voltage applied to the grid develops across  $R_{k}$  and the internal impedance of V1.

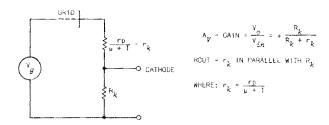

Fig. 3-5 depicts a cathode-follower model. A theoretical voltage generator, or source, drives the control grid. Grid voltage  $(V_g)$  develops across a voltage divider consisting of external cathode load  $(R_k)$  and internal tube impedance  $(r_k)$ . Formulas included in Fig. 3-5 define gain as a voltage-divider ratio. They also show that output impedance at the cathode terminal results from  $R_k$  paralleling  $r_k$ .

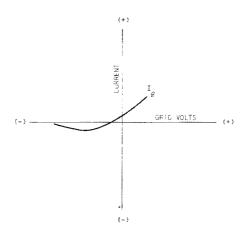

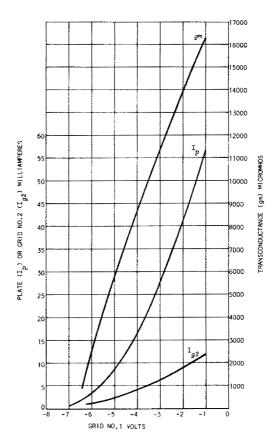

Active device parameters such as amplification factor  $(\mu)$  and plate resistance (rp) must be considered. Because transconductance (gm) applies to any active device, it appears more often in this book than any other dynamic parameter.

Using parameters  $\mu$  and gm, one builds the cathode-follower model shown in Fig. 3-6. This figure assumes  $\mu$  = 30 and gm = 5000  $\mu$ mho. The voltage source applies grid voltage, modified by  $\mu$ , across voltage divider  $r_k$  and  $R_k$ . Both models (Figs. 3-5 and 3-6) develop gain of 0.8, indicating active parameter interdependence.

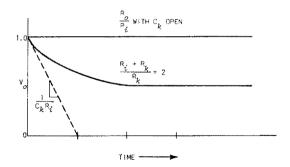

gain approximations ignore µ Usually satisfactory approximations result from using transconductance alone. Discarding  $\mu$  in the gain formula of Fig. 3-6 leaves the resistance ratio only. Gain now resolves to 0.83, sufficiently accurate for most circuit analysis.

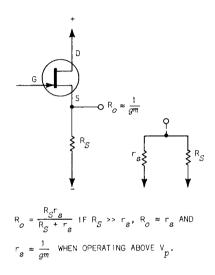

transconductance determines output impedance Parameter gm establishes output impedance as shown in Fig. 3-7. Output circuits connect to the junction of  $R_{\mathcal{K}}$  and  $r_{\mathcal{K}}$ . Therefore, output impedance  $(R_{\mathcal{O}})$  cannot exceed the value of  $r_{\mathcal{K}}\left(\frac{1}{gm}\right)$ . High gm devices present a smaller  $R_{\mathcal{O}}$  to output circuits than low gm devices.

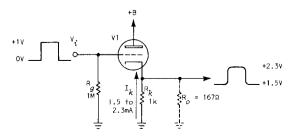

plate current affects gm Plate current affects gm, causing questionable gain stability of the circuit shown in Fig. 3-8. For small signals this circuit might be satisfactory. But large signal gain stability does not exist because of the large change in plate current. The circuit as shown experiences 65% plate current change. Plate current and gm relate directly and gain is a function of gm:

$$\mathbf{r}_{k} = \frac{1}{gm}.$$

$$\mathbf{r}_{i} \cong \mathbf{R}_{g}$$

$$\mathbf{R}_{o} \approx \mathbf{R}_{k} \| \mathbf{r}_{k} \approx 167n$$

Fig. 3-7. CF output impedance.

Fig. 3-8. CF signal current.

Fig. 3-9. Plate voltage determines output level.

Fig. 3-10. Positive grid return equivalent to negative cathode return.

gain stability results from constant plate current

Fig. 3-9 represents an improvement. Notice that output DC levels, output impedance and gain are the same as in Fig. 3-8. An adjustable plate return sets the quiescent output DC level. Plate current is determined by self-bias, Ry and the negative cathode supply voltage. The positive signal excursion now causes only 8% change in plate current. This percentage reduces further when both Rk and the negative return increase. For example, if Rk were 2 k $\Omega$  returned to a -18.5 V supply, an input signal of 1 V would cause 4% plate-current change. external components free the circuit to act as a constant-current device. Fig. 3-10 functions the same as the circuit in Fig. 3-9 except the cathode resistor returns to ground.

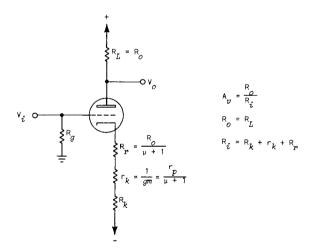

longtailing

constant  $I_p$  stabilizes gm

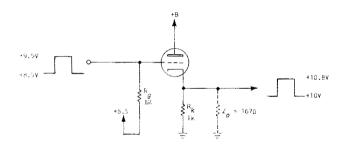

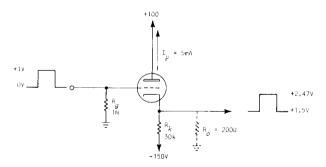

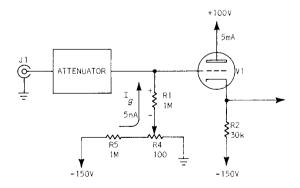

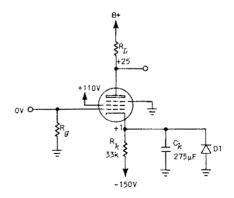

A method of current driving an active device, so popular it has a name, is shown in Fig. 3-11. This is a longtail circuit. The name derives from the large cathode resistor. Ratio of  $r_k$  to  $R_k$  is such that output impedance is  $\frac{1}{gm}$  and gain is  $\frac{\mu}{\mu+1}$ . One volt signal causes less than 3/4% change in plate current, stabilizing transconductance.

The cathode returns to -150 volts through 30 k $\Omega$ . Operating characteristics demand cathode potential of +1.5 volts at quiescence. 5.05 mA then flows under no signal conditions. Increasing grid voltage 1 volt increases cathode current by 0.03 mA or a total of 5.08-mA plate current.

This small change hardly affects gm. Notice that gain approaches unity. The longtailed cathode follower meets most of the follower requirements.

Fig. 3-12 shows a longtail configuration returning  $\mathbf{R}_k$  to ground. Concepts remain as explained.

Fig. 3-11. Longtail cathode follower.

Fig. 3-12. Longtail CF with cathode returned to ground potential.

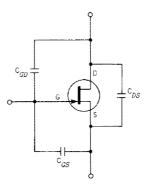

Fig. 3-13. Interelectrode capacitance.

Fig. 3-14. Input capacitance.

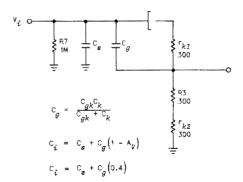

triode capacitances The presentation assumed only resistive components acted upon signals, yet reactive elements exist in any circuit. Reactive components within the tube, grid-to-plate and grid-to-cathode capacitance, are of greatest concern. The effect of these capacitors depends upon circuit design. Fig. 3-13 identifies triode capacitances.

How much a capacitor affects a signal is determined by the signal voltage across the capacitor.  $C_{gp}$  and V1 plate return to a low-impedance voltage supply. Cathode follower design then innately reduces the effect of  $C_{gp}$ , although still a circuit component.

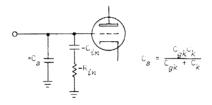

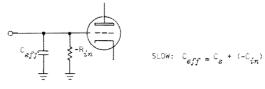

gain and grid-tocathode capacitance establish input capacitance If unity gain could be realized, capacitance from grid to cathode could be ignored. With no voltage difference across the capacitor, equivalent capacitance is zero. Equivalent grid capacitance then is  $C_{gk}$  multiplied by one minus voltage gain:  $[C_g = C_{gk} \ (1 - A_V)]$ . Another reduction is illustrated in Fig. 3-14. Capacitance, filament-to-cathode and plate-to-cathode, appears in series with

$\mathbf{C}_{\mathcal{G}k}$ . Assume cathode follower input capacitance falls between less than one picofarad and two picofarads.

output impedance provides charge path for output capacitance Capacitance, associated with cathode-follower output, rapidly charges through the low-output impedance. This capacitance affects the performance of "fast-rise" amplifiers and as such receives attention later in the chapter. Ignore, for now, cathode-follower output capacitance.

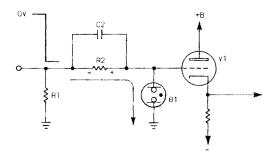

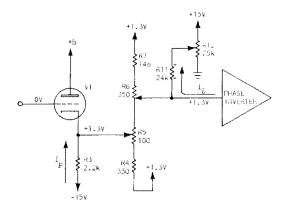

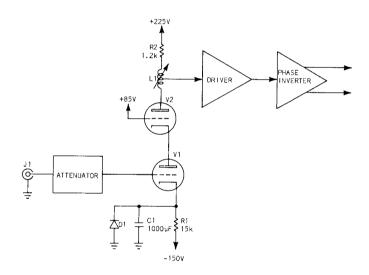

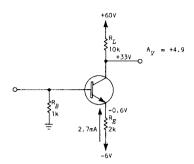

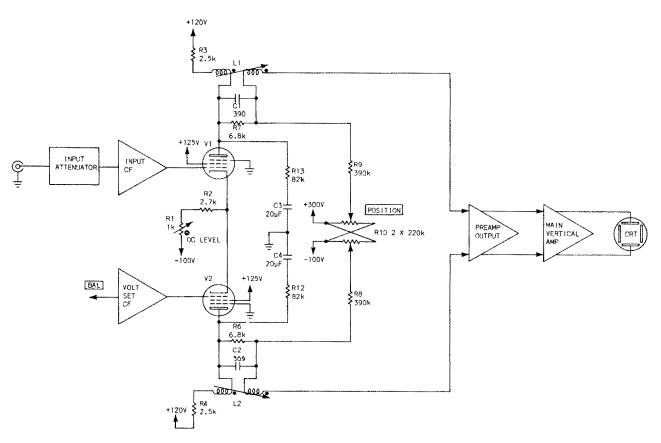

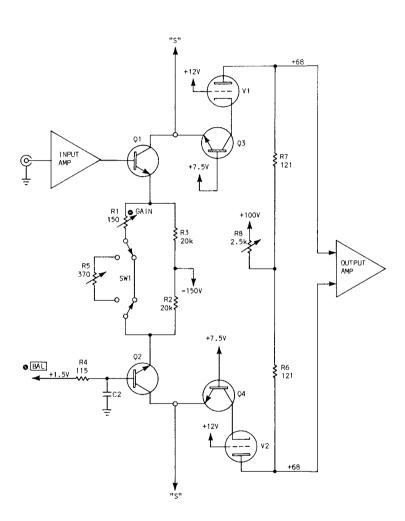

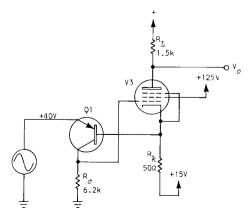

typical circuits Vertical amplifiers having a frequency response of DC to ten megahertz or so contain cathode followers as developed. Fig. 3-15 through 3-20 are examples of typical oscilloscope circuits using concepts presented.

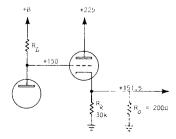

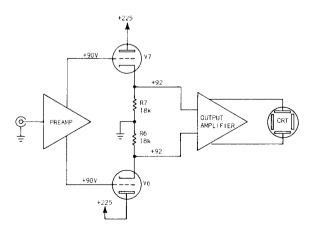

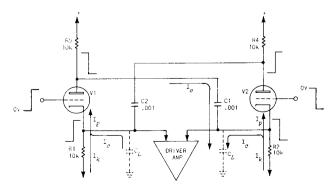

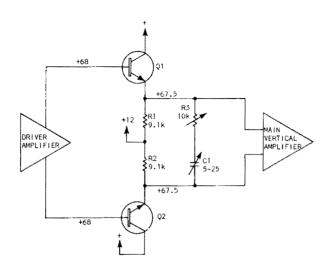

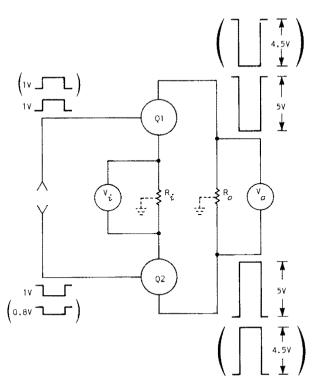

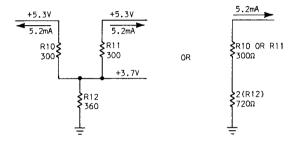

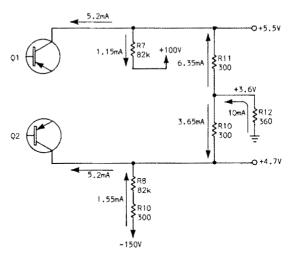

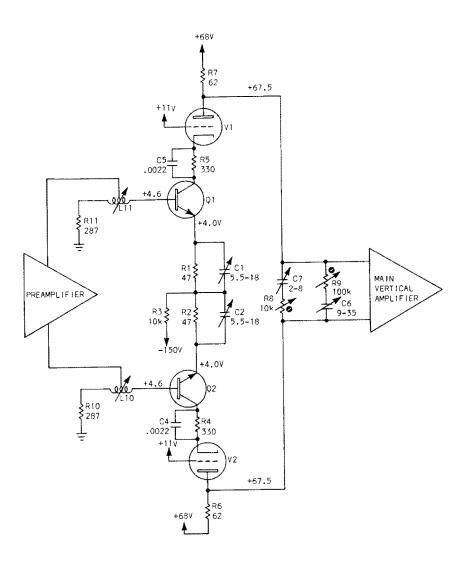

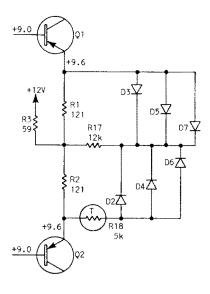

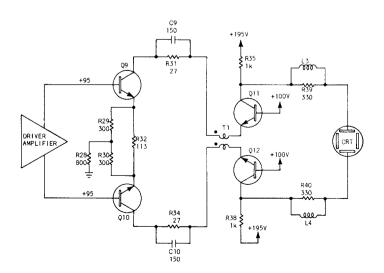

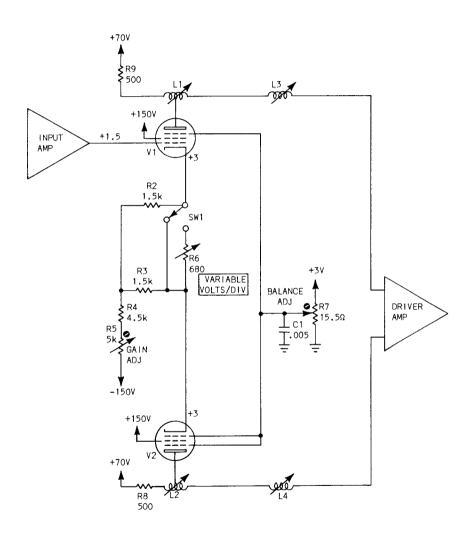

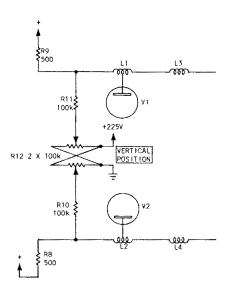

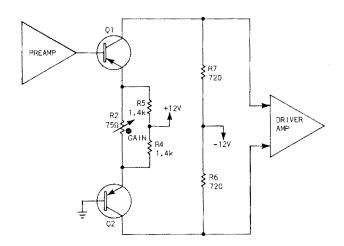

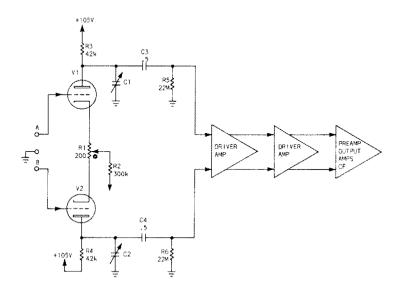

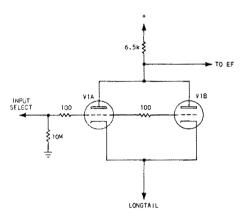

Fig. 3-15 shows a pair of cathode followers driven push-pull. These longtailed circuits function to breakup parallel capacitive networks.

V6 and V7 operate independently to act as a kind of coupling circuit. R6 and R7, in conjunction with the positive grid potentials, longtail V6 and V7. DC levels and signal amplitudes applied to the output amplifier approximate values applied to V6 and V7 grids.

Both the preamplifier and main vertical output amplifiers are plate loaded. A longtailed cathode follower presents much less input capacitance and

Fig. 3-15. Main vertical input amplifier.

risetime improvement output impedance than a plate-loaded amplifier. Placing the cathode followers between the plate-loaded amplifiers then improves risetime. The small input capacitance of V6 and V7 shunts the preamplifier output, while the relatively large input capacitance of the output amplifier rapidly charges and discharges through the small R<sub>O</sub> of V6 and V7.

Series peaking coils may appear in the output leads of V6 and V7.

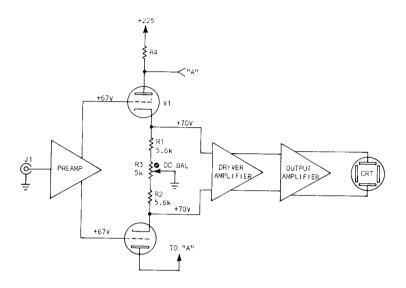

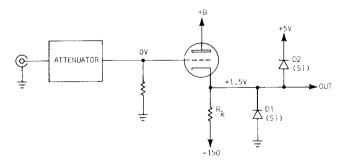

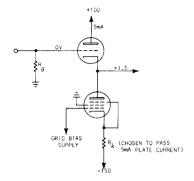

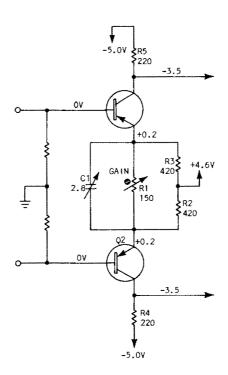

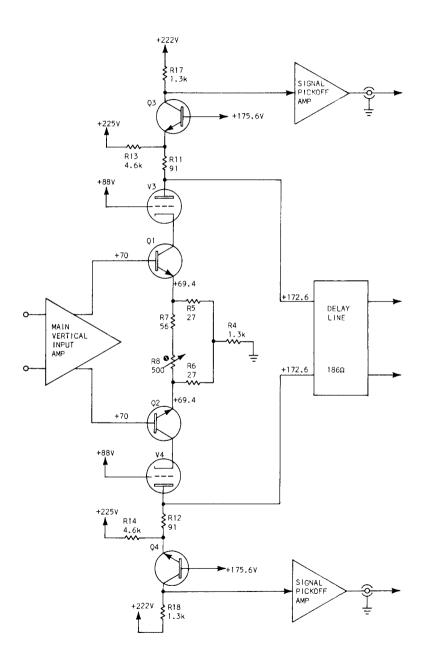

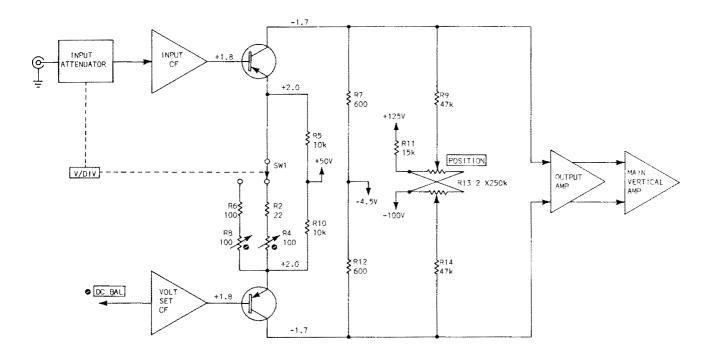

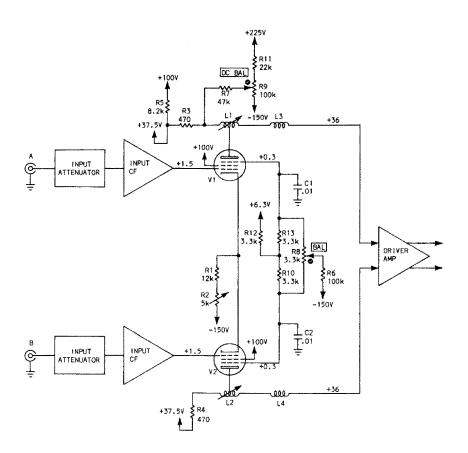

Fig. 3-16 depicts a cathode-follower circuit, used to improve bandwidth (risetime), which includes a balance control within the longtail network.

coupling devices Driven push-pull, VI and V2 operate independently. Grid DC and signal levels originate within the preamplifier. The cathode followers merely couple preamplifier voltages to the driver amplifier, elevated by a DC level representing self bias.

R4 serves to reduce the positive supply voltage to the correct operating level at V1 and V2 plates.

R4 is common to V1 and V2 plate current. Push-pull signal currents flow in V1 and V2 and these equal-amplitude opposite-phase currents maintain a constant drop across R4. A capacitor bypassing R4 is thus superfluous.

centering control

Most main vertical amplifiers consist of cascaded direct-coupled push-pull stages. Any imbalance at the input, amplified, deflects the CRT as a signal. This is the correct action for DC measurements. Quiescently however, the CRT display must center. Placing a ground at input connector J1, one adjusts R3 to compensate for: An unbalanced preamplifier, small differences between V1 and V2, and unbalanced conditions of following stages.

One sets R3 for a vertically centered CRT display.

centering empirical

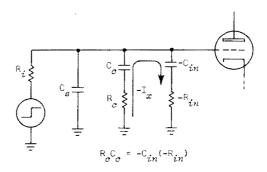

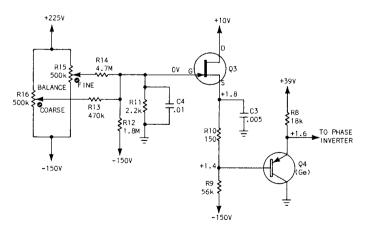

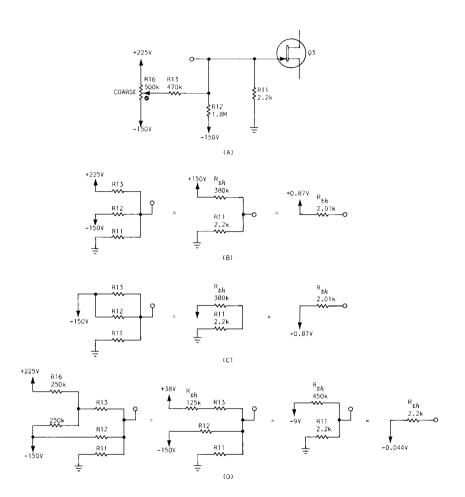

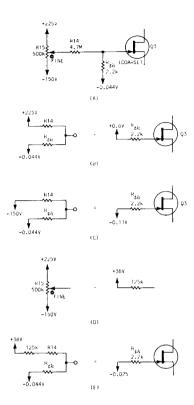

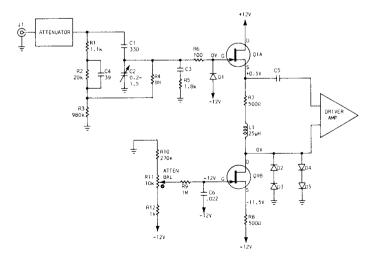

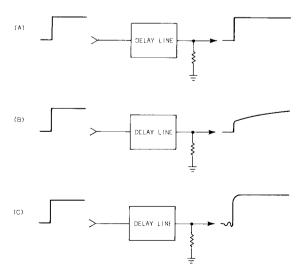

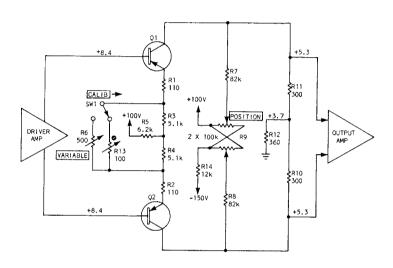

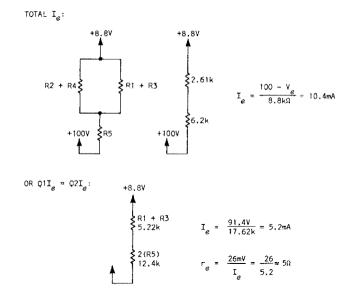

Changing R3 changes V1 and V2 plate currents in opposite quantities. Plate current and gm track. Therefore, adjusting R3 affects small changes in cathode-follower gain in opposite quantities.