S-6: Difference between revisions

(added internal description) |

No edit summary |

||

| Line 48: | Line 48: | ||

7s12-s6-s52-f.jpg | S-6 sampling head and [[S-52|S-52 pulse generator head]] in a [[7S12|7S12 TDR/Sampler plugin]] | 7s12-s6-s52-f.jpg | S-6 sampling head and [[S-52|S-52 pulse generator head]] in a [[7S12|7S12 TDR/Sampler plugin]] | ||

Tek s-6 black.jpg | S-6 with a black face plate | Tek s-6 black.jpg | S-6 with a black face plate | ||

S-6_Schematic_naked.png| S-6 schematic | |||

Tek s-6 left internal.jpg | S-6 internal left side | Tek s-6 left internal.jpg | S-6 internal left side | ||

Tek s-6 right internal.jpg| S-6 internal right side | Tek s-6 right internal.jpg| S-6 internal right side | ||

Revision as of 20:52, 26 February 2021

Template:Plugin Sidebar 2 The Tektronix S-6 Sampling Head plug-in is a 50 Ω feed-through unit with a rise-time of 30 ps and bandwidth of 11.5 GHz. It was introduced in 1971.

The S-6 provides two unterminated 50 Ω SMA connections in a loop-through configuration as is convenient for TDR applications. It is good practice to leave a termination resistor on the unit when unused to give some protection against electrostatic discharge. The S-6 does not provide a trigger pickoff signal.

Key Specifications

| Rise time | 30 ps |

|---|---|

| Bandwidth | 11.5 GHz |

| Operating input voltage range | 1 Vp-p |

| Maximum single sample step | 250 mV for less than 5% aberration |

| Maximum input voltage | ±5 VDC |

| Input impedance | 50 Ω (unterminated!) |

| Noise | < 5 mV of noise |

| Features |

|

Internals

The S-6 is very similar to the S-4 as that it uses a 6-diode traveling wave trapped-charge sampling gate. This gate is implemented in the 155-0053-00 hybrid. Since the S-6 is a feed-through sampling head, the blow-by compensation is implemented slightly differently using a 10 k resistor in the hybrid directly connected to the input signal. The S-6 replaces the discrete preamplifier of the S-4 with two opamps from a 155-0035-00 quad opamp chip. The two other opamps are used to buffer the gate bias voltages.

Links

- S-6 internal photo and simulation

- Repairing an S-6 head (with internal photos)

- S-6 @ amplifier.cd 7S12 page

- S-6 @ barrytech.com

Pictures

-

S-6 front

-

S-6, entire plugin

-

S-6 sampling head and S-52 pulse generator head in a 7S12 TDR/Sampler plugin

-

S-6 with a black face plate

-

S-6 schematic

-

S-6 internal left side

-

S-6 internal right side

-

S-6 internal right side

-

S-6 internal left side, Preamp board removed

-

S-6 internal all boards removed, 155-0053-00 hybrid remains

-

S-6 Preamp board top

-

S-6 Preamp board backside

-

S-6 Strobe board backside

-

S-6 interconnect board

-

155-0053-00 hybrid sampling diode assembly

-

155-0053-00 hybrid sampling diode assembly (internal)

-

155-0053-00 hybrid sampling diode assembly with lid

-

155-0053-00 hybrid sampling diode assembly (internal)

-

155-0053-00 hybrid sampling diode assembly (internal)

Measurements

-

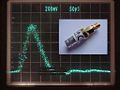

Impulse taken with S6 sampling head. Every dot is equivalent to one sample taken, and combined on the CRT with a rate of app. 100 Hz. Bright dots are newer than dimmed ones.

-

Incident pulse from an S-52 (nom. < 25 ps) displayed by an S-6 head (nom. < 30 ps), both installed in a 7S12. Displayed rise time ~35 ps confirms spec.

-

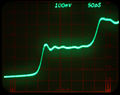

"Self Portrait" of an S-6: A pulse reflected on the unterminated "through" path (approx. 120 ps one way)