DL2: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| (4 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{Plugin Sidebar | {{Plugin Sidebar | ||

| manufacturer=Tektronix | |manufacturer=Tektronix | ||

| type=DL2 | |type=DL2 | ||

| summary=Digital Latch | |summary=Digital Latch | ||

| image=Tek dl2 1.jpg | |image=Tek dl2 1.jpg | ||

| caption=DL2 | |caption=DL2 | ||

| series=7000-series scopes | |series=7000-series scopes | ||

| introduced=1978 | |introduced=1978 | ||

| discontinued=(?) | |discontinued=(?) | ||

| manuals= | |manuals= | ||

* [[Media: | * [[Media:070-2394-00.pdf|Tektronix DL2 Manual]] | ||

}} | }} | ||

The '''Tektronix DL2 Digital Latch''' functions as a glitch detector extension to the [[7D01]] logic analyzer. | The '''Tektronix DL2 Digital Latch''' is a plug-in for [[7000-series scopes]] that functions as a glitch detector extension to the [[7D01]] logic analyzer. There is a [[TM500_system|TM500]] counterpart, the [[DL502]]. | ||

It connects between the [[P6451]] probes and the [[7D01]] | It connects between the [[P6451]] probes and the [[7D01]] and receives the latter's store clock via a front panel [[BNC connector]]. Short pulses ≥5 ns are stretched to the clock period. | ||

{{BeginSpecs}} | {{BeginSpecs}} | ||

| Line 20: | Line 20: | ||

{{Spec |Minimum clock period | 20 ns }} | {{Spec |Minimum clock period | 20 ns }} | ||

{{EndSpecs}} | {{EndSpecs}} | ||

==Internals== | |||

The data path in the DL2 is built using standard 100k ECL circuits. The –4.8 V and –2 V ECL supplies are generated by a 555-driven switcher powered off the ±15 V rails (same board as in the [[7D01]]). | |||

==Links== | ==Links== | ||

* [http://www.barrytech.com/tektronix/tek7000/tekdl2.html DL2 @ barrytech.com] | * [http://www.barrytech.com/tektronix/tek7000/tekdl2.html DL2 @ barrytech.com] | ||

* [ | * [https://www.amplifier.cd/Test_Equipment/Tektronix/Tektronix_7000_series_special/logicanalyzer_7D01.htm 7D01, DF1, DF2 and DL2 @ amplifier.cd] | ||

{{Documents|Link=DL2}} | |||

==Pictures== | ==Pictures== | ||

| Line 32: | Line 36: | ||

Tek dl2 4.jpg | Tek dl2 4.jpg | ||

Tek dl2 5.jpg | Tek dl2 5.jpg | ||

Tek DL2 left.jpg | |||

Tek DL2 right.jpg | |||

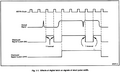

Tek DL2 timing diagram.png | Operating principle (timing diagram) | |||

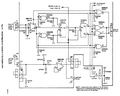

Tek DL2 principle schematic.png | Operating principle (channel schematic) | |||

</gallery> | </gallery> | ||

{{ | ==Components== | ||

{{Parts|DL2}} | |||

[[Category:7000 series special-function plugins]] | [[Category:7000 series special-function plugins]] | ||

[[Category:Logic analyzers]] | [[Category:Logic analyzers]] | ||

Latest revision as of 05:42, 12 December 2023

The Tektronix DL2 Digital Latch is a plug-in for 7000-series scopes that functions as a glitch detector extension to the 7D01 logic analyzer. There is a TM500 counterpart, the DL502.

It connects between the P6451 probes and the 7D01 and receives the latter's store clock via a front panel BNC connector. Short pulses ≥5 ns are stretched to the clock period.

Key Specifications

| Number of channels | 16 |

|---|---|

| Minimum pulse width | 5 ns |

| Minimum clock period | 20 ns |

Internals

The data path in the DL2 is built using standard 100k ECL circuits. The –4.8 V and –2 V ECL supplies are generated by a 555-driven switcher powered off the ±15 V rails (same board as in the 7D01).

Links

Documents Referencing DL2

| Document | Class | Title | Authors | Year | Links |

|---|---|---|---|---|---|

| Tekscope 1977 V9 N3.pdf | Article | New Products | 1977 | FEM181 • DL2 • DL502 • 851 |

Pictures

-

-

-

-

-

-

-

-

Operating principle (timing diagram)

-

Operating principle (channel schematic)

Components

Some Parts Used in the DL2

- (no results)