ACVS: Difference between revisions

No edit summary |

|||

| (12 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

Tektronix 11000-series plug-ins and mainframes contain a subsystem called the Analog Control Voltage System (ACVS). | Tektronix [[11000-series plug-ins]] and [[11000-series scopes|mainframes]] contain | ||

a subsystem called the '''Analog Control Voltage System (ACVS)'''. | |||

The ACVS produces several independently controllable DC voltages. | The ACVS produces several independently controllable DC voltages. | ||

The voltages are fed to the analog signal path circuitry | The voltages are fed to the analog signal path circuitry, e.g., the gain and offset control pins of the [[M377]], | ||

or the OFFSET pin on the [[Tekprobe_BNC_connector|TekProbe]] input connector. | or the OFFSET pin on the [[Tekprobe_BNC_connector|TekProbe]] input connector. | ||

In plug-ins, the number of voltages produced by the ACVS depends on how many channels the plug-in has. | |||

For example, the [[11A34]] | For example, the [[11A34]] has four channels and has an ACVS that produces sixteen control voltages. | ||

== AVCS in 11000-Series Plug-ins == | == AVCS in 11000-Series Plug-ins == | ||

The ACVS comprises three parts: | The ACVS comprises three parts: | ||

* [[Media:AD667.pdf|AD667]] 12-bit DAC (single output) | * [[Media:AD667.pdf|AD667]] 12-bit DAC (single output) | ||

* [[Media: | * [[Media:Cd74hc4051-ep.pdf|74HC4051]] analog switches and holding capacitors, implementing a set of sample and hold circuits | ||

* [[Media:Tl074.pdf|TL074]] JFET-input opamps, providing a set of unity-gain output buffers | * [[Media:Tl074.pdf|TL074]] JFET-input opamps, providing a set of unity-gain output buffers | ||

| Line 16: | Line 17: | ||

The sample and hold and output buffers are on a daughterboard. (See photo below) | The sample and hold and output buffers are on a daughterboard. (See photo below) | ||

The ACVS is controlled by the [[M382]] chip, which also implements [[SDI]] and sequences the amplifier output enable signals. | The ACVS is controlled by the [[M382]] chip, which also implements [[SDI|Serial Data Interface (SDI)]] | ||

and sequences the amplifier output enable signals. | |||

The ACVS also has a loopback function using one of the 74HC4051 analog multiplexers. | |||

The output voltages can be routed to a TLC540 8-bit ADC in the plug-in (U750 in the 11A52) | |||

which allows the microprocessor to verify that the control voltages are approximately correct. | |||

<gallery> | <gallery> | ||

Tek 11a32 sample and hold.jpg|ACVS sample-and-hold circuits on daughterboard on [[11A32]] | Tek 11a32 sample and hold.jpg|ACVS sample-and-hold circuits on daughterboard on [[11A32]] | ||

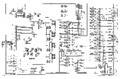

Tektronix 11A52 main amp & control schematic.JPG|ACVS sample and hold schematic in the [[11A52]] | Tektronix 11A52 main amp & control schematic.JPG|ACVS sample and hold schematic in the [[11A52]] | ||

Tek 11a33 670-8986 crop.jpg|ACVS in 11A33 | |||

670-8986-00 Sample and Hold Farm-11K plugins.jpg|670-8986-00 Sample and Hold Farm with Labeled Components | |||

</gallery> | </gallery> | ||

== ACVS in 11000-Series Mainframes == | == ACVS in 11000-Series Mainframes == | ||

In | In 11300 mainframes, the ACVS is controlled by an 8051-family microcontroller. | ||

It employs a [[Media:DAC312.pdf|DAC312]] 12-bit DAC, | It employs a [[Media:DAC312.pdf|DAC312]] 12-bit DAC, | ||

whose output is fed to an array of | whose output is fed to an array of 32 sample-and-hold circuits similar to the ones in the plug-ins. | ||

A refresh cycle sequentially refreshes the voltage on each of the sample-and-hold capacitors. | A refresh cycle sequentially refreshes the voltage on each of the sample-and-hold capacitors. | ||

The time to complete the entire refresh cycle is 900 μs. | The time to complete the entire refresh cycle is 900 μs. | ||

The precision | The precision of each sample-and-hold voltage 12 bits. | ||

These | Twenty six of the sample-and-hold voltages are used independently. | ||

The other six voltages are combined in groups of three using resistor summing networks | |||

to produce two outputs that each have 14.6 bit precision. | |||

These two precision voltages are DLYREF0 and DLYREF1. | |||

DLYREF0 is the comparator voltage for the SWEEP A delay. | |||

DLYREF1 is the comparator voltage for the SWEEP B delay. | |||

See schematic below. | |||

Historical note: Earlier analog scopes (e.g., the [[565]]) | |||

used the same basic architecture for sweep delay: | |||

the instantaneous sweep ramp voltage is compared with | |||

a user-controllable DC voltage that represents the desired amount of delay. | |||

In 11300 scopes, the DC voltage is produced by the ACVS; | |||

In the 565 it is produced by a multi-turn potentiometer on the front panel. | |||

The ACVS in DSA600 mainframes generates 48 control voltages. | |||

<gallery> | <gallery> | ||

Tek 11300 acvs.png|ACVS schematic in 11300 mainframes | Tek 11300 acvs.png|ACVS schematic in 11300 mainframes. | ||

Tek 11300 dlyref3.png|The weighted sum of three ACVS voltages is fed to the delay ramp comparator. | |||

Tek_565_delay_pickoff.png|Delayed trigger in 565. Delay Interval potentiometer produces control voltage. | |||

</gallery> | </gallery> | ||

[[Category:Circuits and Concepts]] | |||

Latest revision as of 07:13, 25 August 2020

Tektronix 11000-series plug-ins and mainframes contain a subsystem called the Analog Control Voltage System (ACVS). The ACVS produces several independently controllable DC voltages. The voltages are fed to the analog signal path circuitry, e.g., the gain and offset control pins of the M377, or the OFFSET pin on the TekProbe input connector. In plug-ins, the number of voltages produced by the ACVS depends on how many channels the plug-in has. For example, the 11A34 has four channels and has an ACVS that produces sixteen control voltages.

AVCS in 11000-Series Plug-ins

The ACVS comprises three parts:

- AD667 12-bit DAC (single output)

- 74HC4051 analog switches and holding capacitors, implementing a set of sample and hold circuits

- TL074 JFET-input opamps, providing a set of unity-gain output buffers

The output from the DAC is sampled and held, and the buffered voltages are fed to the rest of the plug-in. The voltages in the sample and hold are periodically refreshed. The sample and hold and output buffers are on a daughterboard. (See photo below)

The ACVS is controlled by the M382 chip, which also implements Serial Data Interface (SDI) and sequences the amplifier output enable signals.

The ACVS also has a loopback function using one of the 74HC4051 analog multiplexers. The output voltages can be routed to a TLC540 8-bit ADC in the plug-in (U750 in the 11A52) which allows the microprocessor to verify that the control voltages are approximately correct.

-

ACVS sample-and-hold circuits on daughterboard on 11A32

-

ACVS sample and hold schematic in the 11A52

-

ACVS in 11A33

-

670-8986-00 Sample and Hold Farm with Labeled Components

ACVS in 11000-Series Mainframes

In 11300 mainframes, the ACVS is controlled by an 8051-family microcontroller. It employs a DAC312 12-bit DAC, whose output is fed to an array of 32 sample-and-hold circuits similar to the ones in the plug-ins. A refresh cycle sequentially refreshes the voltage on each of the sample-and-hold capacitors. The time to complete the entire refresh cycle is 900 μs. The precision of each sample-and-hold voltage 12 bits.

Twenty six of the sample-and-hold voltages are used independently. The other six voltages are combined in groups of three using resistor summing networks to produce two outputs that each have 14.6 bit precision. These two precision voltages are DLYREF0 and DLYREF1. DLYREF0 is the comparator voltage for the SWEEP A delay. DLYREF1 is the comparator voltage for the SWEEP B delay. See schematic below. Historical note: Earlier analog scopes (e.g., the 565) used the same basic architecture for sweep delay: the instantaneous sweep ramp voltage is compared with a user-controllable DC voltage that represents the desired amount of delay. In 11300 scopes, the DC voltage is produced by the ACVS; In the 565 it is produced by a multi-turn potentiometer on the front panel.

The ACVS in DSA600 mainframes generates 48 control voltages.

-

ACVS schematic in 11300 mainframes.

-

The weighted sum of three ACVS voltages is fed to the delay ramp comparator.

-

Delayed trigger in 565. Delay Interval potentiometer produces control voltage.