7D14: Difference between revisions

(circuit details) |

No edit summary |

||

| Line 52: | Line 52: | ||

==Pictures== | ==Pictures== | ||

<gallery> | <gallery> | ||

File:7d14-front.jpg | 7D14 front panel | File:7d14-front.jpg | 7D14 front panel. The unit pictured was able to count up to 640 MHz on the external input and 532 MHz on the trigger path (7A19 in 7904). | ||

File:7d14-left.jpg | 7D14 left side | File:7d14-left.jpg | 7D14 left side | ||

File:7d14-right.jpg | 7D14 right side | File:7d14-right.jpg | 7D14 right side | ||

Revision as of 05:04, 3 October 2014

The Tektronix 7D14 is a 525 MHz frequency counter plug-in for 7000 series mainframes.

It uses the mainframe's readout system to display an eight-digit count on the CRT. Modes include frequency, frequency ratio and events count using manual or external gate.

When installed in a horizontal compartment, it can count the trigger pickoff from a vertical amplifier unit. This allows simultaneous viewing and counting of a signal in four-bay mainframes.

In a vertical compartment, the trigger signal (i.e. the "shaped" input) can be displayed as the module's Y output.

Specifications

Key Specifications

| Frequency | 525 MHz (5 MHz bandwidth limiting switch available) |

|---|---|

| Sensitivity | 100 mV to 10 V |

| Input Impedance | 50 Ω or 1 MΩ // 20 pF on external input, 1.5 Div internal when set to "Trig Source" |

| Gate time | 1 ms to 10 s |

| Display time | 0.1 s to 5 s or infinite |

| Features |

|

Internals

An input section using relays selects the counter signal from the internal trigger path or external input, and activates 50 Ω termination and/or attenuators.

A differential FET buffer + bipolar amplifier stage drives a counter gate that uses a 10 mA tunnel diode as the switching element.

The first decade is implemented as a divide-by-2 ECL flip-flop followed by a 5-stage ring counter made with discrete transistor pairs (note circular layout) and some logic to BCD-encode the count result.

The following seven counter stages are conventional TTL decade ripple counters (N8292A).

The counter outputs are multiplexed onto a common 4-bit bus using open-collector NAND gates under control of the mainframe's readout system. The multiplexed digit value feeds a D/A converter (Tek 155-0038-01) that in turn drives the analog row and column returns to the readout system. A separate blanking logic eliminates leading zeroes and displays a ">" sign in the leftmost column if the counter overflows.

Links

Pictures

-

7D14 front panel. The unit pictured was able to count up to 640 MHz on the external input and 532 MHz on the trigger path (7A19 in 7904).

-

7D14 left side

-

7D14 right side

-

7D14 detail - input amplifier. Own photo.

-

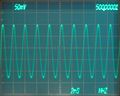

7D14 detail - counter gate

-

7D14 detail - 525 MHz divide-by-2 stage

-

7D14 detail - divide-by-5 discrete ring counter stage

-

-

-