P7001: Difference between revisions

(Added Computer controlled XY Mode, some minor text changes) |

(Added first public presentation date, Link to IEEE Intercon in 1973 and Block Diagram) |

||

| Line 24: | Line 24: | ||

* [http://w140.com/tek_p7001_gpib_service_070_2623_00_sm.pdf Tektronix P7001 IEEE 488 Interface (GPIB) (PDF)] | * [http://w140.com/tek_p7001_gpib_service_070_2623_00_sm.pdf Tektronix P7001 IEEE 488 Interface (GPIB) (PDF)] | ||

* [[Media:070-2623-00.pdf|Tektronix P7001 IEEE 488 Interface Manual, 1986 Revision (OCR, PDF)]] | * [[Media:070-2623-00.pdf|Tektronix P7001 IEEE 488 Interface Manual, 1986 Revision (OCR, PDF)]] | ||

* [[Media:061-1344-00.pdf|needed: | * [[Media:061-1344-00.pdf|needed: Hardware Signal Averager (HSA) Manual 061-1344-00]] | ||

* [[Media:070-2846-00.pdf|needed: | * [[Media:070-2846-00.pdf|needed: Hardware Signal Averager (HSA) Manual 070-2846-00]] | ||

[[Category:Manual needed]] | [[Category:Manual needed]] | ||

}} | }} | ||

The '''Tektronix P7001''' is a digitizer, processor, and memory for the [[7704A]] oscilloscope. | The '''Tektronix P7001''' is a digitizer, processor, and memory for the [[7704A]] oscilloscope. The P7001 can also be connected to an external computer which then is able to process the digitized signals. The complete system was called "Digital Processing Oscilloscope" or "DPO" for short and was presented to the public on 27 March 1973 at the IEEE Intercon in New York City. | ||

The design of the P7001 assumes it will be part of a 7704A system, and that the 7704A will be displaying a steady trace. | The design of the P7001 assumes it will be part of a 7704A system, and that the 7704A will be displaying a steady trace. | ||

| Line 42: | Line 42: | ||

{{Spec | Resolution | 10 bit (V), 9 bit (H) }} | {{Spec | Resolution | 10 bit (V), 9 bit (H) }} | ||

{{Spec | Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) }} | {{Spec | Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) }} | ||

{{Spec | Sampling rate | | {{Spec | Sampling rate | 150 kHz ±30 kHz }} | ||

{{Spec | External interface | 16 bit parallel, proprietary "[[CP bus]]" (dual 37-pin [[Sub-D connector]]s) interfacing with Tektronix CP-1100 or CP-4100 series controllers }} | {{Spec | External interface | 16 bit parallel, proprietary "[[CP bus]]" (dual 37-pin [[Sub-D connector]]s) interfacing with Tektronix CP-1100 or CP-4100 series controllers }} | ||

{{EndSpecs}} | {{EndSpecs}} | ||

| Line 48: | Line 48: | ||

==Links== | ==Links== | ||

* [https://groups.io/g/TekScopes/topic/7654269 Thread on P7001 and interfaces] | * [https://groups.io/g/TekScopes/topic/7654269 Thread on P7001 and interfaces] | ||

* [https://vintagetek.org/wp-content/uploads/2018/11/IEEENAB1973_TW_03231973.pdf (PDF) Article on vintagetek.org about the IEEE Intercon 1973] | |||

==Catalog / Specs== | ==Catalog / Specs== | ||

| Line 66: | Line 67: | ||

==Internals== | ==Internals== | ||

The signal coming from the acquisition unit enters a fast [[sampling diodes|four-diode sample and hold circuit]] where it is sampled at | The signal coming from the acquisition unit enters a fast [[sampling diodes|four-diode sample and hold circuit]] where it is sampled at 150 ksamples/sec. | ||

Each sample is digitized using a successive-approximation scheme. | Each sample is digitized using a successive-approximation scheme. | ||

The analog to digital converter is made of several chips: a digital to analog converter, a comparator, and control logic. | The analog to digital converter is made of several chips: a digital to analog converter, a comparator, and control logic. | ||

| Line 196: | Line 197: | ||

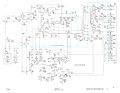

'''Schematics''' | '''Schematics''' | ||

<gallery> | <gallery> | ||

Tek_P7001_BlockDiagram.jpg|Block Diagram | |||

P7001 ps1.jpg|Power supply schematic 1 | P7001 ps1.jpg|Power supply schematic 1 | ||

P7001 ps2.jpg|Power supply schematic 2 | P7001 ps2.jpg|Power supply schematic 2 | ||

Revision as of 08:17, 31 July 2019

The Tektronix P7001 is a digitizer, processor, and memory for the 7704A oscilloscope. The P7001 can also be connected to an external computer which then is able to process the digitized signals. The complete system was called "Digital Processing Oscilloscope" or "DPO" for short and was presented to the public on 27 March 1973 at the IEEE Intercon in New York City.

The design of the P7001 assumes it will be part of a 7704A system, and that the 7704A will be displaying a steady trace. The vertical and horizonal plug-ins control the beam as they would in any 7000-series scope.

The P7001 periodically samples the horizontal and vertical signals simultaneously as they pass from the plug-ins to the vertical and horizontal amplifiers. This allows it to fill its memory with data points represented as coordinate pairs, (x1,y1), (x2,y2), (x3,y3), etc. It is not necessary that x2 be greater than x1, i.e. the samples can be taken out-of-order with respect to their equivalent time in the waveform.

Key Specifications

| Resolution | 10 bit (V), 9 bit (H) |

|---|---|

| Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) |

| Sampling rate | 150 kHz ±30 kHz |

| External interface | 16 bit parallel, proprietary "CP bus" (dual 37-pin Sub-D connectors) interfacing with Tektronix CP-1100 or CP-4100 series controllers |

Links

Catalog / Specs

- P7001 Spec 1973

- P7001 Spec 1974

- P7001 Spec 1975

- P7001 Spec 1976

- P7001 Spec 1977

- P7001 Spec 1978

- P7001 Spec 1979

- P7001 Spec 1980

- P7001 Spec 1981

Advertising

Internals

The signal coming from the acquisition unit enters a fast four-diode sample and hold circuit where it is sampled at 150 ksamples/sec. Each sample is digitized using a successive-approximation scheme. The analog to digital converter is made of several chips: a digital to analog converter, a comparator, and control logic.

The P7001 has its own power supply built into it, independent of the power supply in the acquisition unit of the 7704A. It has a backplane with an asynchronous bus and several cards that plug into that bus: sampler, analog to digital converter, memory, external digital interface, and display electronics. The P7001 was available with semiconductor memory or with magnetic core memory. Both types of memory were available through the whole production time of the P7001. In the first years the core memory module was cheaper and the default module. In later years the semiconductor memory module got cheaper and then this module was the default one. But the core memory module has one big adavantage: The memory content was preserved during a shutdown of the unit. This may have been the reason the core memory option remained available in the later years of P7001 production.

The bus is used for low speed signals. High speed signals are sent through coaxial cables that connect to the cards using Peltola connectors.

The Acquisition Unit of the 7704A, the P7001 Processor, and the Display Unit of the 7704A are connected by the Acquisition-Processor-Display (APD) Interface shown below.

External Interfaces

| Part Number | Description |

|---|---|

| 021-0113-00 | DPO to Data General Nova |

| 021-0116-00 | DPO to APD |

| 021-0117-00 | DPO to CP1100 (CP Bus) |

| 021-0127-00 | DPO to TEK31 calculator |

| 021-0146-00 | DPO to CAMAC |

| 021-0175-00 | DPO to 4010 Family |

| 021-0206-00 | DPO to GPIB |

Pictures

-

Front panel

-

P7001 in 7704A

-

P7001 in 7704A

-

Internal

-

Top view

-

Front of backplane

-

main interface board (backplane)

-

Rear of backplane

-

Interunit connector

-

Interunit connector

-

Interunit connector

-

Switching power supply

-

front panel rear

-

extender boards

Keyboard overlay cards

-

blank card for user definable programs

-

Two examples of original overlay cards

-

Example of aftermarket overlay cards

External Interfaces (optional)

-

CPBus interface mounted

-

CP Bus Interface front

-

CP Bus Interface rear

-

GPIB Interface IO board

-

GPIB Interface IO board with shielding

-

GPIB Interface CPU board

-

Modern clone of the P7001 GPIB interface

-

Modern clone of the P7001 GPIB interface

Sample and Hold Card

-

Vertical sampling bridge

-

Horizontal sampling bridge

-

Sampling strobe generator

-

Sample and hold edge connector

-

Sample and hold transformers

-

Sample and hold transformer

-

Sample and hold rear

Core Memory (optional)

-

Address decoder

-

Core boards

-

Core memory

-

Core closeup

-

Core closeup

-

High Resolution view of partial core module

Semiconductor memory (optional)

-

2K semiconductor memory (aka "MOS")

ADC and Display

-

Front panel connections

-

ADC

-

ADC rear

-

Probe points on ADC

-

Display generator

-

Display generator rear

-

Z-axis and panel controller

-

Z-axis and panel controller rear

-

Readout interface

Hardware signal Averager (HSA)

-

HSA timing board. The HSA module (optional) performs signal averaging and can calculate a histogram.

-

HSA memory board.

Schematics

-

Block Diagram

-

Power supply schematic 1

-

Power supply schematic 2

-

APD Interconnect

Cofigurations

-

Example of Calculator based system (WP1100) in 1974

-

Example of Calculator based system (WP1100) in 1978

-

Example of Controller based system (WP1200) in 1973

-

Example of Controller based system (WP1200) in 1975

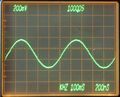

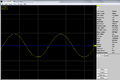

Workflow with connected Controller

-

With pressing a program-call button on the P7001...

-

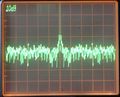

.. the displayed signal is digitized...

-

...and transferred to the Controller...

-

...the Controller does some calculations...

-

...and transfers the result back to the P7001

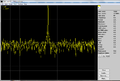

X/Y Mode for external Controller

-

A connected computer has direct access to the Display Generator. This allows software-controlled live movements of the Beam.