DF1: Difference between revisions

(more relevant key specs) |

No edit summary |

||

| Line 16: | Line 16: | ||

'''Alternate copy''' | '''Alternate copy''' | ||

* [http://w140.com/smb/df1_sm.pdf Tektronix DF1 Manual] (OCR) | * [http://w140.com/smb/df1_sm.pdf Tektronix DF1 Manual] (OCR) | ||

</small> | |||

{{ROM Images}} | |||

* U284: [[Media:156-0899-00.bin|156-0899-00]] | |||

* U294: [[Media:156-0900-00.bin|156-0900-00]] | |||

}} | }} | ||

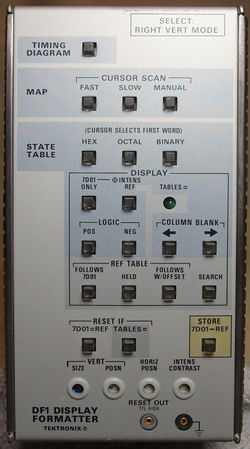

The '''Tektronix DF1''' is a display formatter for use with the [[7D01]] logic analyzer. It adds "data domain displays" (binary, octal and hexadecimal state tables, and a function map display) to the 7D01's time-domain display. It can store a reference table, to which the captured data can be compared. The [[DF2]] is essentially a DF1 with an extra key ("Menu") and additional ROM supporting GPIB diagnostics. | The '''Tektronix DF1''' is a display formatter for use with the [[7D01]] logic analyzer. It adds "data domain displays" (binary, octal and hexadecimal state tables, and a function map display) to the 7D01's time-domain display. It can store a reference table, to which the captured data can be compared. The [[DF2]] is essentially a DF1 with an extra key ("Menu") and additional ROM supporting GPIB diagnostics. | ||

Revision as of 00:29, 10 January 2022

The Tektronix DF1 is a display formatter for use with the 7D01 logic analyzer. It adds "data domain displays" (binary, octal and hexadecimal state tables, and a function map display) to the 7D01's time-domain display. It can store a reference table, to which the captured data can be compared. The DF2 is essentially a DF1 with an extra key ("Menu") and additional ROM supporting GPIB diagnostics.

Project manager for the DF1 was Murlan Kaufman.

The DF01 attaches to the 7D01 through a 50-pin D-sub connector on the right side panel only, it has no direct connection to the scope mainframe. The DF1 and 7D01 are mechanically coupled by three nylon standoffs that slide into cutouts in the 7D01's case rails. The bottom two standoffs are fixed and are inserted first, then the connector is plugged in and the third, sliding, stand-off at the top is moved to its locked position.

Key Specifications

| Memory | One reference table memory, same as 7D01 capacity (max. 16 channels at 254 bits/ch) |

|---|---|

| Display modes |

|

| Reset output | Positive 100 μs pulse, ≤0.4 V / ≥2.4 V |

Internals

The DF1 is built around a Motorola 6800 microprocessor with two 2K×8 masked ROMs and sixteen 1K×1 SRAMs (2101).

Pictures

-

Front

-

Internal

-

-

Side connector

-

-

-

Custom ICs used in the DF1

No results