7D02: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

(added info about options) |

||

| Line 33: | Line 33: | ||

{{BeginSpecs}} | {{BeginSpecs}} | ||

{{Spec | Channels | up to 52 - 28 (optionally 44) synchronous, 8 sync or async (timing option) }} | {{Spec | Channels | up to 52 - 28 (optionally 44) synchronous, 8 sync or async (timing option) }} | ||

{{Spec | Signal Inputs standard 7D02 | | |||

*8 Data | |||

*16 Address | |||

*10 Control | |||

*1 Ext. Trigger }} | |||

{{Spec | Memory | 256 words }} | {{Spec | Memory | 256 words }} | ||

{{Spec | Timing option | 8 channels, 255 word acquisition memory, 255 word glitch memory, 9 bit word recognizer; sampling 5 ms to 20 ns; [[P6451]] logic probe }} | {{Spec | Timing option | 8 channels, 255 word acquisition memory, 255 word glitch memory, 9 bit word recognizer; sampling 5 ms to 20 ns; [[P6451]] logic probe }} | ||

| Line 38: | Line 43: | ||

{{EndSpecs}} | {{EndSpecs}} | ||

:[[Category:Specifications needed]] ''please add'' | :[[Category:Specifications needed]] ''please add'' | ||

==Options== | |||

* Option 01 − Timing Option: provides 8 additional asynchronous channels with sample rates up to 50 MHz using [[P6451]] probe | |||

* Option 03 − Expansion: Adds 8 Data and 8 Address lines to 7D02, required for 16 bit microprocessors. | |||

==Links== | ==Links== | ||

* [[Media:Tekscope 1980 V12 N4.pdf | Tekscope Vol. 12 No. 4, Dec 1980]]: Mike Reiney, ''A User-Programmable Logic Analyzer for Microprocessor Design'' | * [[Media:Tekscope 1980 V12 N4.pdf | Tekscope Vol. 12 No. 4, Dec 1980]]: Mike Reiney, ''A User-Programmable Logic Analyzer for Microprocessor Design'' | ||

* [http://www.barrytech.com/tektronix/tek7000/tek7d02.html 7D02 @ barrytech.com] | * [http://www.barrytech.com/tektronix/tek7000/tek7d02.html 7D02 @ barrytech.com] | ||

Revision as of 11:13, 25 December 2021

The Tektronix 7D02 is a programmable logic analyzer plug-in for the 7000-series scopes.

The 7D02 makes used of an embedded Intel 8085 microprocessor, Tektronix part number 165-1088-00 on the A09 Central Processing Unit board.

It connects to a target microprocessor system through a target module:

- PM101 - General Purpose Logic Analysis

- PM102 - Motorola 6800

- PM103 - Motorola 6802

- PM104 - Intel 8085

- PM105 - Zilog Z-80

- PM106 - Intel 8086

- PM107 - Intel 8088

- PM108 - Zilog Z-8000

- PM109 - Motorola 68000

- PM110 - Zilog Z-8000

- PM111 - Motorola 6809

See the Microprocessor support table for microprocessor disassembly configuration options.

Key Specifications

| Channels | up to 52 - 28 (optionally 44) synchronous, 8 sync or async (timing option) |

|---|---|

| Signal Inputs standard 7D02 |

|

| Memory | 256 words |

| Timing option | 8 channels, 255 word acquisition memory, 255 word glitch memory, 9 bit word recognizer; sampling 5 ms to 20 ns; P6451 logic probe |

| Sampling Rate | up to 10 MHz |

- please add

Options

- Option 01 − Timing Option: provides 8 additional asynchronous channels with sample rates up to 50 MHz using P6451 probe

- Option 03 − Expansion: Adds 8 Data and 8 Address lines to 7D02, required for 16 bit microprocessors.

Links

- Tekscope Vol. 12 No. 4, Dec 1980: Mike Reiney, A User-Programmable Logic Analyzer for Microprocessor Design

- 7D02 @ barrytech.com

Pictures

-

-

7D02 bare plugin

-

7D02 front panel

-

7D02 top

-

7D02 in 7603 mainframe

-

7D02 in mainframe with personality module in front

-

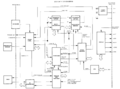

Block Diagram

Custom ICs used in the 7D02

No results