P7001: Difference between revisions

No edit summary |

(Added 1978 advert for the HSA module) |

||

| (23 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{Oscilloscope Sidebar |manufacturer=Tektronix | | {{Oscilloscope Sidebar | ||

series=7000-series scopes|model= P7001| | |manufacturer=Tektronix | ||

image=P7001 front.jpg| | |series=7000-series scopes | ||

caption=Tektronix P7001 front panel| | |model=P7001 | ||

introduced=1973 | | |image=P7001 front.jpg | ||

discontinued=1981 | | |caption=Tektronix P7001 front panel | ||

summary=Digitizer for the 7704A oscilloscope| | |introduced=1973 | ||

manuals= | |discontinued=1981 | ||

* [ | |summary=Digitizer for the 7704A oscilloscope | ||

* [ | |designers=Hiro Moriyasu;Luis Navarro;Bruce Hamilton;Jack Gilmore;Bob Shand;Bruce Hamilton;Jack Robinson;Bill Lucas;Jack Grimes;Dennis Keldsen;Mohamed Saba;Dick Beatty;Wayne Eshelman;George Rhine;Bill Markwart;Marlow Butler;Carl Dalby;Colin Doward;Gale Byers | ||

* [ | |manuals= | ||

* [ | * [[Media:070-1599-00.pdf | P7001 Operators Manual]] | ||

* [ | * [[Media:070-1600-00.pdf | P7001 Specs and Calibration]] | ||

* [ | * [[Media:070-1604-00.pdf | P7001 Main Interface]] | ||

* [ | * [[Media:070-1605-00.pdf | P7001 Core Memory]] | ||

* [ | * [[Media:070-1606-00.pdf | P7001 Semiconductor Memory]] | ||

* [[Media:070-1612-00.pdf| | * [[Media:070-1608-00.pdf | P7001 Display Generator]] | ||

* [ | * [[Media:070-1609-00.pdf | P7001 Readout Interface]] | ||

* [[Media:Tek p7001 670-2379-00 interim manual.pdf| | * [[Media:070-1610-00.pdf | P7001 Front Panel / Z Axis]] | ||

* [ | * [[Media:070-1612-00.pdf | P7001 Checkout Software Manual]] | ||

* [ | * [[Media:070-1654-01.pdf | P7001 CP Bus Interface 021-0116-00 & up]] | ||

* [ | * [[Media:Tek p7001 670-2379-00 interim manual.pdf | P7001 A/D Converter Interim Manual]] | ||

* [ | * [[Media:070-1809-00.pdf | P7001 A/D Converter]] | ||

* [ | * [[Media:070-1810-00.pdf | P7001 Sample/Hold]] | ||

* [[Media:070-2623-00.pdf| | * [[Media:070-1882-00.pdf | P7001 Processor]] | ||

* [[Media: | * [[Media:070-1890-00.pdf | P7001 Power Supply]] | ||

* [[Media:061-1344-00.pdf| | * [[Media:070-2623-00 1978.pdf | P7001 IEEE 488 (GPIB) Interface]] (1978) | ||

* [[Media:070-2846-00.pdf| | * [[Media:070-2623-00.pdf | P7001 IEEE 488 (GPIB) Interface]] (1986, OCR) | ||

* [[Media:P7001 Calculator Aided Measurements.pdf | P7001 / 31 Calculator Aided Measurements]] | |||

* [[Media:070-1971-00.pdf|DPO Interface Concepts using the DPO/CP Bus Interface]] | |||

''Missing, please upload:'' | |||

* [[Media:061-1344-00.pdf | Hardware Signal Averager (HSA) Manual 061-1344-00]] | |||

* [[Media:070-2846-00.pdf | Hardware Signal Averager (HSA) Manual 070-2846-00]] | |||

{{ROM Images}} | |||

'''[[021-0206-00]] GPIB Interface:''' | |||

* U215: [[Media:160-0174-00.bin|160-0174-00]] | |||

* U214: [[Media:160-0175-00.bin|160-0175-00]] | |||

* U213: [[Media:160-0176-00.bin|160-0176-00]] | |||

* U212: [[Media:160-0177-00.bin|160-0177-00]] | |||

* U115: [[Media:160-0178-00.bin|160-0178-00]] | |||

* U114: [[Media:160-0179-00.bin|160-0179-00]] | |||

* U113: [[Media:160-0180-00.bin|160-0180-00]] | |||

}} | }} | ||

The '''Tektronix P7001''' is a digitizer, processor, and memory for the [[7704A]] oscilloscope. The P7001 can also be connected to an [[SPS|external computer]] which then is able to process the digitized signals. The complete system was called "Digital Processing Oscilloscope" or "DPO" for short and was presented to the public on 26 March 1973 at the IEEE Intercon in New York City. | The '''Tektronix P7001''' is a digitizer, processor, and memory for the [[7704A]] oscilloscope. The P7001 can also be connected to an [[SPS|external computer]] which then is able to process the digitized signals. The complete system was called "Digital Processing Oscilloscope" or "DPO" for short and was presented to the public on 26 March 1973 at the IEEE Intercon in New York City. | ||

| Line 38: | Line 56: | ||

{{BeginSpecs}} | {{BeginSpecs}} | ||

{{Spec | Bandwidth | 175 MHz }} | {{Spec | Bandwidth | 175 MHz }} | ||

{{Spec | Resolution | 10 bit (V), 9 bit (H) }} | {{Spec | Resolution | 10 bit (V), 9 bit (H) }} | ||

{{Spec | Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) <br />plus 12 messages with 80 characters}} | {{Spec | Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) <br />plus 12 messages with 80 characters}} | ||

{{Spec | Sampling rate | 150 kHz ±30 kHz }} | {{Spec | Sampling rate | 150 kHz ±30 kHz }} | ||

{{Spec | Single shot performance | 500 μs/Div }} | {{Spec | Single-shot performance | 500 μs/Div }} | ||

{{Spec | External interface | 16 bit parallel, proprietary "[[CP bus]]" (dual 37-pin [[Sub-D connector]]s) interfacing with Tektronix CP-1100 or CP-4100 series controllers | {{Spec | External interface | 16 bit parallel, proprietary "[[CP bus]]" (dual 37-pin [[Sub-D connector]]s) interfacing with Tektronix CP-1100 or CP-4100 series controllers; other interfaces available }} | ||

{{Spec | Power | {{Spec | Power | 115 V, 60 Hz; 7704A: 180 W, P7001: 120 W }} | ||

{{Spec | Dimensions | {{Spec | Dimensions | 12" (30.6 cm) W × 18.9" (47.5 cm) H × 22.7" (57.7 cm) D }} | ||

{{Spec | | {{Spec | Weight | 48 lbs (21.8 kg) without plugins }} | ||

{{Spec | | {{Spec | Temperature Range | 0°C to +50°C operating }} | ||

{{EndSpecs}} | {{EndSpecs}} | ||

==Links== | |||

* [https://vintagetek.org/p7001/ P7001 history] @ VintageTek.org | |||

* [https://vintagetek.org/wp-content/uploads/2018/11/IEEENAB1973_TW_03231973.pdf Article about IEEE Intercon 1973] @ VintageTek.org | |||

* [https://groups.io/g/TekScopes/topic/7654269 Thread on P7001 and interfaces] | |||

* [https://aei.pitt.edu/83031/1/1974.11.pdf CAMAC bulletin, Nov 1974] with a description of the [[CAMAC]] interface for Tektronix digitizers | |||

* [[Patent US 4225940A|United States Patent 4225940A Oscilloscope system for acquiring, processing, and displaying information]] | |||

* [[Patent US 3824382A|United States Patent 3824382A Vector Generator]] | |||

* [[WP1000]] | |||

{{Documents|Link=P7001}} | |||

==Internals== | ==Internals== | ||

| Line 58: | Line 86: | ||

The P7001 has its own power supply built into it, independent of the power supply in the acquisition unit of the 7704A. | The P7001 has its own power supply built into it, independent of the power supply in the acquisition unit of the 7704A. | ||

The Acquisition Unit of the 7704A, the P7001 Processor, and the Display Unit of the 7704A are connected by the | The Acquisition Unit of the 7704A, the P7001 Processor, and the Display Unit of the 7704A are connected by the Acquisition-Processor-Display (APD) Interface. | ||

Acquisition-Processor-Display (APD) Interface. | |||

===Asynchronus Bus=== | ===Asynchronus Bus=== | ||

<gallery> | <gallery> | ||

Tek_P7001_Buspriority.jpg | Tek_P7001_Buspriority.jpg|Interrupt priority om the internal bus. | ||

</gallery> | </gallery> | ||

To provide maximum flexibility all P7001 circuit cards are connected over an 16 bit asynchronous bus with 13 address lines. The bus is mostly implemented as etched lines on the Main Interface Board. | To provide maximum flexibility all P7001 circuit cards are connected over an 16 bit asynchronous bus with 13 address lines. The bus is mostly implemented as etched lines on the Main Interface Board. High speed signals are sent through coaxial cables that connect to the cards using [[Peltola connector]]s. A serially connected line, or daisy chain, in the bus establishes device priority. This signal is called "Data Channel Grant Line". Each card has a specific location in the DPO. The position determines the priority that each card has in the use of the address and data buses. Unused slots must be fitted with a jumper card to close the daisy chain. Most of the card-specific signals are routed over [[Harmonica connector|Harmonica connectors]]. This enables the possibility to be able to swap around cards or to change the order of signal processing. This was done, for example, to give the HSA card access to the lights in the front panel. | ||

===Front Panel & Z-Axis boards=== | ===Front Panel & Z-Axis boards=== | ||

<gallery> | <gallery> | ||

P7001 front.jpg | P7001 front.jpg|Front view of the p7001 | ||

P7001 frontpanel back.jpg | P7001 frontpanel back.jpg|Rear side of the front panel | ||

P7001 z-axis front panel.jpg | P7001 z-axis front panel.jpg|Z Axis & Front panel board - with [[WP1000AF|Mod 515]] | ||

</gallery> | </gallery> | ||

The Front Panel board contains coding and debouncing logic for the 28 pushbuttons and driver logic for the 15 status indicators. The Z-Axis/Front panel card contains circuits for system control and the P7001 status latches. Bus termination, Z-Axis switching circuits and Z Axis Valid sensing are also located on this card. Eighteen of the front-panel buttons are used to communicate with the computer. The SEND and RECEIVE buttons direct the computer to transfer waveforms. The 16 Program call buttons on the right side of the front panel are used to execute user-definable programs on the computer. | The Front Panel board contains coding and debouncing logic for the 28 pushbuttons and driver logic for the 15 status indicators. The Z-Axis/Front panel card contains circuits for system control and the P7001 status latches. Bus termination, Z-Axis switching circuits and Z Axis Valid sensing are also located on this card. Eighteen of the front-panel buttons are used to communicate with the computer. The SEND and RECEIVE buttons direct the computer to transfer waveforms. The 16 Program call buttons on the right side of the front panel are used to execute user-definable programs on the computer. | ||

| Line 77: | Line 104: | ||

===Memory=== | ===Memory=== | ||

<gallery> | <gallery> | ||

Tek_P7001_CoreMem_DataRegister.jpg | Tek_P7001_CoreMem_DataRegister.jpg|Core Memory - Data Register board | ||

Tek_P7001_CoreMem_controller.jpg | Tek_P7001_CoreMem_controller.jpg|Core Memory - Controller board | ||

P7001 CORE DETAIL01.JPG | P7001 CORE DETAIL01.JPG|High-Res picture of the magnetic-memory cores | ||

P7001 2k memory.jpg | P7001 2k memory.jpg|Semiconductor memory, 2k variant | ||

</gallery> | </gallery> | ||

Several types of memory configurations were available: 1k, 2k, 3k or 4k semiconductor memory and also 4k non-volatile core memory. All configurations were available through the whole lifecycle of the P7001. The memory serves to store the acquired waveforms and their associated scale factors. It also stores the computer output for display. Depending on the configuration the following storing capabilities are available: | Several types of memory configurations were available: 1k, 2k, 3k or 4k semiconductor memory and also 4k non-volatile core memory. All configurations were available through the whole lifecycle of the P7001. The memory serves to store the acquired waveforms and their associated scale factors. It also stores the computer output for display. Depending on the configuration the following storing capabilities are available: | ||

| Line 126: | Line 153: | ||

===Readout Interface=== | ===Readout Interface=== | ||

<gallery> | <gallery> | ||

P7001 readout interface.jpg | P7001 readout interface.jpg|Readout Interface card | ||

</gallery> | </gallery> | ||

There are two readout devices in the DPO. One is the readout board in the acquisition unit of the 7704A and the other is the readout interface card in the P7001. In the modes "PLUG-INS" or "STORE" all readout information displayed on the CRT come directly from the plugins. In "STORE" mode the readout interface digitizes these informations, converts them to ASCII-data and stores it in memory. In the modes "BOTH" or "MEMORY" the readout interface converts the ASCII data back to readout information and displays them on the CRT. | There are two readout devices in the DPO. One is the readout board in the acquisition unit of the 7704A and the other is the readout interface card in the P7001. In the modes "PLUG-INS" or "STORE" all readout information displayed on the CRT come directly from the plugins. In "STORE" mode the readout interface digitizes these informations, converts them to ASCII-data and stores it in memory. In the modes "BOTH" or "MEMORY" the readout interface converts the ASCII data back to readout information and displays them on the CRT. | ||

| Line 132: | Line 159: | ||

===Display Generator=== | ===Display Generator=== | ||

<gallery> | <gallery> | ||

P7001 display generator.jpg | P7001 display generator.jpg|Display Generator card | ||

</gallery> | </gallery> | ||

The Display Generator card generates the CRT display of either real-time computer output (XY mode) or data stored in the processors memory (XT mode). Any combination of the stored and acquired waveforms may be displayed simultaneously. Also, since the display generator operates independent of other devices, changing data may be viewed during a store operation. The Display Generator card has a set of jumpers which switch the CRT output between vector and dot display. | The Display Generator card generates the CRT display of either real-time computer output (XY mode) or data stored in the processors memory (XT mode). Any combination of the stored and acquired waveforms may be displayed simultaneously. Also, since the display generator operates independent of other devices, changing data may be viewed during a store operation. The Display Generator card has a set of jumpers which switch the CRT output between vector and dot display. | ||

| Line 141: | Line 168: | ||

===A/D Converter=== | ===A/D Converter=== | ||

<gallery> | <gallery> | ||

P7001 adc.jpg | P7001 adc.jpg|AD-Converter card, front view | ||

P7001 adc rear.jpg | P7001 adc rear.jpg|AD-Converter card, rear view | ||

P7001 adc probe points.jpg | P7001 adc probe points.jpg|AD-Converter card, probe points details | ||

</gallery> | </gallery> | ||

The A/D Converter uses a successive approximation technique to digitize the vertical and horizontal samples. The vertical resolution is 10 bits, the horizontal resolution 9 bits. It is worth mentioning that the vertical part of the signal is digitized in a range of 10 divisions. As a result, even signal components that are slightly above or below the screen edge are captured. A two bit memory location code (A, B, C or D) is added to the converted horizontal data. The result is the direct memory address at which the vertical data is stored to. For sweeps slower or equal to 500 μs/Div all 512 waveform points are digitized in one sweep. For faster sweep speeds the samples will be taken out-of-order with respect to their equivalent time in the waveform. In this case subsequent sweeps are needed complete the digitized data. The computer has direct access to the register of the A/D converter and may at any time read the last vertical sample. This makes it possible to create arrays with more than 512 elements. | The A/D Converter uses a successive approximation technique to digitize the vertical and horizontal samples. The vertical resolution is 10 bits, the horizontal resolution 9 bits. It is worth mentioning that the vertical part of the signal is digitized in a range of 10 divisions. As a result, even signal components that are slightly above or below the screen edge are captured. A two bit memory location code (A, B, C or D) is added to the converted horizontal data. The result is the direct memory address at which the vertical data is stored to. For sweeps slower or equal to 500 μs/Div all 512 waveform points are digitized in one sweep. For faster sweep speeds the samples will be taken out-of-order with respect to their equivalent time in the waveform. In this case subsequent sweeps are needed complete the digitized data. The computer has direct access to the register of the A/D converter and may at any time read the last vertical sample. This makes it possible to create arrays with more than 512 elements. | ||

| Line 149: | Line 176: | ||

===Hardware Signal Averager=== | ===Hardware Signal Averager=== | ||

<gallery> | <gallery> | ||

P7001 HSA timing.jpg | P7001 HSA timing.jpg|Timing board of the HSA module | ||

P7001 HSA memory.jpg | P7001 HSA memory.jpg|Memory board of the HSA module | ||

Tek_p7001_hsa_lights.jpg|Front Panel Lights #13 & #14 are controlled by the HSA module | |||

Electronics_1978_03_26_pag24_25.jpg|Advert from Electronics magazine with reference to the HSA module | |||

</gallery> | </gallery> | ||

For DPOs which are connected via the fast CP bus, it is no problem to transfer several data sets over the interface and then have the computer calculate the averaged | |||

The HSA card was introduced as an additional option to the GPIB interface in 1978. For DPOs which are connected via the fast CP bus, it is no problem to transfer several data sets over the interface and then have the computer calculate the averaged waveforms. But with the relatively slow GPIB Interface this procedure is impractical. The optional HSA card solves this problem by locally computing the averaged waveform of up to 4096 single waveforms. The HSA card also has the ability to calculate the histogram of a waveform. The histogram will be displayed horizontally at the lower third of the CRT. The lights of the PROGRAMM CALL buttons #13,#14 and #16 are normally connected to the external interface card of the P7001. During the installation procedure of the card, the backplane is reconfigured to allow the HSA card to control the lights #13 and #14. The HSA card comes with its own semiconductor Memory. This can lead to a configuration where a P7001 is equipped with both magnetic-core and semiconductor memory at the same time. | |||

===External Interfaces=== | ===External Interfaces=== | ||

<gallery> | <gallery> | ||

P7001 dpo controller board.jpg | P7001 dpo controller board.jpg|CP bus interface card | ||

P7001 GPIB adaper left dismounted.jpg | P7001 GPIB adaper left dismounted.jpg|RAM portion & bus logic of the GPIB Interface | ||

P7001 GPIB adaper right dismounted.jpg | P7001 GPIB adaper right dismounted.jpg|CPU portion of the GPIB Interface | ||

</gallery> | </gallery> | ||

The external interface card provides a bilateral link between the P7001 and an external controller. The controller has full access to all programmable functions in the Processor, and the P7001, in turn, may interrupt the controller at any time. During the production time of the P7001, the following interfaces were gradually developed: | The external interface card provides a bilateral link between the P7001 and an external controller. The controller has full access to all programmable functions in the Processor, and the P7001, in turn, may interrupt the controller at any time. During the production time of the P7001, the following interfaces were gradually developed: | ||

| Line 170: | Line 201: | ||

| DPO to Data General Nova | | DPO to Data General Nova | ||

| [[021-0113-00]] | | [[021-0113-00]] | ||

| [[Media:070-1776-00.pdf|070-1776-00 | | [[Media:070-1776-00.pdf|070-1776-00]] | ||

|- | |- | ||

| DPO to APD ([[CP Bus]]) | | DPO to APD ([[CP Bus]]) | ||

| [[021-0116-00]] | | [[021-0116-00]] | ||

| [[Media:070-1654-00.pdf|070-1654-00 | | [[Media:070-1654-00.pdf|070-1654-00]] | ||

|- | |- | ||

| DPO to CP1100 ([[CP Bus]]) | | DPO to CP1100 ([[CP Bus]]) | ||

| [[021-0117-00]] | | [[021-0117-00]] | ||

| [ | | [[Media:070-1654-01.pdf|070-1654-01]] | ||

|- | |- | ||

| DPO to [[31|TEK31]] calculator | | DPO to [[31|TEK31]] calculator | ||

| [[021-0127-00]] | | [[021-0127-00]] | ||

| [[Media:070-1777-00.pdf|070-1777-00 | | [[Media:070-1777-00.pdf|070-1777-00]] | ||

|- | |- | ||

| DPO to [[CAMAC]] | | DPO to [[CAMAC]] | ||

| [[021-0146-00]] | | [[021-0146-00]] | ||

| | | ? | ||

|- | |- | ||

| DPO to [[4010|4010 Family]] | | DPO to [[4010|4010 Family]] | ||

| [[021-0175-00]] | | [[021-0175-00]] | ||

| [[Media:070-1936-00.pdf|070-1936-00 | | [[Media:070-1936-00.pdf|070-1936-00]] | ||

|- | |- | ||

| DPO to [[GPIB_interface|GPIB]] | | DPO to [[GPIB_interface|GPIB]] | ||

| [[021-0206-00]] | | [[021-0206-00]] | ||

| [[Media:070-2623-00.pdf|070-2623-00 | | [[Media:070-2623-00.pdf|070-2623-00]] | ||

|} | |} | ||

===Power Supply=== | ===Power Supply=== | ||

<gallery> | <gallery> | ||

P7001 ps.jpg | P7001 ps.jpg|Power supply | ||

</gallery> | </gallery> | ||

The power supply in the P7001 is a reduced version of the power supply in the 7704A. Both power supplies are connected together using a relay in a master-slave configuration. | The power supply in the P7001 is a reduced version of the power supply in the 7704A. Both power supplies are connected together using a relay in a master-slave configuration. | ||

| Line 208: | Line 239: | ||

Tek 7704a p7001 vt.jpg|P7001 in [[7704A|7704A]] | Tek 7704a p7001 vt.jpg|P7001 in [[7704A|7704A]] | ||

Tek_P7001_B010101.JPG|First P7001 (B010101) running the pulse parameter analysis program | Tek_P7001_B010101.JPG|First P7001 (B010101) running the pulse parameter analysis program | ||

Tek 7704a p7001 2.jpg|P7001 in 7704A | Tek 7704a p7001 2.jpg|P7001 in 7704A. The Mainframe contains [[WP1000AF|Mod 515C]] | ||

Tek 7704a p7001 nasa.jpg | Tek 7704a p7001 nasa.jpg|P7001 | ||

Tek_p7001_purple.jpg|P7001 with purple decals | Tek_p7001_purple.jpg|P7001 with purple decals | ||

</gallery> | </gallery> | ||

| Line 278: | Line 309: | ||

Core20.jpg|Core closeup | Core20.jpg|Core closeup | ||

Core17.jpg|Core closeup | Core17.jpg|Core closeup | ||

P7001 CORE DETAIL01.JPG|High Resolution view of partial core module. | P7001 CORE DETAIL01.JPG|High Resolution view of partial core module. One core has a diameter of 20 mil (0.02" or ~0.5 mm). | ||

</gallery> | </gallery> | ||

'''Semiconductor memory (optional)''' | '''Semiconductor memory (optional)''' | ||

| Line 330: | Line 361: | ||

<gallery> | <gallery> | ||

Tek_P7001_Controller_XY_Mode.jpg|A connected computer has direct access to the Display Generator. This allows software-controlled live movements of the Beam. | Tek_P7001_Controller_XY_Mode.jpg|A connected computer has direct access to the Display Generator. This allows software-controlled live movements of the Beam. | ||

Tek_P7001_Controller_XY_Mode2.jpg|Another example of software controlled X/Y mode. 124900 vectors are drawn within 1 second. | |||

</gallery> | </gallery> | ||

'''Design Team''' | '''Design Team''' | ||

[[File:Tek_P7001_Designteam.jpg|thumb|650px|right|Key design Team of the P7001 ''(click to enlarge)'']] | |||

* Program Manager Computer Aided Measurement Group: [[Hiro Moriyasu]] | |||

* Hardware and Analog Circuits Project Leader: [[Luis Navarro]] | |||

* Logic Design Project Leader: [[Jack Gilmore]] | |||

* Software Project Leader: [[Bruce Hamilton]] | |||

* Mechanical Design Leader: [[Bob Shand]] | |||

* Sample and Hold: [[Jack Robinson]], [[Bill Lucas]] | |||

* A/D Converter: [[Jack Grimes]], [[Dennis Keldsen]], [[Mohamed Saba]] | |||

* Memory: [[Dick Beatty]] | |||

* Vector Generator: [[Wayne Eshelman]] | |||

* Interface I/O: [[George Rhine]] | |||

* Readout Interface: [[Bill Markwart]] | |||

* Mechanical Design: [[Marlow Butler]], [[Carl Dalby]], [[Colin Doward]] | |||

* Manufacturing Responsibility: [[Gale Byers]] | |||

'''Development''' | '''Development''' | ||

| Line 345: | Line 386: | ||

'''Scope-Mobile Carts''' | '''Scope-Mobile Carts''' | ||

At least 3 different Scope-Mobile Carts were designed in order to be able to move the DPO with the attached minicomputer around. The [[202|202D]] and the 202R were introduced together with the P7001 in 1973 and the [[Model 7|Model 7 Rack Cart]] was officially released in 1977. | |||

<gallery> | <gallery> | ||

Tek_scopecart_202d.jpg|Scopecart [[202|202D]] with DPO and | Tek_scopecart_202d.jpg|Scopecart [[202|202D]] with DPO and a DEC PDP-11/05 minicomputer | ||

Tek_scopecart_202d_dim.jpg|Dimensions of Scopecart 202D | Tek_scopecart_202d_dim.jpg|Dimensions of Scopecart 202D | ||

TEK_202R_front.jpg|Scopecart 202R front side | TEK_202R_front.jpg|Scopecart 202R front side | ||

| Line 356: | Line 398: | ||

</gallery> | </gallery> | ||

'''Options''' | |||

Not all options were available through the whole lifecycle of the DPO. As an Example: 4k Core Memory was the default configuration in early production years and became an option in later years. Other options like the CP bus Interface got an update and a new part number. | |||

{| class="wikitable sortable" | {| class="wikitable sortable" | ||

| Line 393: | Line 435: | ||

| 31 | | 31 | ||

| Add IEEE 488 Bus Interface | | Add IEEE 488 Bus Interface | ||

| 021-0206-00 | | [[021-0206-00]] | ||

| +$2000 | | +$2000 | ||

|- | |- | ||

| 32 | | 32 | ||

| Add CP Bus Interface | | Add CP Bus Interface | ||

| 021-0116-00,<br />021-0116-01,<br />021-0116-02 or<br />021-0116-03 | | [[021-0116-00]],<br />021-0116-01,<br />021-0116-02 or<br />021-0116-03 | ||

| +$475 | | +$475 | ||

|- | |- | ||

| Line 407: | Line 449: | ||

|- | |- | ||

|} | |} | ||

==Programming Examples== | ==Programming Examples== | ||

| Line 417: | Line 458: | ||

Tek_P7001_Addressmap.jpg | Tek_P7001_Addressmap.jpg | ||

</gallery> | </gallery> | ||

The following examples might help to understand the programming differences between 16- and 10-bit data access and high level information access. | |||

Example A: 16 bit Memory or Register Access | All three examples write the word "HELLO" to the Location D in Message Field 2 and instruct the Readout Interface to show this Message on the CRT. | ||

While the data bus of the P7001 is 16 bit wide, most of the stored data is only 10 bit wide. | Descriptions of the Readout Interface Status Register and data format can be seen in the images above. There is also an overview of the P7001 Address Map. | ||

''Example A: 16 bit Memory or Register Access'' | |||

While the data bus of the P7001 is 16 bit wide, most of the stored data is only 10 bit wide. More importantly, bit 0 of the needed data word is not always aligned to bit 0 of the data bus. A very good example of this design is the data format of the Readout Interface. Bit 0 of the readout information starts at bit 5 on the data bus. To get or write the readout information we have to shift and crop or expand the data bits. | |||

The ASCII code for the character "H" is 72. Converted to 16 bit binary and shifted 5 times to the left: 0000100100000000 or in octal notation: 004400. Our destination message field starts at memory location 3456 (octal: 6600). We can do the same calculations for the other readout characters. At the end we have to instruct the Readout Interface to display the message. For displaying Location D of | The ASCII code for the character "H" is 72. Converted to 16 bit binary and shifted 5 times to the left: 0000100100000000 or in octal notation: 004400. Our destination message field starts at memory location 3456 (octal: 6600). We can do the same calculations for the other readout characters. At the end we have to instruct the Readout Interface to display the message. For displaying Location D of Message field 2, we have to set the bits 6 and 14 of the Readout Interface Register. | ||

In binary notation: 0100000001000000 | In binary notation: 0100000001000000 | ||

In octal notation: 040100 | In octal notation: 040100 | ||

| Line 429: | Line 472: | ||

The final program might look like: | The final program might look like: | ||

<nowiki> | |||

SEND ("ADR 3456", "OCT 004400") // 'H' -> ASCII 72 -> 0000100100000000 -> 004400 | SEND ("ADR 3456", "OCT 004400") // 'H' -> ASCII 72 -> 0000100100000000 -> 004400 | ||

SEND ("ADR 3457", "OCT 004240") // 'E' -> ASCII 69 -> 0000100010100000 -> 004240 | SEND ("ADR 3457", "OCT 004240") // 'E' -> ASCII 69 -> 0000100010100000 -> 004240 | ||

| Line 435: | Line 478: | ||

SEND ("ADR 3459", "OCT 004600") // 'L' -> ASCII 76 -> 0000100110000000 -> 004600 | SEND ("ADR 3459", "OCT 004600") // 'L' -> ASCII 76 -> 0000100110000000 -> 004600 | ||

SEND ("ADR 3460", "OCT 004740") // 'O' -> ASCII 79 -> 0000100111100000 -> 004740 | SEND ("ADR 3460", "OCT 004740") // 'O' -> ASCII 79 -> 0000100111100000 -> 004740 | ||

SEND ("ADR 7296", "OCT 040100") // Show | SEND ("ADR 7296", "OCT 040100") // Show Message field 2 / Location D on CRT | ||

</nowiki> | </nowiki> | ||

''Example B: 10 bit Memory Access'' | |||

Example B: 10 bit Memory Access | Most of the time we're dealing with 10 bit data information. To make life easier, Tektronix implemented the "WRD" instruction set on the controller. This instruction set handles the data conversion between the ASCII data and the 16 bit universe of the P7001. The command also implements an auto-increment for the address data. | ||

Most of the time we're dealing with 10 bit data information. To make life easier Tektronix implemented the "WRD" instruction set on the controller. This instruction set handles the data conversion between the ASCII data and the 16 bit universe of the P7001. The command also implements an auto-increment for the address data. | |||

The new program looks like: | The new program looks like: | ||

<nowiki> | |||

SEND ("ADR 3456" , "WRD 72") //'H' | SEND ("ADR 3456" , "WRD 72") //'H' | ||

SEND ("WRD 69") //E -> the destination address is auto-incremented | SEND ("WRD 69") //E -> the destination address is auto-incremented | ||

| Line 451: | Line 494: | ||

</nowiki> | </nowiki> | ||

''Example C: High Level Instruction Set'' | |||

Example C: High Level Instruction Set | Finally, there is a high-level command implemented which sends the readout data in one line: | ||

Finally there is a high-level command implemented which sends the readout data in one line: | <nowiki> | ||

SEND ("ADR 3456", "SCL HELLO ") // The last space is needed as terminator character. | SEND ("ADR 3456", "SCL HELLO ") // The last space is needed as terminator character. | ||

SEND ("ADR 7296", "OCT 040100") // Show | SEND ("ADR 7296", "OCT 040100") // Show Message field 2 / Location D on CRT | ||

</nowiki> | </nowiki> | ||

| Line 465: | Line 507: | ||

Tek_P7001_Controller_XY_Mode.jpg | Tek_P7001_Controller_XY_Mode.jpg | ||

</gallery> | </gallery> | ||

The Display Generator Status Register is located at memory location 7168 (octal: 16000) | A description of the Display Generator Status Register and Data Format can be seen in the images above. | ||

To enable the software-controlled X-Y Display and waveform "D" we have to set bit 13 and 6 in this register. | |||

The Display Generator Status Register is located at memory location 7168 (octal: 16000). | |||

To enable the software-controlled X-Y Display and waveform "D", we have to set bit 13 and 6 in this register. | |||

In binary notation: 0010000001000000 | In binary notation: 0010000001000000 | ||

In octal notation: 020100 | In octal notation: 020100 | ||

To display a shape we have to continuously move the beam around from point to point. The X/Y coordinates for the lower left point on the CRT is 7680/0 (octal: 17000/0) and for the upper right point 8191/1023 (octal: 17777/1777). We can also control the beam intensity of each movement between 0 (disabled) and 3 (full brightness). The Y-value and brightness level are encoded into the Display Generators Data Format and the result is sent to the desired X-Address of the Display Generator. | To display a shape, we have to continuously move the beam around from point to point. The X/Y coordinates for the lower left point on the CRT is 7680/0 (octal: 17000/0), and for the upper right point 8191/1023 (octal: 17777/1777). We can also control the beam intensity of each movement between 0 (disabled) and 3 (full brightness). The Y-value and brightness level are encoded into the Display Generators Data Format and the result is sent to the desired X-Address of the Display Generator. | ||

The resulting program in pseudo-code: | The resulting program in pseudo-code: | ||

<nowiki> | |||

SEND ("ADR 7168", "OCT 020100") //enable X-Y Mode for Waveform "D" | SEND ("ADR 7168", "OCT 020100") //enable X-Y Mode for Waveform "D" | ||

| Line 496: | Line 536: | ||

SEND ("ADR 7168", "OCT 000100") //disable X-Y Mode for Waveform "D" | SEND ("ADR 7168", "OCT 000100") //disable X-Y Mode for Waveform "D" | ||

</nowiki> | </nowiki> | ||

==Bugs & Errors== | ==Bugs & Errors== | ||

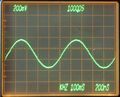

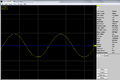

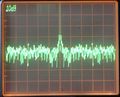

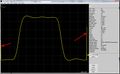

===Design Flaw of the A/D Converter=== | |||

<gallery> | <gallery> | ||

Tek_P7001_ADC_designflaw01.jpg | Tek_P7001_ADC_designflaw01.jpg | ||

Tek_P7001_ADC_bug.jpeg| | Tek_P7001_ADC_bug.jpeg|Example of invalid start & end points | ||

</gallery> | </gallery> | ||

The dynamic range of the sampled waveform is greater than the converted output of the A/D converter. Any sampled point which is left to the | The dynamic range of the sampled waveform is greater than the converted output of the A/D converter. | ||

Any sampled point which is left to the CRT viewing area will be added to memory location 0, and any point which is right to the CRT viewing area will be added to memory location 511. | |||

The end points (0 and 511) of the acquired waveform data should be considered invalid for measurement purposes. | |||

[[Media:ServiceTekNotes 25 Sep 1982.pdf|ServiceTekNotes Issue 25, Sep 1982]] describes the problem and shows a possible solution. | |||

===Firmware Bug in GPIB interface=== | |||

Affected Firmware versions: all | |||

Due to an error in the firmware, pin 9 of U123 is always configured as an output pin. This pin is directly connected to an output of the line driver IC U321. | |||

To prevent damage to the PIA chip, it is recommended to remove the line driver U321. Since U321 is only needed for internal testing, it can be removed without any problems. | |||

==Catalogs & Advertising== | ==Catalogs & Advertising== | ||

| Line 529: | Line 571: | ||

Tek_P7001-1973-Advertising.pdf|Typical DPO advertising in 1973 | Tek_P7001-1973-Advertising.pdf|Typical DPO advertising in 1973 | ||

Tek_P7001_31_just_married.jpg|DPO+[[31]] Just Married advertising from 1973 | Tek_P7001_31_just_married.jpg|DPO+[[31]] Just Married advertising from 1973 | ||

Tek_P7001_Electronics_1973_08_16.pdf| PDO advertising in 'Electronics' magazine july 1973 | |||

Tek_P7001_advertising_1977.pdf|Typical DPO advertising in 1977 | Tek_P7001_advertising_1977.pdf|Typical DPO advertising in 1977 | ||

Tek_P7001_Electronics_1978_03_16_GPIB.jpg|1978 advert about the new options GPIB interface and hardware signal averager | |||

</gallery> | </gallery> | ||

==Introduction March 1973== | ===Introduction March 1973=== | ||

<gallery> | <gallery> | ||

BillW_HiroM_DPO.jpg|[[Bill Walker]] and [[Hiro Moriyasu]] with the P7001 at the IEEE Intercon 1973 in New York | BillW_HiroM_DPO.jpg|[[Bill Walker]] and [[Hiro Moriyasu]] with the P7001 at the IEEE Intercon 1973 in New York | ||

| Line 539: | Line 583: | ||

</gallery> | </gallery> | ||

==Appearance in Tektronix Magazines== | ===Name change=== | ||

Early units are named "Tektronix P7001 Processor" - later units (probably starting with B1XXXXX) are named "Tektronix P7001 Digitizer". | |||

<gallery> | |||

Tek_p7001_processor.jpg|Older name | |||

Tek_p7001_digitizer.jpg|Newer name | |||

</gallery> | |||

===Field of Application=== | |||

<gallery> | |||

RCA_Engineer_1979-08-09.pdf|Usage of the P7001 & [[7J20]] at RCA | |||

RCA_Engineer_1980-04-05-06.pdf|Competitive Product Analysis with the P7001 at RCA | |||

</gallery> | |||

===Appearance in Tektronix Magazines=== | |||

* [[Media:ServiceTekNotes 25 Sep 1982.pdf|ServiceTekNotes Issue 25, Sep 1982 about the A/D converters design flaw]] | * [[Media:ServiceTekNotes 25 Sep 1982.pdf|ServiceTekNotes Issue 25, Sep 1982 about the A/D converters design flaw]] | ||

* [[Media:Tekscope 1973 V5 N2 Mar 1973.pdf | TekScope Vol. 5 No. 2, Mar-Apr 1973 about the introduction of the P7001]] | * [[Media:Tekscope 1973 V5 N2 Mar 1973.pdf | TekScope Vol. 5 No. 2, Mar-Apr 1973 about the introduction of the P7001]] | ||

=== | ==Components== | ||

{{Parts|P7001}} | |||

{{ | |||

[[Category:7000 series scopes]] | [[Category:7000 series scopes]] | ||

Latest revision as of 01:37, 7 July 2024

The Tektronix P7001 is a digitizer, processor, and memory for the 7704A oscilloscope. The P7001 can also be connected to an external computer which then is able to process the digitized signals. The complete system was called "Digital Processing Oscilloscope" or "DPO" for short and was presented to the public on 26 March 1973 at the IEEE Intercon in New York City.

The design of the P7001 assumes it will be part of a 7704A system, and that the 7704A will be displaying a steady trace. The vertical and horizontal plug-ins control the beam as they would in any 7000-series scope.

The P7001 periodically samples the horizontal and vertical signals simultaneously as they pass from the plug-ins to the vertical and horizontal amplifiers. This allows it to fill its memory with data points represented as coordinate pairs, (x1,y1), (x2,y2), (x3,y3), etc. It is not necessary that x2 be greater than x1, i.e. the samples can be taken out-of-order with respect to their equivalent time in the waveform.

Key Specifications

| Bandwidth | 175 MHz |

|---|---|

| Resolution | 10 bit (V), 9 bit (H) |

| Memory | four waveforms, 512 samples each (4K × 10 bit core, or multiple 1k × 10 bit or 2k × 10 bit RAM boards) plus 12 messages with 80 characters |

| Sampling rate | 150 kHz ±30 kHz |

| Single-shot performance | 500 μs/Div |

| External interface | 16 bit parallel, proprietary "CP bus" (dual 37-pin Sub-D connectors) interfacing with Tektronix CP-1100 or CP-4100 series controllers; other interfaces available |

| Power | 115 V, 60 Hz; 7704A: 180 W, P7001: 120 W |

| Dimensions | 12" (30.6 cm) W × 18.9" (47.5 cm) H × 22.7" (57.7 cm) D |

| Weight | 48 lbs (21.8 kg) without plugins |

| Temperature Range | 0°C to +50°C operating |

Links

- P7001 history @ VintageTek.org

- Article about IEEE Intercon 1973 @ VintageTek.org

- Thread on P7001 and interfaces

- CAMAC bulletin, Nov 1974 with a description of the CAMAC interface for Tektronix digitizers

- United States Patent 4225940A Oscilloscope system for acquiring, processing, and displaying information

- United States Patent 3824382A Vector Generator

- WP1000

Documents Referencing P7001

| Document | Class | Title | Authors | Year | Links |

|---|---|---|---|---|---|

| 7000 series brochure March 1973.pdf | Brochure | 7000 series brochure, March 1973 | 1973 | 7A11 • 7A12 • 7A13 • 7A14 • 7A15A • 7A16A • 7A17 • 7A18 • 7A19 • 7A21N • 7A22 • 7B50 • 7B53A • 7B70 • 7B71 • 7B92 • 7CT1N • 7D11 • 7D13 • 7D14 • 7D15 • 7M11 • 7L12 • 7S11 • 7S12 • 7T11 • 7704A • R7704 • 7904 • R7903 • 7603 • R7603 • 7403N • R7403N • 7313 • R7313 • 7613 • R7613 • 7623 • R7623 • P7001 | |

| Tekscope 1973 V5 N2 Mar 1973.pdf | Article | The Oscilloscope with Computing Power | Hiro Moriyasu • Luis Navarro • Jack Gilmore • Bruce Hamilton | 1973 | 7704A • P7001 |

Internals

The signal coming from the acquisition unit enters a fast four-diode sample and hold circuit where it is sampled at 150 ksamples/sec. Each sample is digitized using a successive-approximation scheme. The analog to digital converter is made of several chips: a digital to analog converter, a comparator, and control logic.

The P7001 has its own power supply built into it, independent of the power supply in the acquisition unit of the 7704A.

The Acquisition Unit of the 7704A, the P7001 Processor, and the Display Unit of the 7704A are connected by the Acquisition-Processor-Display (APD) Interface.

Asynchronus Bus

-

Interrupt priority om the internal bus.

To provide maximum flexibility all P7001 circuit cards are connected over an 16 bit asynchronous bus with 13 address lines. The bus is mostly implemented as etched lines on the Main Interface Board. High speed signals are sent through coaxial cables that connect to the cards using Peltola connectors. A serially connected line, or daisy chain, in the bus establishes device priority. This signal is called "Data Channel Grant Line". Each card has a specific location in the DPO. The position determines the priority that each card has in the use of the address and data buses. Unused slots must be fitted with a jumper card to close the daisy chain. Most of the card-specific signals are routed over Harmonica connectors. This enables the possibility to be able to swap around cards or to change the order of signal processing. This was done, for example, to give the HSA card access to the lights in the front panel.

Front Panel & Z-Axis boards

-

Front view of the p7001

-

Rear side of the front panel

-

Z Axis & Front panel board - with Mod 515

The Front Panel board contains coding and debouncing logic for the 28 pushbuttons and driver logic for the 15 status indicators. The Z-Axis/Front panel card contains circuits for system control and the P7001 status latches. Bus termination, Z-Axis switching circuits and Z Axis Valid sensing are also located on this card. Eighteen of the front-panel buttons are used to communicate with the computer. The SEND and RECEIVE buttons direct the computer to transfer waveforms. The 16 Program call buttons on the right side of the front panel are used to execute user-definable programs on the computer.

Memory

-

Core Memory - Data Register board

-

Core Memory - Controller board

-

High-Res picture of the magnetic-memory cores

-

Semiconductor memory, 2k variant

Several types of memory configurations were available: 1k, 2k, 3k or 4k semiconductor memory and also 4k non-volatile core memory. All configurations were available through the whole lifecycle of the P7001. The memory serves to store the acquired waveforms and their associated scale factors. It also stores the computer output for display. Depending on the configuration the following storing capabilities are available:

| Configuration | Waveforms | Readout Scale factors |

Messages |

|---|---|---|---|

| 1k with readout | 1 | 1 | 3 |

| 1k no readout(*) | 2 | 0 | 0 |

| 2k with readout | 2 | 2 | 4 |

| 2k no readout(*) | 4 | 0 | 0 |

| 3k | 4 | 1 | 4 |

| 4k | 4 | 4 | 12 |

* Removing the Readout-Interface card doubles the space for storing waveforms but eliminates the capability of displaying text information.

Readout Interface

-

Readout Interface card

There are two readout devices in the DPO. One is the readout board in the acquisition unit of the 7704A and the other is the readout interface card in the P7001. In the modes "PLUG-INS" or "STORE" all readout information displayed on the CRT come directly from the plugins. In "STORE" mode the readout interface digitizes these informations, converts them to ASCII-data and stores it in memory. In the modes "BOTH" or "MEMORY" the readout interface converts the ASCII data back to readout information and displays them on the CRT.

Display Generator

-

Display Generator card

The Display Generator card generates the CRT display of either real-time computer output (XY mode) or data stored in the processors memory (XT mode). Any combination of the stored and acquired waveforms may be displayed simultaneously. Also, since the display generator operates independent of other devices, changing data may be viewed during a store operation. The Display Generator card has a set of jumpers which switch the CRT output between vector and dot display.

Sample & Hold

The functionality of the Sample & Hold card can be divided into 3 areas: Display switching, sampling and multiplexing. The display switching section determines which waveform (real time or stored) is sent to the CRT and is designed around two Tek-made analog multiplexer chips 155-0022-00. A fast four-diode sample and hold circuit is the heart of the sampling circuit. Regardless of sweep speed, the sample & Hold card takes a sample every 6.5us. At first the vertical axis is sampled, 95 nanoseconds later the horizontal axis and the blanking. In the last stage the sampled signals are time-multiplexed to provide one output to the A/D converter. The complete timing of the sample & hold circuits is controlled by the A/D Converter card.

A/D Converter

-

AD-Converter card, front view

-

AD-Converter card, rear view

-

AD-Converter card, probe points details

The A/D Converter uses a successive approximation technique to digitize the vertical and horizontal samples. The vertical resolution is 10 bits, the horizontal resolution 9 bits. It is worth mentioning that the vertical part of the signal is digitized in a range of 10 divisions. As a result, even signal components that are slightly above or below the screen edge are captured. A two bit memory location code (A, B, C or D) is added to the converted horizontal data. The result is the direct memory address at which the vertical data is stored to. For sweeps slower or equal to 500 μs/Div all 512 waveform points are digitized in one sweep. For faster sweep speeds the samples will be taken out-of-order with respect to their equivalent time in the waveform. In this case subsequent sweeps are needed complete the digitized data. The computer has direct access to the register of the A/D converter and may at any time read the last vertical sample. This makes it possible to create arrays with more than 512 elements.

Hardware Signal Averager

-

Timing board of the HSA module

-

Memory board of the HSA module

-

Front Panel Lights #13 & #14 are controlled by the HSA module

-

Advert from Electronics magazine with reference to the HSA module

The HSA card was introduced as an additional option to the GPIB interface in 1978. For DPOs which are connected via the fast CP bus, it is no problem to transfer several data sets over the interface and then have the computer calculate the averaged waveforms. But with the relatively slow GPIB Interface this procedure is impractical. The optional HSA card solves this problem by locally computing the averaged waveform of up to 4096 single waveforms. The HSA card also has the ability to calculate the histogram of a waveform. The histogram will be displayed horizontally at the lower third of the CRT. The lights of the PROGRAMM CALL buttons #13,#14 and #16 are normally connected to the external interface card of the P7001. During the installation procedure of the card, the backplane is reconfigured to allow the HSA card to control the lights #13 and #14. The HSA card comes with its own semiconductor Memory. This can lead to a configuration where a P7001 is equipped with both magnetic-core and semiconductor memory at the same time.

External Interfaces

-

CP bus interface card

-

RAM portion & bus logic of the GPIB Interface

-

CPU portion of the GPIB Interface

The external interface card provides a bilateral link between the P7001 and an external controller. The controller has full access to all programmable functions in the Processor, and the P7001, in turn, may interrupt the controller at any time. During the production time of the P7001, the following interfaces were gradually developed:

| Description | Part Number | Manual |

|---|---|---|

| DPO to Data General Nova | 021-0113-00 | 070-1776-00 |

| DPO to APD (CP Bus) | 021-0116-00 | 070-1654-00 |

| DPO to CP1100 (CP Bus) | 021-0117-00 | 070-1654-01 |

| DPO to TEK31 calculator | 021-0127-00 | 070-1777-00 |

| DPO to CAMAC | 021-0146-00 | ? |

| DPO to 4010 Family | 021-0175-00 | 070-1936-00 |

| DPO to GPIB | 021-0206-00 | 070-2623-00 |

Power Supply

-

Power supply

The power supply in the P7001 is a reduced version of the power supply in the 7704A. Both power supplies are connected together using a relay in a master-slave configuration.

Pictures

-

Front panel

-

P7001 in 7704A

-

First P7001 (B010101) running the pulse parameter analysis program

-

P7001 in 7704A. The Mainframe contains Mod 515C

-

P7001

-

P7001 with purple decals

Internal

-

Top view

-

Front of backplane

-

main interface board (backplane)

-

Rear of backplane

-

Interunit connector

-

Interunit connector

-

Interunit connector

-

Switching power supply

-

front panel rear

-

extender boards

-

"Dummy-card" or official called "Data Channel Grant jumper card". Needs to be installed in empty slots of Backplane.

-

Data Channel Grant Card

-

Bus Priority of a fully equipped P7001

Keyboard overlay cards

-

blank card for user definable programs

-

Two examples of original overlay cards

-

Example of aftermarket overlay cards

-

All variants of the keyboard overlay cards

-

334-1918-00 - Blue variant of the overlay card

-

334-1918-01 - Yellow variant of the overlay card

-

334-1918-02 - Orange variant of the overlay card

-

334-1918-03 - Grey variant of the overlay card

-

Example of aftermarket overlay cards

-

Example of aftermarket overlay cards

-

Example of aftermarket overlay cards

-

Example of aftermarket overlay cards

External Interfaces (optional)

-

CP Bus interface mounted

-

CP Bus Interface front

-

CP Bus Interface rear

-

CP Bus Connector view

-

GPIB Interface IO board

-

GPIB Interface IO board with shielding

-

GPIB Interface CPU board

-

Rear view of the P7001 GPIB interface

-

Modern clone of the P7001 GPIB interface

-

Modern clone of the P7001 GPIB interface

-

Interface to Tek31 calculator

Sample and Hold Card

-

Vertical sampling bridge

-

Horizontal sampling bridge

-

Sampling strobe generator

-

Sample and hold edge connector

-

Sample and hold transformers

-

Sample and hold transformer

-

Sample and hold rear

Core Memory (optional)

-

Memory data register board

-

Controller & Address Drivers

-

Address decoder

-

Core boards

-

Core memory

-

Core closeup

-

Core closeup

-

High Resolution view of partial core module. One core has a diameter of 20 mil (0.02" or ~0.5 mm).

Semiconductor memory (optional)

-

1K semiconductor memory 670-2981-00

-

2K semiconductor memory (aka "MOS") 670-3035-00

ADC and Display

-

Front panel connections

-

ADC

-

ADC rear

-

Probe points on ADC

-

Display generator

-

Display generator rear

-

Z-axis and panel controller

-

Z-axis and panel controller rear

-

Readout interface

Hardware signal Averager (HSA)

-

HSA timing board. The HSA module (optional) performs signal averaging and can calculate a histogram.

-

HSA memory board.

Schematics

-

Block Diagram

-

Address map of a fully equipped P7001

-

Power supply schematic 1

-

Power supply schematic 2

-

APD Interconnect

Configurations

-

Example of Calculator based system (WP1100) in 1978

-

WP1110 System

-

Example of Controller based system (WP1200) in 1973

-

Example of Controller based system (WP1200) in 1975

Workflow with connected Controller

-

With pressing a program-call button on the P7001...

-

... the displayed signal is digitized...

-

...and transferred to the Controller...

-

...the Controller does some calculations...

-

...and transfers the result back to the P7001

X/Y Mode for external Controller

-

A connected computer has direct access to the Display Generator. This allows software-controlled live movements of the Beam.

-

Another example of software controlled X/Y mode. 124900 vectors are drawn within 1 second.

Design Team

- Program Manager Computer Aided Measurement Group: Hiro Moriyasu

- Hardware and Analog Circuits Project Leader: Luis Navarro

- Logic Design Project Leader: Jack Gilmore

- Software Project Leader: Bruce Hamilton

- Mechanical Design Leader: Bob Shand

- Sample and Hold: Jack Robinson, Bill Lucas

- A/D Converter: Jack Grimes, Dennis Keldsen, Mohamed Saba

- Memory: Dick Beatty

- Vector Generator: Wayne Eshelman

- Interface I/O: George Rhine

- Readout Interface: Bill Markwart

- Mechanical Design: Marlow Butler, Carl Dalby, Colin Doward

- Manufacturing Responsibility: Gale Byers

Development

-

Image of P7001 during development or service. The GPIB Interface card is mounted to the front (Spare Slots J3+J4). Please note the quick fasteners of the front panel

Scope-Mobile Carts

At least 3 different Scope-Mobile Carts were designed in order to be able to move the DPO with the attached minicomputer around. The 202D and the 202R were introduced together with the P7001 in 1973 and the Model 7 Rack Cart was officially released in 1977.

-

Scopecart 202D with DPO and a DEC PDP-11/05 minicomputer

-

Dimensions of Scopecart 202D

-

Scopecart 202R front side

-

Scopecart 202R back side

-

Rack Cart Model 7 with DPO and DEC minicomputer

-

Dimensions of Rack Cart Model 7

-

Introduction of Model 7 Rack Cart

Options

Not all options were available through the whole lifecycle of the DPO. As an Example: 4k Core Memory was the default configuration in early production years and became an option in later years. Other options like the CP bus Interface got an update and a new part number.

| Option | Description | Kit- or Partnumber | Price in 1981 |

|---|---|---|---|

| 3 | Electromagnetic Interference (EMI) Shielding | 040-0671-00 | +$185 |

| 9 | Change line voltage to 230V/50Hz | - | No Charge |

| 18 | Change to 1k Semiconductor Memory | 670-2981-00 | -$1045 |

| 19 | Change to 2k Semiconductor Memory | 670-3035-00 | -$760 |

| 20 | Change to 4k Core Memory | 672-0057-00 | +$315 |

| 31 | Add IEEE 488 Bus Interface | 021-0206-00 | +$2000 |

| 32 | Add CP Bus Interface | 021-0116-00, 021-0116-01, 021-0116-02 or 021-0116-03 |

+$475 |

| ? | Add Hardware Signal Average (HSA) Module | 644-0092-00 or 672-0725-00 |

Programming Examples

Various ways of data access

The following examples might help to understand the programming differences between 16- and 10-bit data access and high level information access. All three examples write the word "HELLO" to the Location D in Message Field 2 and instruct the Readout Interface to show this Message on the CRT. Descriptions of the Readout Interface Status Register and data format can be seen in the images above. There is also an overview of the P7001 Address Map.

Example A: 16 bit Memory or Register Access While the data bus of the P7001 is 16 bit wide, most of the stored data is only 10 bit wide. More importantly, bit 0 of the needed data word is not always aligned to bit 0 of the data bus. A very good example of this design is the data format of the Readout Interface. Bit 0 of the readout information starts at bit 5 on the data bus. To get or write the readout information we have to shift and crop or expand the data bits.

The ASCII code for the character "H" is 72. Converted to 16 bit binary and shifted 5 times to the left: 0000100100000000 or in octal notation: 004400. Our destination message field starts at memory location 3456 (octal: 6600). We can do the same calculations for the other readout characters. At the end we have to instruct the Readout Interface to display the message. For displaying Location D of Message field 2, we have to set the bits 6 and 14 of the Readout Interface Register. In binary notation: 0100000001000000 In octal notation: 040100 The register is located at memory address 7296 (octal: 16200)

The final program might look like:

SEND ("ADR 3456", "OCT 004400") // 'H' -> ASCII 72 -> 0000100100000000 -> 004400

SEND ("ADR 3457", "OCT 004240") // 'E' -> ASCII 69 -> 0000100010100000 -> 004240

SEND ("ADR 3458", "OCT 004600") // 'L' -> ASCII 76 -> 0000100110000000 -> 004600

SEND ("ADR 3459", "OCT 004600") // 'L' -> ASCII 76 -> 0000100110000000 -> 004600

SEND ("ADR 3460", "OCT 004740") // 'O' -> ASCII 79 -> 0000100111100000 -> 004740

SEND ("ADR 7296", "OCT 040100") // Show Message field 2 / Location D on CRT

Example B: 10 bit Memory Access Most of the time we're dealing with 10 bit data information. To make life easier, Tektronix implemented the "WRD" instruction set on the controller. This instruction set handles the data conversion between the ASCII data and the 16 bit universe of the P7001. The command also implements an auto-increment for the address data.

The new program looks like:

SEND ("ADR 3456" , "WRD 72") //'H'

SEND ("WRD 69") //E -> the destination address is auto-incremented

SEND ("WRD 76") //L

SEND ("WRD 76") //L

SEND ("WRD 79") //O

SEND ("ADR 7296", "OCT 040100") // Show Messagefield 2 / Location D on CRT

Example C: High Level Instruction Set Finally, there is a high-level command implemented which sends the readout data in one line: SEND ("ADR 3456", "SCL HELLO ") // The last space is needed as terminator character. SEND ("ADR 7296", "OCT 040100") // Show Message field 2 / Location D on CRT

X/Y Mode

A description of the Display Generator Status Register and Data Format can be seen in the images above.

The Display Generator Status Register is located at memory location 7168 (octal: 16000). To enable the software-controlled X-Y Display and waveform "D", we have to set bit 13 and 6 in this register. In binary notation: 0010000001000000 In octal notation: 020100

To display a shape, we have to continuously move the beam around from point to point. The X/Y coordinates for the lower left point on the CRT is 7680/0 (octal: 17000/0), and for the upper right point 8191/1023 (octal: 17777/1777). We can also control the beam intensity of each movement between 0 (disabled) and 3 (full brightness). The Y-value and brightness level are encoded into the Display Generators Data Format and the result is sent to the desired X-Address of the Display Generator.

The resulting program in pseudo-code:

SEND ("ADR 7168", "OCT 020100") //enable X-Y Mode for Waveform "D"

SEND ("ADR 7834", "OCT 063100") //blank the beam and move it invisible to the start point of drawing

Start loop //write a T-shaped curve continuously in a loop at full intensity

SEND ("ADR 8069", "OCT 063130")

SEND ("ADR 8069", "OCT 054030")

SEND ("ADR 7981", "OCT 054030")

SEND ("ADR 7981", "OCT 014670")

SEND ("ADR 7918", "OCT 014670")

SEND ("ADR 7918", "OCT 054030")

SEND ("ADR 7834", "OCT 054030")

SEND ("ADR 7834", "OCT 063130")

End loop

SEND ("ADR 7168", "OCT 000100") //disable X-Y Mode for Waveform "D"

Bugs & Errors

Design Flaw of the A/D Converter

-

-

Example of invalid start & end points

The dynamic range of the sampled waveform is greater than the converted output of the A/D converter. Any sampled point which is left to the CRT viewing area will be added to memory location 0, and any point which is right to the CRT viewing area will be added to memory location 511. The end points (0 and 511) of the acquired waveform data should be considered invalid for measurement purposes. ServiceTekNotes Issue 25, Sep 1982 describes the problem and shows a possible solution.

Firmware Bug in GPIB interface

Affected Firmware versions: all

Due to an error in the firmware, pin 9 of U123 is always configured as an output pin. This pin is directly connected to an output of the line driver IC U321. To prevent damage to the PIA chip, it is recommended to remove the line driver U321. Since U321 is only needed for internal testing, it can be removed without any problems.

Catalogs & Advertising

-

P7001 Spec 1973

-

P7001 Spec 1974

-

P7001 Spec 1975

-

P7001 Spec 1976

-

P7001 Spec 1977

-

P7001 Spec 1978

-

P7001 Spec 1979

-

P7001 Spec 1980

-

P7001 Spec 1981

-

Partial Master Publication Index with all DPO related pages

-

Typical DPO advertising in 1973

-

DPO+31 Just Married advertising from 1973

-

PDO advertising in 'Electronics' magazine july 1973

-

Typical DPO advertising in 1977

-

1978 advert about the new options GPIB interface and hardware signal averager

Introduction March 1973

-

Bill Walker and Hiro Moriyasu with the P7001 at the IEEE Intercon 1973 in New York

-

Tekweek about new products at the 1973 IEEE Intercon in New York

-

Electronis Magazine about the new DPO in 1973. Article written by Hiro Moriyasu, Bruce Hamilton, Luis Navarro and Wayne Eshelman

Name change

Early units are named "Tektronix P7001 Processor" - later units (probably starting with B1XXXXX) are named "Tektronix P7001 Digitizer".

-

Older name

-

Newer name

Field of Application

-

Usage of the P7001 & 7J20 at RCA

-

Competitive Product Analysis with the P7001 at RCA

Appearance in Tektronix Magazines

- ServiceTekNotes Issue 25, Sep 1982 about the A/D converters design flaw

- TekScope Vol. 5 No. 2, Mar-Apr 1973 about the introduction of the P7001